A Reconfigurable Hybrid RF Front-End Rectifier for Dynamic PCE Enhancement of Ambient RF Energy Harvesting Systems

Abstract

1. Introduction

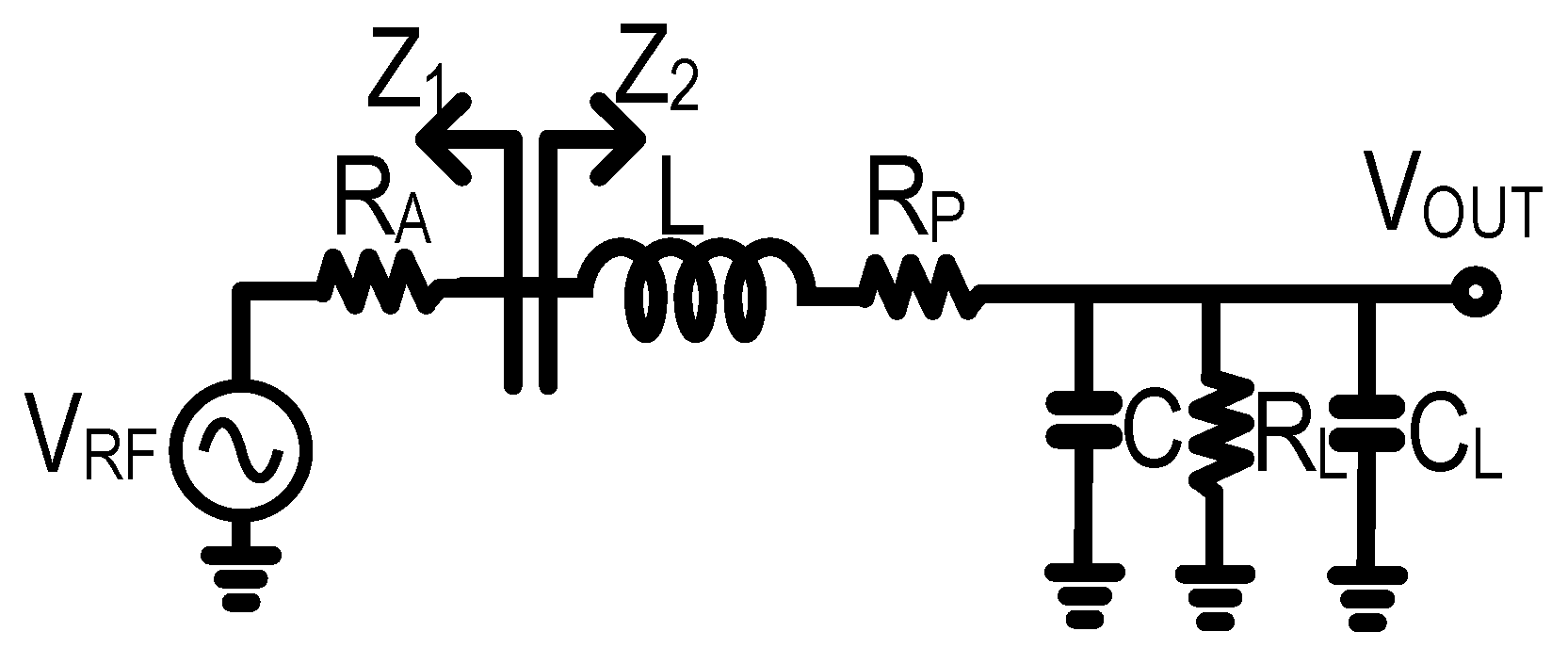

2. RFEH System Architecture

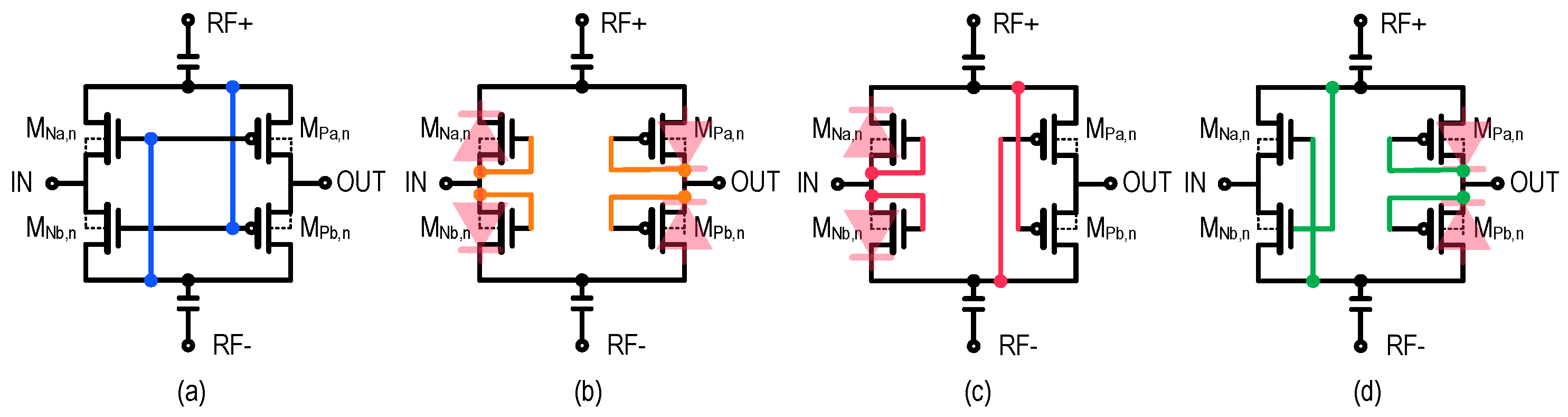

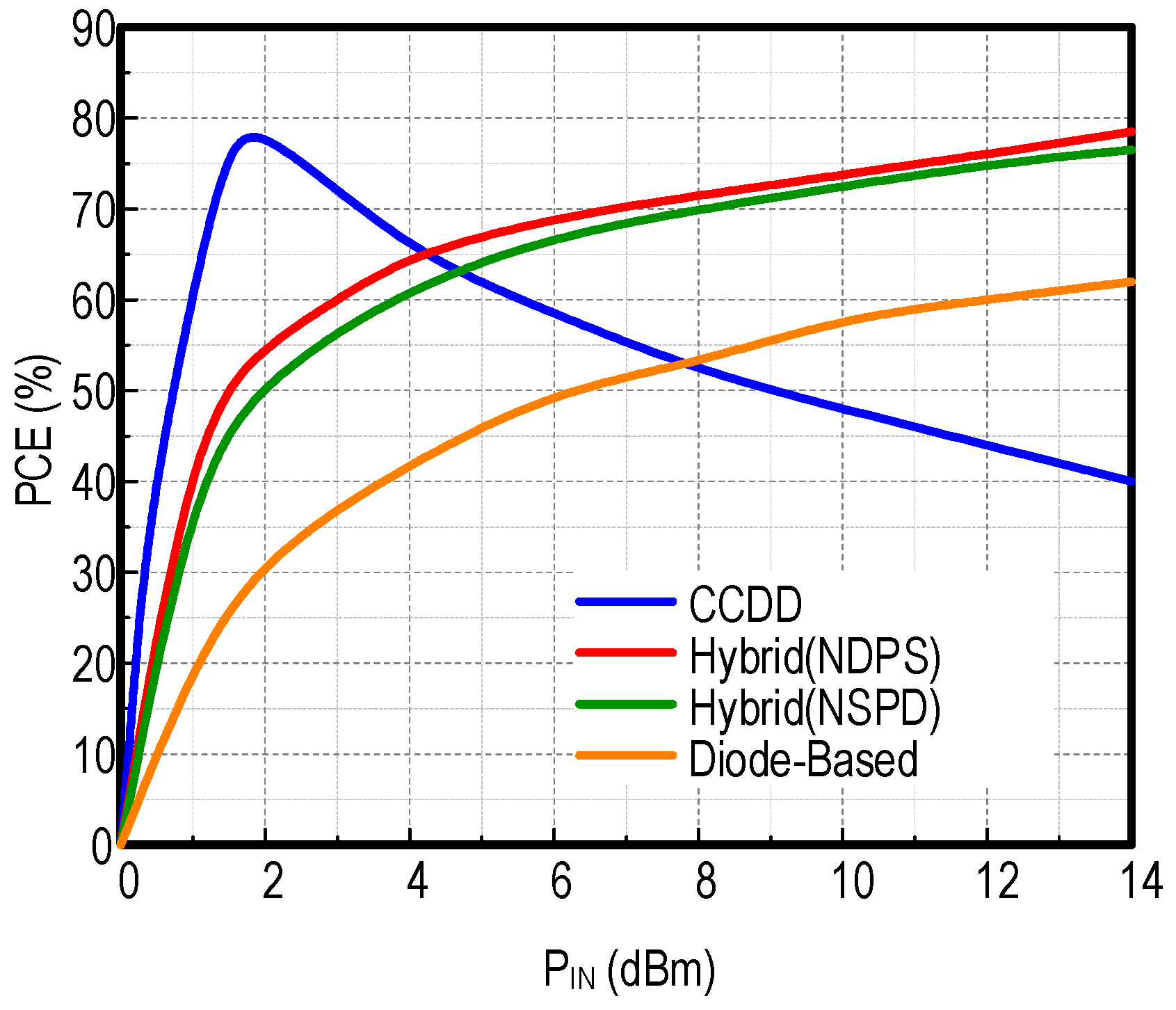

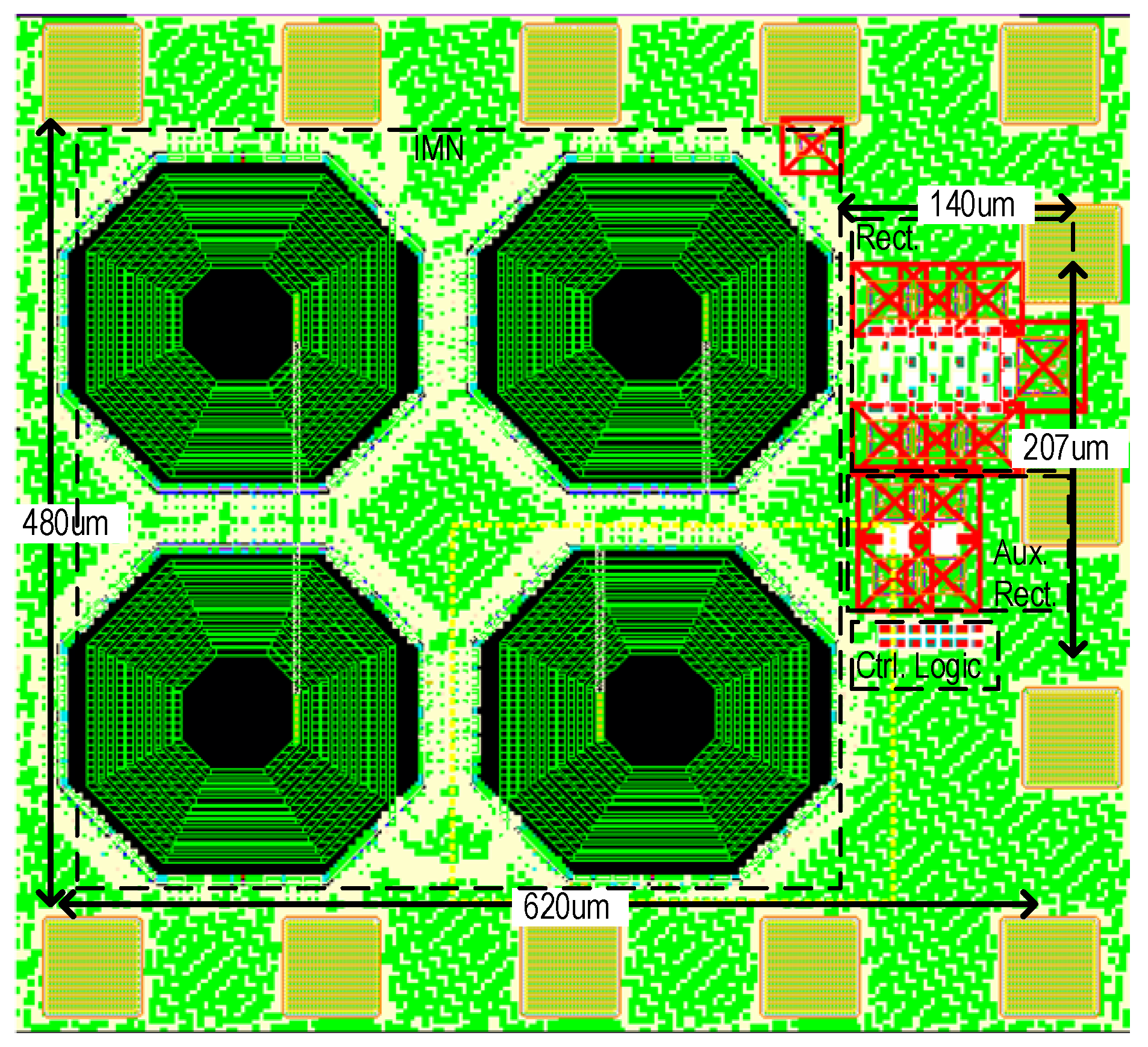

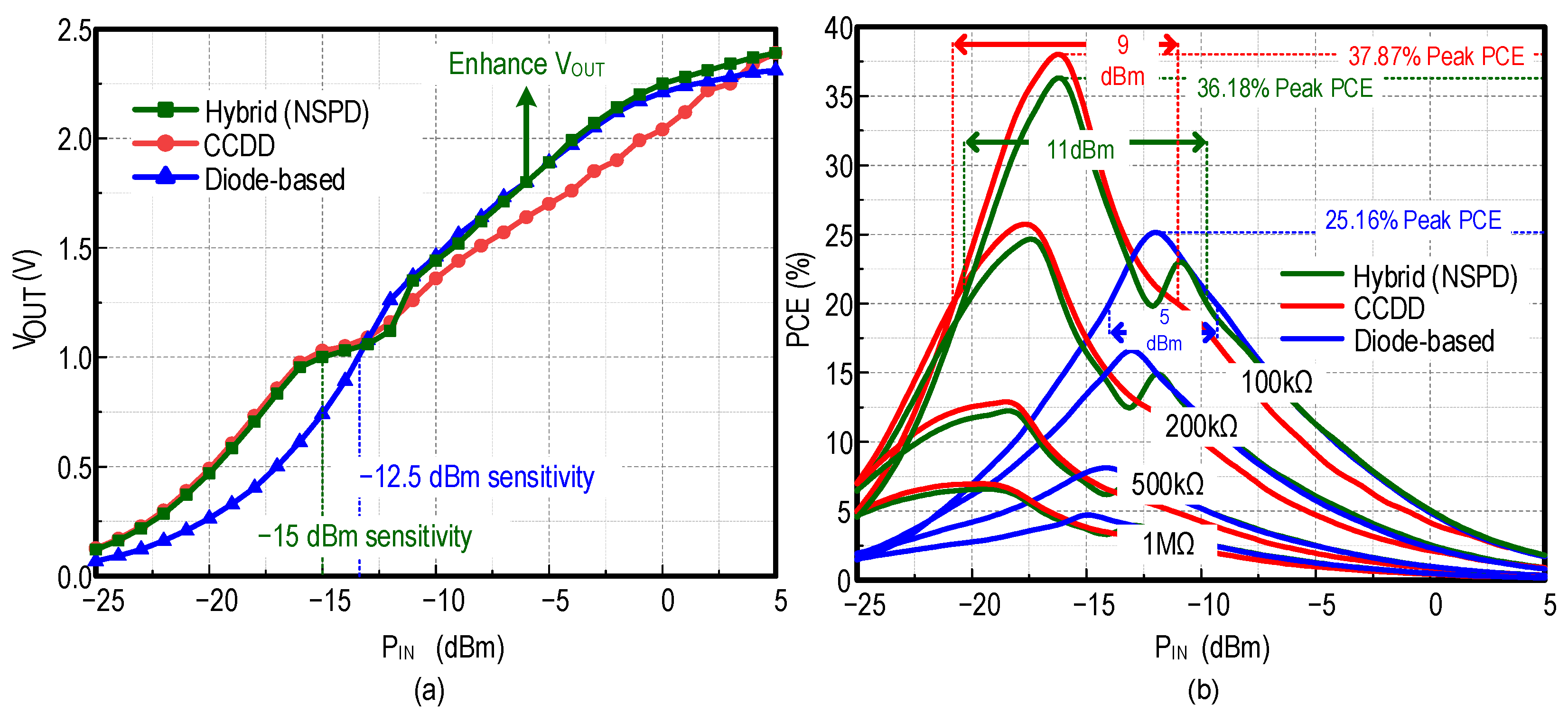

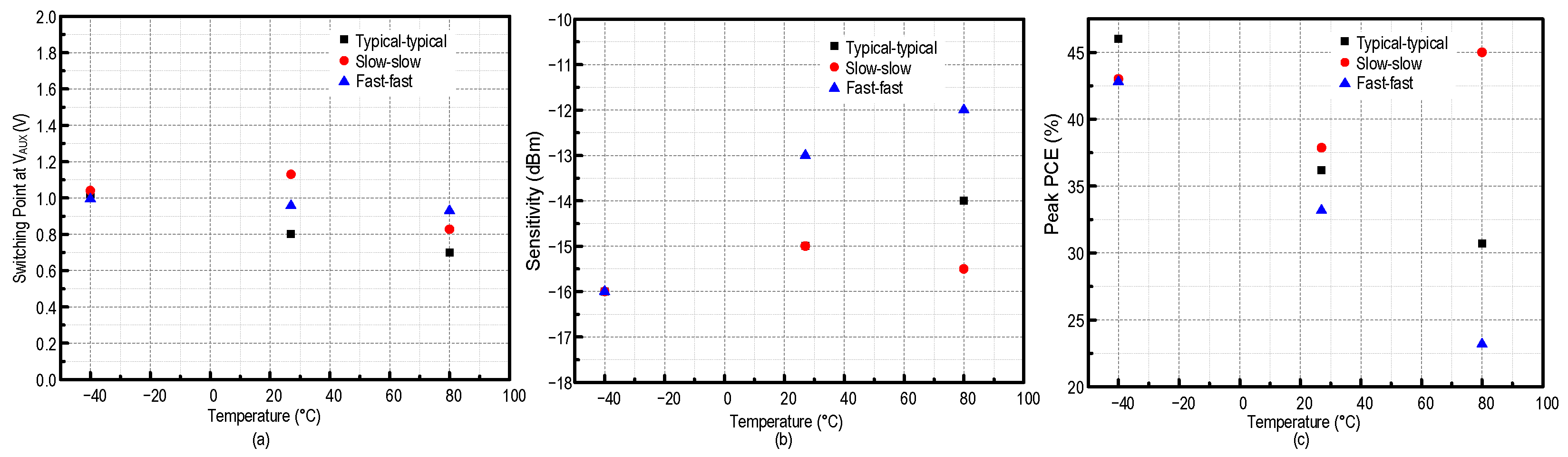

2.1. Rectifier Topologies

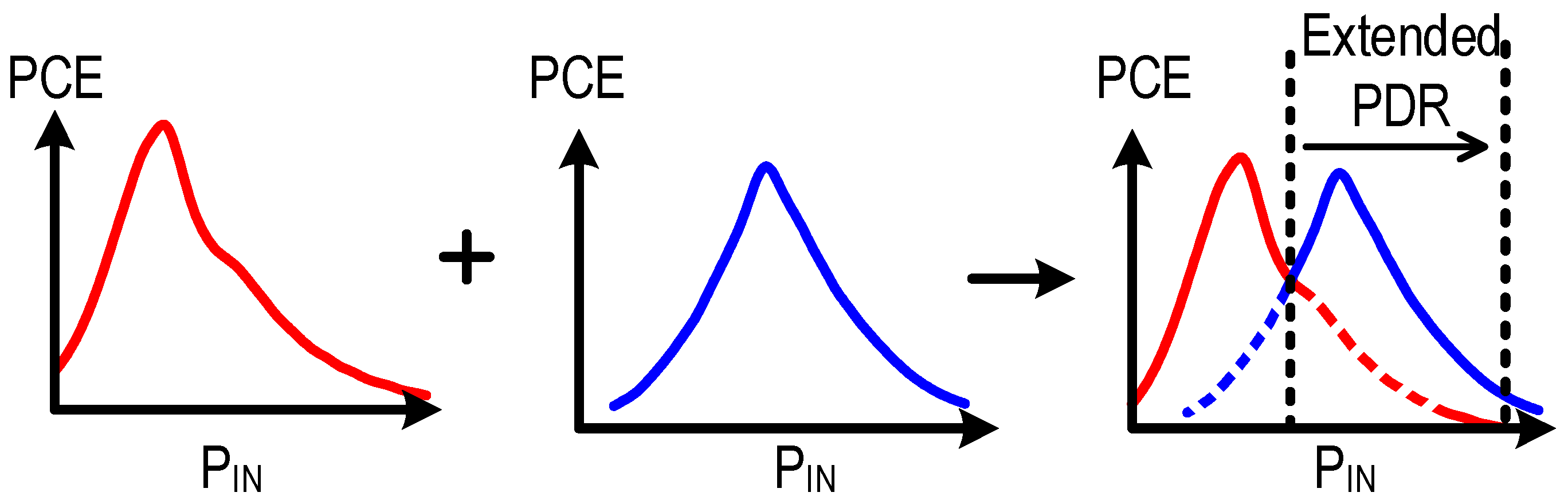

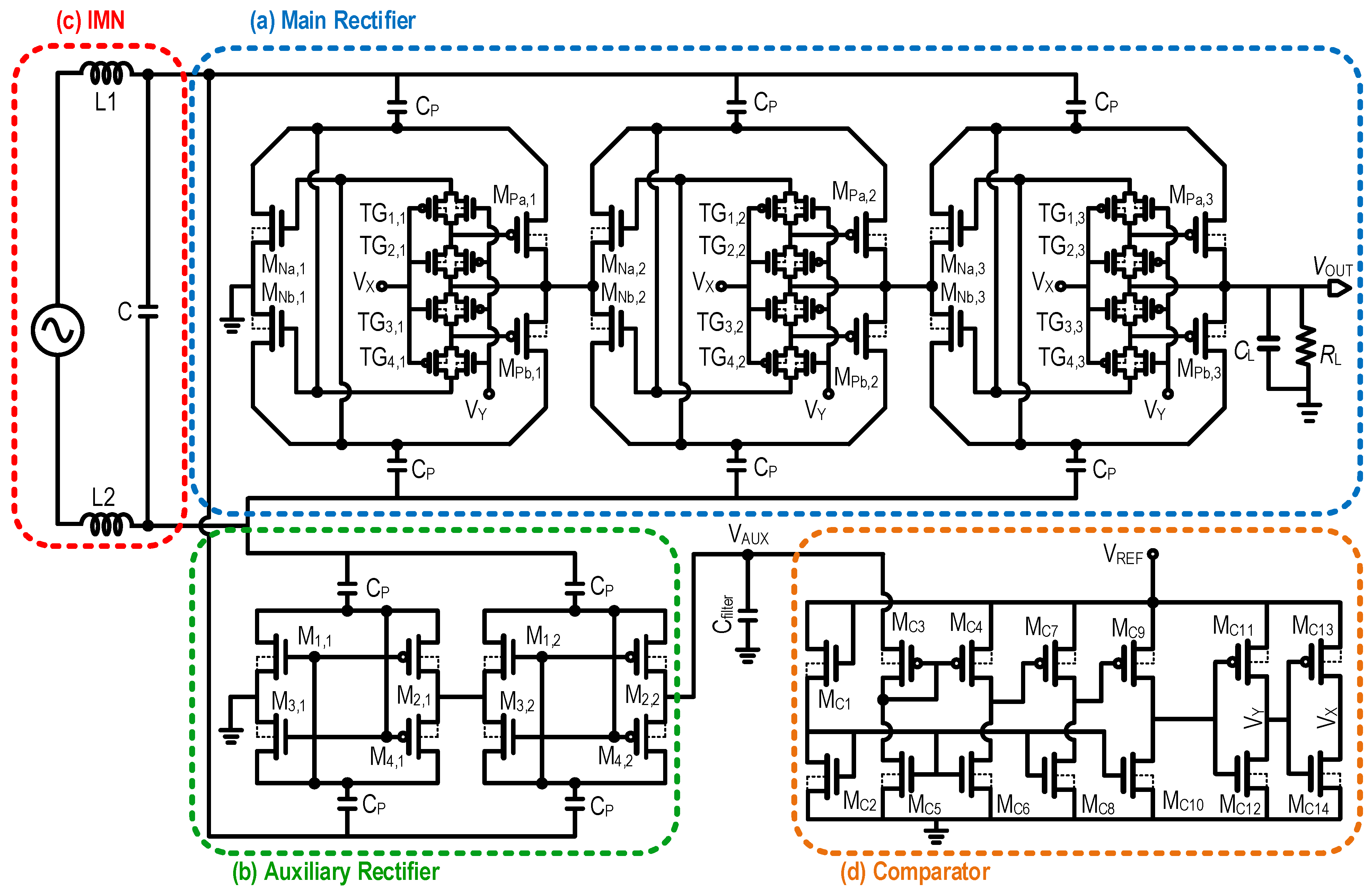

2.2. Proposed Circuit Architecture

3. Circuit Description

3.1. Main Rectifier

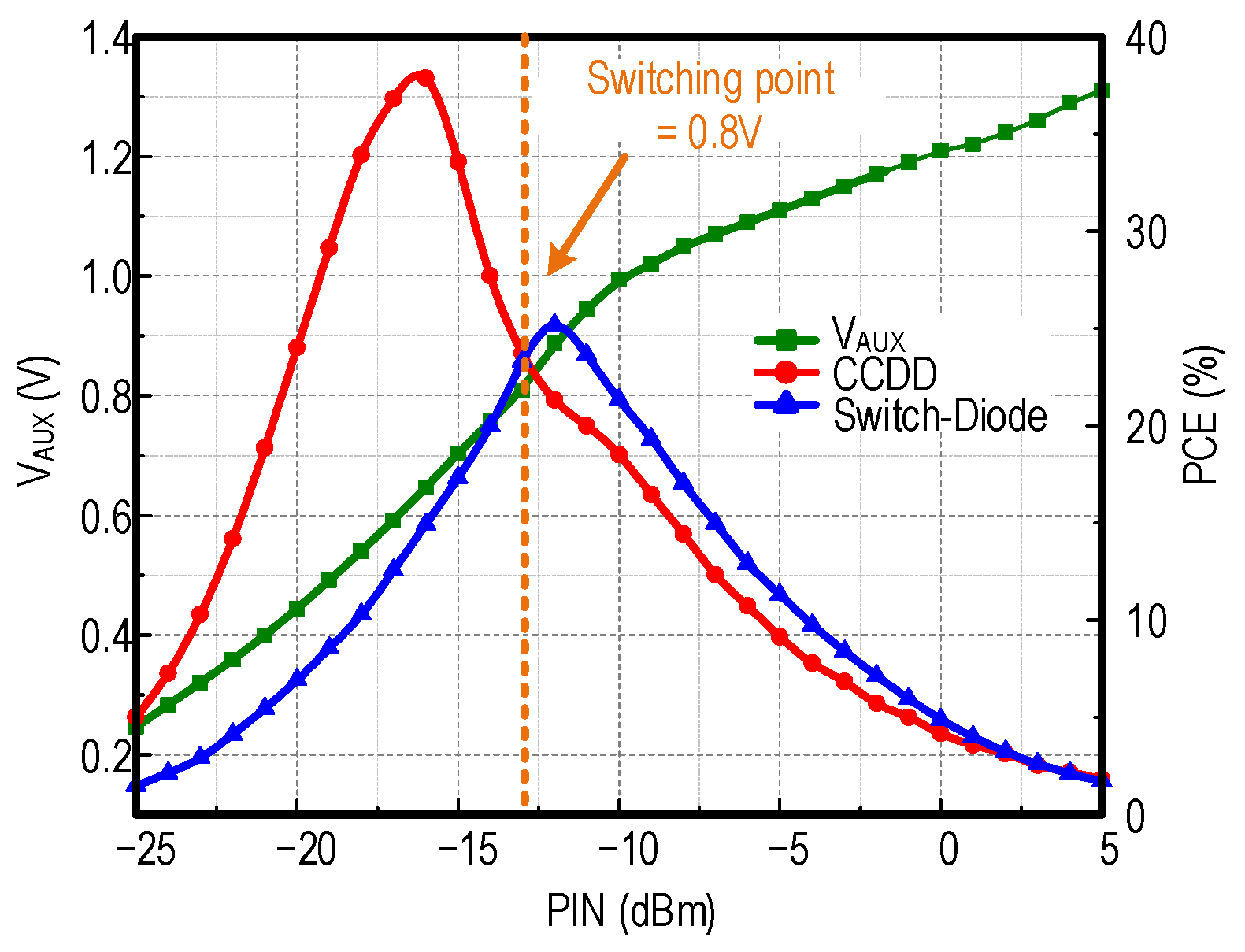

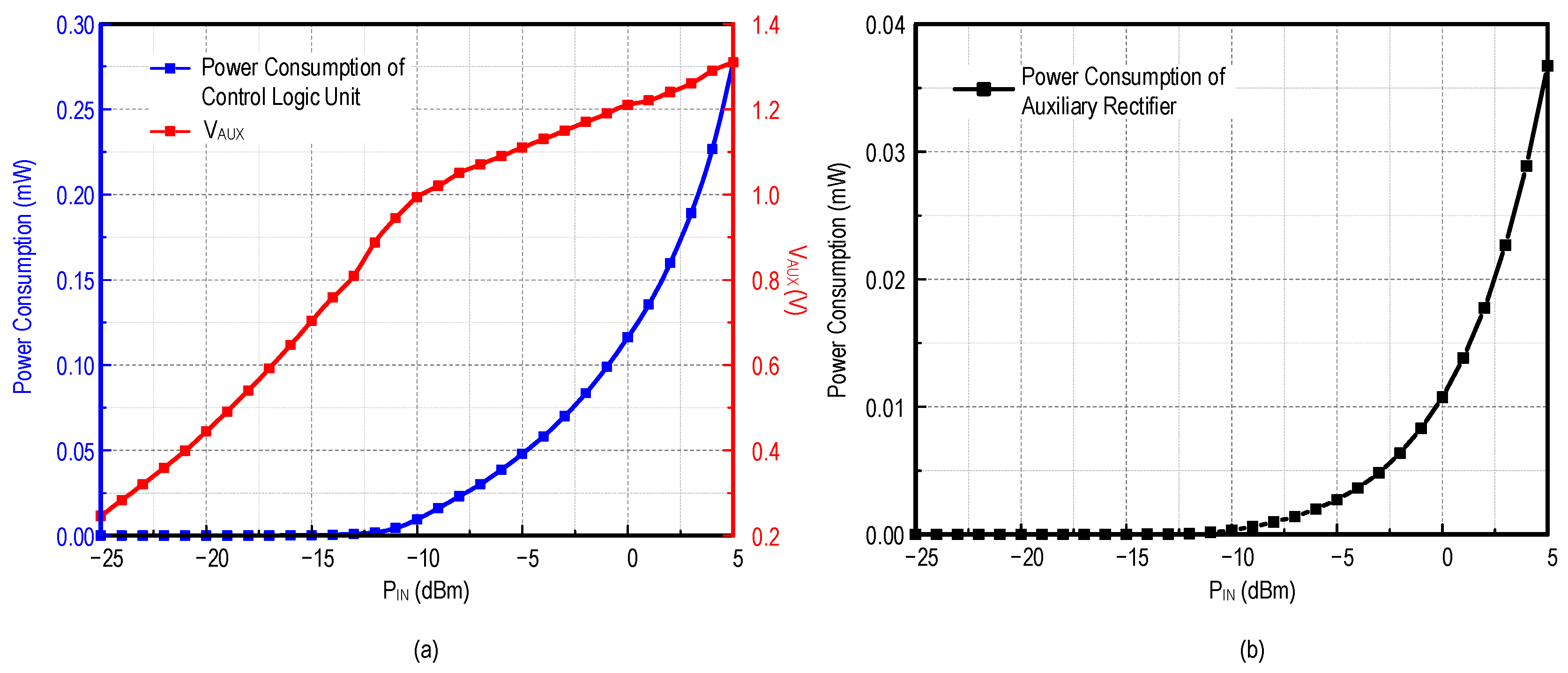

3.2. Auxiliary Rectifier

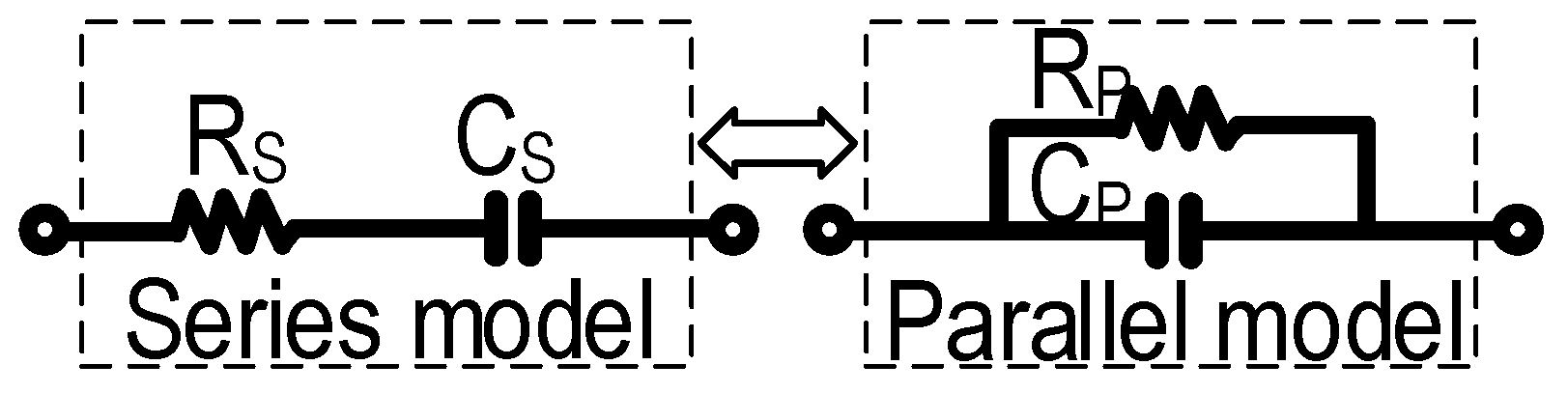

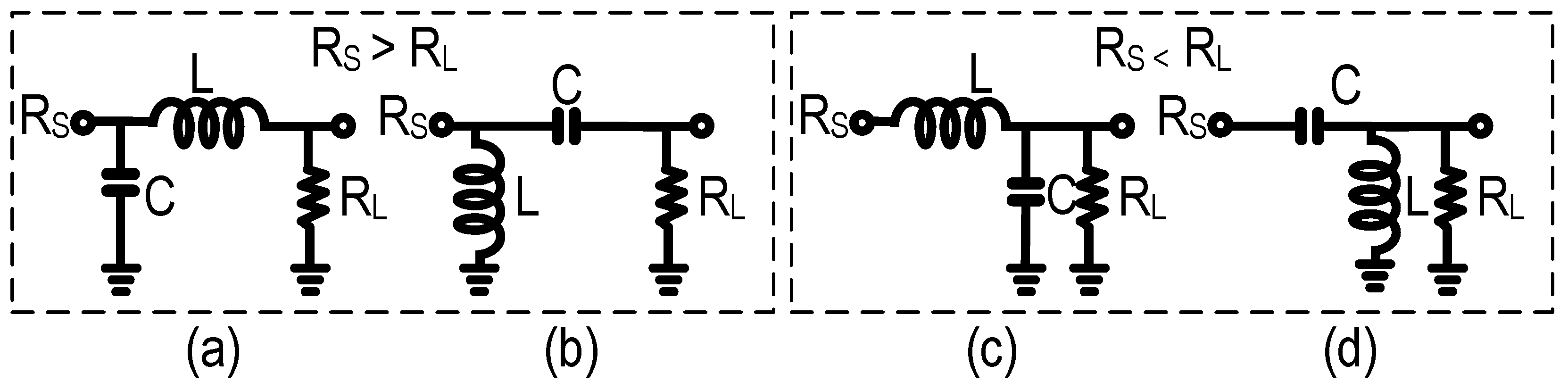

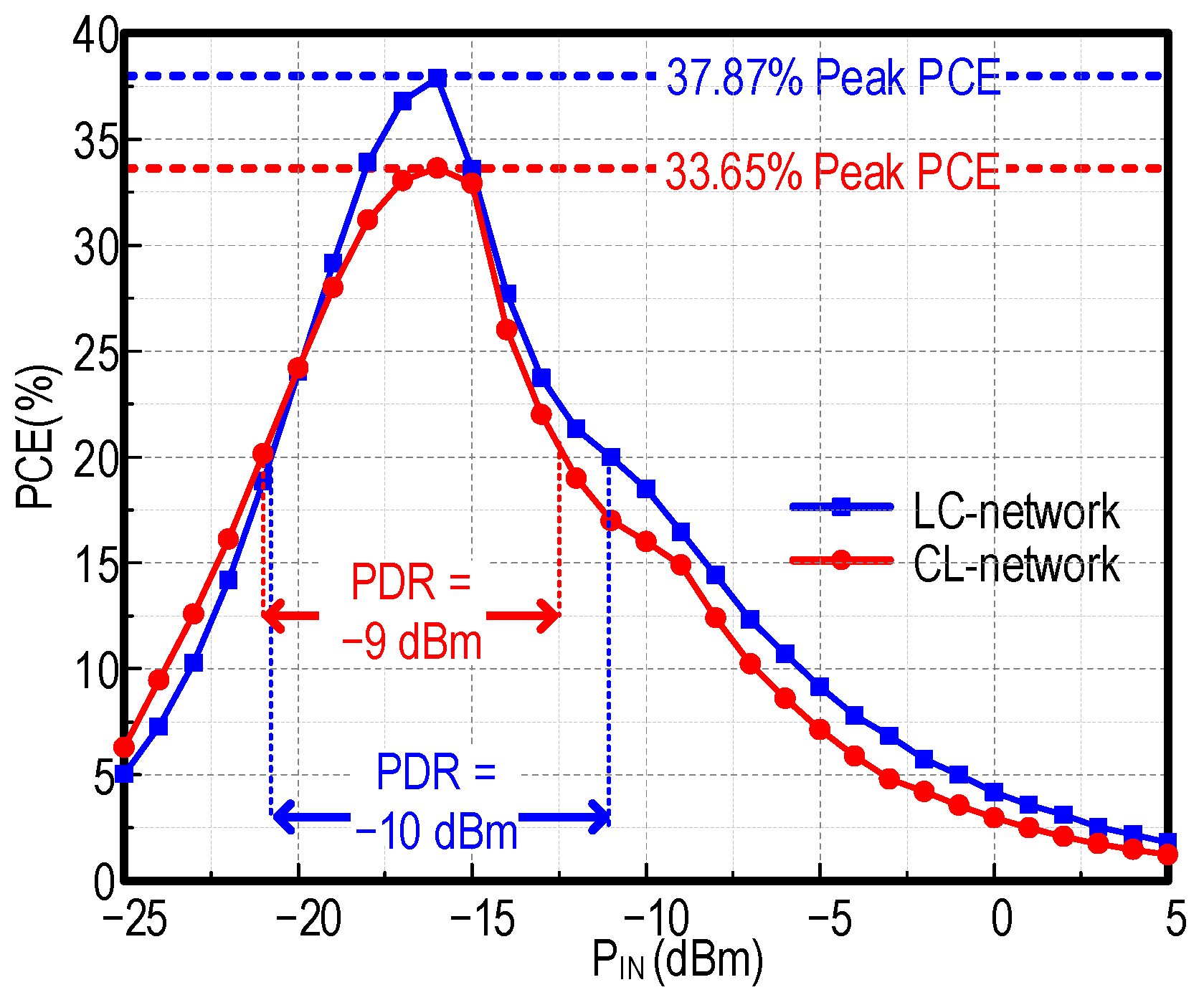

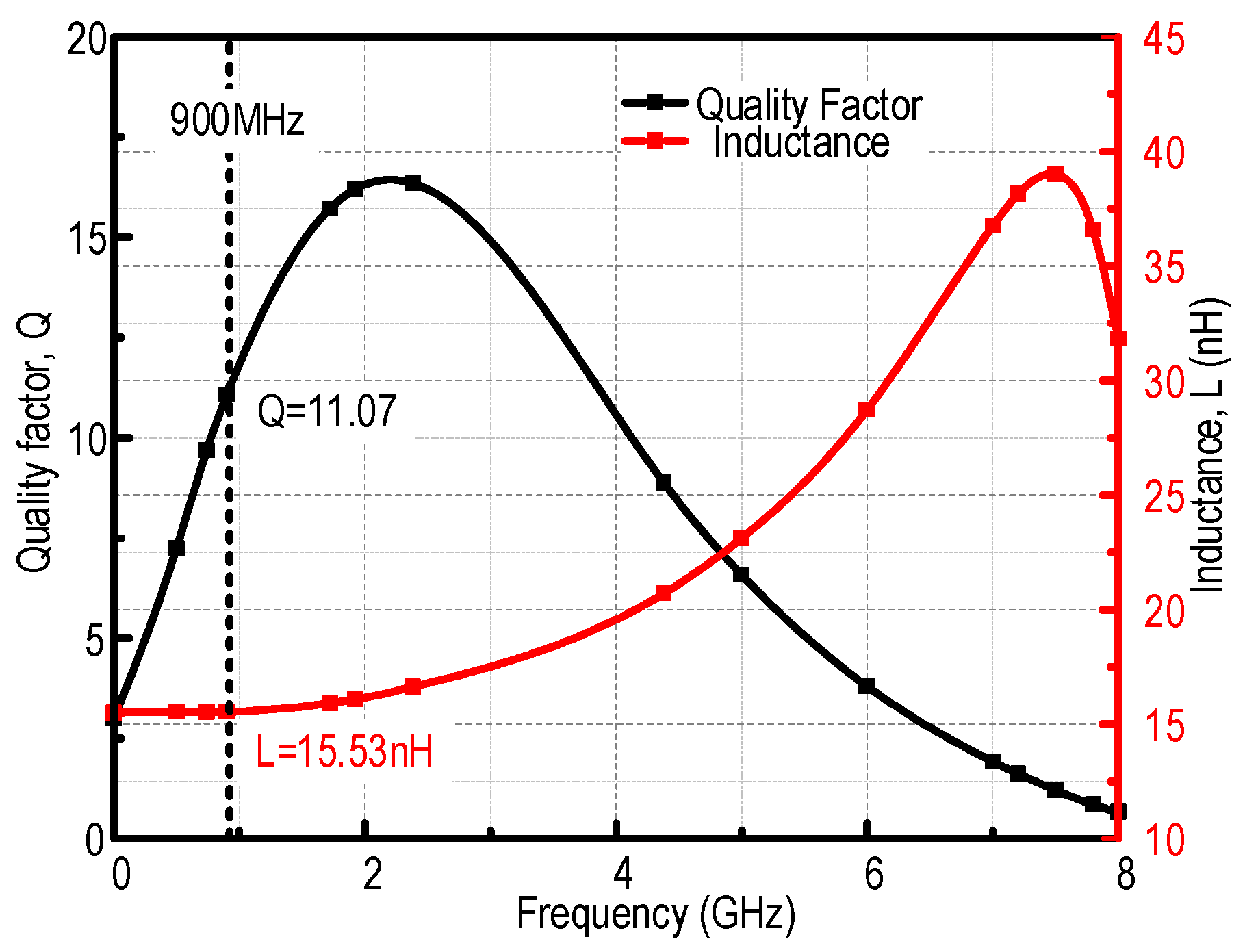

3.3. Impedance Matching Network

3.4. Control Logic Circuit

4. Postlayout and Simulation Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Luo, Y.; Pu, L.; Wang, G.; Zhao, Y. RF Energy Harvesting Wireless Communications: RF Environment, Device Hardware and Practical Issues. Sensors 2019, 19, 3010. [Google Scholar] [CrossRef] [PubMed]

- Ho, T.S.; Ramiah, H.; Churchill, K.K.P.; Chen, Y.; Lim, C.C.; Lai, N.S.; Mak, P.-I.; Martins, R.P. Low Voltage Switched-Capacitive-Based Reconfigurable Charge Pumps for Energy Harvesting Systems: An Overview. IEEE Access 2022, 10, 126910–126930. [Google Scholar] [CrossRef]

- Saffari, P.; Basaligheh, A.; Moez, K. An RF-to-DC Rectifier With High Efficiency Over Wide Input Power Range for RF Energy Harvesting Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 4862–4875. [Google Scholar] [CrossRef]

- Basim, M.; Khan, D.; Ain, Q.U.; Shehzad, K.; Shah, S.A.A.; Jang, B.-G.; Pu, Y.-G.; Yoo, J.-M.; Kim, J.-T.; Lee, K.-Y. A Highly Efficient RF-DC Converter for Energy Harvesting Applications Using a Threshold Voltage Cancellation Scheme. Sensors 2022, 22, 2659. [Google Scholar] [CrossRef]

- Chong, G.; Ramiah, H.; Yin, J.; Rajendran, J.; Mak, P.I.; Martins, R.P. A Wide-PCE-Dynamic-Range CMOS Cross-Coupled Differential-Drive Rectifier for Ambient RF Energy Harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1743–1747. [Google Scholar] [CrossRef]

- Churchill, K.K.P.; Chong, G.; Ramiah, H.; Ahmad, M.; Rajendran, J. Low-Voltage Capacitive-Based Step-Up DC-DC Converters for RF Energy Harvesting System: A Review. IEEE Access 2020, 8, 186393–186407. [Google Scholar] [CrossRef]

- Yong, J.K.; Ramiah, H.; Churchill, K.K.P.; Chong, G.; Mekhilef, S.; Chen, Y.; Mak, P.-I.; Martins, R.P. A 0.1-V VIN Subthreshold 3-Stage Dual-Branch Charge Pump With 43.4% Peak Power Conversion Efficiency Using Advanced Dynamic Gate-Bias. IEEE Trans. Circuits Syst. II Express Briefs 2022, 9, 3929–3933. [Google Scholar] [CrossRef]

- Almansouri, A.S.; Ouda, M.; Salama, K.N. A CMOS RF-to-DC Power Converter With 86% Efficiency and −19.2-dBm Sensitivity. IEEE Trans. Microw. Theory Tech. 2018, 66, 2409–2415. [Google Scholar] [CrossRef]

- Ouda, M.H.; Khalil, W.; Salama, K.N. Self-Biased Differential Rectifier with Enhanced Dynamic Range for Wireless Powering. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 515–519. [Google Scholar] [CrossRef]

- Lu, Y.; Dai, H.; Huang, M.; Law, M.-K.; Sin, S.-W.; Seng-Pan, U.; Martins, R.P. A Wide Input Range Dual-Path CMOS Rectifier for RF Energy Harvesting. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 166–170. [Google Scholar] [CrossRef]

- Choo, A.; Ramiah, H.; Churchill, K.K.P.; Chen, Y.; Mekhilef, S.; Mak, P.-I.; Martins, R.P. A Reconfigurable CMOS Rectifier With 14-dB Power Dynamic Range Achieving >36-dB/mm2 FoM for RF-Based Hybrid Energy Harvesting. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 1533–1537. [Google Scholar] [CrossRef]

- Heo, B.-R.; Kwon, I. A Dual-Band Wide-Input-Range Adaptive CMOS RF–DC Converter for Ambient RF Energy Harvesting. Sensors 2021, 21, 7483. [Google Scholar] [CrossRef] [PubMed]

- Guler, U.; Jia, Y.; Ghovanloo, M. A Reconfigurable Passive RF-to-DC Converter for Wireless IoT Applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1800–1804. [Google Scholar] [CrossRef]

- Ouda, M.H.; Khalil, W.; Salama, K.N. Wide-Range Adaptive RF-to-DC Power Converter for UHF RFIDs. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 634–636. [Google Scholar] [CrossRef]

- Alhoshany, A. A 900 MHz, Wide-Input Range, High-Efficiency, Differential CMOS Rectifier for Ambient Wireless Powering. Sensors 2022, 22, 974. [Google Scholar] [CrossRef]

- Chong, G.C.; Ramiah, H.; Yin, J.; Rajendran, J.; Wong, W.R.; Mak, P.-I.; Martins, R.P.; Ru, W.W. CMOS Cross-Coupled Differential-Drive Rectifier in Subthreshold Operation for Ambient RF Energy Harvesting—Model and Analysis. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1942–1946. [Google Scholar] [CrossRef]

- Lian, W.X.; Ramiah, H.; Chong, G.; Churchill, K.K.P.; Lai, N.S.; Chen, Y.; Mak, P.-I.; Martins, R.P. A −20-dBm Sensitivity RF Energy-Harvesting Rectifier Front End Using a Transformer IMN. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 1808–1812. [Google Scholar] [CrossRef]

- Chun, A.C.C.; Ramiah, H.; Mekhilef, S. Wide Power Dynamic Range CMOS RF-DC Rectifier for RF Energy Harvesting System: A Review. IEEE Access 2022, 10, 23948–23963. [Google Scholar] [CrossRef]

- Pakkirisami Churchill, K.K.; Ramiah, H.; Chong, G.; Chen, Y.; Mak, P.I.; Martins, R.P. A Fully-Integrated Ambient RF Energy Harvesting System with 423-μW Output Power. Sensors 2022, 22, 4415. [Google Scholar] [CrossRef]

- Soltani, N.; Yuan, F. A step-up transformer impedance transformation technique for efficient power harvesting of passive transponders. Microelectron. J. 2010, 41, 0026–2692. [Google Scholar] [CrossRef]

- Soltani, N.; Yuan, F. A High-Gain Power-Matching Technique for Efficient Radio-Frequency Power Harvest of Passive Wireless Microsystems. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 2685–2695. [Google Scholar] [CrossRef]

- Yuen, P.W.; Chong, G.; Ramiah, H. A high efficient dual-output rectifier for piezoelectric energy harvesting. Int. J. Electron. Commun. 2019, 111, 1434–8411. [Google Scholar] [CrossRef]

- Moghaddam, A.K.; Chuah, J.; Ramiah, H.; Ahmadian, J.; Mak, P.I.; Martins, R.P. A 73.9%-Efficiency CMOS Rectifier Using a Lower DC Feeding (LDCF) Self-Body-Biasing Technique for Far-Field RF Energy-Harvesting Systems. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 992–1002. [Google Scholar] [CrossRef]

| Circuit Blocks | Circuit | Components Type | Components Name | Size |

|---|---|---|---|---|

| Main Rectifier | Rectifier | NMOS (LVT) | MNa & MNb | 18 μm |

| PMOS (LVT) | PNa & PNb | 36 μm | ||

| MIM Capacitor | CP | 1 pF | ||

| Transmission Gate | NMOS (LVT) | TG (NMOS) | 2 μm | |

| PMOS (LVT) | TG (PMOS) | 4 μm | ||

| Auxiliary Rectifier | Rectifier | NMOS (LVT) | M1 & M3 | 600 nm |

| PMOS (LVT) | M2 & M4 | 36 μm | ||

| MIM Capacitor | CP | 1 pF | ||

| MIM Capacitor | CFilter | 1 pF | ||

| Control Logic Unit | Comparator | NMOS (Standard) | MC1,2,5,6,8,10,12,14 | 21.6 μm |

| PMOS (Standard) | MC3,4,7,9,11,13 | 7.2 u |

| Reference | This Work | [3] | [5] | [8] | [10] | [11] | [23] | [13] |

|---|---|---|---|---|---|---|---|---|

| CMOS Tech. (nm) | 65 | 130 | 130 | 180 | 65 | 130 | 130 | 350 |

| Frequency (MHz) | 900 | 896 | 900 | 900 | 900 | 900 | 953 | 1356 |

| Rectifier Topology | CCDD | Dickson | CCDD | CCDD | CCDD | Dickson | CCDD | CCDD |

| Proposed Technique | Reconfigurable hybrid switch-diode configuration | Voltage Compensation | Self-body-biasing | Double-Sided Self-Biasing | Dual-Path | Reconfigurable No. of Stage/Series/ Parallel | Self-body-biasing/low-feeding DC | Manual hybrid switch-diode configuration |

| Sensitivity @1 V | −21 dBm @1 MΩ | −22 dBm @1 MΩ | −18.7 dBm @100 KΩ | −18.2 dBm @100 KΩ | −17.7 dBm @∞ | −21.7 dBm @1 MΩ | −6.5 dBm @50 KΩ | 3.22 dBm ** @500 KΩ |

| Rectifier’s Peak PCE | 88.7% @100 KΩ | 51% @300 KΩ | 80.3% @100 KΩ | 66% @100 KΩ | 36.5% @147 KΩ | 34.93% @1 MΩ | 69.5% @2 KΩ | 82% ** @500 KΩ |

| PDR (Rectifier PCE > 20%) | 23 dB | 10.5 dB | 17.5 dB * | 20 dB * | 11 dB | 14 dB | 13 dB * | N.A. |

| PDR (Rectifier PCE > 40%) | 16 dB | 4 dB | 14.5 dB | 10.5 dB | N.A. | N.A. | 10 dB | N.A. |

| PDR (Rectifier PCE > 60%) | 10 dB | N.A. | 9 dB | 3 dB | N.A. | N.A. | 5 dB | N.A. |

| Rectifier’s Effective Chip Area (mm2) | 0.028 | 0.053 | 0.062 | 0.0088 | 0.048 | 0.039 | 0.029 | 0.019 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lian, W.X.; Yong, J.K.; Chong, G.; Churchill, K.K.P.; Ramiah, H.; Chen, Y.; Mak, P.-I.; Martins, R.P. A Reconfigurable Hybrid RF Front-End Rectifier for Dynamic PCE Enhancement of Ambient RF Energy Harvesting Systems. Electronics 2023, 12, 175. https://doi.org/10.3390/electronics12010175

Lian WX, Yong JK, Chong G, Churchill KKP, Ramiah H, Chen Y, Mak P-I, Martins RP. A Reconfigurable Hybrid RF Front-End Rectifier for Dynamic PCE Enhancement of Ambient RF Energy Harvesting Systems. Electronics. 2023; 12(1):175. https://doi.org/10.3390/electronics12010175

Chicago/Turabian StyleLian, Wen Xun, Jack Kee Yong, Gabriel Chong, Kishore Kumar Pakkirisami Churchill, Harikrishnan Ramiah, Yong Chen, Pui-In Mak, and Rui P. Martins. 2023. "A Reconfigurable Hybrid RF Front-End Rectifier for Dynamic PCE Enhancement of Ambient RF Energy Harvesting Systems" Electronics 12, no. 1: 175. https://doi.org/10.3390/electronics12010175

APA StyleLian, W. X., Yong, J. K., Chong, G., Churchill, K. K. P., Ramiah, H., Chen, Y., Mak, P.-I., & Martins, R. P. (2023). A Reconfigurable Hybrid RF Front-End Rectifier for Dynamic PCE Enhancement of Ambient RF Energy Harvesting Systems. Electronics, 12(1), 175. https://doi.org/10.3390/electronics12010175