A High Phase Detection Density and Low Space Complexity Mueller-Muller Phase Detector for DB PAM-4 Wireline Receiver

Abstract

:1. Introduction

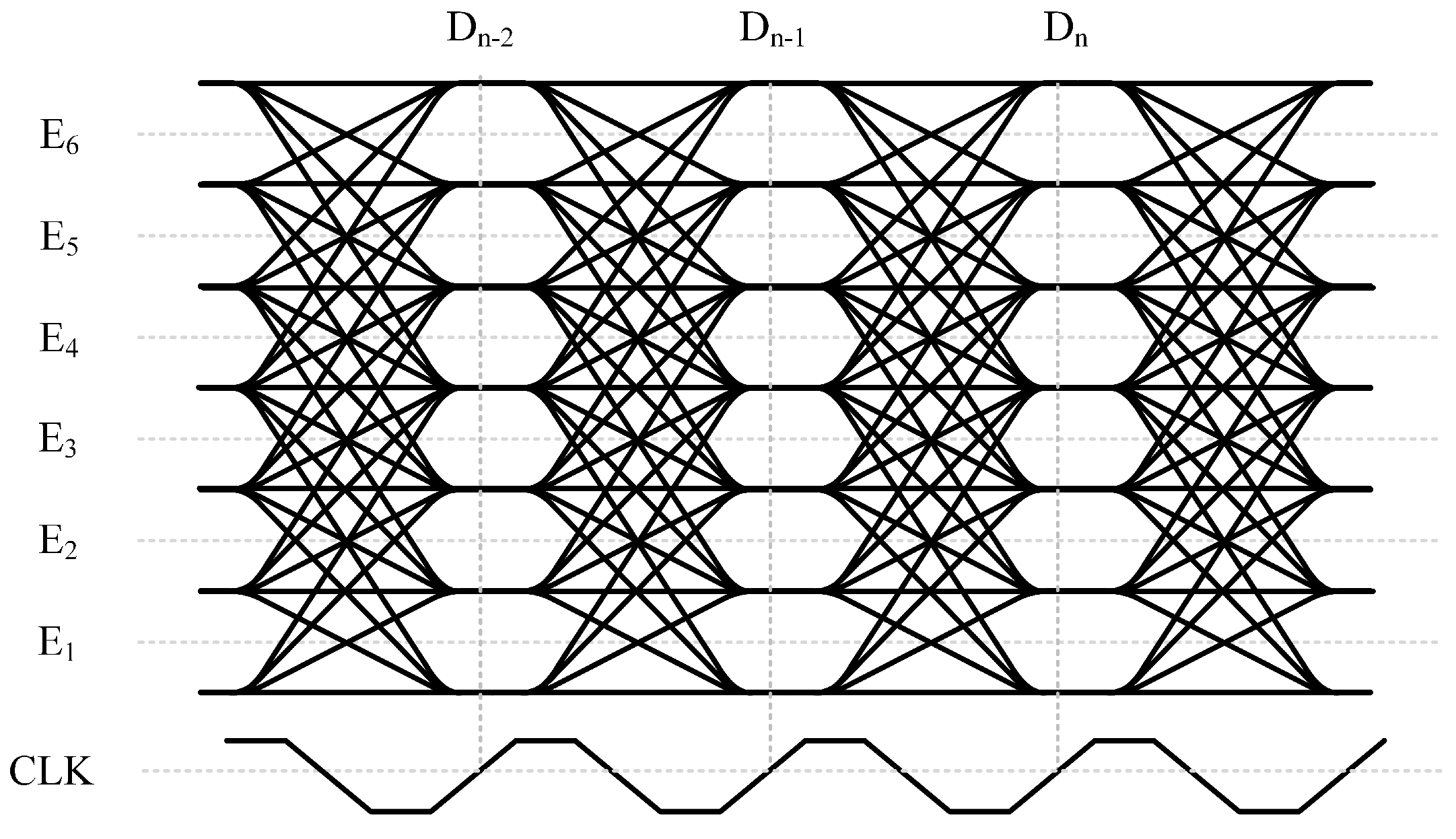

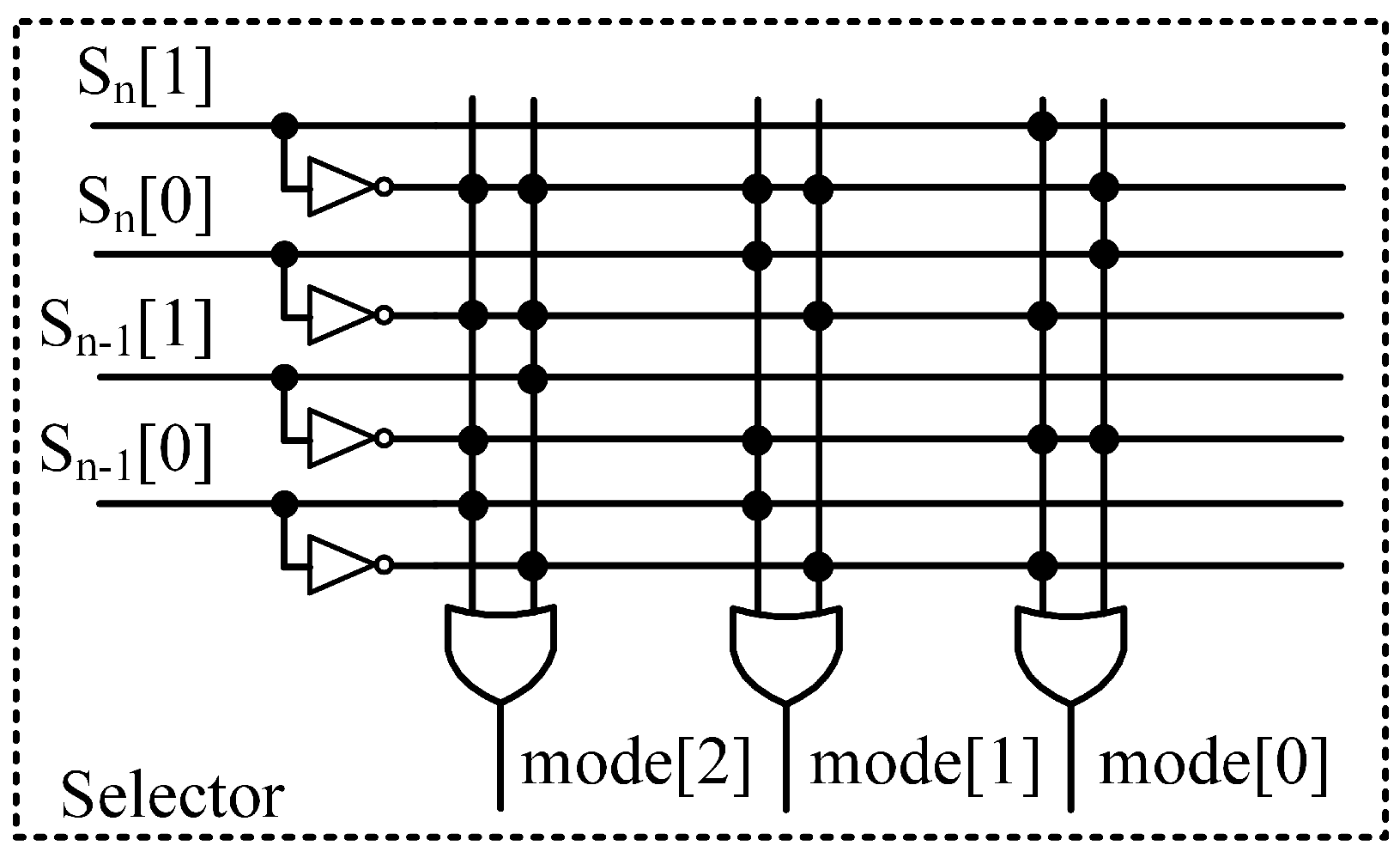

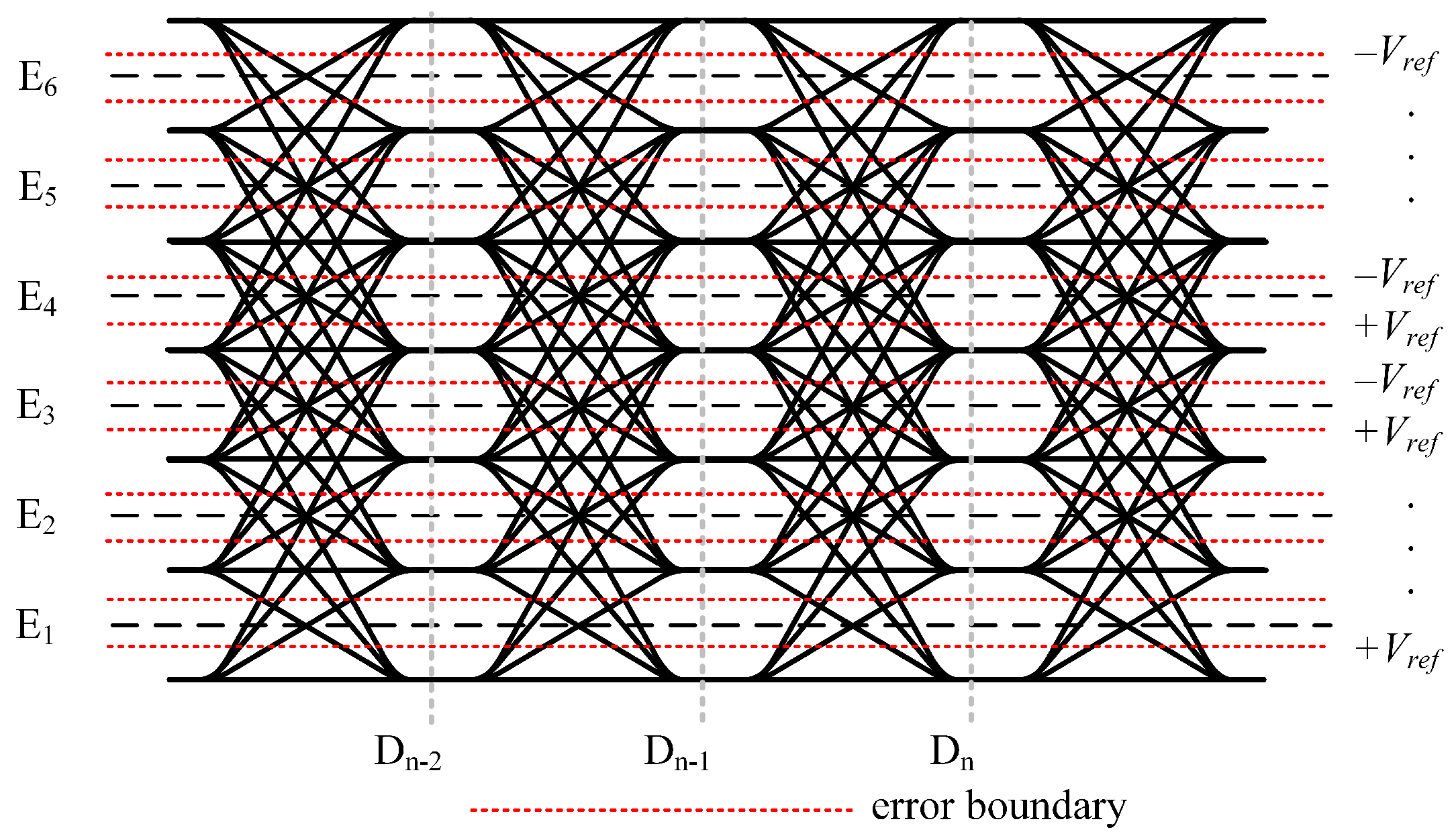

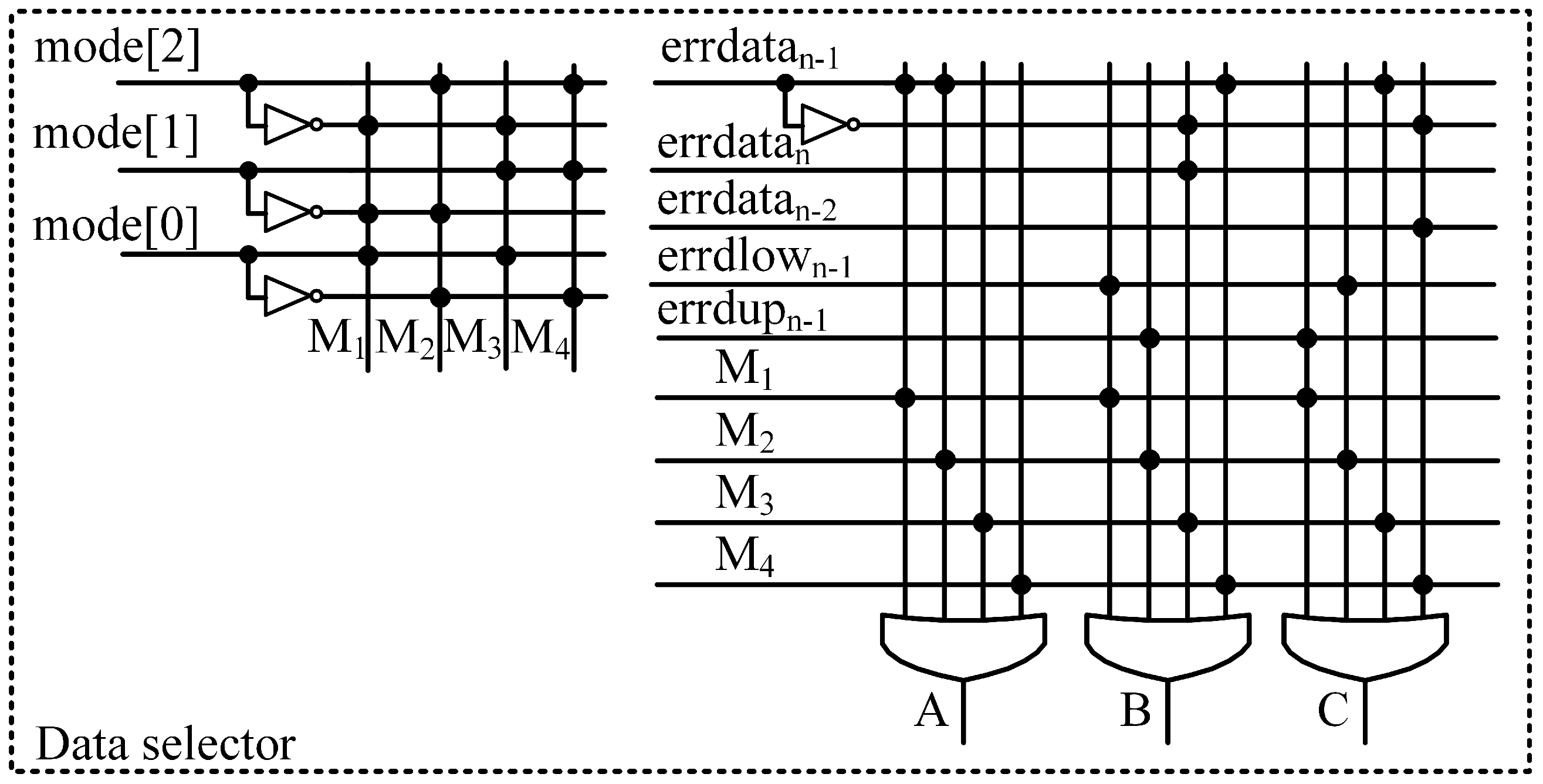

2. System Architecture Documentation

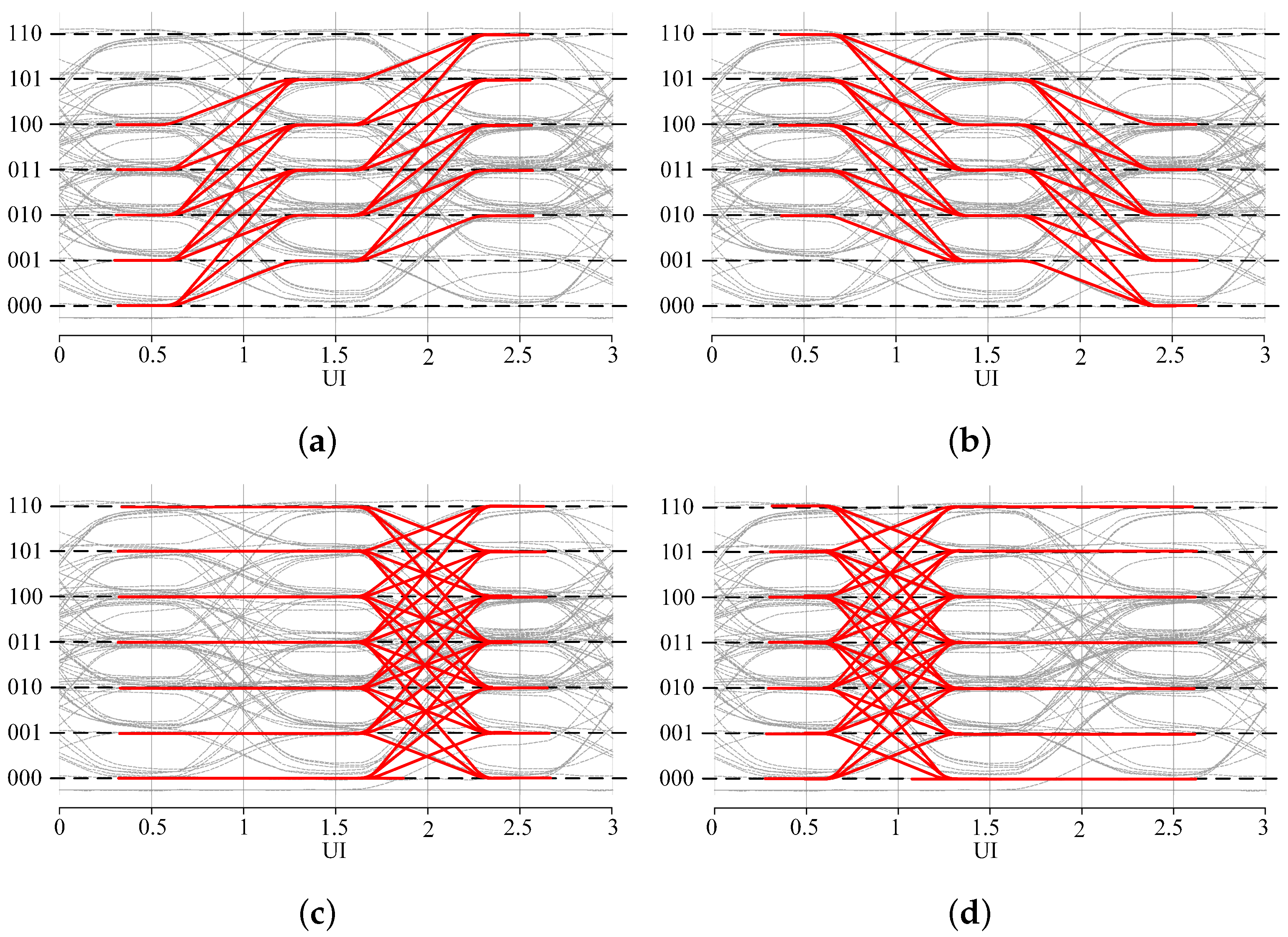

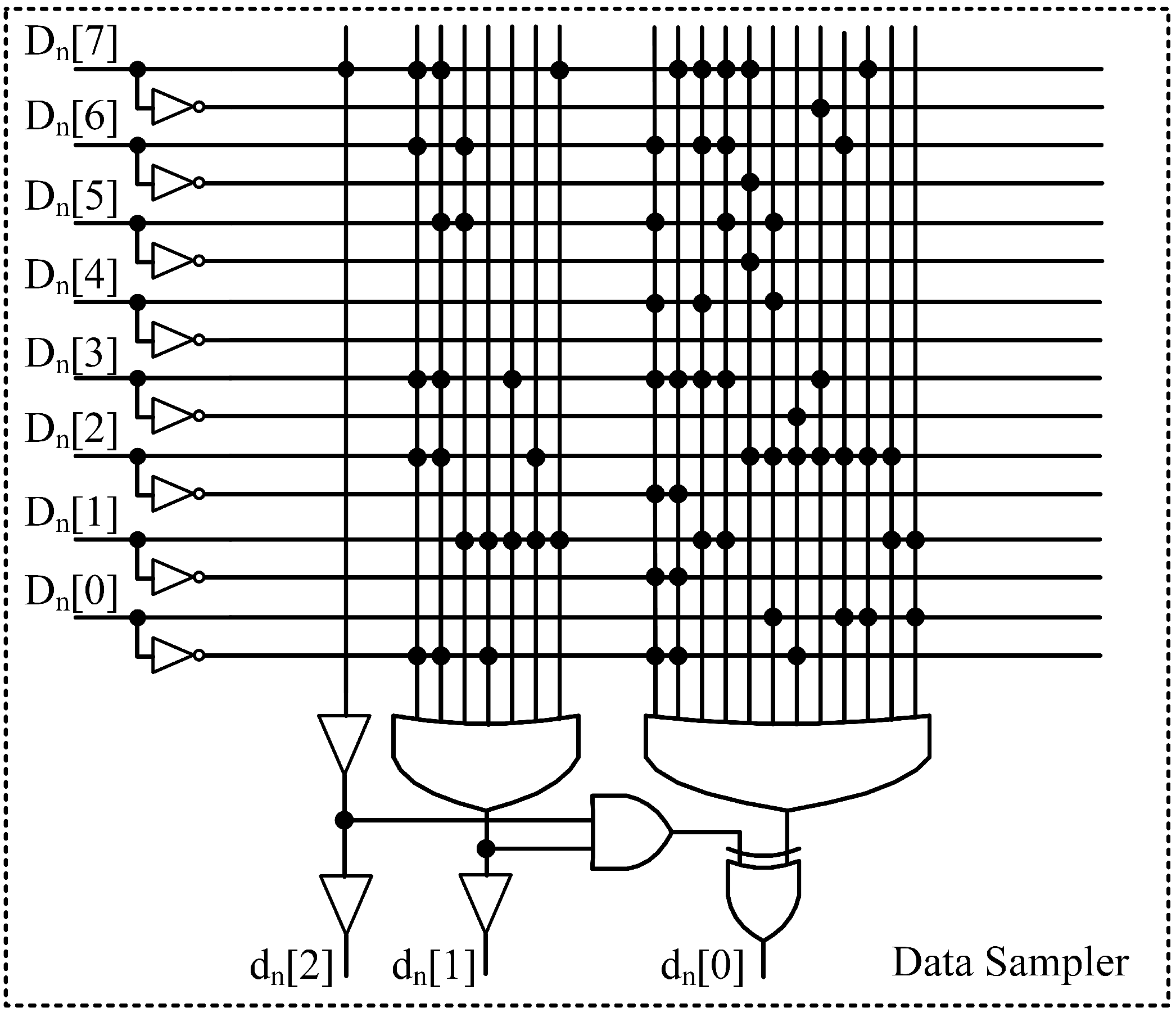

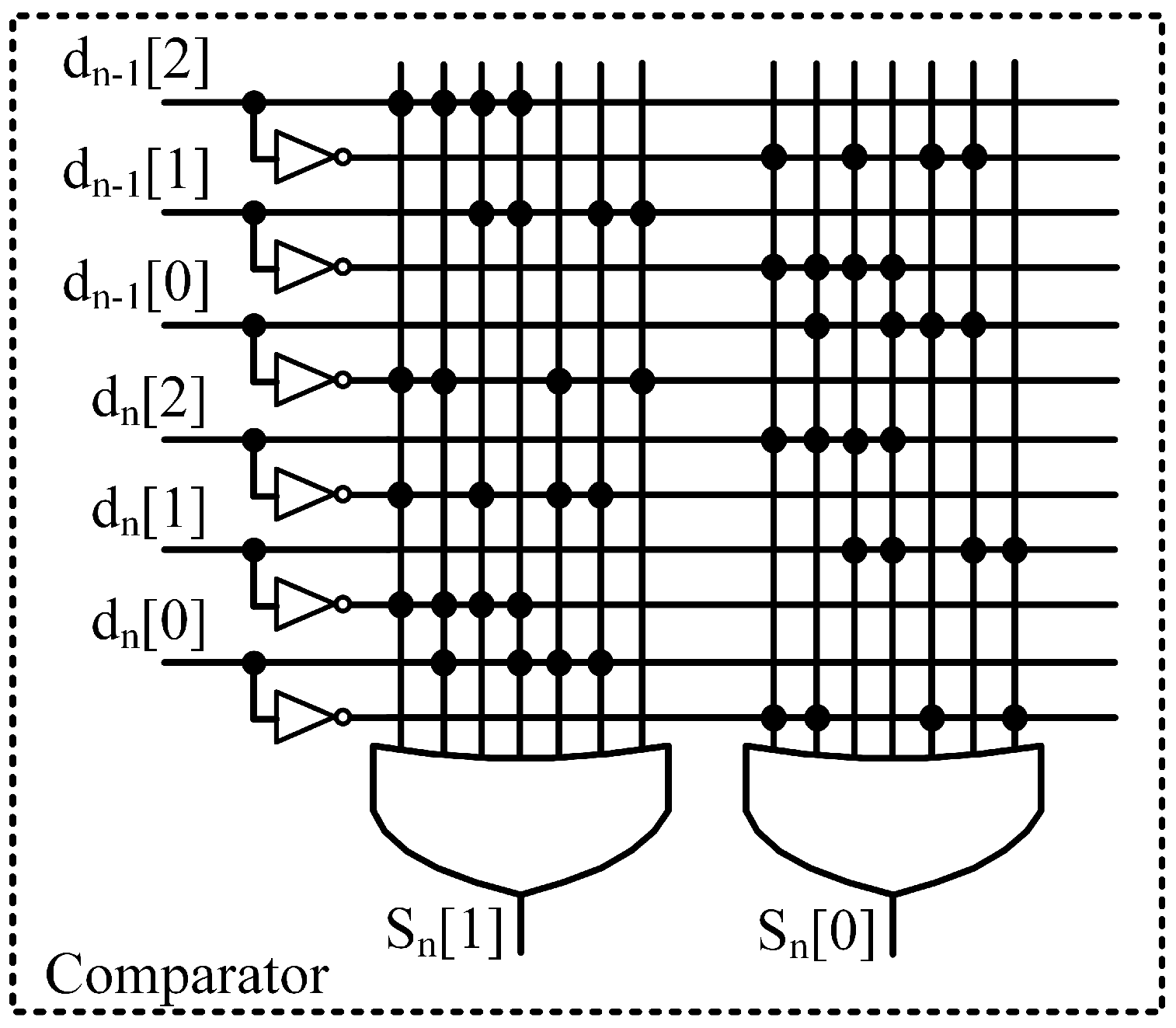

3. MMPD Design for DB PAM4

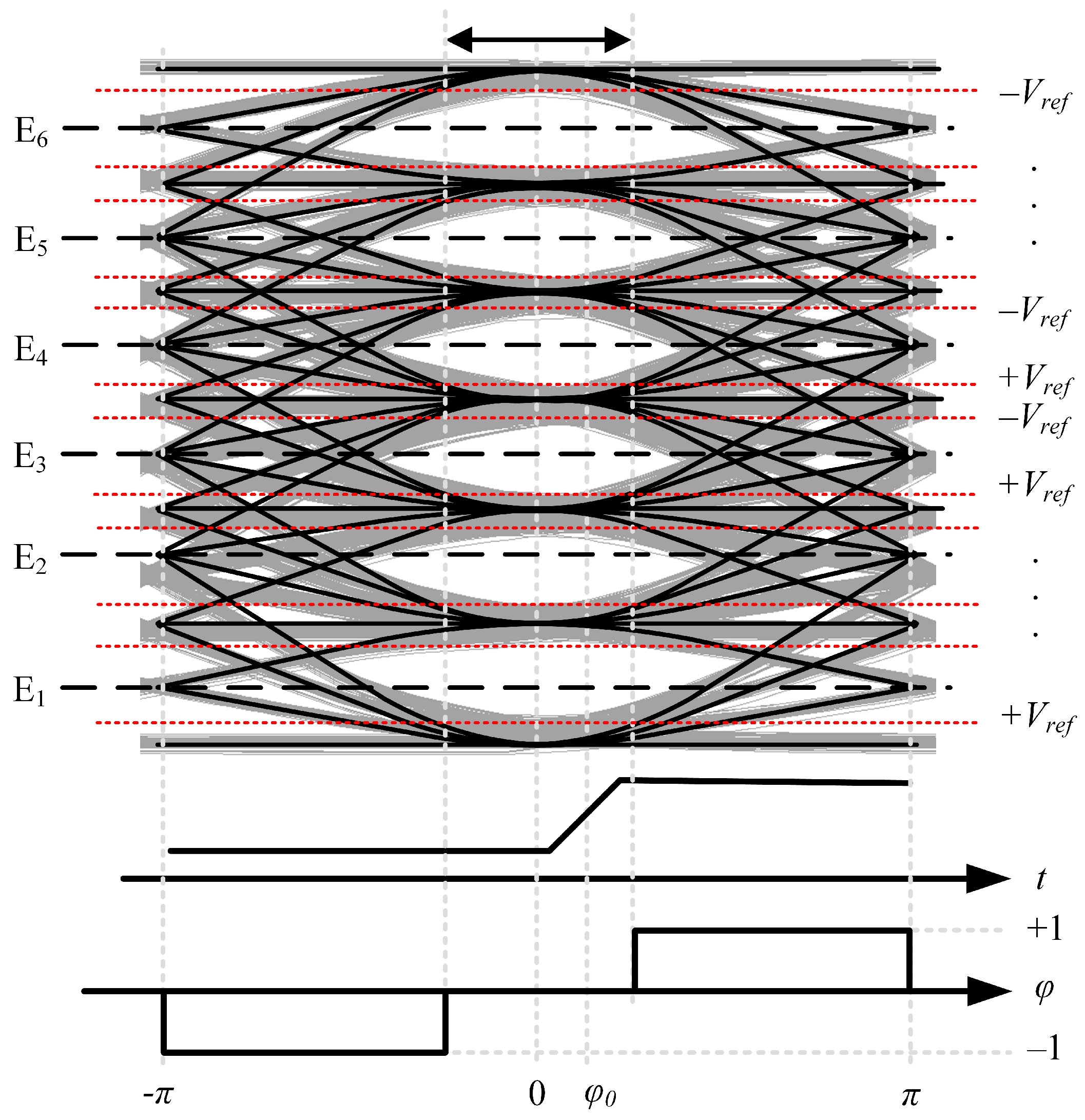

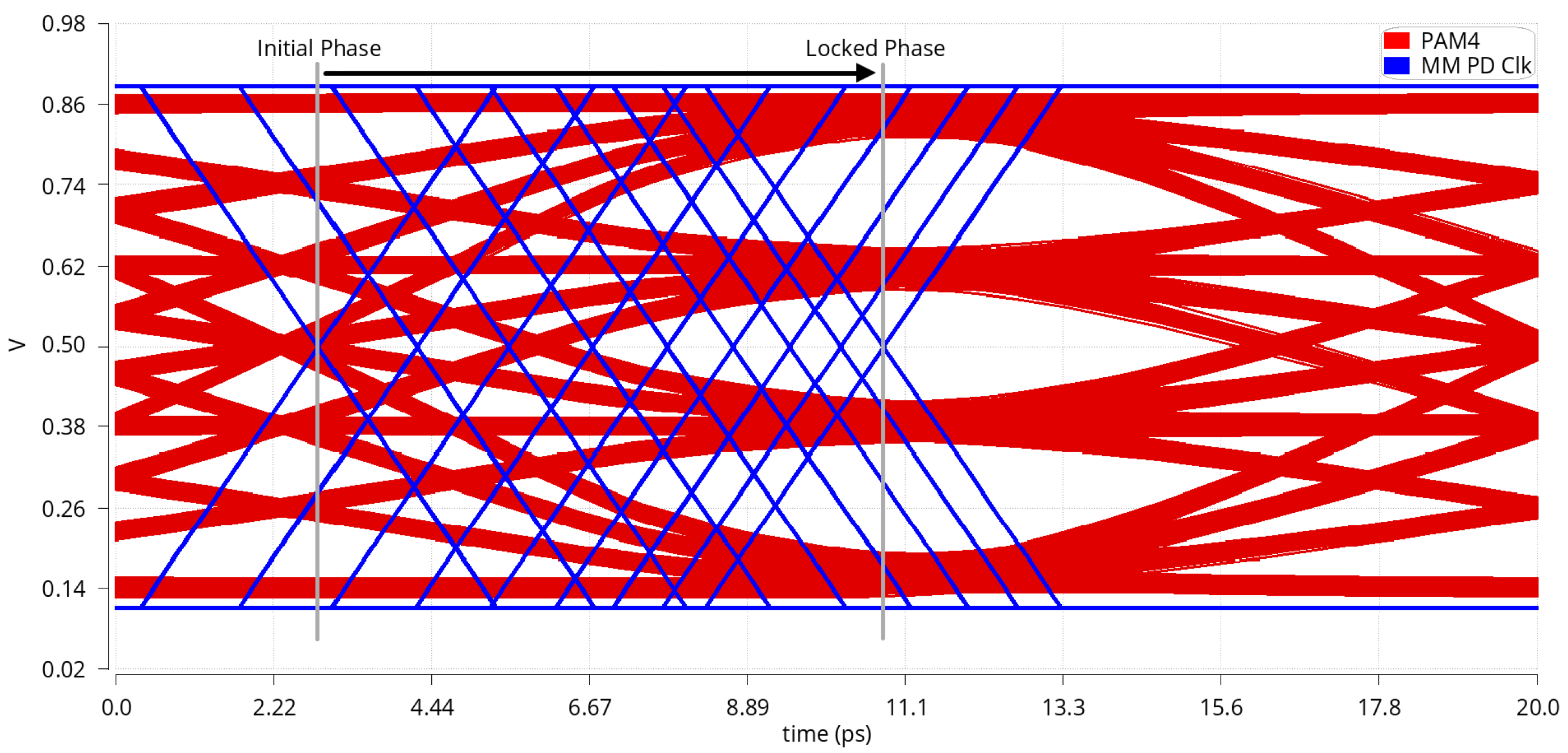

4. MMPD Performance Analysis

4.1. MMPD Phase-Detection Gain Analysis

4.2. High Phase Density Analysis in CDR Loop

5. Simulation Result

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tang, Z.; Lv, F.; Shi, J.; Zhang, J.; Wang, Z.; Li, P. 112 Gbps High-speed SerDes Transmitter Based on Duo-Binary Pam4 Encoding. In Proceedings of the 2021 6th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 22–24 October 2021; pp. 73–76. [Google Scholar]

- Qiang, Z.; Stojanovic, N.; Zuo, T.; Liang, Z.; Zhou, E. Single-lane 180 Gb/s SSB-duobinary-PAM-4 signal transmission over 13 km SSMF. In Proceedings of the Optical Fiber Communication Conference, Los Angeles, CA, USA, 19–23 March 2017; pp. 1–3. [Google Scholar]

- Li, J.; An, S.; Li, X.; Su, Y. Dual-SSB Modified Duobinary PAM4 Signal Transmission in a Direct Detection System without using Guard Band. In Proceedings of the 2020 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 8–12 March 2020; pp. 1–3. [Google Scholar]

- Saber, M.G.; Plant, D.V.; Gutierrez-Castrejon, R.; Alam, M.S.; Lessard, S. 100 Gb/s/λ Duo-Binary PAM-4 Transmission Using 25G Components Achieving 50 km Reach. IEEE Photonics Technol. Lett. 2020, 32, 138–141. [Google Scholar] [CrossRef]

- Lee, M.J.; Dally, W.J.; Poulton, J.; Greer, T.; Edmondson, J.; Farjad-Rad, R.; Ng, H.T.; Rathi, R.; Senthinathan, R. A second-order semi-digital clock recovery circuit based on injection locking. In Proceedings of the 2003 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; Volume 1, pp. 74–75. [Google Scholar]

- He, M.Y.; Poulton, J. A CMOS mixed-signal clock and data recovery circuit for OIF CEI-6G+ backplane transceiver. IEEE J. Solid-State Circuits 2006, 41, 597–606. [Google Scholar] [CrossRef]

- Sonntag, J.L.; Stonick, J. A digital clock and data recovery architecture for multi-gigabit/s binary links. IEEE J. Solid-State Circuits 2006, 41, 1867–1875. [Google Scholar] [CrossRef]

- Liu, T.; Li, T.; Lv, F.; Liang, B.; Zheng, X.; Wang, H.; Wu, M.; Lu, D.; Zhao, F. Analysis and Modeling of Mueller–Muller Clock and Data Recovery Circuits. Electronics 2021, 10, 1888. [Google Scholar] [CrossRef]

- Mueller, K.; Muller, M. Timing recovery in digital synchronous data receivers. IEEE Trans. Commun. 1976, 24, 516–531. [Google Scholar] [CrossRef]

- Sommer, N. Timing recovery of PAM signals using baud rate interpolation. In Proceedings of the 2004 11th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2004, Tel Aviv, Israel, 15 December 2004; pp. 350–353. [Google Scholar]

- Shi, L.; Gai, W.; Tang, L.; Xiang, X.; He, A. Hardware-efficient slope-error algorithm based PAM4 baud rate CDR scheme for 40 Gb/s receiver. Electron. Lett. 2018, 54, 1020–1022. [Google Scholar] [CrossRef]

- Peng, P.J.; Li, J.F.; Chen, L.Y.; Lee, J. 6.1 a 56Gb/s PAM-4/NRZ transceiver in 40nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 110–111. [Google Scholar]

- Lee, Y.S.; Chen, W.Z. A 20-Gb/s, 2.4 pJ/bit, Fully Integrated Optical Receiver with a Baud-Rate Clock and Data Recovery. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Musa, F.A.; Carusone, A.C. A baud-rate timing recovery scheme with a dual-function analog filter. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 1393–1397. [Google Scholar] [CrossRef]

- Im, J.; Zheng, K.; Chou, C.H.A.; Zhou, L.; Kim, J.W.; Chen, S.; Wang, Y.; Hung, H.W.; Tan, K.; Lin, W.; et al. A 112-Gb/s PAM-4 Long-Reach Wireline Transceiver Using a 36-Way Time-Interleaved SAR ADC and Inverter-Based RX Analog Front-End in 7-nm FinFET. IEEE J.-Solid State Circuits 2021, 56, 7–18. [Google Scholar] [CrossRef]

- Zhang, J.; Lv, F.; Pang, Z.; Shi, J.; Tang, Z.; Zhang, G. Low complexity Bang-Bang PD Design of 112Gb/s Duo-Binary PAM-4 CDR. In Proceedings of the 2021 6th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 22–24 October 2021; pp. 351–356. [Google Scholar]

| Classification | Relative Relation | Number | Probability |

|---|---|---|---|

| Up | D < D < D | 27 | 9/64 |

| Down | D > D > D | 27 | 9/64 |

| Keep-Jump | D = D ≠ D | 30 | 3/16 |

| Jump-Keep | D ≠ D = D | 30 | 3/16 |

| No-Decision | Other | 61 | 11/32 |

| Reference | Modulation | Mode | Classification Number | Phase-Detection Density |

|---|---|---|---|---|

| [8] | NRZ | MM | 3 | 1/2 |

| [11] | PAM-4 | MM | 3 | 7/16 |

| This paper | PAM-4 | MM | 5 | 1/2 |

| This paper | DB PAM-4 | MM | 5 | 21/32 |

| [16] | DB PAM-4 | BB | 4 | 1/4 |

| Mode | errdata | A | B | C |

|---|---|---|---|---|

| 000 | x | 0 | 0 | 0 |

| 001 | x | errdata | errlow | errup |

| 100 | x | errdata | errup | errlow |

| 011 | 0 | 1 | errdata | errdata |

| 011 | 1 | 1 | 0 | 1 |

| 110 | 0 | 1 | errdata | errdata |

| 110 | 1 | 1 | 1 | 0 |

| Mode | errdata | errdata | errup | errlow | errdata | Y | Y | Phase Info |

|---|---|---|---|---|---|---|---|---|

| 000 | x | x | x | x | x | 0 | 0 | No Info |

| 001 | x | 0 | 0 | 0 | x | 0 | 0 | No Info |

| 001 | x | 1 | 1 | 0 | x | 0 | 1 | LATE |

| 001 | x | 1 | 0 | 1 | x | 1 | 0 | EARLY |

| 100 | x | 0 | 0 | 0 | x | 0 | 0 | No Info |

| 100 | x | 1 | 1 | 0 | x | 0 | 1 | EARLY |

| 100 | x | 1 | 0 | 1 | x | 1 | 0 | LATE |

| 011 | x | 0 | 0 | 0 | 0 | 0 | 0 | No Info |

| 011 | x | 0 | 0 | 0 | 1 | 1 | 0 | EARLY |

| 011 | x | 1 | x | x | x | 0 | 1 | LATE |

| 110 | 0 | 0 | 0 | 0 | x | 0 | 0 | No Info |

| 110 | 1 | 0 | 0 | 0 | x | 0 | 1 | LATE |

| 110 | x | 1 | x | x | x | 1 | 0 | EARLY |

| Parameter | Value ( = 0.09 UI, = 0.09 UI) |

|---|---|

| TD | 21/32 |

| KxTD/64 | 4.21(uiform), 3.64(Gaussian), 1.64(sinusoidal) |

| K | 1 + 2 |

| K | 1/128 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, J.; Lv, F.; Shi, J.; Tang, Z.; Lv, D. A High Phase Detection Density and Low Space Complexity Mueller-Muller Phase Detector for DB PAM-4 Wireline Receiver. Electronics 2022, 11, 3246. https://doi.org/10.3390/electronics11193246

Zhang J, Lv F, Shi J, Tang Z, Lv D. A High Phase Detection Density and Low Space Complexity Mueller-Muller Phase Detector for DB PAM-4 Wireline Receiver. Electronics. 2022; 11(19):3246. https://doi.org/10.3390/electronics11193246

Chicago/Turabian StyleZhang, Jinwang, Fangxu Lv, Jianjun Shi, Zixiang Tang, and Dongbin Lv. 2022. "A High Phase Detection Density and Low Space Complexity Mueller-Muller Phase Detector for DB PAM-4 Wireline Receiver" Electronics 11, no. 19: 3246. https://doi.org/10.3390/electronics11193246

APA StyleZhang, J., Lv, F., Shi, J., Tang, Z., & Lv, D. (2022). A High Phase Detection Density and Low Space Complexity Mueller-Muller Phase Detector for DB PAM-4 Wireline Receiver. Electronics, 11(19), 3246. https://doi.org/10.3390/electronics11193246