Abstract

In this paper, we propose a finite alphabet iterative decoder (FAID) named rate-compatible mutual-information-maximizing quantized shuffled min-sum (RC-MIM-QSMS) decoder, for decoding quasi-cyclic low-density parity-check (QC-LDPC) codes with various code rates. Our proposed decoder exchanges the coarsely quantized messages represented by symbols from finite alphabets and adopts single-input lookup tables (LUTs) to implement the node updates. To construct the LUTs used for decoding, we first propose a modified density evolution by considering the shuffled schedule to generate the LUTs which vary with different layers and iterations. Furthermore, to reduce the memory requirement for storing the LUTs, we optimize the constructed LUTs into a unique set of LUTs that only change with different decoding iterations. To the best of our knowledge, the RC-MIM-QSMS decoder is the first one to integrate the rate compatibility of LDPC codes with the shuffled decoding schedule. Simulation results show that the proposed RC-MIM-QSMS decoder outperforms the floating-point shuffled belief propagation decoder in the high signal-to-noise region and achieves comparable convergence speed to other state-of-the-art FAIDs. Moreover, the RC-MIM-QSMS decoder is able to save up to memory requirement compared to the benchmark MIM-FAIDs.

1. Introduction

Low-density parity-check (LDPC) codes [1] have been widely applied to diverse applications, such as wireless communication and data storage systems [2,3], due to their capability of approaching the capacity under iterative message passing decoding [4]. Many researchers have devoted to developing efficient LDPC decoders [5,6,7] to achieve a trade-off between the error rate performance and decoding complexity.

Recently, a class of finite alphabet iterative decoders (FAIDs) [8,9,10,11,12,13,14,15,16] have drawn much attention due to their excellent performance by using coarsely quantized messages. Due to the use of messages quantized by a low bit width, these FAIDs also achieve a low decoding complexity and are in favor of services and applications such as the Internet of things [17] and wireless sensor networks [18,19,20], which require strict power constraint for the devices. Different from the conventional LDPC decoders such as [5], these FAIDs exchange the messages represented by symbols from finite alphabets between the variable nodes (VNs) and the check nodes (CNs). Moreover, they utilize lookup tables (LUTs) with single input to carry out the node updates. These LUTs are carefully designed based on the density evolution (DE) [4] with a selected coarse quantization scheme, which aims to maximize the mutual information (MI) between the coded bits and the exchanged messages within the decoders. We hereby call this type of FAIDs the mutual-information-maximizing FAIDs (MIM-FAIDs). More specifically, the MIM-FAIDs [8,9,10,12,14,15] implement the coarse quantization scheme by dynamic programming (DP) [21], which has been proved to be optimal with respect to maximizing MI. In [11,13], the LUTs of the MIM-FAIDs are designed based on the information bottleneck (IB) method, which makes use of machine learning rather than DP in the design process. Furthermore, the MIM-FAID proposed in [16] constructs the LUTs by using a hierarchical dynamic quantization which is a greedy quantization scheme similar to the IB method and requires less computational complexity compared to DP. In addition, there are two different node updating architectures considered by the above MIM-FAIDs. One is designing multiple sets of concatenated two-input LUTs for decoding, e.g., [8,11,12], where each set of LUTs is dedicated to updating the nodes of a specific degree at each iteration. However, the concatenated LUTs only focus on maximizing MI between two consecutive tables after quantization and hence lead to a loss of MI, which may deteriorate the decoder performance. Moreover, the memory requirement for storing the LUTs may be intolerable because the number of LUTs increases significantly when the node degree or the decoding iteration becomes large. To reduce the memory demand and preserve more MI after quantization, the MIM-FAIDs were proposed in [9,10,14,15,16], which performed the node updates following a reconstruction–calculation–quantization architecture. Specifically, the FAID in [16] utilizes real additions and multiple sets of single-input LUTs with real-valued entries to update all nodes of different degrees. The mutual-information-maximizing (MIM) quantized decoders in [9,10,14,15] adopt integer additions and the LUTs of integer entries for practical consideration.

To accelerate the convergence speed, some MIM-FAIDs, i.e., [13,15,16], further consider either a layered schedule [22] or a shuffled schedule [23]. For example, the layered MIM-FAID [13] is designed by the IB method for decoding the regular LDPC codes. The LUTs of the FAID in [16] are constructed based on the layered schedule with a high-precision uniform channel quantizer. The MIM quantized shuffled min-sum (MIM-QSMS) decoder was proposed in [15], which designs the LUTs by considering the shuffled decoding schedule. All of these MIM-FAIDs with different decoding schedules, e.g., [15,16], are designed for a particular LDPC code with a fixed code rate, which cannot be used to decode LDPC codes with different code rates. However, the rate-compatible quasi-cyclic LDPC (RC-QC-LDPC) codes are preferred in many practical applications such as data storage systems [24,25]. An LDPC decoder that fails to support rate compatibility may incur a high complexity for hardware implementations. Although the rate-compatible MIM-FAIDs were investigated in [11,14], they were only designed based on the flooding schedule [26]. Therefore, how to design the MIM-FAID with a layered/shuffled schedule for LDPC codes with different code rates is still a challenging problem.

In this paper, we develop an MIM-QSMS decoder for decoding RC-QC-LDPC codes, which is referred to as the rate-compatible MIM-QSMS (RC-MIM-QSMS) decoder. Compared to other MIM-FAIDs in the literature, our proposed RC-MIM-QSMS decoder integrates the shuffled decoding schedule and the rate compatibility in a single round of the LUT design process. To the best of our knowledge, this is the first design for the FAID to support the rate compatibility with a shuffled schedule. In particular, we modify the DE in [15] and propose the shuffled MIM-DE (SMIM-DE) by considering the weighted expectation of the probability mass functions (pmfs) and the joint degree distributions. Based on the SMIM-DE, we are able to construct LUTs that vary with different layers and iterations for decoding RC-QC-LDPC codes. Moreover, an LUT optimization method is further proposed to generate a unique set of LUTs that only vary with decoding iterations. In this way, the memory requirement for storing the LUTs can be significantly reduced. We conduct a comprehensive evaluation on the proposed RC-MIM-QSMS decoder in terms of the error rate performance, the convergence speed, and the memory requirement for decoding. We demonstrate that the proposed RC-MIM-QSMS decoder surpasses the floating-point shuffled belief propagation (SBP) decoder [23] in the high signal-to-noise (SNR) region and has comparable convergence speed to other state-of-the-art MIM-FAIDs. More importantly, the RC-MIM-QSMS decoder can save up to memory requirement compared to the benchmark MIM-FAIDs.

The rest of this paper is organized as follows. Section 2 provides the preliminaries of this work including the notations, the QC-LDPC codes, the shuffled min-sum (SMS) decoder [27], and the decoding framework of the MIM-QSMS decoder [15]. The proposed SMIM-DE and the LUT optimization method for designing the RC-MIM-QSMS decoder are illustrated in Section 4. In Section 5, we evaluate the proposed RC-MIM-QSMS decoder from the aspects of the error rate performance, the convergence speed, and the memory usage for implementing decoding. Section 6 concludes this paper.

2. Preliminaries

2.1. Notations

In this paper, calligraphy capitals denote alphabet sets. Normal capitals denote the random variables. Lower-case letters denote the realization of a random variable. Boldface letters are used to define a vector or matrix.

2.2. QC-LDPC Codes

QC-LDPC codes belong to a class of structured LDPC codes which can be represented by an base matrix . Each element in corresponds to a circulant permutation matrix [28] of size such that we use integers between 0 and to specify the position of the one-entry in the first row of the circulant and use ∞ to represent an all-zero matrix. Let be the parity-check matrix (PCM) of a QC-LDPC code. Accordingly, there are rows and columns in .

2.3. The SMS Decoder

Consider the Tanner graph [29] representation of the PCM for a QC-LDPC code. For any positive integer , we define the set . For and , we denote the nth variable node (VN) and the mth check node (CN) in the Tanner graph by and , respectively. Note that and are known as neighbors and connected to each other if there is a one-entry in the mth row and nth column of . Define the index sets of neighboring nodes of and by and , respectively. For a set and an element , we denote the set with index a excluded by .

The shuffled decoding schedule was first proposed in [23] for the belief propagation (BP) algorithm to reduce the loading latency of the exchanged messages. For practical concerns, we focus on the low-complexity SMS decoder [27] and briefly introduce the details as follows. Denote the check-to-variable (C2V) message sent from to at the tth iteration by , and denote the variable-to-check (V2C) message sent from to by . Here, , where is a maximum preset number of iterations. Define as the channel output of the node . At each iteration, the SMS decoder updates the exchanged (C2V/V2C) messages by

where is the normalized factor and is the indicator function operating as

Note that for , we have . Denote a posterior message of the node by , which can be computed at the end of each iteration by

In practice, the shuffled decoding schedule is generally conducted by partitioning the PCM into groups, so-called the layers, where each layer consists of Z VNs and corresponds to a QC column block of . Note that we consider that any two columns in each layer have at most a one-entry in the same row. Therefore, the layer j of is equivalent to the jth column of the base matrix . Within a layer, the SMS decoder updates the exchanged messages in parallel and the decoding process proceeds in serial among consecutive layers.

3. The Related Work: Decoding Framework of an MIM-QSMS Decoder

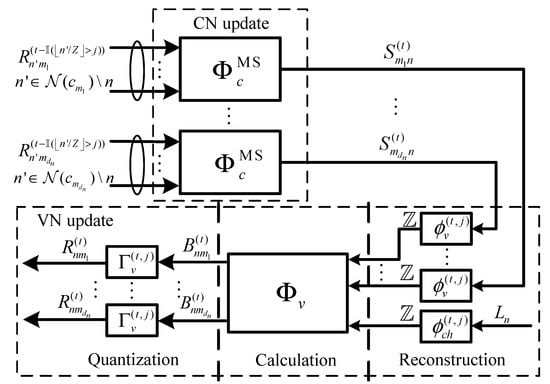

The MIM-QSMS decoder [15] is one type of FAIDs that exchange the messages represented by symbols from finite alphabets within the decoder. The precision of the MIM-QSMS decoder is predetermined according to system constraints, which can be represented by the tuple (, ). More specifically, is the bit width of the exchanged messages and refers to the bit width of the a posteriori message. Figure 1 demonstrates the decoding framework of a (, ) MIM-QSMS decoder with respect to the node of degree at the tth iteration. Suppose that the MIM-QSMS decoder proceeds based on the base matrix as described in Section 2.3. Therefore, we have and .

Figure 1.

The decoding architecture of the layer-specific MIM-QSMS decoder [15].

- CN update: The MIM-QSMS decoder adopts the min operation [15] for the CN update, where we denote the CN update function by . Assume that for all are the V2C message symbols received at a neighboring node connecting to the node . Let be a function mapping the V2C message symbols to integers , respectively. At the tth iteration, the C2V message symbol is computed bywhere is the inverse function of .

- VN update: The VN update of the MIM-QSMS decoder computes the V2C messages for all , which contains three steps, i.e., reconstruction, calculation, and quantization. We denote the quantized channel output of the node by . Denote the C2V message coming from the node to the node by . During the VN update, the quantized channel output and all C2V messages are firstly mapped to the computational messages based on reconstruction LUTs and , respectively. The computational messages are essentially the integers of bit width much larger than . Following that, the VN update function is adopted in the calculation step to compute the V2C computational messages, denoted by , asFinally, each V2C computational message is quantized into a V2C message in by a quantization LUT, denoted by . Note that the reconstruction LUTs and quantization LUTs of the MIM-QSMS decoder in [15] originally vary with decoding iterations and layers. Here, we omitted the associated iteration and layer of the LUTs in (6) for simplicity.

Based on the decoding architecture in Figure 1, the main idea of designing the MIM-QSMS decoder in [15] is to construct the LUTs by tracking the probability mass functions (pmfs) of exchanged messages via DE [4]. To be more specific, the reconstruction LUTs are generated by scaling the LLR values associated with each message symbol in and , respectively. The quantization LUTs are designed to be an optimal sequential deterministic quantizer (SDQ) by using dynamic programming (DP) [21].

4. Design of MIM-QSMS Decoder for RC-QC-LDPC Codes

The MIM-QSMS decoder in [15] is designed for an LDPC code with a fixed code rate, where we refer to this type of decoder as the rate-dependent MIM-QSMS (RD-MIM-QSMS) decoder. Obviously, decoding LDPC codes with various code rates using the RD-MIM-QSMS decoder requires different sets of LUTs corresponding to each code rate. Thus, it not only requires multiple rounds of design process to construct the LUTs but also a large amount of memory usage for hardware implementation. Although constructing LUTs used for decoding RC-QC-LDPC codes has been proposed in [11,14], these methods only focus on the flooding schedule and cannot be directly applied to a shuffled decoder. This is because the updating order of the exchanged messages in a shuffled decoder is different from that in a decoder with a flooding schedule. Motivated by the above observations, in this section, we propose a design method of the RC-MIM-QSMS decoder, which is capable of decoding RC-QC-LDPC codes based on only one set of LUTs with much less memory requirement.

4.1. Proposed SMIM-DE

In [14], the joint edge-degree distributions were considered by the DE in the LUT design process to support rate compatibility. Inspired by this, we propose a SMIM-DE to construct the LUTs of the RC-MIM-QSMS decoder, which is modified from the DE in [14] and considers both the joint edge-degree distributions and the shuffled decoding schedule. Let and be the sets of CN and VN degrees for K target LDPC codes, respectively.

Then,

where and represent the sets of the CN and VN degrees of the kth target LDPC code, respectively. The joint edge-degree distributions can be given by [14]

where and are the fractions of edges connected to the CNs of degree d and the VNs of degree d, respectively, in the Tanner graphs of all K target LDPC codes. Similar to the MIM-QSMS decoder described in Section 3, we consider the LUT design to be processed on the base matrices of the target LDPC codes. For the kth target LDPC code, we assume its base matrix has columns, which correspond to layers for the shuffled schedule. Define as the maximum number of layers for K target LDPC codes. Let be the random variable for the coded bit. For a random variable A taking values from , we denote as the pmf of conditioned on . We also define the random variable for the channel output by , and the random variable for the V2C (respectively, C2V) message by (respectively, ). For convenience, we use the superscript () to represent a pmf computed at the jth layer and tth iteration, where and . The SMIM-DE is illustrated as follows.

4.1.1. Channel Quantization

As shown in the literature, e.g., [9,11,12,16], the design of the FAIDs is conducted under a discrete additive white Gaussian noise (AWGN) channel with a properly selected noise standard deviation. Therefore, we first present the channel quantization considered by the SMIM-DE, which is used to discretize a continuous AWGN channel at the beginning of the design process. Assume that X is modulated by binary phase-shift keying (BPSK). Given a preset bit width , we first uniformly quantize the AWGN channel into a discrete memoryless channel with Y outputs, where , and we set in this paper. Then, we adopt DP to find an optimal SDQ [21] for a -bit channel output, which aims to maximize the mutual information between X and L. In this way, we can obtain the conditional pmf and the corresponding quantization LUT of the SDQ, denoted by . The constructed quantization LUT is essentially a threshold set with , which operates as

Based on and , we next discuss the node updates of the SMIM-DE.

4.1.2. CN Update

In [15], we assume that the V2C messages sent to the CNs located in the same layer have equal contributions so that we consider their expected pmfs for the CN update. However, this is not the case in designing the RC-MIM-QSMS decoder because the CNs at the same layer are supposed to receive the V2C messages not only from different layers but also from different target LDPC codes when using the joint edge-degree distributions. Since the number of layers may be different for each target LDPC code, we consider the weighted expectation of the V2C message pmfs in the proposed SMIM-DE by introducing a parameter called the weight coefficient. Define of size as the layered indicator of the kth target LDPC code. Each entry for is of binary values such that

where the value 1 means that the corresponding layer exists for the kth target LDPC code. At the jth layer, we define the weight coefficient of the V2C message pmfs as

At the tth iteration, a CN of degree d () in layer j receives the V2C messages that were updated at iteration from layers and have been updated at iteration t from layers . Therefore, the expected pmf of the V2C message received at layer j can be expressed as

Note that we have for . Define the vector of V2C messages received at a degree-d () CN by , where is a realization of . Denote as the vector of coded bits associated to its neighboring VNs. With the independent and identical distribution (i.i.d.) assumption [4], the joint pmf at layer j and iteration t is given by

where is a realization of X, and means the checksum of the CN is satisfied. For each received realization , the CN update function computes the corresponding output s as in (5). By considering the fraction in (8), the conditional pmf of the C2V message at layer j and iteration t can be obtained by

Note that the computation of (14) can be conducted recursively such as in [4,16] to achieve low complexity, which is not a big issue for an off-line process.

4.1.3. VN Update

For the VN update, the SMIM-DE calculates the conditional pmf for layer j at the tth iteration following the reconstruction, calculation, and quantization steps. Based on the conditional pmfs and , we denote for , and for , respectively. Inspired by [15], the reconstruction LUTs associated to a degree-d () VN at layer j and iteration t can be generated by

where returns the closest integer to x, and is the scaling factor, i.e.,

to allow the maximum number of bit width for the VN update. Assume that the C2V messages sent to the VNs in the same layer are i.i.d. We denote the vector of the C2V messages and the channel output received at a degree-d VN by , where and is a realization of and L, respectively. The joint pmf at layer j and iteration t can be computed by

Define as the alphabet set of the V2C computational message calculated at layer j and iteration t for the VN update, where is the random variable for the V2C computational message. After reconstruction, the VN update function computes the realization b of B based on each input to form the alphabet set . According to the fraction given by (8), the conditional pmf of the V2C computational message is represented by

4.2. LUT Optimization

The SMIM-DE described above tracks the evolution of and at each layer and each iteration to construct the LUTs varying with different layers and iterations for decoding. For a predetermined maximum number of decoding iterations and layers of the target LDPC codes, the memory requirement for storing the LUTs constructed in this way grows linearly with , which increases significantly in particular for the target LDPC codes with large . Thus, it is necessary to optimize the SMIM-DE to generate LUTs with less memory demand for hardware implementation. To this end, we propose an optimization method for the RC-MIM-QSMS decoder in a postprocessing manner to design the LUTs that only vary with decoding iterations, which we refer to as the iteration-specific LUTs in the rest of this paper. In particular, we first conduct the SMIM-DE at each iteration to obtain the conditional pmfs for all layers. Similar to the case of the CN update, we assume that the C2V messages sent to a VN at the tth iteration are from layers of all target LDPC codes. Thus, we combine the conditional pmfs from layers into the iteration-specific pmf by considering the weighted expectation of the C2V message pmfs at the tth iteration such that

The iteration-specific reconstruction LUTs and can be constructed by replacing in (15) and (16) with . The quantization LUT for each iteration can also be obtained following (17)–(19). With these iteration-specific LUTs, the conditional pmf requires to be further updated by the SMIM-DE for designing the LUTs at the next iteration. The LUT optimization repeats at each iteration until the preset maximum number of iterations is reached.

To summarize, we present the design flow of the RC-MIM-QSMS decoder with the LUT optimization in Algorithm 1. Note that by adopting the LUT optimization, the RC-MIM-QSMS decoder requires only four LUTs per iteration, which consists of two reconstruction LUTs ( and ) and two quantization LUTs ( and ). For the decoding process, all the LUTs are fixed for different received signal-to-noise ratios (SNRs). Furthermore, is fixed for all iterations while the other LUTs may vary with different iterations.

| Algorithm 1 The Design Flow of MIM-QSMS Decoder with LUT Optimization |

|

4.3. Remarks

Denote the noise standard deviation of the selected AWGN channel to design the RC-MIM-QSMS decoder as . Given the tuple , the degree distributions , and the maximum number of iterations , different choices of result in different sets of reconstruction and quantization LUTs. Compared to the conventional DE [4] that focuses on the decoding error probability, the design of the RC-MIM-QSMS decoder is similar to that of other MIM-FAIDs, e.g., [12,15,16], which aim to achieve a certain MI value approaching 1 for the a posteriori messages. Let be the optimal noise standard deviation for designing the RC-MIM-QSMS decoder, which is determined by following the steps below. Denote the alphabet set of a posteriori messages by , where is the random variable for a posterior message. With the iteration-specific reconstruction LUTs and the conditional pmf given by (20), we first obtain from (6) and compute the conditional pmf based on (18) by considering . Define as the hard decision of Q, which takes values from . We select equal to the maximum that achieves a mutual information between X and greater than after iterations, i.e.,

As shown in the literature [12,15,16], we set in this paper for achieving a desirable error rate performance across a wide range of SNRs. We note that the proposed RC-MIM-QSMS decoder directly determines the coded bits at each iteration according to rather than using the quantization LUT for bit decision as in [14,15]. This is more efficient for hardware implementation compared to the RD-MIM-QSMS decoder [15] and the MIM-FAID [14].

In addition, we also notice that it is possible for the RC-MIM-QSMS decoder to cause a performance degradation compared to the RD-MIM-QSMS decoders since the joint degree distributions considered in the LUT design are mismatched with the specific degree distributions of any target LDPC codes. However, the performance loss can be limited within a certain range by selecting appropriate target LDPC codes for rate-compatible design. Intuitively, for preset bit widths (, ) and the maximum number of iterations , the target LDPC codes that have the design noise standard deviations close to each other are preferable to be optimized jointly. This is because the MI values of these target LDPC codes are likely to approach 1 after iterations. To verify this hypothesis, we quantify for a given code rate by the corresponding design SNR, which is denoted as

Based on extensive simulation results, we let any two target LDPC codes have different values of within dB for achieving a desirable error rate performance. As we can see in the later simulations, this criterion leads to the RC-MIM-QSMS decoders operating on three different code rates for the length-1296 IEEE 802.11n LDPC codes [30] and the fifth-generation (5G) LDPC codes [31].

5. Simulation Results and Discussion

In this section, we evaluate the performance of the proposed RC-MIM-QSMS decoder with respect to the frame error rate, the convergence speed, and the memory requirement via Monte-Carlo simulations. Moreover, we also include the performance of the floating-point SBP decoder [23], the conventional QSMS decoder [27], the rate-compatible FAID (RC-FAID) decoder with flooding schedule [11], the rate-compatible MIM quantized min-sum (RC-MIM-QMS) decoder [14], and the RD-MIM-QSMS decoder [15] for comparison. We denote the bit width settings of the exchanged messages () and the a posteriori message () of different LDPC decoders by (, ), and the floating-point precision is represented by “∞”.

We adopted a BPSK modulation and assumed the LDPC codewords were transmitted over the AWGN channels. We considered two types of LDPC codes which have moderate and short block lengths, respectively. One was the length-1296 LDPC codes adopted in the IEEE 802.11n standard [30] with code rates , , and , respectively. Another was the 5G LDPC codes constructed from a base graph one with lifting size 26 with code rates , , and after rate matching [31]. Table 1 and Table 2 show the degree distributions of the simulated codes and the design noise standard deviation () for the associated MIM-QSMS decoder, respectively. Note that we designed the RC-FAID decoder based on DP [21] rather than the information bottleneck method [11] because DP proved to be optimal for maximizing MI. At least 300 error frames were collected at each simulated SNR. In addition, we set for the conventional QSMS decoder and for all decoders.

Table 1.

Degree Distributions of the IEEE 802.11n LDPC Codes and the 5G LDPC Codes.

Table 2.

Design Noise Standard Deviations for the RC-MIM-QSMS and RD-MIM-QSMS Decoders.

5.1. FER Performance

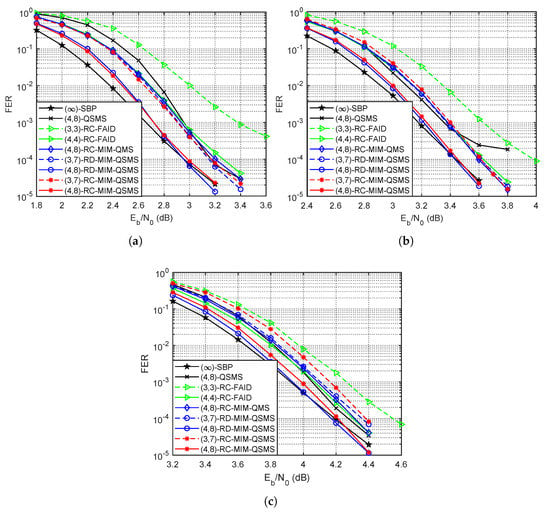

Figure 2 shows the FER performance of different decoders for the length-1296 IEEE 802.11n LDPC codes with code rates , , and . We can see that the proposed RC-MIM-QSMS decoder achieves almost the same FER compared to its rate-dependent counterparts for the same bit width settings and the same LDPC codes. Moreover, the ()-RC-MIM-QSMS decoder can outperform the ()-QSMS decoder by at least dB and approaches the performance of the (∞)-SBP decoder within dB. In addition, the ()-RC-MIM-QSMS decoder also surpasses both the RC-MIM-QMS decoder and the RC-FAID decoder with the same bit width settings at most dB for all simulated codes. With the () bit width settings, the RC-MIM-QSMS decoder has an FER performance close to the ()-QSMS decoder for code rate and even outperforms the ()-QSMS decoder for code rates and . Compared to the ()-RC-FAID decoder, the ()-RC-MIM-QSMS decoder achieves a performance gain of at least dB for all code rates.

Figure 2.

The FER performance of different decoders for the length-1296 IEEE 802.11n LDPC codes with code rates , , and . (a) . (b) . (c) .

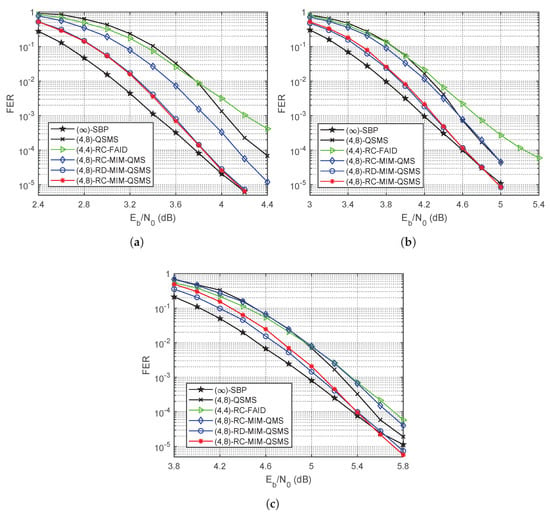

Figure 3 depicts the FER performance of different decoders for the 5G LDPC codes with lifting size 26 and code rates , , and . As shown by the figure, the proposed ()-RC-MIM-QSMS decoder achieves almost the same FER compared to its rate-dependent counterparts for the same simulated code rates. Furthermore, the ()-RC-MIM-QSMS decoder performs better than the ()-QSMS decoder by up to dB and approaches the performance of the (∞)-SBP decoder within dB. With the () bit width settings, the proposed RC-MIM-QSMS decoder also outperforms both the RC-MIM-QMS decoder and the RC-FAID decoder by at least dB for all simulated code rates.

Figure 3.

The FER performance of different decoders for the 5G LDPC codes with lifting size 26 and code rates , , and . (a) . (b) . (c) .

In the high SNR region, the proposed RC-MIM-QSMS decoder even shows slightly better error floor performance compared to the (∞)-SBP decoder for both the 802.11n LDPC codes and the 5G LDPC code. This is because there are degree-two VNs in the Tanner graphs of the simulated codes, which results in trapping sets due to the cycles being confined among these degree-two VNs [32]. These trapping sets become the most harmful objects and cause error floor in the high SNR region for the BP decoder. Similar phenomena are also observed in the literature [8,10,14,15,16], which show that the MIM quantization schemes can assist to mitigate the negative impact of certain harmful objects in the code structure.

5.2. Convergence Speed Analysis

Apart from the FER performance, the convergence speed is another critical factor to assess the decoding latency. Define the average number of iterations required for decoding one codeword as . In Table 3, we compared the convergence speed of different quantized decoders with for the 802.11n LDPC codes in perspective of . It can be seen that the proposed RC-MIM-QSMS decoder outperforms both the RC-FAID decoder and the RC-MIM-QMS decoder for all simulated code rates by reducing up to . The RC-MIM-QSMS decoder also achieves up to less than the conventional QSMS decoder in the low-to-moderate SNR region. We observe that of the proposed RC-MIM-QSMS decoder is up to less than the RD-MIM-QSMS decoder for the rate- 802.11n LDPC code, and it slightly increases compared to the RD-MIM-QSMS decoder for the simulated LDPC codes with code rates and . This is because the proposed RC-MIM-QSMS decoder is designed based on the joint degree distributions, which considers a larger portion of high-degree VNs with respect to the individual degree distributions of the rate- 802.11n LDPC code. However, compared to the individual degree distributions of both rate- and rate- 802.11n LDPC codes, there are a large portion of low-degree VNs considered by the joint degree distributions. The high-degree VNs lead to a faster convergence speed and the low-degree VNs have a slower convergence speed. Therefore, the proposed RC-MIM-QSMS decoder requires less for lower code rates and more for higher code rates compared to its rate-dependent counterparts.

Table 3.

The average number of iterations of different LDPC decoders with for the 802.11n LDPC codes.

Table 4 demonstrates the of different quantized decoders with for the 5G LDPC codes. We can see that the proposed RC-MIM-QSMS decoder achieves less for all simulated code rates by at least in the moderate-to-high SNR region. Compared to the conventional QSMS decoder, the RC-MIM-QSMS decoder can reduce by up to for the rate- 5G LDPC code. Similar to the case of the 802.11n LDPC codes, we also observe the phenomenon that of the proposed RC-MIM-QSMS decoder has a minor reduction compared to the RD-MIM-QSMS decoder for the rate- 5G LDPC code while it increases slightly for the code rates and .

Table 4.

The average number of iterations of different LDPC decoders with for the 5G LDPC codes.

5.3. Memory Requirement

We further investigated the overall memory requirement of the proposed RC-MIM-QSMS decoder and compare it to that of different quantized LDPC decoders. Here, we considered the decoders that are implemented based on software-defined radios or digital signal processors so that the LUTs are stored in memories [11]. We divided the memory into two types according to their usage, i.e., the memories for arithmetic calculation and those for storing the LUTs. For the conventional QSMS decoders, all -bit V2C messages need to be stored for the arithmetic calculation of the node updates at each iteration [27], while the RC-FAID decoder with flooding schedule uses the memories for arithmetic calculation to store two -bit C2V messages for each CN and one a posteriori message of bit width for each VN per iteration. Note that we considered the parity-check matrix of the rate- 802.11n LDPC code to evaluate the maximum memory requirement for arithmetic calculation since it had the largest size among all simulated codes. Moreover, we assumed that the memories for arithmetic calculation could be reused between two consecutive iterations for improving efficiency. On the other hand, the memory requirement for storing one LUT could be computed by in bytes, where E is the number of entries in one LUT, and refers to the maximum bit width of an entry. According to [11], at each iteration, the RC-FAID decoder requires cascaded LUTs for updating the VNs of different degrees and one LUT for message alignment process. Since the RC-FAID decoder exchanges -bit messages within the decoder and adopts two-input LUTs, we had for each LUT and . In addition, there was one extra LUT of at each iteration for making the hard decision. For the two MIM-QSMS decoders with , all LUTs had a single input so that there were two reconstruction LUTs of size and one quantization LUT of size . The bit width of each entry in each LUT could be obtained by , where is the maximum magnitude of the entry.

Table 5 summarizes the overall memory requirements of different quantized LDPC decoders with and for the 802.11n LDPC codes. As shown in the table, our proposed RC-MIM-QSMS decoder requires almost the same memory as the RC-MIM-QMS decoder and it only has a slight increase in the memory demand of compared to that of the conventional QSMS decoder. More importantly, the RC-MIM-QSMS decoder can reduce the memory demand by compared to its rate-dependent counterparts, and significantly saves of memory demand when compared with the RC-FAID decoder.

Table 5.

The Overall Memory Requirement for Different Quantized Decoders with and for the 802.11n LDPC codes.

Table 6 presents the overall memory requirements of different quantized LDPC decoders with and for the 5G LDPC codes. It shows that our proposed RC-MIM-QSMS decoder only increases the memory demand by compared to the conventional QSMS decoder and also requires less memory demand when compared with the RC-MIM-QMS decoder. More significantly, the RC-MIM-QSMS decoder requires and less memory demand compared to its rate-dependent counterparts and the RC-FAID decoder, respectively.

Table 6.

The Overall Memory Requirement for Different Quantized Decoders with and for the 5G LDPC codes.

6. Conclusions

In this paper, we proposed a framework of the RC-MIM-QSMS decoder to achieve less memory requirement for decoding QC-LDPC codes with different code rates. More specifically, we proposed the SMIM-DE to design the LUTs used by the RC-MIM-QSMS decoder, which took the weighted expectation of the pmfs and the joint degree distributions of RC-QC-LDPC codes into consideration. In such manner, we generated LUTs that varied with different layers and iterations. An optimization method was further adopted to unify the constructed LUTs into a unique set of iteration-specific LUTs. Simulation results showed that the proposed RC-MIM-QSMS decoder reduced memory usage by compared to that of the RC-FAID decoder and achieved almost the same convergence speed compared to the RD-MIM-QSMS decoder. More importantly, the RC-MIM-QSMS decoder showed only minor performance degradation with respect to the RD-MIM-QSMS decoder and even slightly outperformed the floating-point SBP decoder in the high SNR region.

Author Contributions

Conceptualization, P.K. and X.H.; methodology, P.K. and X.H.; software, P.K.; validation, P.K., X.H. and K.C.; formal analysis, P.K. and X.H.; investigation, P.K. and X.H.; resources, P.K. and K.C.; data curation, P.K.; writing—original draft preparation, P.K.; writing—review and editing, P.K., X.H., and K.C.; visualization, P.K. and X.H.; supervision, K.C.; project administration, K.C.; funding acquisition, K.C. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the Singapore Ministry of Education Academic Research Fund Tier 2 T2EP50221-0036, by RIE2020 Advanced Manufacturing and Engineering (AME) programmatic grant A18A6b0057, by Fundamental Research Funds for the Central Universities under grant 2682022CX023, and by Natural Science Foundation of Sichuan under grant 2022NSFSC0952.

Data Availability Statement

The data presented in this study will be available on request from the corresponding author.

Acknowledgments

The authors would like to thank Singapore Ministry of Education, Agency for Science, Technology and Research (ASTAR), Ministry of Education of the People’s Republic of China, and Natural Science Foundation of Sichuan for supporting this work.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Gallager, R.G. Low-Density Parity-Check Codes. IEEE Trans. Inf. Theory 1962, 8, 21–28. [Google Scholar] [CrossRef]

- Divsalar, D.; Dolinar, S.; Jones, C.R.; Andrews, K. Capacity-Approaching Protograph Codes. IEEE J. Sel. Areas Commun. 2009, 27, 876–888. [Google Scholar] [CrossRef]

- Chen, P.; Cai, K.; Zheng, S. Rate-Adaptive Protograph LDPC Codes for Multi-Level-Cell NAND Flash Memory. IEEE Commun. Lett. 2018, 22, 1112–1115. [Google Scholar] [CrossRef]

- Richardson, T.; Urbanke, R. The Capacity of Low-Density Parity-Check Codes under Message-Passing Decoding. IEEE Trans. Inf. Theory 2001, 47, 599–618. [Google Scholar] [CrossRef]

- Chen, J.; Dholakia, A.; Eleftheriou, E.; Fossorier, M.P.C.; Hu, X. Reduced-Complexity Decoding of LDPC Codes. IEEE Trans. Commun. 2005, 53, 1288–1299. [Google Scholar] [CrossRef]

- Lee, J.K.-S.; Thorpe, J. Memory-Efficient Decoding of LDPC Codes. In Proceedings of the IEEE International Symposium on Information Theory (ISIT), Adelaide, Australia, 4–9 September 2005; pp. 459–463. [Google Scholar]

- Kang, P.; Xie, Y.; Yang, L.; Yuan, J. Enhanced Quasi-Maximum Likelihood Decoding Based on 2D Modified Min-Sum Algorithm for 5G LDPC Codes. IEEE Trans. Commun. 2020, 68, 6669–6682. [Google Scholar] [CrossRef]

- Romero, F.J.C.; Kurkoski, B.M. LDPC Decoding Mappings that Maximize Mutual Information. IEEE J. Sel. Areas Commun. 2016, 34, 2391–2401. [Google Scholar] [CrossRef]

- He, X.; Cai, K.; Mei, Z. Mutual Information-Maximizing Quantized Belief Propagation Decoding of Regular LDPC Codes. arXiv 2019, arXiv:1904.06666v4. Available online: http://arxiv.org/abs/1904.06666 (accessed on 14 April 2019).

- He, X.; Cai, K.; Mei, Z. On Mutual Information-Maximizing Quantized Belief Propagation Decoding of LDPC Codes. In Proceedings of the IEEE Global Communications Conference (GLOBECOM), Waikoloa, HI, USA, 9–13 December 2019; pp. 1–6. [Google Scholar]

- Stark, M.; Wang, L.; Bauch, G.; Wesel, R.D. Decoding Rate-Compatible 5G-LDPC Codes with Coarse Quantization Using the Information Bottleneck Method. IEEE Open J. Commun. Soc. 2020, 1, 646–660. [Google Scholar] [CrossRef]

- Meidlinger, M.; Matz, G.; Burg, A. Design and Decoding of Irregular LDPC Codes Based on Discrete Message Passing. IEEE Trans. Commun. 2020, 68, 1329–1343. [Google Scholar] [CrossRef]

- Mohr, P.; Bauch, G.; Yu, F.; Li, M. Coarsely Quantized Layered Decoding Using the Information Bottleneck Method. In Proceedings of the IEEE International Conference on Communications (ICC), Montreal, QC, Canada, 14–23 June 2021; pp. 1–6. [Google Scholar]

- Kang, P.; Cai, K.; He, X.; Yuan, J. Memory Efficient Mutual Information-Maximizing Quantized Min-Sum Decoding for Rate-Compatible LDPC Codes. IEEE Commun. Lett. 2022, 26, 733–737. [Google Scholar] [CrossRef]

- Kang, P.; Cai, K.; He, X.; Li, S.; Yuan, J. Generalized Mutual Information-Maximizing Quantized Decoding of LDPC Codes with Layered Scheduling. IEEE Trans. Veh. Tech. 2022, 71, 7258–7273. [Google Scholar] [CrossRef]

- Wang, L.; Terrill, C.; Stark, M.; Li, Z.; Chen, S.; Hulse, C.; Kuo, C.; Wesel, R.D.; Bauch, G.; Pitchumani, R. Reconstruction-Computation-Quantization (RCQ): A Paradigm for Low Bit Width LDPC Decoding. IEEE Trans. Commun. 2022, 70, 2213–2226. [Google Scholar] [CrossRef]

- Kumar, P.; Kumar, R.; Srivastava, G.; Gupta, G.P.; Tripathi, R.; Gadekallu, T.R.; Xiong, N.N. PPSF: A Privacy-Preserving and Secure Framework Using Blockchain-Based Machine-Learning for IoT-Driven Smart Cities. IEEE Trans. Netw. Sci. Eng. 2021, 8, 2326–2341. [Google Scholar] [CrossRef]

- Lin, C.; He, Y.; Xiong, N. An Energy-Efficient Dynamic Power Management in Wireless Sensor Networks. In Proceedings of the International Symposium on Parallel and Distributed Computing, Timisoara, Romania, 6–9 July 2006; pp. 148–154. [Google Scholar]

- Xia, F.; Hao, R.; Li, J.; Xiong, N.; Yang, T.L.; Zhang, Y. Adaptive GTS allocation in IEEE 802.15.4 for real-time wireless sensor networks. J. Syst. Archit. 2013, 59, 1231–1242. [Google Scholar] [CrossRef]

- Cheng, H.; Xie, Z.; Shi, Y.; Xiong, N. Multi-Step Data Prediction in Wireless Sensor Networks Based on One-Dimensional CNN and Bidirectional LSTM. IEEE Access 2019, 7, 117883–117896. [Google Scholar] [CrossRef]

- He, X.; Cai, K.; Song, W.; Mei, Z. Dynamic Programming for Sequential Deterministic Quantization of Discrete Memoryless Channels. IEEE Trans. Commun. 2021, 69, 3638–3651. [Google Scholar] [CrossRef]

- Zhang, K.; Huang, X.; Wang, Z. High-Throughput Layered Decoder Implementation for Quasi-Cyclic LDPC Codes. IEEE J. Sel. Areas Commun. 2009, 27, 985–994. [Google Scholar] [CrossRef]

- Zhang, J.; Fossorier, M.P.C. Shuffled Iterative Decoding. IEEE Trans. Commun. 2005, 53, 209–213. [Google Scholar] [CrossRef]

- Nguyen, T.V.; Nosratinia, A.; Divsalar, D. The Design of Rate-Compatible Protograph LDPC Codes. IEEE Trans. Commun. 2012, 60, 2841–2850. [Google Scholar] [CrossRef]

- Mei, Z.; Cai, K.; Dai, B. Polar Codes for Spin-Torque Transfer Magnetic Random Access Memory. IEEE Trans. Magn. 2018, 54, 3401305. [Google Scholar] [CrossRef]

- Kschischang, F.R.; Frey, B.J. Iterative Decoding of Compound Codes by Probability Propagation in Graphical Models. IEEE J. Select. Areas Commun. 1998, 16, 219–230. [Google Scholar] [CrossRef]

- Cui, Z.; Wang, Z.; Zhang, X. Reduced-Complexity Column-Layered Decoding and Implementation for LDPC Codes. IET Commun. 2011, 5, 2177–2186. [Google Scholar] [CrossRef]

- Ryan, W.; Lin, S. Channel Codes: Classical and Modern; Cambridge University Press: Cambridge, UK, 2009. [Google Scholar]

- Tanner, R. A Recursive Approach to Low Complexity Codes. IEEE Trans. Inf. Theory 1981, 27, 533–547. [Google Scholar] [CrossRef]

- IEEE Computer Society LAN/MAN Standards Committee. IEEE Standard for Information Technology—Telecommunications and Information Exchange Between Systems—Local and Metropolitan Area Networks-Specific Requirements— Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications; IEEE Computer Society LAN/MAN Standards Committee: Piscataway, NJ, USA, 2009. [Google Scholar]

- 3rd Generation Partnership Project. Technical Specification Group Radio Access Network; NR.; Multiplexing and Channel Coding (Release 16), 3GPP TS 38.212; 3rd Generation Partnership Project: Valbonne, France, 2021. [Google Scholar]

- Richardson, T. Error Floor of LDPC Codes. In Proceedings of the 41st Annual Allerton Conference on Communication, Control, and Computing, Monticello, IL, USA, 1–3 October 2003. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).