Abstract

Today’s technology demands compact, portable, fast, and energy-efficient devices. One approach to making energy-efficient devices is an in-memory computation that addresses the memory bottleneck issues of the present computing system by utilizing a spintronic device viz. magnetic tunnel junction (MTJ). Further, area and energy can be reduced through approximate computation. We present a circuit design based on the logic-in-memory computing paradigm on voltage-controlled magnetic anisotropy magnetoresistive random access memory (VCMA-MRAM). During the computation, multiple bit cells within the memory array are selected that are in parallel by activating multiple word lines. The designed circuit performs all logic operations-Read/NOT, AND/NAND, OR/NOR, and arithmetic SUM operation (1-bit approximate adder with 75% accuracy for SUM and accurate carry out) by slight modification using control signals. All the simulations have been performed at a 45 nm CMOS technology node with VCMA-MTJ compact model by using the HSPICE simulator. Simulation results show that the proposed circuit’s approximate adder consumes about 300% less energy and 2.3 times faster than its counterpart exact adder.

1. Introduction

In conventional von Neumann computer architectures, the limited data bandwidth and data transfer between the processor and the memory consume high energy and latency, causing significant degradation of the system’s performance and efficiency. These issues being called “memory wall” and “power wall” are causing unprecedented challenges for traditional computing to handle big data [1,2,3]. To overcome these issues, in-memory processing (IMP) paradigm has been proposed for incorporating a limited number of processing units inside the memory [4]. This paradigm pre-processes the raw data and transfers only intermediate results to the processor instead of moving all the raw data. This paradigm improves performance by reducing the power and data transfer bandwidth overhead courtesy of simple logic operations in the memory. However, these paradigms are rather complex and costly because of the manufacturing of the performance-optimized processing units and the density-optimized memory on the same chip. Furthermore, the scaling of complementary metal-oxide-semiconductor (CMOS) devices is becoming challenging due to associated static and dynamic power dissipation [5]. Therefore, researchers are exploring other computer architectures by utilizing new emerging technologies (spintronics [6], memristors [7], carbon nanotube field-effect transistors (CNFETs) [8], and nanowire field-effect transistors (NWFETs) [9], etc.) to enhance the performance of the computing systems.

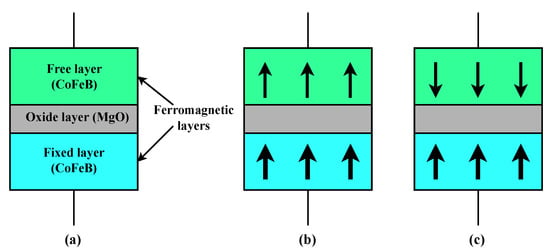

Magnetic-based logic devices have become a promising alternative to CMOS logic devices in dealing with the aforementioned issues. Magnetic domain walls [10], magnetic vortexes [11], magnetic skyrmions [12], and magnetic tunnel junction (MTJ) [13] have nowadays become a central area of research due to the achievements in the science and technology towards miniaturization of devices into the nanometer length scale. The MTJ offers low-power consumption, non-volatility, and high endurance making them an ideal candidate for designing processors and memories in combination with CMOS technology [14,15,16,17,18,19,20,21,22]. An MTJ is a non-volatile device that can store 1-bit of data depending upon its state. Figure 1a shows a typical MTJ structure comprising two relatively thick ferromagnetic layers (a fixed layer and a free layer) separated by a relatively thin tunnel barrier layer. When the fixed and the free layers have the same magnetic direction, as shown in Figure 1b, the MTJ shows a lower resistance. On the contrary, when the magnetic directions of both layers are anti-parallel, as shown in Figure 1c, the MTJ shows a higher resistance. The tunnel magnetoresistance (TMR) ratio characterizes the resistance difference and is defined by the following equation:

where () and () are the MTJ’s resistances in anti-parallel and parallel states, respectively. If the difference between the resistances in parallel and anti-parallel is significant, it shows higher TMR and readability. In this paper, we examined the switching characteristics of the VCMA-assisted STT switching based on the Landau–Lifshitz–Gilbert (LLG) equation. The proposed scheme has the advantage of the deterministic switching state. The LLG equation [23,24,25,26] is given by:

where M is the magnetization vector of the free layer, is the voltage-dependent effective magnetic field, P is the spin polarization factor, ℏ is the reduced Planck’s constant, J is the switching current density, is fixed layer’s magnetization vector, and e is the electron charge. consists of different field components that affect the free layer [25].

where is the external magnetic field, is the demagnetization field, is the thermal field, is the voltage-dependent effective perpendicular anisotropy field, is the permeability, m = [, , ] is the magnetization moment, and [x, y, z] is the unit vector.

Figure 1.

(a) Vertical structure of the MTJ. (b) MTJ’s parallel state/high logic value (1)/low resistance. (c) MTJ’s antiparallel state/low logic value (0)/high resistance.

Several methods have been discussed in the literature to change the switching states of an MTJ. For instance, spin-transfer torque (STT) [23], spin Hall effect (SHE) [24], voltage-controlled magnetic anisotropy (VCMA) [25], STT-assisted SHE [24], VCMA-assisted STT [25], and VCMA-assisted SOT [27]. The conventional STT switching-based MTJ has poor write endurance and suffers from high switching energy as charge current flows through the MTJ stacks [28]. To overcome these issues, a three-terminal SOT switching-based MTJ has been introduced where write and read paths are separated by adding a heavy metal layer under MTJ’s free layer. This isolation significantly improves the reliability of the device since the write current now flows through the heavy metal and generates SOT and SHE to switch the magnetization of the MTJ’s free layer [27,29]. However, an additional in-plane magnetic field is required to achieve deterministic switching for the MTJ. Another emerging write mechanism is VCMA which lowers the energy barrier and switches the magnetization by applying a voltage across the MTJ [30]. Reference [31] discusses the basic concepts of the approximate computing (AC) paradigm and focuses on the design and testing of integrated circuits for AC-based systems. A survey on AC is discussed in [32] to provide researchers with knowledge of how AC approaches work and to promote more study in order to make AC the standard computing paradigm in upcoming systems. A progressive scaling scheme for STT-RAM arrays is presented in [33] that reduces the power consumption at the cost of minor quality degradation. Reference [34] provides a summary of the challenges involved in designing energy-efficient IoT edge devices and summarizes recent studies that have suggested potential solutions to these challenges. Reference [35] reports a circuit that performs Read/NOT, AND/NAND, OR/NOR, Sum, and carry operations. It consists of eight MTJs and eleven MOSFETs excluding the writing circuit for MTJs in its logic tree. Reference [18] presents a circuit that performs all the basic logic operations such as NOT, NAND/AND, OR/NOR, and memory read. The hardware requires only six MTJs in its logic tree excluding the writing circuit.

This paper presents a fully non-volatile hybrid MTJ/CMOS logic-in-memory computing-based multi-functional circuit that performs all the basic logic operations such as Read/NOT, AND/NAND, OR/NOR, and arithmetic operation SUM (1-bit approximate adder with 75% accuracy for sum and accurate carry out) by a slight modification using the control signals. All the simulations have been performed in 45 nm CMOS technology with VCMA-MTJ compact model [25] using the HSPICE simulator. The proposed multi-functional circuit will be the main building block of the future MTJ-based processors where CMOS transistors will be replaced by hybrid MTJ/CMOS or only MTJ. The rest of the paper is organized as follows. Section 2 covers the basics of the VCMA-MRAM bank. Section 3 demonstrates the working principle of the proposed multi-functional circuit. Simulation results are discussed in Section 4. Section 5 finally concludes the paper.

2. Fundamentals of VCMA-MRAM

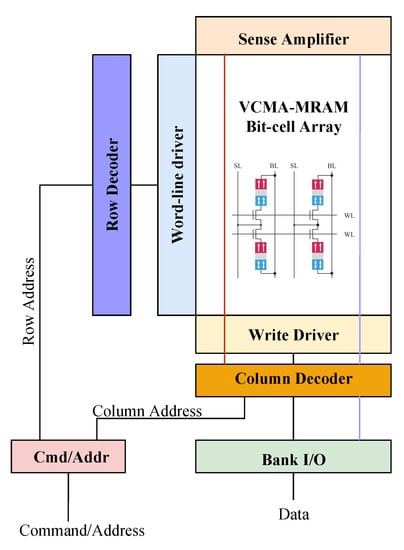

The schematic diagram of the VCMA-MRAM bank is illustrated in Figure 2. A conventional bit cell consists of one MTJ and one transistor; both are in series and an array of bit-cells is designed with multiple word-lines, source-lines, and bit-lines [36]. The spintronic memory bank contains a bit-cell array, a sense amplifier, a word-line driver, a write driver, a row/column decoder, and an input/output interface. The row and column decoder are used to select a particular bit cell according to its row and column address. The data in the MTJs are written by passing shaped voltage pulse through a write driver [37]. The shaped voltage pulse changes the magnetization state of the free layer of the MTJ or can say data is written in the bit-cell. In this paper, the circuit is designed by selecting five bit cells from the memory array in which three bit cells are connected to one arm of a differential sense amplifier and the other two bit cells are connected to the other arm. The implementation and working principle of other peripheral circuits are beyond the scope of this paper.

Figure 2.

Schematic diagram of VCMA-MRAM bank.

3. Proposed Multi-Functional Circuit

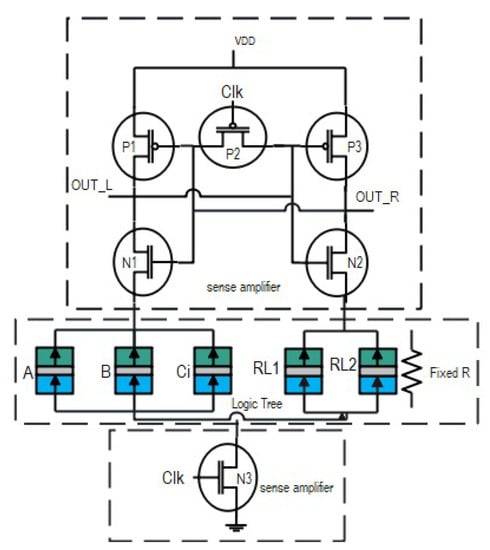

The schematic diagram of the proposed logic-in-memory-based multi-functional circuit is shown in Figure 3. The hybrid MTJ-CMOS circuit performs all the basic logic operations such as Read/NOT, AND/NAND, OR/NOR, and an arithmetic SUM operation (1-bit approximate adder with 75% accuracy for sum and accurate carry out) by slight modification using the control signals illustrated in Table 1.

Figure 3.

Schematic diagram of the proposed multi-functional circuit.

Table 1.

Operation of the control signals.

The circuit shown in Figure 3 consists of two parts: (1) sense amplifier; SRAM-based sense amplifier is cross-coupled with two inverters that sense the small voltage difference across the nodes and pulls one of its nodes to the full swing voltage level and the other one to zero in the differential manner in the sensing mode, and (2) logic tree; made up of MTJs that store input logic values in their spin. The reconfigurable MTJs in the left arm of the sense amplifier uses the VCMA-assisted STT switching mechanism while the MTJs in the right arm of the sense amplifier have resistances, RL1 and RL2 that are fixed and both the MTJs are in low resistance mode. In order to function the circuit correctly, the net resistance of the right arm should be in between RL‖RL‖RH and RH‖RH‖RL, hence, is fixed at RL‖RL. Additionally, the TMR of the circuit must be greater than 100%. The multi-functional circuit is a dynamic circuit that works in two phases: (1) pre-charge phase, and (2) evaluate phase. In the pre-charge phase, when Clk = 0, all the transistors turn ON except the transistor N3; output nodes are pre-charged to supply voltage minus the threshold voltage of the PMOS transistors. In evaluate phase, when Clk = 1, all the transistors turn ON except the transistor P2; based on the inputs logic values stored on the MTJs and one of its output nodes is discharged to zero through a lower resistance path and pulls the other output node to a full supply voltage, VDD.

The mode of the circuit is controlled by the left arm’s MTJs as mentioned in Table 1. When the MTJ Ci is at a low logic value (offers high resistance), the circuit performs two inputs AND/NAND operations between inputs logic A and logic B, gives simultaneously AND and NAND logic values to the output nodes OUT_L and OUT_R, respectively. When the control signal (Ci) is kept at a high logic value then the circuit performs 1-bit OR and NOR operations between inputs logic A and logic B. The output nodes OUT_L and OUT_R give OR and NOR logical values, respectively. The circuit acts as a logical Read/NOT operation when the MTJA and MTJB store the same logic values that are considered to be the input to the gate irrespective of the values of the MTJ Ci. The output node OUT_L and OUT_R give logical NOT values and read the data, respectively. Moreover, the circuit performs arithmetic SUM operation; the MTJA, and the MTJB are one-bit inputs to the adder, and the carry from the previous bit is fed to the MTJ Ci. The operations are performed among the inputs and hence logical SUM (Asum) with 75% accuracy and carry output (Cout) with 100% accuracy as per the truth Table 2 are stored in output nodes OUT_L and OUT_R, respectively.

Table 2.

Truth table of the proposed 1-bit Approximate Full Adder.

To understand the operation of the circuit with more clarity, let’s consider that the inputs MTJ A store logical value 1, MTJ B store the logical value 0, and the carry from the previous bit is applied to the MTJ Ci i.e., high logic value. Therefore, the total resistance of the left arm is RL‖RH‖RL = 11.40 KΩ and the right arm resistances, RL1 and RL2 are in low resistance mode, hence, it offers a resistance of RL‖RL = 13.25 KΩ as illustrated in the seventh row of Table 2. Consequently, the output node OUT_L discharges faster than the output node OUT_R. Hence, OUT_L is at zero voltage level while the OUT_R node is at a full swing supply voltage. Likewise, the rest of the combinations can be explained.

4. Simulations and Discussion

The simulations of the proposed circuit have been performed in 45 nm CMOS technology using predictive technology model (PTM) and VCMA-assisted STT switching mechanism at VCMA coefficient value of 105 fJV−1m−1 using VCMA-MTJ compact model [25] with HSPICE simulator in order to validate its functionalities as well as its robustness against the counterpart circuits [18,35]. The comparison circuits are also simulated with the same MTJ and CMOS model for fair comparison which is illustrated in Table 3.

Table 3.

Performance metrics of the multifunctional circuit and its counterpart circuits (T = 300 K, TMR = 208, RL = 26.5 K, RH = 81.7 K).

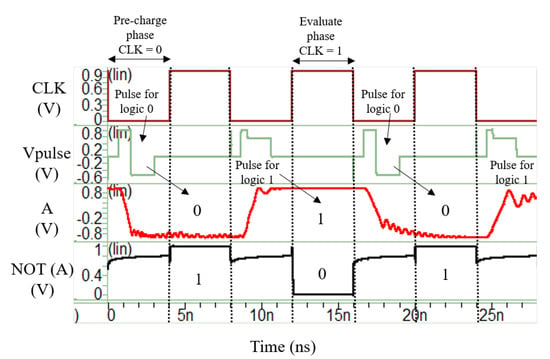

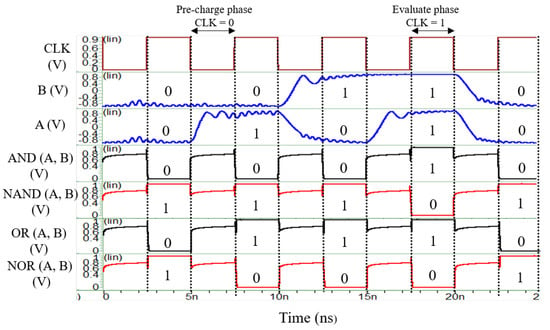

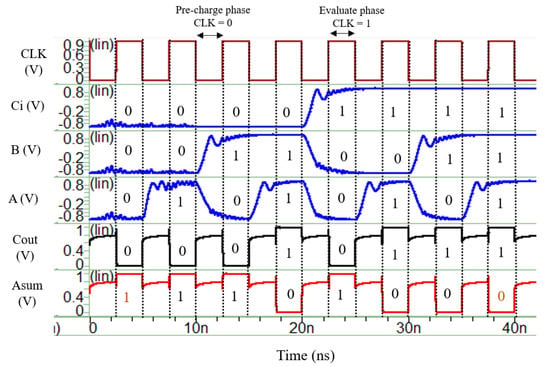

The transient response of the logic operation NOT is shown in Figure 4. Figure 5 presents the transient response of the logic operations AND, NAND, OR, and NOR. Similarly, Figure 6 demonstrates the arithmetic SUM operation (approximate adder) for all possible input combinations. A clock voltage pulse of 0.9 V peak to peak amplitude and 8 ns period with a duty cycle of 50% is applied for all the operations. When CLK = 0; reconfigurable MTJs are in the writing phase. The MTJs store logic values by applying a shaped voltage pulse (Vpulse) of amplitude 0.8 V for VCMA switching followed by a lower voltage (for STT switching) of +0.55 V for high logic value or −0.55 V for lower logic value as shown in Figure 4. When CLK = 1; the circuit is in the evaluation phase so it gives the logical NOT values as NOT (A) of applied input A as shown in Figure 4 and logical AND/NAND, OR/NOR values of inputs logic values A and B as shown in Figure 5. The input-output waveforms of the approximate adder (SUM) are illustrated in Figure 6 according to the truth table shown in Table 2.

Figure 4.

Transient response of logic operation NOT where CLK is the input clock pulse, Vpulse is the shaped voltage pulse that is used to switch the state of MTJ, A is input logic values, and NOT (A) is the logical not values.

Figure 5.

Transient response of logic operations AND, NAND, OR, and NOR where CLK is input clock pulse, A and B input logic values, AND (A, B), NAND (A, B), OR (A, B), and NOR (A, B) are the logical AND, NAND, OR, and NOR values between inputs A and B.

Figure 6.

Transient response of arithmetic operation SUM, where CLK is input clock pulse, A and B are input logic values, Ci is carry input values, Cout is the output carry values, and Asum is the approximate sum values.

The performance metrics of the proposed circuit along with the previously existing circuits CKT1 [18], and CKT2 [35] are tabulated in Table 3. The sensing power of the proposed circuit is slightly less than the CKT1 and less than half than the CKT2. Moreover, the proposed approximate adder consumes 4.3 times less power than the exact adder of the CKT2. This is due to the presence of two sense amplifiers and additional transistors in the reconfigurable MTJs’ path of the CKT2. The CKT2 calculates Sum and Cout separately while the proposed circuit uses one sense amplifier for both and calculates ASum and Cout simultaneously, but the accuracy of the sum is 75% and the carry output is accurate. The delay depends upon the net resistance of discharging path of a circuit. The CKT1 has all the six MTJs, that are reconfigurable in the logic tree: three of the MTJs are parallelly connected to one arm of the sense amplifier and the other three MTJs are to the other arm in a complementary manner. Hence, the net maximum resistance of the CKT1’s discharging path always be less than the proposed circuit’s maximum resistance of discharging path. So the delay of the CKT1 is roughly about 20% less as compared to the proposed circuit although the CKT1 lags behind in terms of the number of operations. Both the CKT2 and the proposed circuit perform all the basic logic operations and addition operations while the CKT1 only performs basic logic operations. So, the better counterpart to the proposed circuit is CKT2, but in this case, the delay of the proposed circuit is winning and far less than the CKT2–delay of the CKT2 is 2.3 times of the proposed circuit. The switching energy depends upon the number of reconfigurable MTJs and operations of the circuits or arrangement of the MTJs and the transistors in the logic tree that’s why it varies hugely from one circuit to others. The energy-delay product (EDP) of the CKT2 is 9.5 times the proposed circuit.

5. Conclusions

This paper presents a logic-in-memory multi-functional circuit that performs the main logic functions like Read/NOT, AND/NAND, OR/NOR, and an arithmetic SUM function (approximate full adder) with 75% accuracy and Cout with 100% accuracy by using the control signals. It requires less hardware (five MTJs in the logic tree, six transistors in the sense amplifier) as compared to the previous works. The proposed circuit’s approximate adder is 2.3 times faster than CKT2’s exact adder and saves energy by about 330%. Overall, the proposed adder EDP is remarkably greater than the exact adder of the CKT1. The fully non-volatile functionality of the proposed circuit lowers the energy consumption over the buses that connect the memory to the processor, has no need for refreshing energy, and also reduces the leakage power to near zero.

Author Contributions

Conceptualization, G.G. and S.A.; methodology, G.G. and S.A.; software, G.G.; validation, G.G., S.A. and H.F.; formal analysis, G.G., S.A. and R.K.; investigation, G.G., S.A., R.K. and D.K.; resources, S.A., H.F. and Y.M.; data curation, G.G. and S.A.; writing—original draft preparation, G.G., R.K. and D.K.; writing—review and editing, G.G., R.K. and D.K.; visualization, G.G. and S.A.; supervision, S.A., H.F. and Y.M.; project administration, H.F. and Y.M.; funding acquisition, Y.M. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data sharing is not applicable to this article.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Kim, N.S.; Austin, T.; Baauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar]

- Wulf, W.A.; McKee, S.A. Hitting the memory wall: Implications of the obvious. ACM SIGARCH Comput. Archit. News 1995, 23, 20–24. [Google Scholar] [CrossRef]

- Chi, P.; Li, S.; Xu, C.; Zhang, T.; Zhao, J.; Liu, Y.; Wang, Y.; Xie, Y. PRIME: A Novel Processing-in-Memory Architecture for Neural Network Computation in ReRAM-Based Main Memory. In Proceedings of the 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, Korea, 18–22 June 2016; pp. 27–39. [Google Scholar]

- Li, S.; Xu, C.; Zou, Q.; Zhao, J.; Lu, Y.; Xie, Y. Pinatubo: A processing-in-memory architecture for bulk bitwise operations in emerging non-volatile memories. In Proceedings of the 2016 53nd ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, USA, 2–10 June 2016; pp. 1–6. [Google Scholar]

- Hanyu, T.; Endoh, T.; Suzuki, D.; Koike, H.; Ma, Y.; Onizawa, N.; Natsui, M.; Ikeda, S.; Ohno, H. Standby-Power-Free Integrated Circuits Using MTJ-Based VLSI Computing. Proc. IEEE 2016, 104, 1844–1863. [Google Scholar] [CrossRef]

- Wolf, S.A.; Awschalom, D.D.; Buhrman, R.A.; Daughton, J.M.; Von Molnár, S.; Roukes, M.L.; Chtchelkanova, A.Y.; Treger, D.M. Spintronics: A spin-based electronics vision for the future. Science 2001, 294, 1488–1495. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. The Desired Memristor for Circuit Designers. IEEE Circuits Syst. Mag. 2013, 13, 17–22. [Google Scholar] [CrossRef]

- Lin, S.; Kim, Y.B.; Lombardi, F. CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 2011, 10, 217–225. [Google Scholar] [CrossRef]

- Mikolajick, T.; Heinzig, A.; Trommer, J.; Baldauf, T.; Weber, W.M. The RFET—A reconfigurable nanowire transistor and its application to novel electronic circuits and systems. Semicond. Sci. Technol. 2017, 32, 043001. [Google Scholar] [CrossRef]

- Cheng, R.; Li, M.; Sapkota, A.; Rai, A.; Pokhrel, A.; Mewes, T.; Mewes, C.; Xiao, D.; Graef, M.D.; Sokalski, V. Magnetic domain wall skyrmions. Phys. Rev. B. 2019, 99, 184412. [Google Scholar] [CrossRef]

- Wang, Y.; Mehmood, N.; Hou, Z.; Mi, W.; Zhou, G.; Gao, X.; Liu, J. Electric Field-Driven Rotation of Magnetic Vortex Originating from Magnetic Anisotropy Reorientation. Adv. Electron. Mater. 2021, 8, 2100561. [Google Scholar] [CrossRef]

- Yang, H.; Wang, C.; Wang, X.; Wang, X.S.; Cao, Y.; Yan, P. Twisted skyrmions at domain boundaries and the method of image skyrmions. Phys. Rev. B. 2018, 98, 014433. [Google Scholar] [CrossRef]

- Divyanshu, D.; Kumar, R.; Khan, D.; Amara, S.; Massoud, Y. Physically Unclonable Function using GSHE driven SOT assisted MTJ for next Generation Hardware Security Applications. In Proceedings of the IEEE 65th International Midwest Symposium on Circuits and Systems (MWSCAS), Virtual, 7–10 August 2022; pp. 1–4. [Google Scholar]

- Cai, H.; Wang, Y.; de Barros Naviner, L.A.; Yang, J.; Zhao, W. Exploring hybrid STT-MTJ/CMOS energy solution in near-/sub-threshold regime for IoT applications. IEEE Trans. Magn. 2018, 54, 3400409. [Google Scholar] [CrossRef]

- Kim, J.; Chen, A.; Behin-Aein, B.; Kumar, S.; Wang, J.-P.; Kim, C.H. A technology-agnostic MTJ SPICE model with user-defined dimensions for STT-MRAM scalability studies. In Proceedings of the 2015 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 28–30 September 2015; pp. 1–4. [Google Scholar]

- Islam, S.M.; Sangwan, V.K.; Buchholz, D.B.; Wells, S.A.; Peng, L.; Zeng, L.; He, Y.; Hersam, M.C.; Ketterson, J.B.; Marks, T.J.; et al. Amorphous to Crystal Phase Change Memory Effect with Two-Fold Bandgap Difference in Semiconducting K2Bi8Se13. J. Am. Chem. Soc. 2021, 143, 6221–6228. [Google Scholar] [CrossRef]

- Jain, S.; Ranjan, A.; Roy, K.; Raghunathan, A. Computing in Memory With Spin-Transfer Torque Magnetic RAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 470–483. [Google Scholar] [CrossRef]

- Kang, W.; Wang, H.; Wang, Z.; Zhang, Y.; Zhao, W. In-Memory Processing Paradigm for Bitwise Logic Operations in STT–MRAM. IEEE Trans. Magn. 2017, 53, 6202404. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; De Barros Naviner, L.A.; Zhao, W. Robust Ultra-Low Power Non-Volatile Logic-in-Memory Circuits in FD-SOI Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 847–857. [Google Scholar] [CrossRef]

- Parveen, F.; He, Z.; Angizi, S.; Fan, D. HielM: Highly flexible in-memory computing using STT MRAM. In Proceedings of the 2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), Jeju Island, Korea, 22–25 June 2018; pp. 361–366. [Google Scholar]

- Zabihi, M.; Zhao, Z.; Mahendra, D.C.; Chowdhury, Z.I.; Resch, S.; Peterson, T.; Karpuzcu, U.R.; Wang, J.-P.; Sapatnekar, S.S. Using Spin-Hall MTJs to Build an Energy-Efficient In-memory Computation Platform. In Proceedings of the 20th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 6–7 March 2019; pp. 52–57. [Google Scholar]

- Kumar, R.; Divyanshu, D.; Khan, D.; Amara, S.; Massoud, Y. Spin Orbit Torque-Assisted Magnetic Tunnel Junction-Based Hardware Trojan. Electronics 2022, 11, 1753. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhao, W.; Lakys, Y.; Klein, J.-O.; Kim, J.-V.; Ravelosona, D.; Chappert, C. Compact Modeling of Perpendicular-Anisotropy CoFeB/MgO Magnetic Tunnel Junctions. IEEE Trans. Electron Devices 2012, 59, 819–826. [Google Scholar] [CrossRef]

- Ahmed, I.; Zhao, Z.; Mankalale, M.G.; Sapatnekar, S.S.; Wang, J.-P.; Kim, C.H. A Comparative Study Between Spin-Transfer-Torque and Spin-Hall-Effect Switching Mechanisms in PMTJ Using SPICE. IEEE J. Explor. Solid-State Comput. Devices Circuits 2017, 3, 74–82. [Google Scholar] [CrossRef]

- Song, J.; Ahmed, I.; Zhao, Z.; Zhang, D.; Sapatnekar, S.S.; Wang, J.-P.; Kim, C.H. Evaluation of Operating Margin and Switching Probability of Voltage-Controlled Magnetic Anisotropy Magnetic Tunnel Junctions. IEEE J. Explor. Solid-State Comput. Devices Circuits 2018, 4, 76–84. [Google Scholar] [CrossRef]

- Kang, W.; Ran, Y.; Zhang, Y.; Lv, W.; Zhao, W. Modeling and Exploration of the Voltage-Controlled Magnetic Anisotropy Effect for the Next-Generation Low-Power and High-Speed MRAM Applications. IEEE Trans. Nanotechnol. 2017, 16, 387–395. [Google Scholar] [CrossRef]

- Shreya, S.; Kaushik, B.K. Modeling of Voltage-Controlled Spin–Orbit Torque MRAM for Multilevel Switching Application. IEEE Trans. Electron Devices 2020, 67, 90–98. [Google Scholar] [CrossRef]

- Wang, Z.; Zhou, H.; Wang, M.; Cai, W.; Zhu, D.; Klein, J.O.; Zhao, W. Proposal of Toggle Spin Torques Magnetic RAM for Ultrafast Computing. IEEE Electron Device Lett. 2019, 40, 726–729. [Google Scholar] [CrossRef]

- Lee, S.-W.; Lee, K.-J. Emerging three-terminal magnetic memory devices. Proc. IEEE 2016, 104, 1831–1843. [Google Scholar] [CrossRef]

- Lee, H.; Lee, A.; Wang, S.; Ebrahimi, F.; Gupta, P.; Amiri, P.K.; Wang, K.L. Analysis and compact modeling of magnetic tunnel junctions utilizing voltage-controlled magnetic anisotropy. IEEE Trans. Magn. 2018, 54, 4400209. [Google Scholar] [CrossRef]

- Bosio, A.; Virazel, A.; Girard, P.; Barbareschi, M. Approximate computing: Design & test for integrated circuits. In Proceedings of the 2017 18th IEEE Latin American Test Symposium (LATS), Bogota, Colombia, 13–15 March 2017. [Google Scholar]

- Mittal, S. A survey of techniques for approximate computing. ACM Comput. Surv. 2016, 48, 62. [Google Scholar] [CrossRef]

- Zeinali, B.; Karsinos, D.; Moradi, F. Progressive Scaled STT-RAM for Approximate Computing in Multimedia Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 938–942. [Google Scholar] [CrossRef]

- Jayakumar, H.; Raha, A.; Kim, Y.; Sutar, S.; Lee, W.S.; Raghunathan, V. Energy-efficient system design for IoT devices. In Proceedings of the 2016 21st Asia and South Pacific Design Automation Conference (ASP-DAC), Macao, Macao, 25–28 January 2016; pp. 298–301. [Google Scholar]

- Wang, C.; Wang, Z.; Wang, G.; Zhang, Y.; Zhao, W. Design of an Area-Efficient Computing in Memory Platform Based on STT-MRAM. IEEE Trans. Magn. 2021, 57, 3400504. [Google Scholar] [CrossRef]

- Kang, W.; Chang, L.; Zhang, Y.; Zhao, W. Voltage-controlled MRAM for working memory: Perspectives and challenges. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, 27–31 March 2017; pp. 542–547. [Google Scholar]

- Gulafshan; Khan, M.A.; Hasan, M. Design of High Speed, Energy, and Area Efficient Spin-Based Hybrid MTJ/CMOS and CMOS Only Approximate Adders. IEEE Trans. Magn. 2022, 58, 3400608. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).