The Design of a Low Noise and Low Power Current Readout Circuit for Sub-pA Current Detection Based on Charge Distribution Model

Abstract

:1. Introduction

2. Analysis and Design

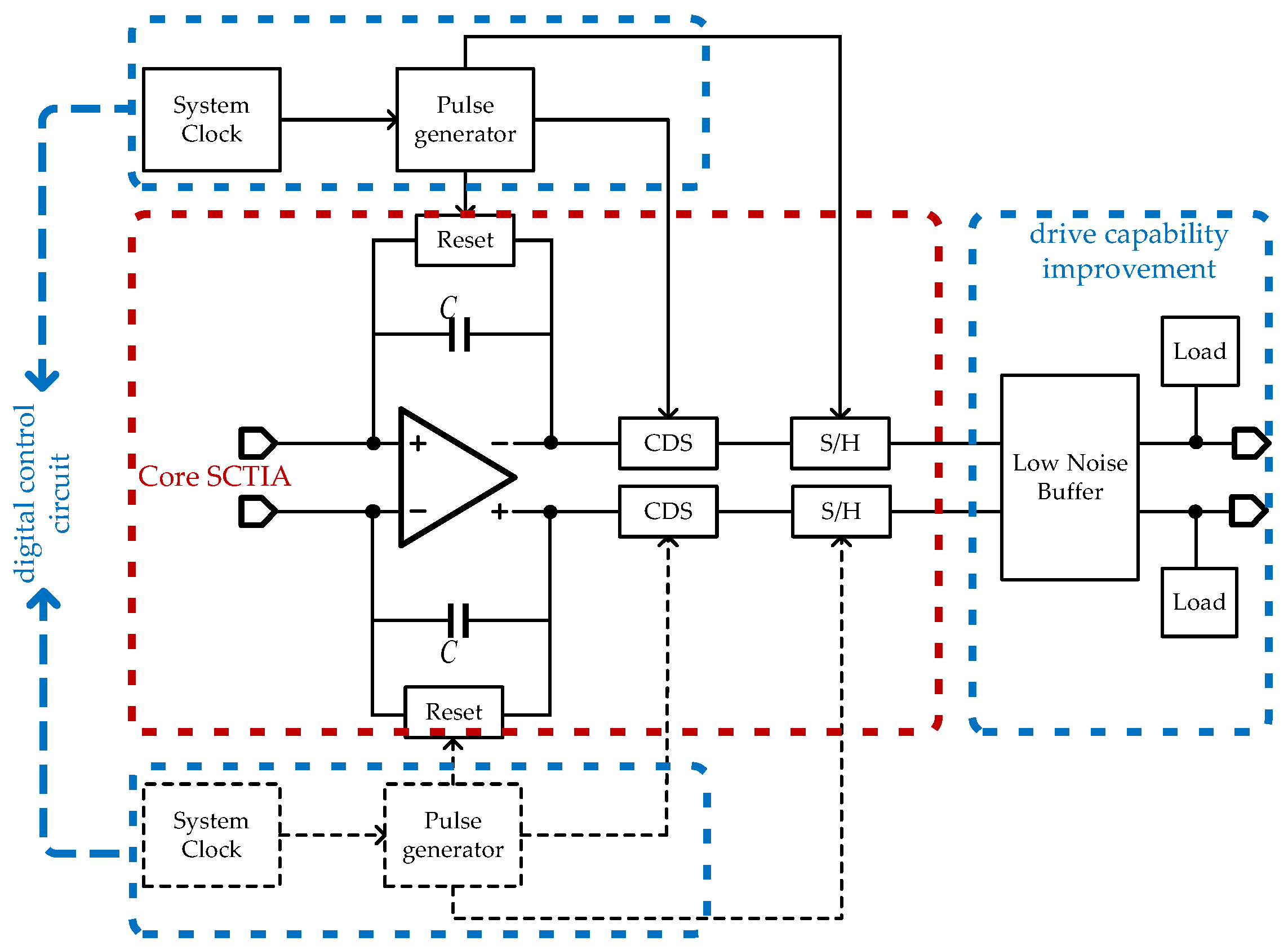

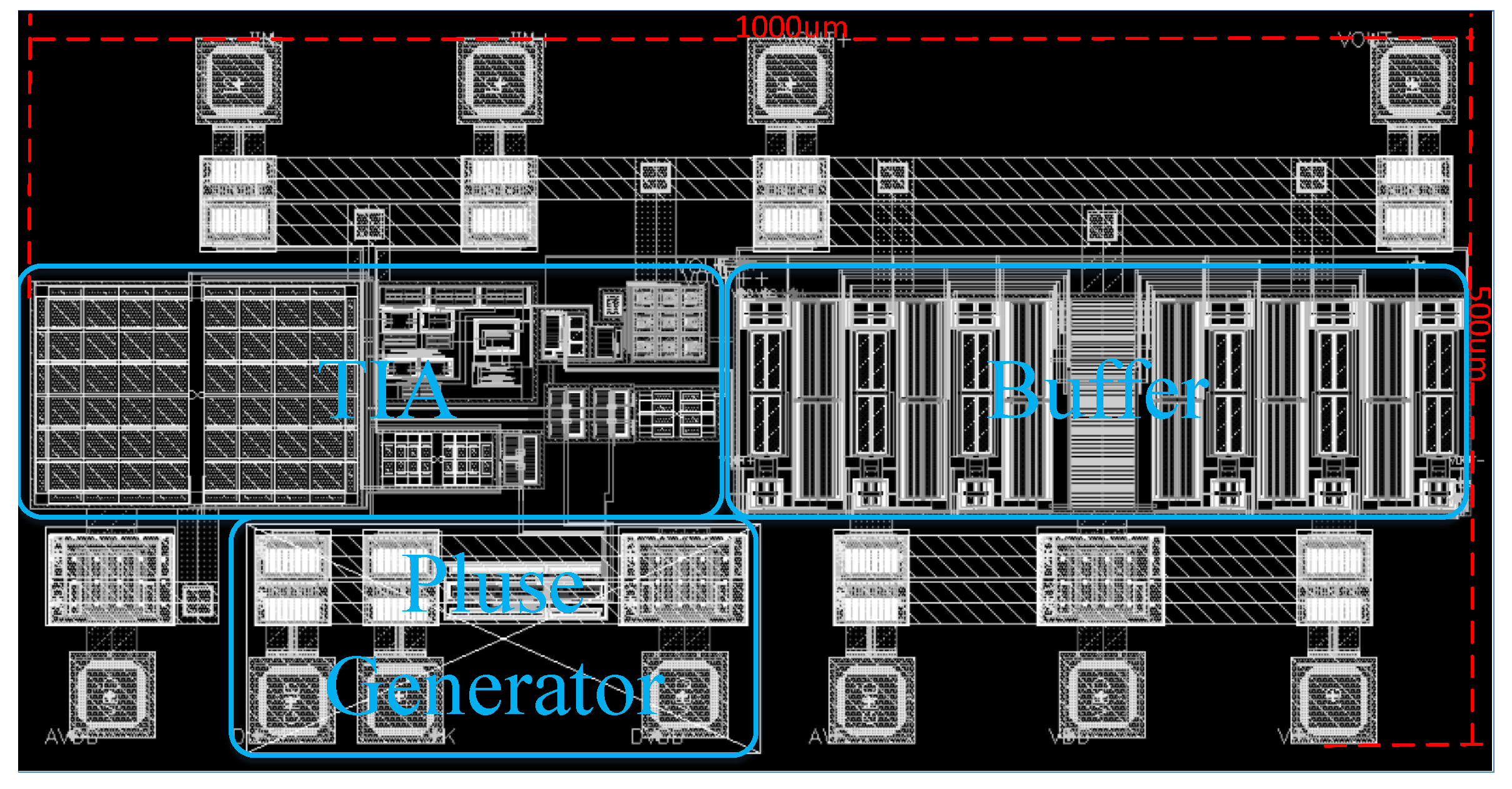

2.1. The Architecture Design

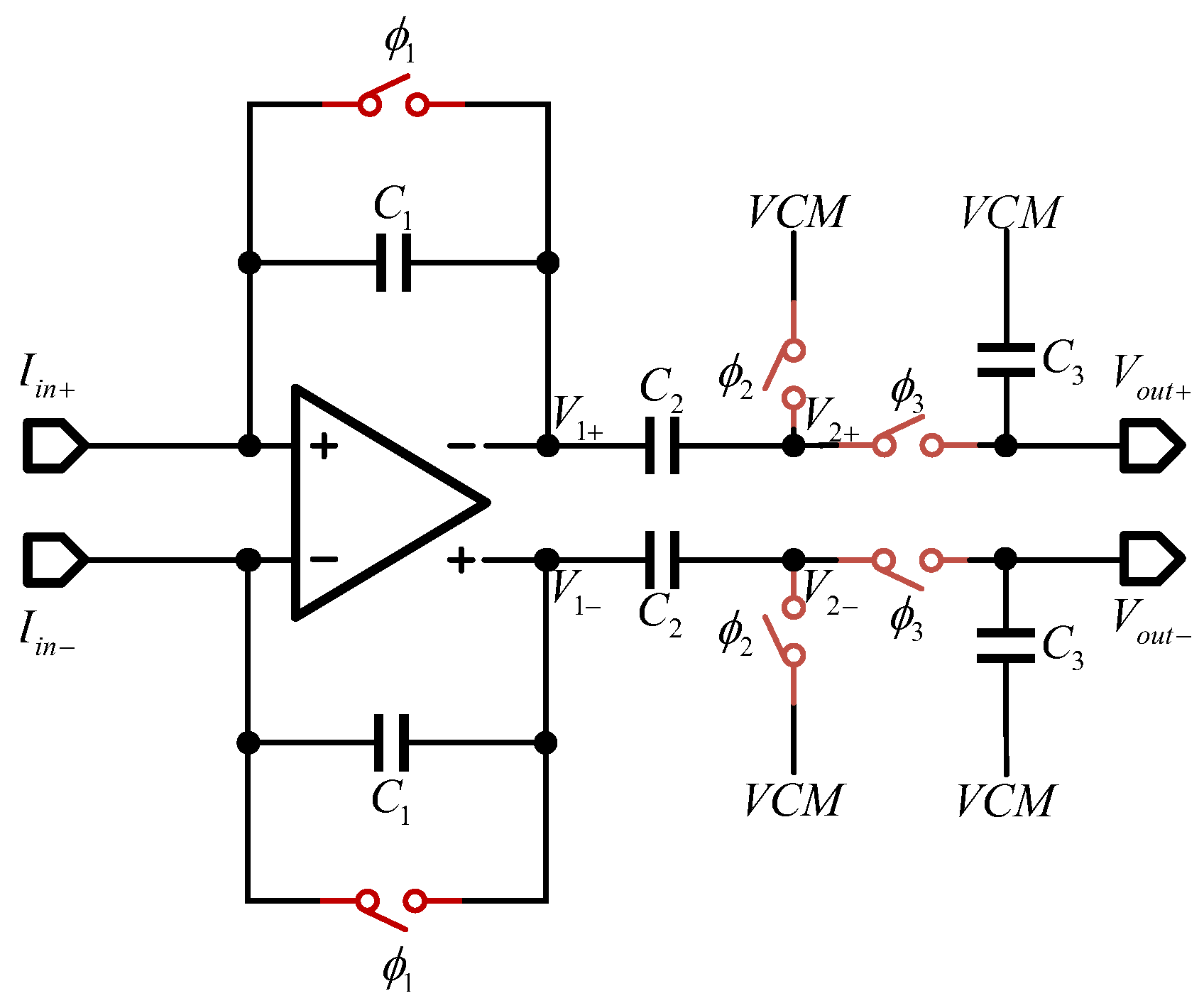

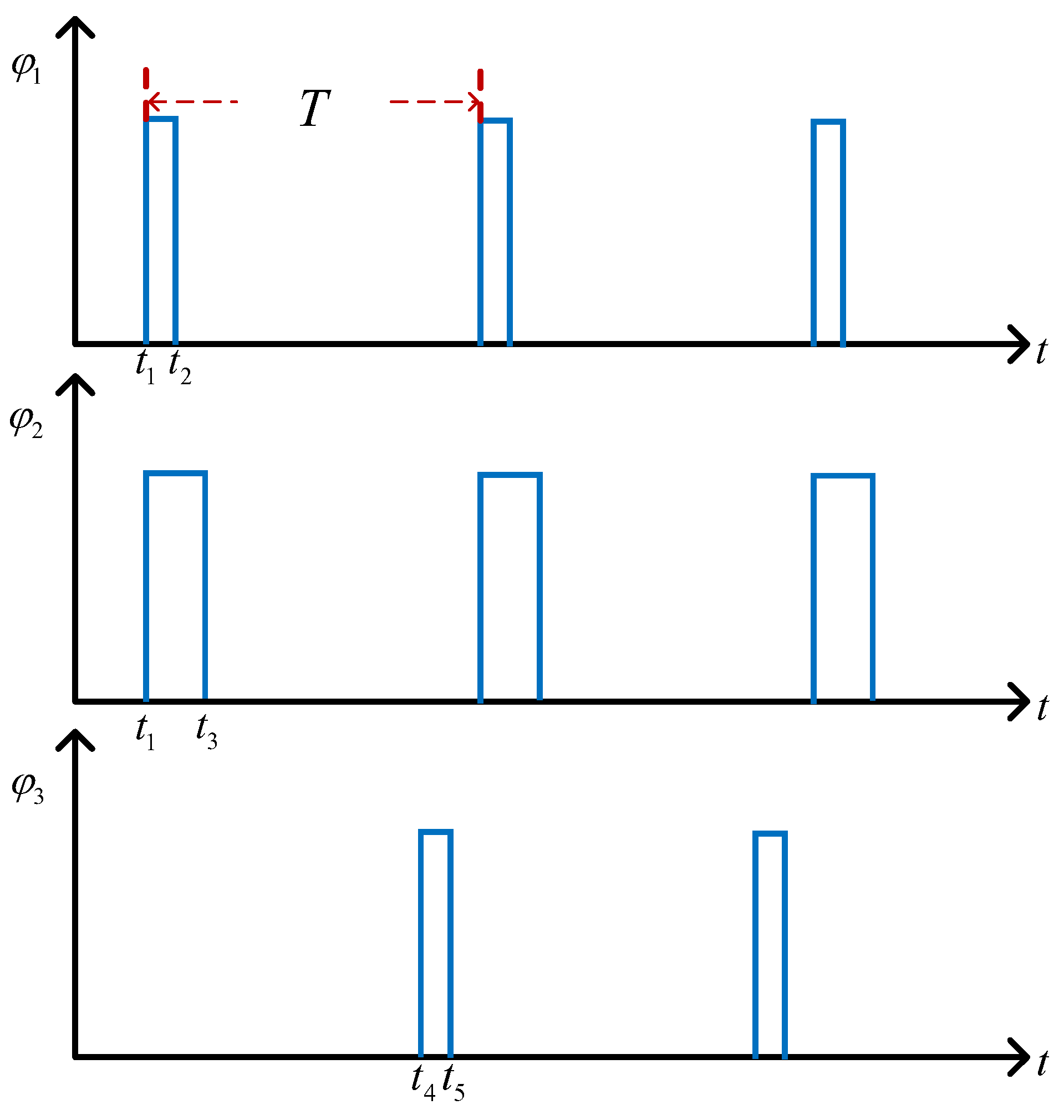

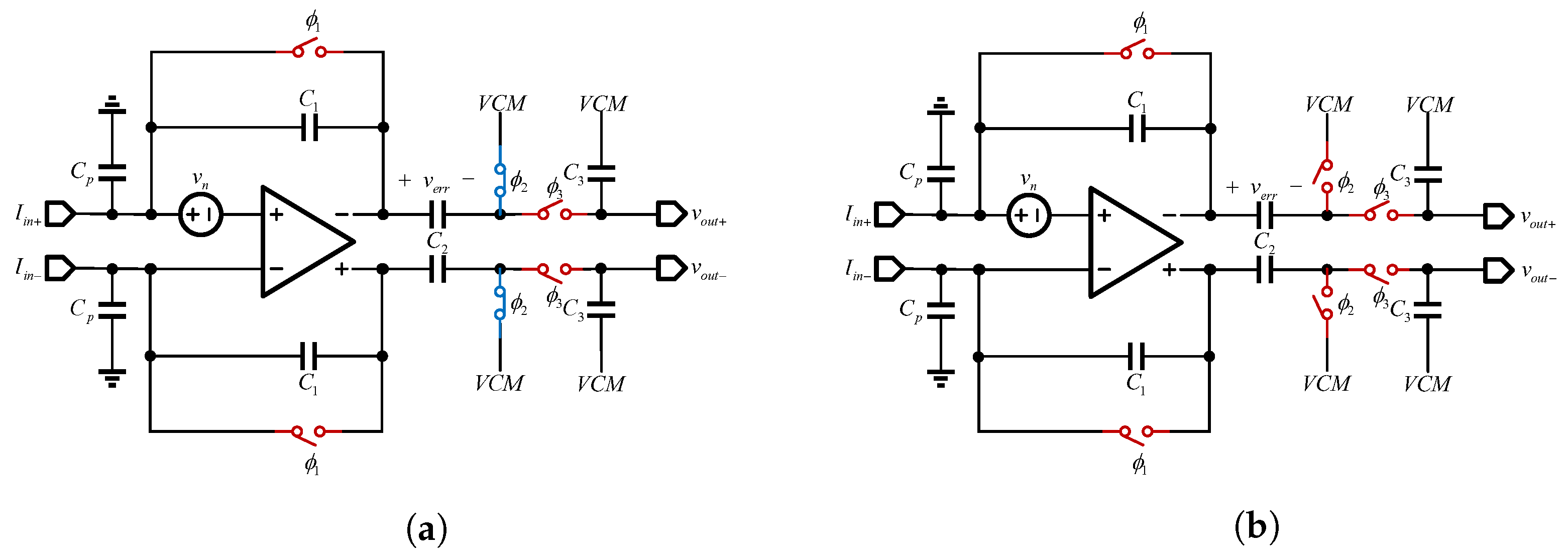

2.2. The Introduction to SCTIA

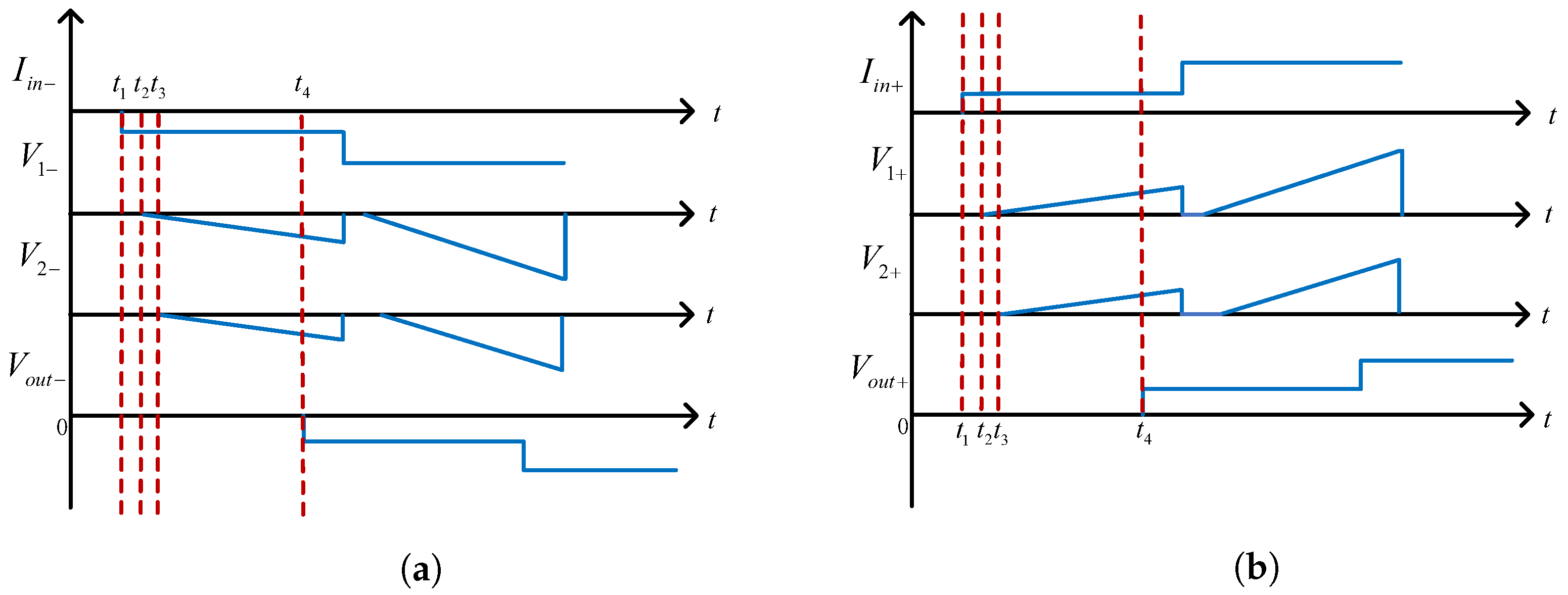

2.3. Correlated Double Sampling

3. Detailed Analysis

3.1. The Charge Distribution Model

3.2. Equivalent Load Capacitance

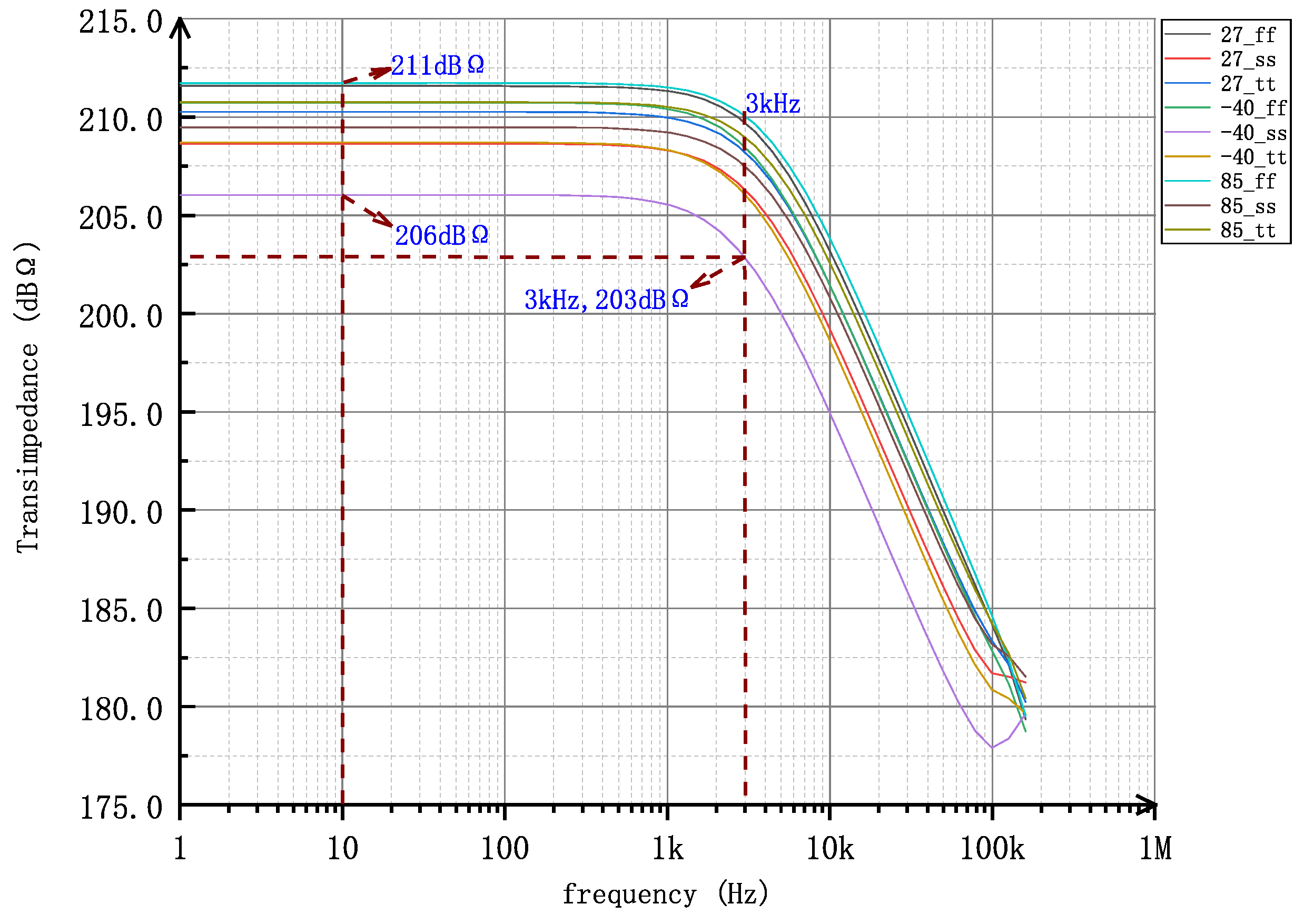

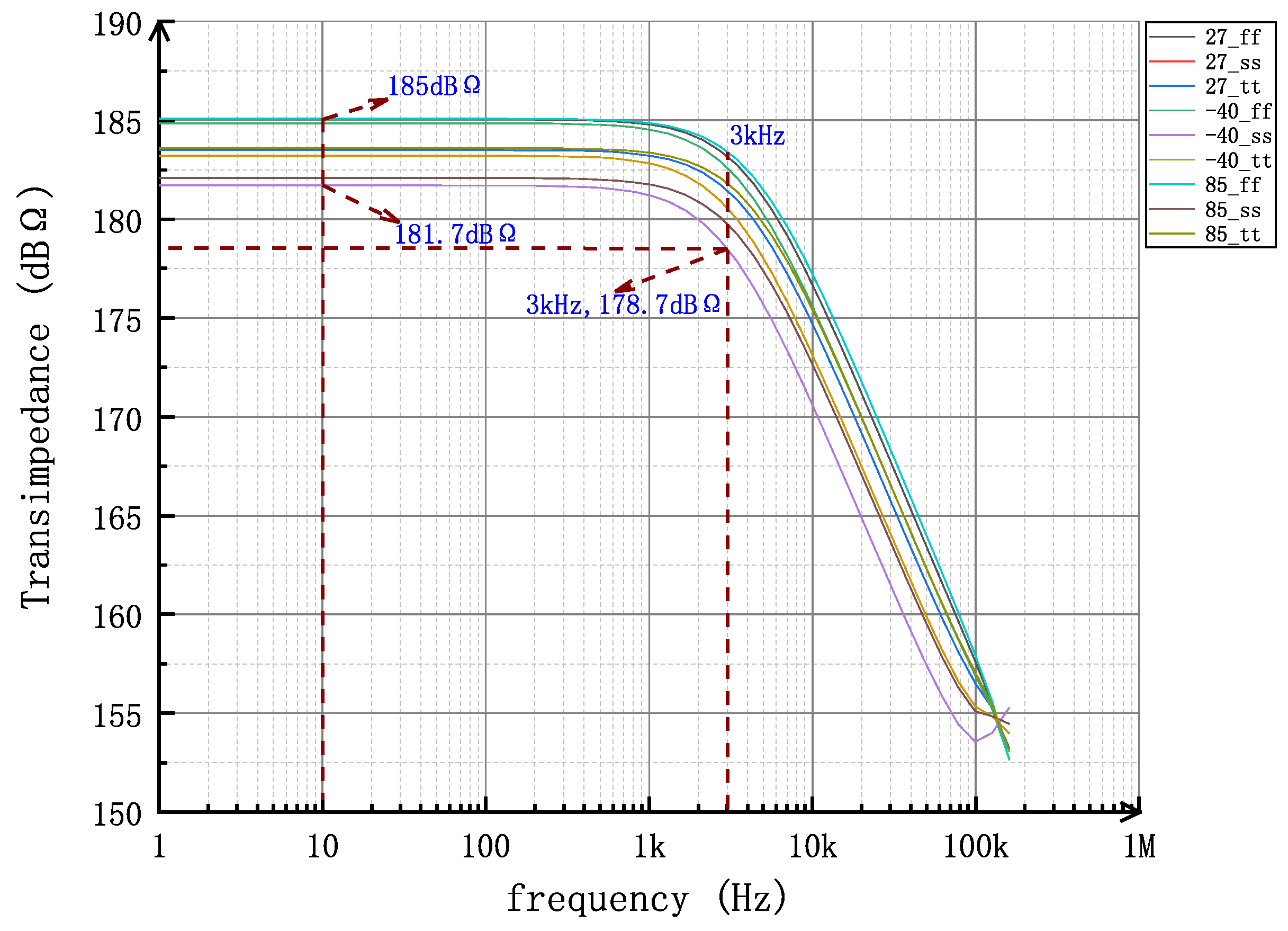

3.3. Analysis of Bandwidth

3.4. Analysis of Leakage Current

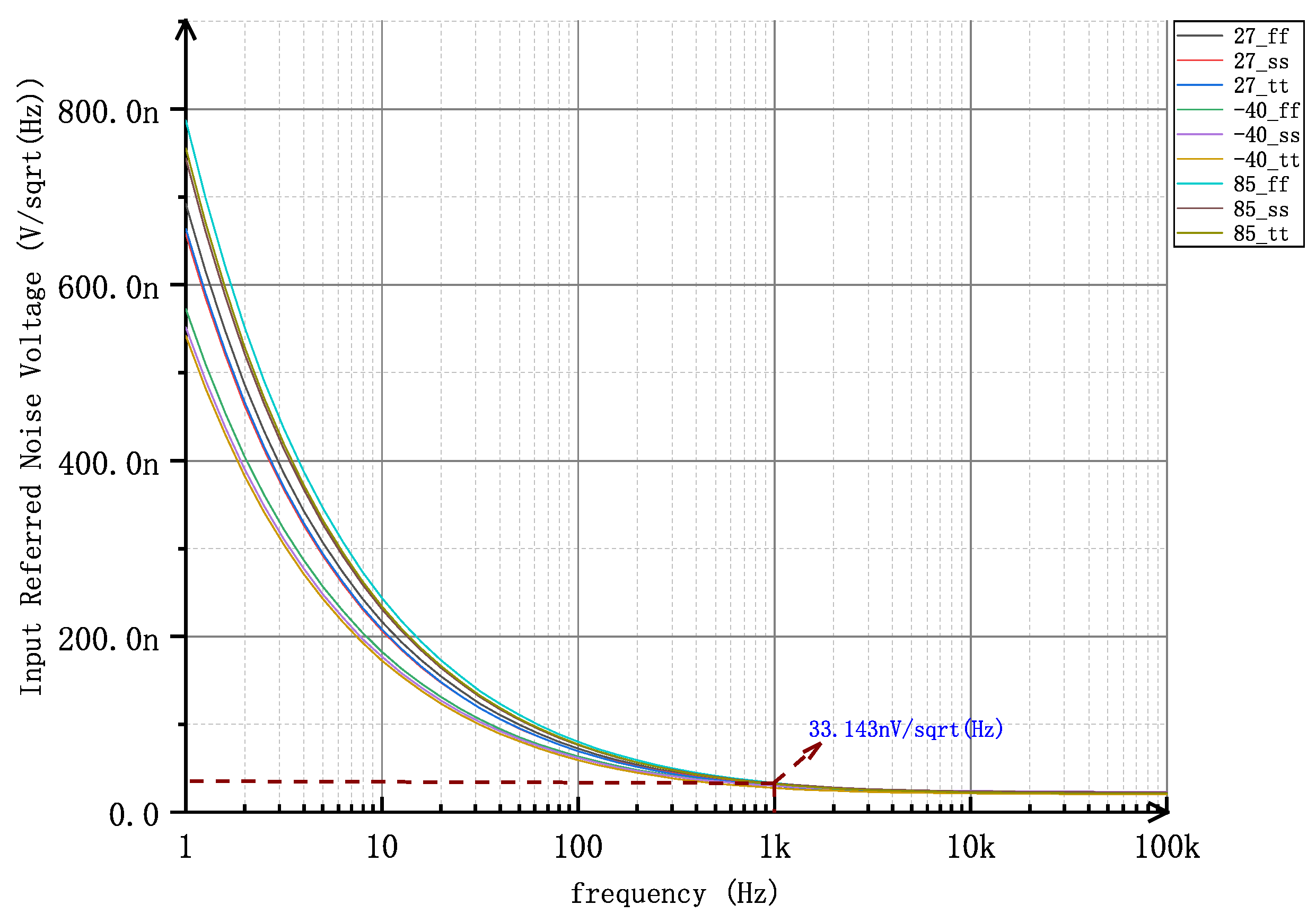

3.5. Effects of the Operational Amplifier on TIA

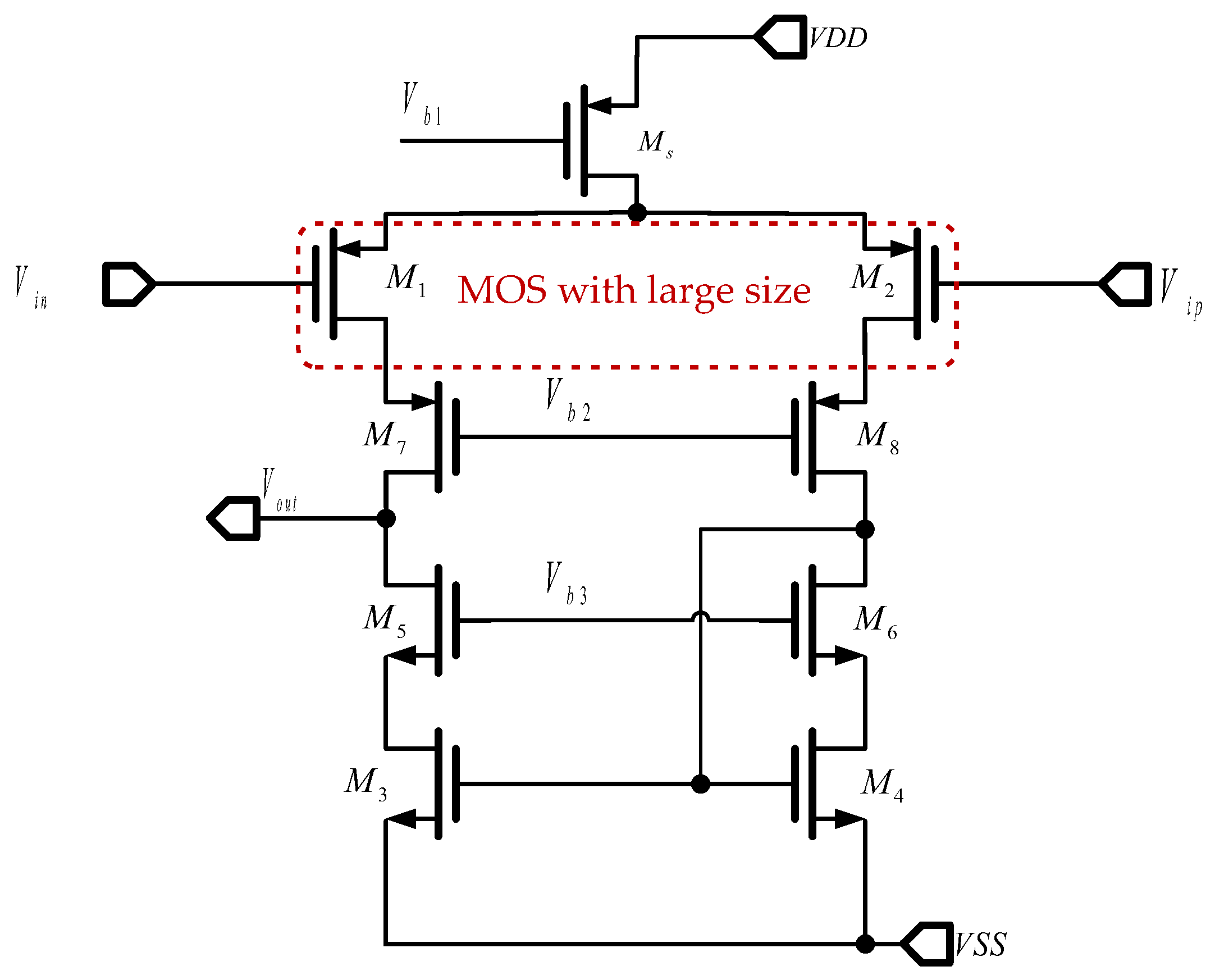

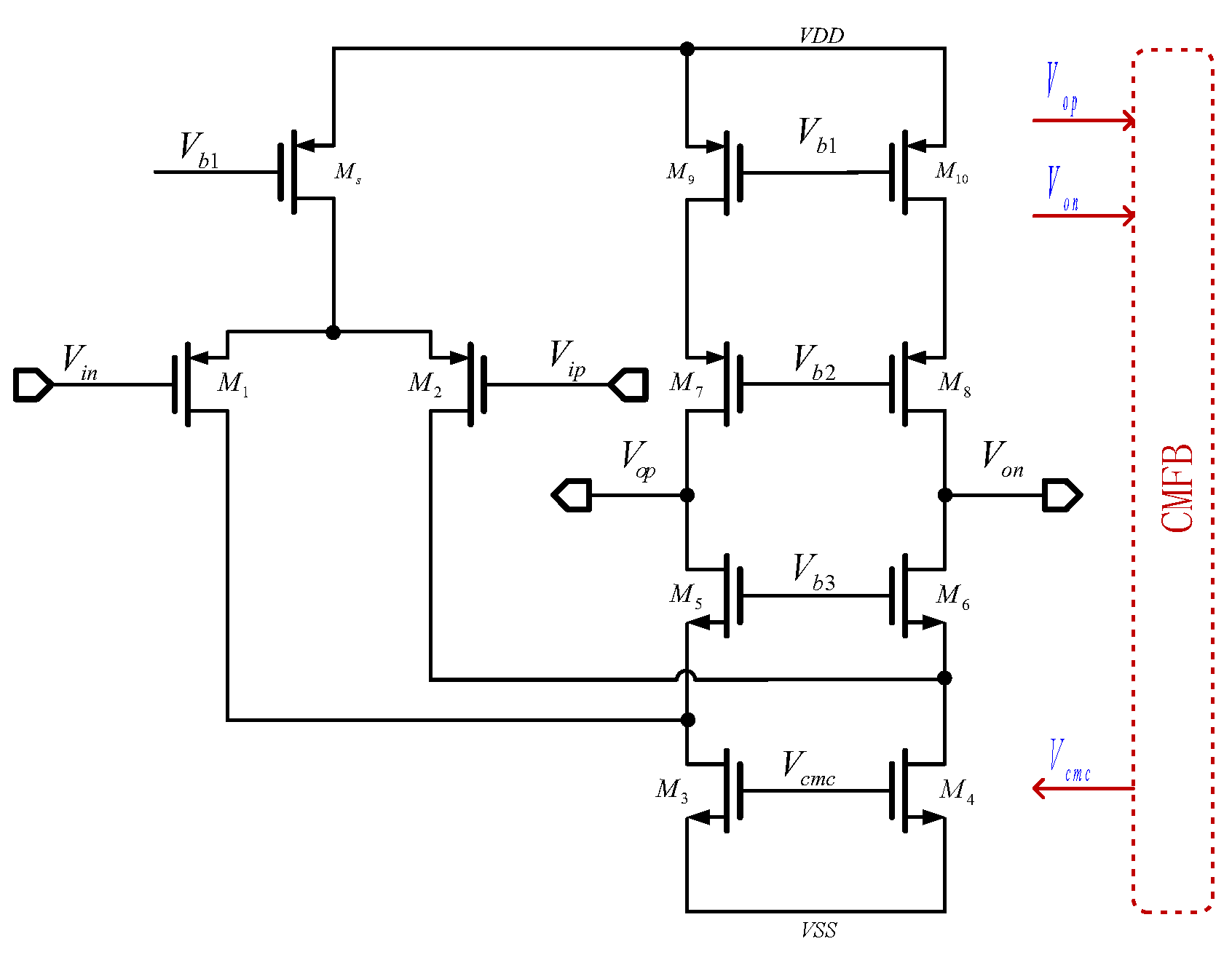

3.6. Buffer Design

4. Result and Analysis

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| ADC | Analog to Digital Converter |

| MCU | Micro Control Unit |

| DSP | Digital Signal Processor |

| TIA | Transimpedance amplifier |

| SCTIA | Switched-capacitor transimpedance amplifier |

| Opamp | Operational amplifier |

| GBW | Gain-Bandwidth product |

| CDS | Correlated double sampling |

| ESD | Electro-Static Discharge |

| KCL | Kirchhoff’s Current Law |

| CT-TIAs | Continuous type trans-impedance amplifiers |

| DT-TIAs | Discrete type trans-impedance amplifiers |

| PSS | Periodic Steady State |

| PAC | Periodic Alternating Current |

| PNOISE | Periodic Noise |

References

- Kim, S.; Hwang, D.H.; Lee, H.; Han, S.K.; Cho, S. The effect of Micro-current electrical stimulation on muscle atrophy caused by sciatic nerve compression. In Proceedings of the 2019 International Conference on Electronics, Information, and Communication (ICEIC 2019), Auckland, New Zealand, 22–25 January 2019. [Google Scholar]

- Lagoumintzis, G.; Sideris, S.K.M.P.K.K.C.R.H. Wireless Micro Current Stimulation technology improves firework burn healing: Clinical applications of WMCS technology. In Proceedings of the 2014 4th International Conference on Wireless Mobile Communication and Healthcare—Transforming Healthcare Through Innovations in Mobile and Wireless Technologies (MOBIHEALTH 2014), Athens, Greece, 3–5 November 2014; pp. 172–175. [Google Scholar]

- Farwell, L.A.; Richardson, D.R.G.F.J. Brain fingerprinting classification concealed information test detects US Navy military medical information with P300. In Proceedings of the FNINS. 2014. Available online: https://www.frontiersin.org/articles/10.3389/fnins.2014.00410/full (accessed on 1 May 2022).

- Ying, M.; Li, Z. Analysis of current situation of the frequent food safety accidents and its reasons in China. In Proceedings of the 2011 International Conference on Computer Science and Service System (CSSS 2011), Nanjing, China, 27–29 June 2011; pp. 3864–3867. [Google Scholar] [CrossRef]

- Ullah, M.N.; Park, Y.; Kim, G.B.; Kim, C.; Park, C.; Choi, H.; Yeom, J.Y. Simultaneous Acquisition of Ultrasound and Gamma Signals with a Single-Channel Readout. Sensors 2021, 21, 1048. [Google Scholar] [CrossRef]

- Garrou, P. Wafer level chip scale packaging (WL-CSP): An overview. TADVP 2000, 23, 198–205. [Google Scholar] [CrossRef]

- Li, D.; Minoia, G.; Repossi, M.; Baldi, D.; Temporiti, E.; Mazzanti, A.; Svelto, F.D. A Low-Noise Design Technique for High-Speed CMOS Optical Receivers. IEEE J. Solid State Circuits 2014, 49, 1437–1447. [Google Scholar] [CrossRef]

- Park, S.M.; Yoo, H.J.D. 1.25-Gb/s regulated cascode CMOS transimpedance amplifier for Gigabit Ethernet applications. IEEE J. Solid State Circuits 2004, 39, 112–121. [Google Scholar] [CrossRef] [Green Version]

- Ferrari, G.; Gozzini, F.; Molari, A.; Sampietro, M. Transimpedance Amplifier for High Sensitivity Current Measurements on Nanodevices. IEEE J. Solid State Circuits 2009, 44, 1609–1616. [Google Scholar] [CrossRef]

- Sackinger, E.; Circuits, E.D. The Transimpedance Limit. IEEE Trans. Circuits Syst. Regul. Pap. 2010, 57, 1848–1856. [Google Scholar] [CrossRef]

- Lei, K.; Heidari, H.; Mak, P.; Law, M.; Maloberti, F. Exploring the noise limits of fully-differential micro-watt transimpedance amplifiers for Sub-pA/yHz sensitivity. In Proceedings of the 2015 11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME 2015), Glasgow, UK, 29 June–2 July 2015; pp. 290–293. [Google Scholar] [CrossRef]

- Salvia, J.; Lajevardi, P.; Hekmat, M.; Murmann, B. A 56MΩ CMOS TIA for MEMS applications. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC 2009), San Jose, CA, USA, 13–16 September 2009. [Google Scholar]

- Ferrari, G.; Gozzini, F.; Sampietro, M. A Current-Sensitive Front-End Amplifier for Nano-Biosensors with a 2MHz BW. In Proceedings of the Solid-State Circuits Conference, ISSCC 2007, San Francisco, CA, USA, 11–15 February 2007; Digest of Technical Papers. IEEE International: Piscataway, NJ, USA, 2007. [Google Scholar]

- Bianchi, D.; Ferrari, G.; Rottigni, A.; Sampietro, M. CMOS Impedance Analyzer for Nanosamples Investigation Operating up to 150 MHz With Sub-aF Resolution. IEEE J. Solid State Circuits 2014, 49, 2748–2757. [Google Scholar] [CrossRef]

- Chuah, J.H.; Holburn, D. Design of Low-Noise High-Gain CMOS Transimpedance Amplifier for Intelligent Sensing of Secondary Electrons. IEEE Sens. J. 2015, 15, 5997–6004. [Google Scholar] [CrossRef]

- Tajalli, A.; Leblebici, Y.; Brauer, E.J. Implementing ultra-high-value floating tunable CMOS resistors. Electron. Lett. 2008, 44, 349–350. [Google Scholar] [CrossRef] [Green Version]

- Djekic, D.; Fantner, G.; Behrends, J.; Lips, K.; Ortmanns, M.; Anders, J. A transimpedance amplifier using a widely tunable PVT-independent pseudo-resistor for high-performance current sensing applications. In Proceedings of the 43rd IEEE European Solid State Circuits Conference(ESSCIRC 2017), Leuven, Belgium, 11–14 September 2017; pp. 79–82. [Google Scholar] [CrossRef] [Green Version]

- Crescentini, M.; Bennati, M.; Carminati, M.; Tartagni, M. Noise Limits of CMOS Current Interfaces for Biosensors: A Review. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 278–292. [Google Scholar] [CrossRef]

- Djekic, D.; Häberle, M.; Mohamed, A.; Baumgärtner, L.; Anders, J. A 440-kOhm to 150-GOhm Tunable Transimpedance Amplifier based on Multi-Element Pseudo-Resistors. In Proceedings of the 2021 IEEE 47th European Solid State Circuits Conference (ESSCIRC 2021), Grenoble, France, 13–22 September 2021; pp. 403–406. [Google Scholar] [CrossRef]

- Tang, Y.; Zhang, Y.; Fedder, G.K.; Carley, L.R. A Dual Probe STM Imaging System and a Low Noise Switched-Capacitor Transimpedance Amplifier. IEEE Sens. J. 2013, 13, 2984–2992. [Google Scholar] [CrossRef]

- Kim, D.; Goldstein, B.; Tang, W.; Sigworth, F.J.; Culurciello, E. Noise Analysis and Performance Comparison of Low Current Measurement Systems for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 52–62. [Google Scholar] [CrossRef]

- Del Rio, R.; Medeiro, F. Reliable analysis of settling errors in SC integrators: Application to ΣΔ modulators. ELL 2000, 36, 503–504. [Google Scholar] [CrossRef]

- Saxena, S.; Akashe, S. Design of Low Leakage Current Average Power CMOS Current Comparator Using SVL Technique. In Proceedings of the 2015 Fifth International Conference on Advanced Computing and Communication Technologies (ACCT 2015), Haryana, India, 21–22 February 2015. [Google Scholar]

- Linares-Barranco, B.; Serrano-Gotarredona, T. On the design and characterization of femtoampere current-mode circuits. IEEE J. Solid State Circuits 2003, 38, 1353–1363. [Google Scholar] [CrossRef]

- Saad, S.; Tan, C.L.; Othman, M.A.; Holger, P.; Herman, S.H. A study of fluorine implant in the formation of low leakage P+/N junction in BiCMOS technologies. In Proceedings of the International Conference on Enabling Science and Nanotechnology, Johor Bahru, Malaysia, 5–7 January 2012. [Google Scholar]

- Erouel, M.; Diallo, A.K.; Ly, E.; Seck, M. Humidity Sensor Using Subthreshold Regime of Flexible Organic Field Effect Transistor: Concomitant Effect of Gate Leakage Current and Semiconductor Conductivity. In Proceedings of the 2019 IEEE International Conference on Design and Test of Integrated Micro and Nano-Systems (DTS 2019), Gammarth, Tunisia, 28 April–1 May 2019. [Google Scholar]

- Bai, N.; Hu, Z.; Wang, Y.; Xu, Y. Leakage Current Stability Analysis for Subthreshold SRAM. Electronics 2022, 11, 1196. [Google Scholar] [CrossRef]

- Olivera, F.; Petraglia, A. Analytic Modeling of Static Noise Margin Considering DIBL and Body Bias Effects. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS 2017), Baltimore, MD, USA, 28–31 May 2017. [Google Scholar]

- Reddy, A.M.; Harish, B.P. Process Variation-Aware Analytical Modeling of Subthreshold Leakage Power. In Proceedings of the 29th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS 2019), Rhodes, Greece, 1–3 July 2019. [Google Scholar]

- Juszkiewicz, R. Rarely Asked Questions-Issue 161: A New Spin on a Classic Architecture: Achieving a Fully Differential Output Using Single-Ended Instrumentation Amplifiers. In Proceedings of the Analog Dislogue, San Luis Obispo, CA, USA, 26–30 August 2019; p. Issue 53–01. [Google Scholar]

- Rad, R.E.; Hejazi, A.; Pu, Y.; Lee, K.Y. A Dual-Mode Adjustable High-Gain Ultra-Low Noise Transimpedance Amplifier for Fine Dust Detection. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS 21), Seville, Spain, 12–14 October 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Chaddad, A.; Tanougast, C. Low-noise transimpedance amplifier dedicated to biomedical devices: Near infrared spectroscopy system. In Proceedings of the 2014 International Conference on Control, Decision and Information Technologies (CoDIT 2014), Metz, France, 3–5 November 2014; pp. 601–604. [Google Scholar] [CrossRef]

- Sharma, A.; Zaman, M.F.; Ayazi, F. A 104-dB Dynamic Range Transimpedance-Based CMOS ASIC for Tuning Fork Microgyroscopes. IEEE J. Solid State Circuits 2007, 42, 1790–1802. [Google Scholar] [CrossRef]

- Di Patrizio Stanchieri, G.; De Marcellis, A.; Battisti, G.; Faccio, M.; Palange, E.; Guler, U. A 1.8 V Low-Power Low-Noise High Tunable Gain TIA for CMOS Integrated Optoelectronic Biomedical Applications. Electronics 2022, 11, 1271. [Google Scholar] [CrossRef]

- Djekic, D.; Fantner, G.; Lips, K.; Ortmanns, M.; Anders, J. A 0.1Temperature-Compensated Transimpedance Amplifier Using a Multi-Element Pseudo-Resistor. IEEE J. Solid State Circuits 2018, 53, 1913–1923. [Google Scholar] [CrossRef]

- Kim, J.; Maitra, R.; Pedrotti, K.D.; Dunbar, W.B. A Patch-Clamp ASIC for Nanopore-Based DNA Analysis. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 285–295. [Google Scholar] [CrossRef] [PubMed]

- Karami Horestani, F.; Karami Horastani, Z.; Björsell, N. A Band-Pass Instrumentation Amplifier Based on a Differential Voltage Current Conveyor for Biomedical Signal Recording Applications. Electronics 2022, 11, 1087. [Google Scholar] [CrossRef]

- Kamrani, E.; Lesage, F.; Sawan, M. Low-Noise, High-Gain Transimpedance Amplifier Integrated With SiAPD for Low-Intensity Near-Infrared Light Detection. IEEE Sens. J. 2014, 14, 258–269. [Google Scholar] [CrossRef]

| This Work | IEEE J. Solid State Circuits [11] | ISCAS [31] | Sensors [20] | CoDIT [32] | IEEE J. Solid State Circuits [33] | Electronics [34] | IEEE J. Solid State Circuits [35] | |

|---|---|---|---|---|---|---|---|---|

| Bandwidth/MHz | 4 | 1 | 10 | 0.555 | 2 | |||

| Input referred noise/ | 2.69 | 4 | 27 | 25 | 500 | − | 390 | 140 |

| DC gain/dBΩ | 206 | 153 | 148.9 | 158 | 104.1 | 148 | 124 | 120 |

| Power/mW | 0.643 | 45 | 2.71 | 3.2 | 0.71 | 0.4 | 0.0361 | 9.5 |

| Technology | 0.18 | 0.35 | 0.18 | 0.35 | 0.18 | 0.6 | 0.18 | 0.18 |

| Circuit Type | DT | CT | CT | DT | CT | DT | CT | CT |

| Result | Simulated | Measured | Simulated | Measured | Simulated | Measured | Simulated | Measured |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, D.; Chen, Q.; Li, Z.; Shan, Q.; Wei, Z.; Xiao, J.; Huang, S. The Design of a Low Noise and Low Power Current Readout Circuit for Sub-pA Current Detection Based on Charge Distribution Model. Electronics 2022, 11, 1791. https://doi.org/10.3390/electronics11111791

Jiang D, Chen Q, Li Z, Shan Q, Wei Z, Xiao J, Huang S. The Design of a Low Noise and Low Power Current Readout Circuit for Sub-pA Current Detection Based on Charge Distribution Model. Electronics. 2022; 11(11):1791. https://doi.org/10.3390/electronics11111791

Chicago/Turabian StyleJiang, Dahai, Qinan Chen, Zheng Li, Qiang Shan, Zihui Wei, Jinjin Xiao, and Shuilong Huang. 2022. "The Design of a Low Noise and Low Power Current Readout Circuit for Sub-pA Current Detection Based on Charge Distribution Model" Electronics 11, no. 11: 1791. https://doi.org/10.3390/electronics11111791

APA StyleJiang, D., Chen, Q., Li, Z., Shan, Q., Wei, Z., Xiao, J., & Huang, S. (2022). The Design of a Low Noise and Low Power Current Readout Circuit for Sub-pA Current Detection Based on Charge Distribution Model. Electronics, 11(11), 1791. https://doi.org/10.3390/electronics11111791