Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System

Abstract

1. Introduction

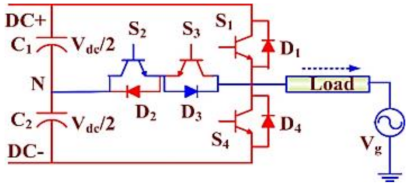

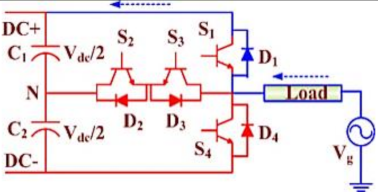

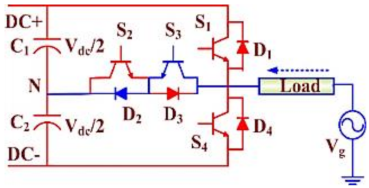

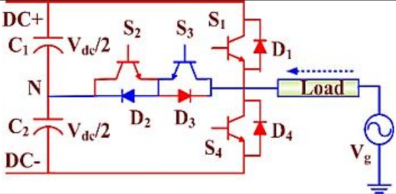

2. Analysis of Transformer-Less Multilevel NPC-MLI

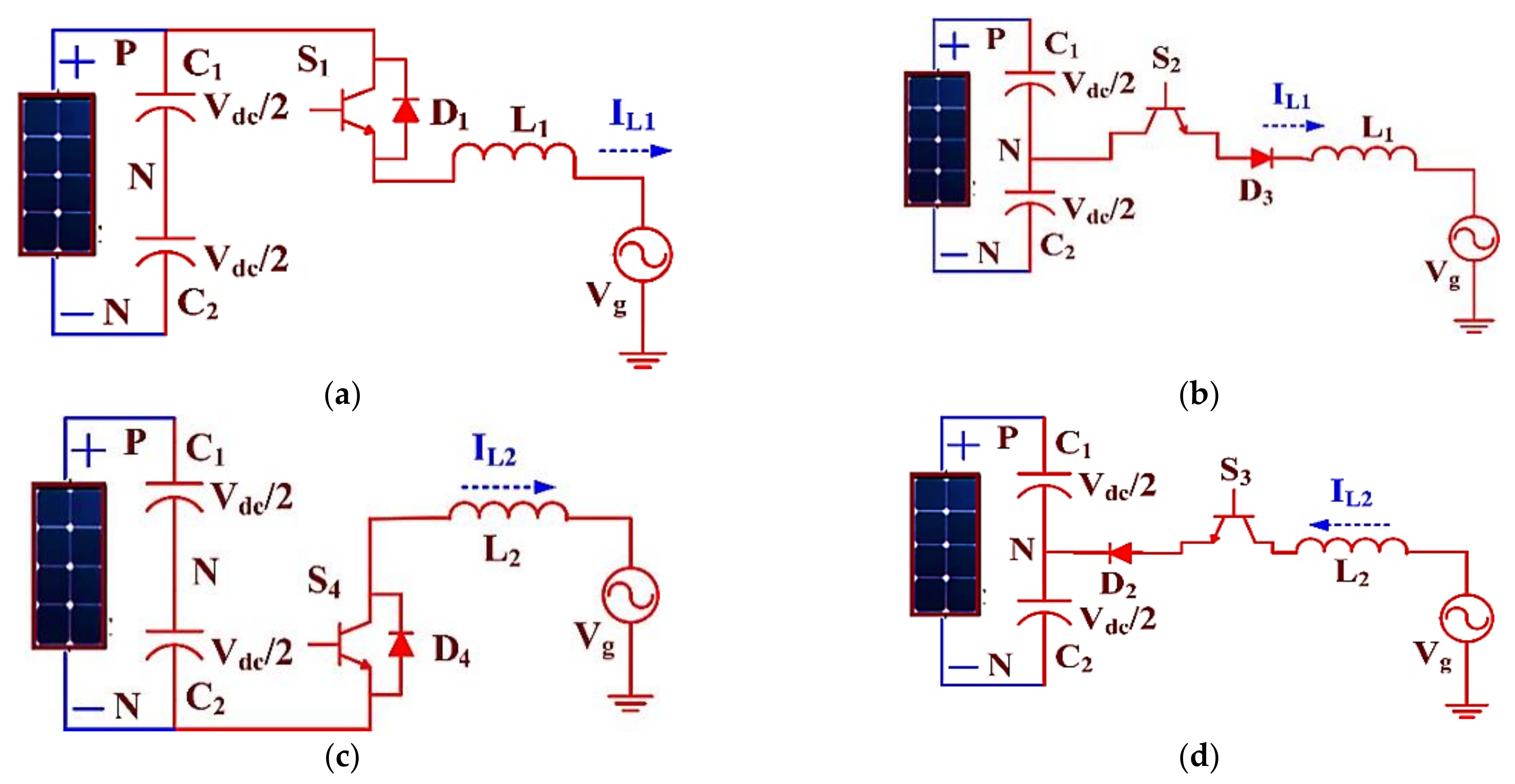

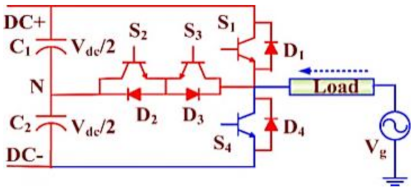

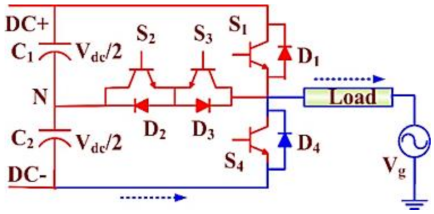

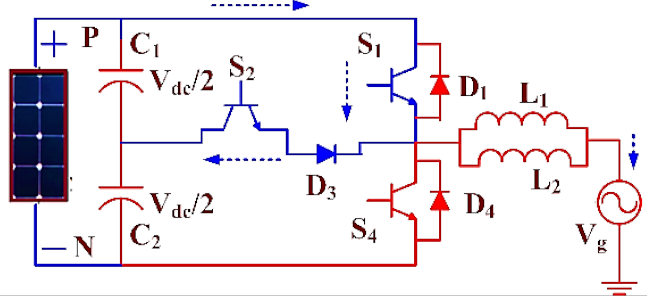

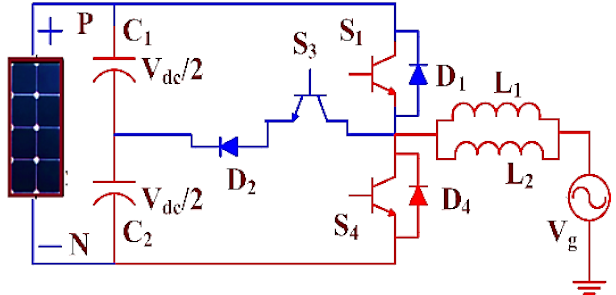

2.1. Single-Phase Three-Level Transformer-Less Multilevel NPC-MLI

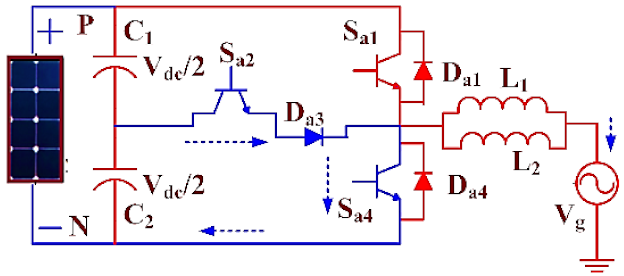

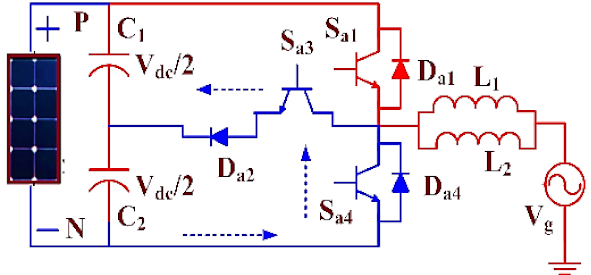

2.2. Single Modes of Operation in PV-Tied Single-Phase Three-Level Transformer-Less TNP-MLI Topology

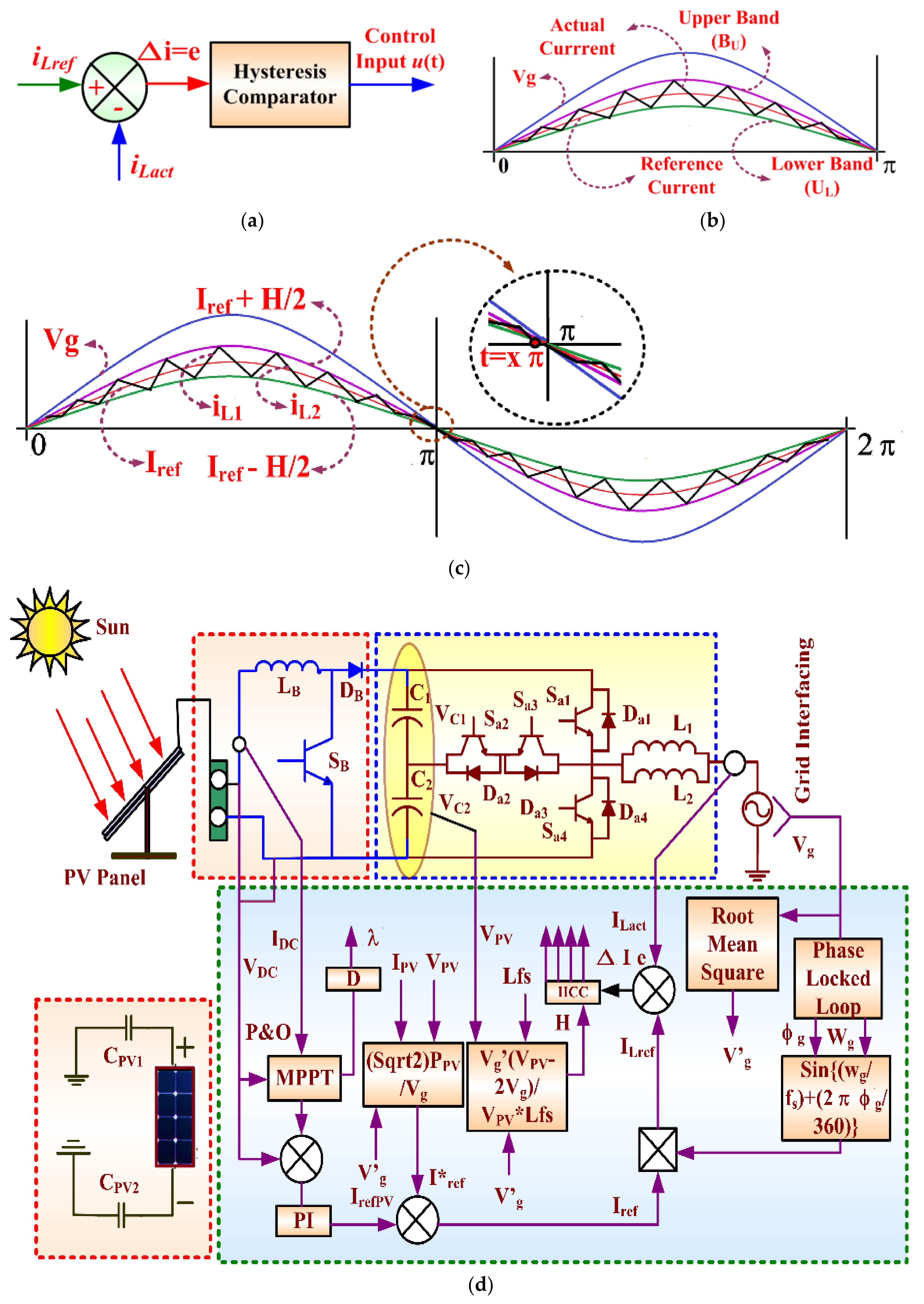

3. Control System of PV Grid Tired Connected Transformer-Less TNP-MLI

3.1. Design

3.2. Closed-Loop PV Tie Grid-Connected Control Strategy of Proposed Transformer-Less TNP-MLI

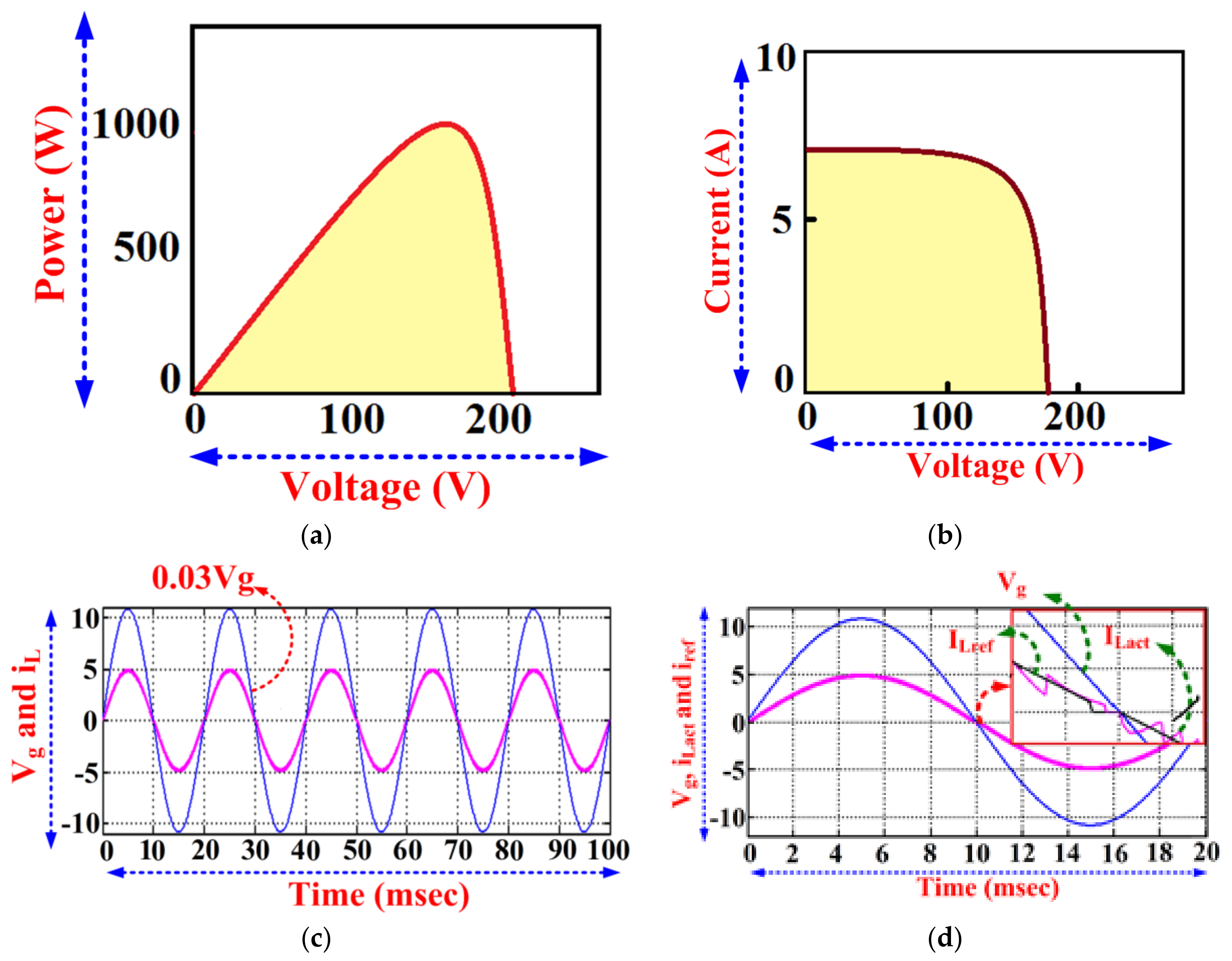

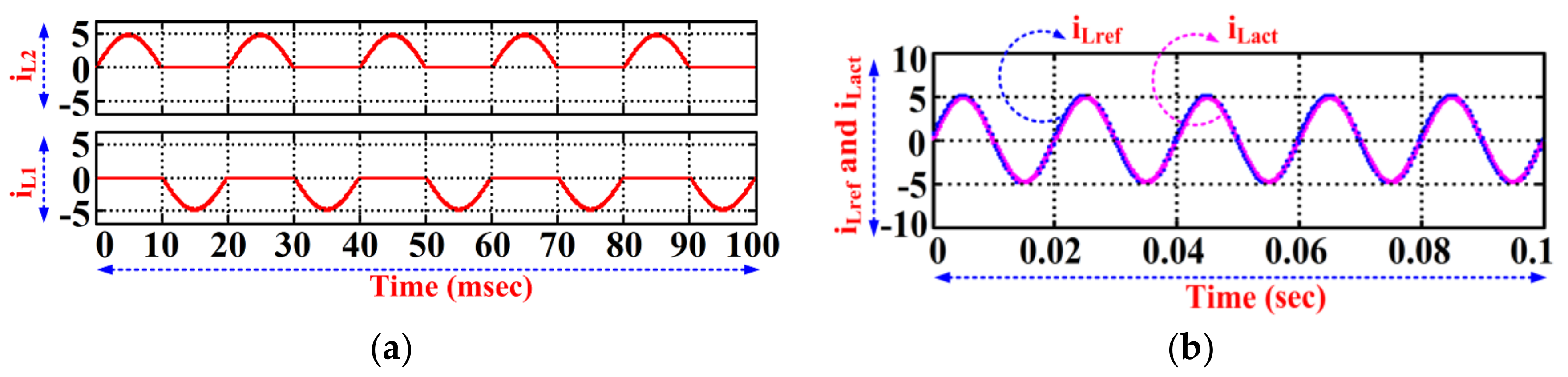

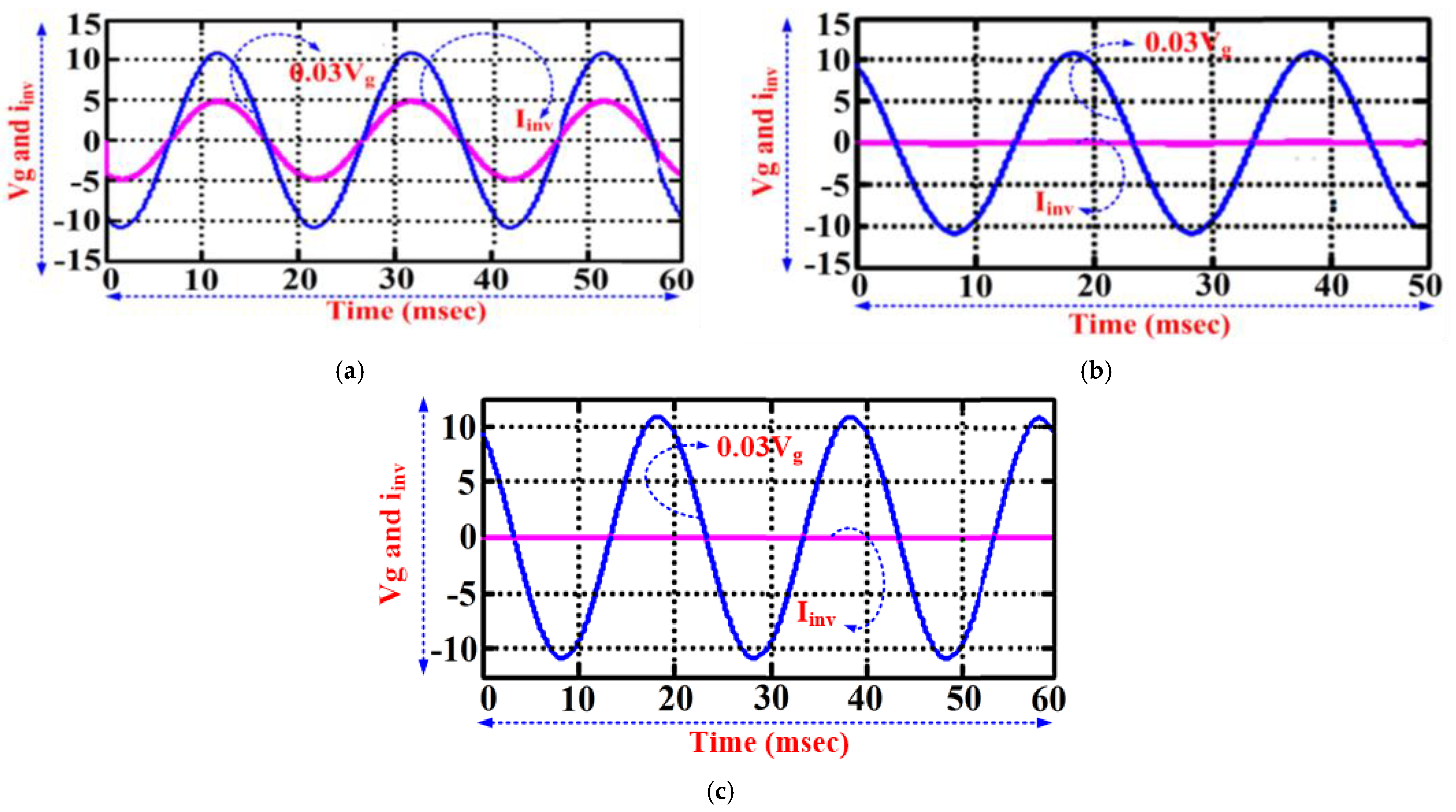

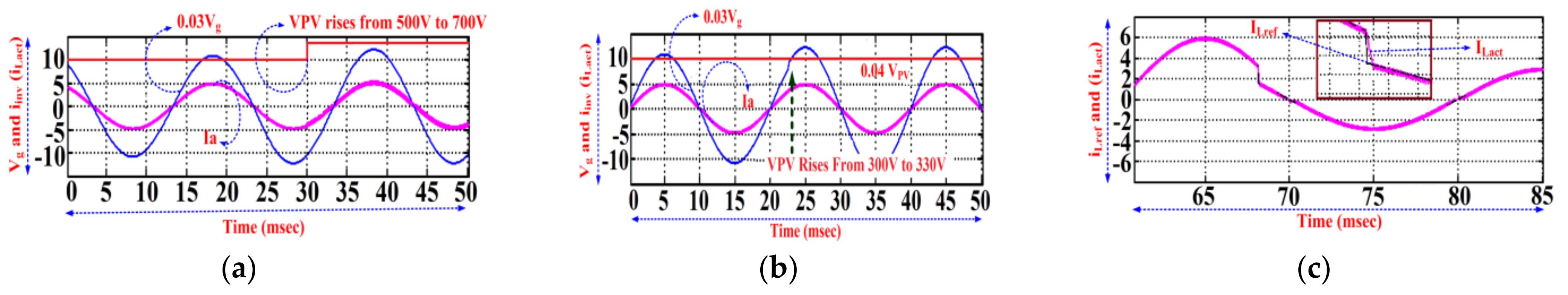

4. Numerical Simulation Results

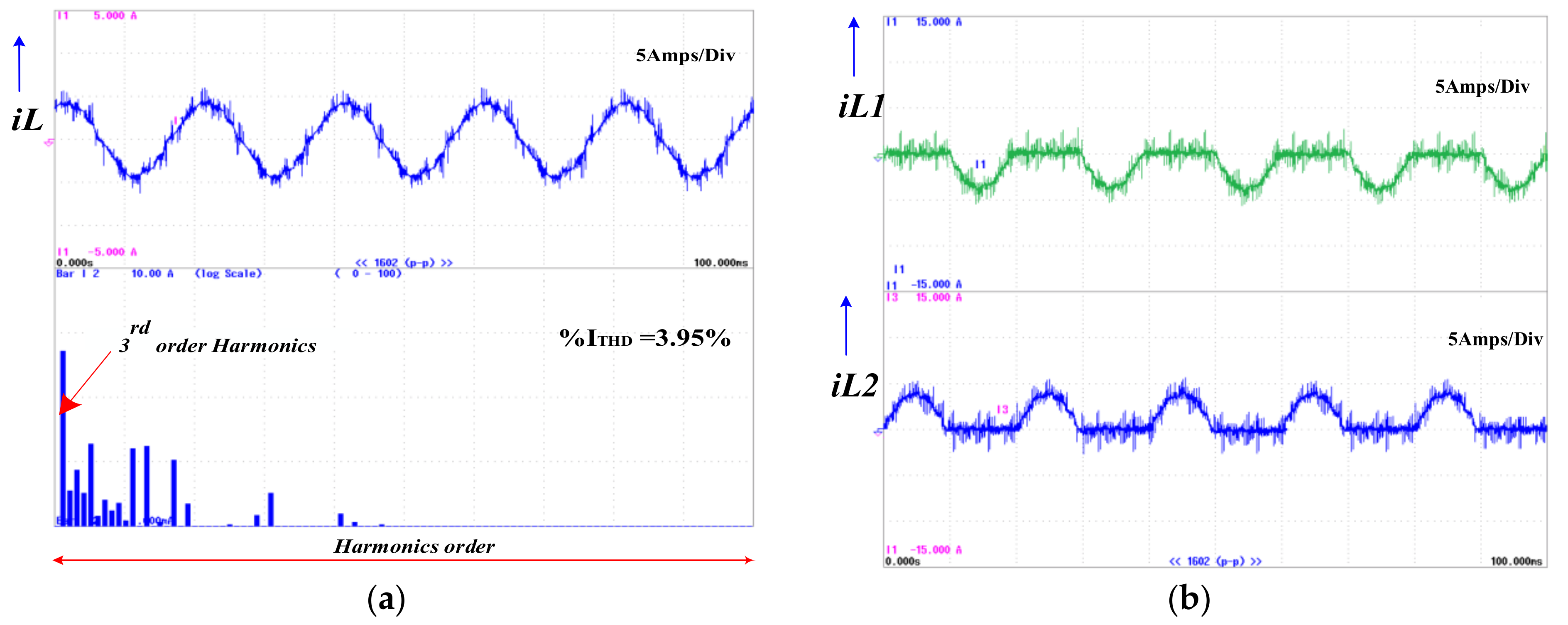

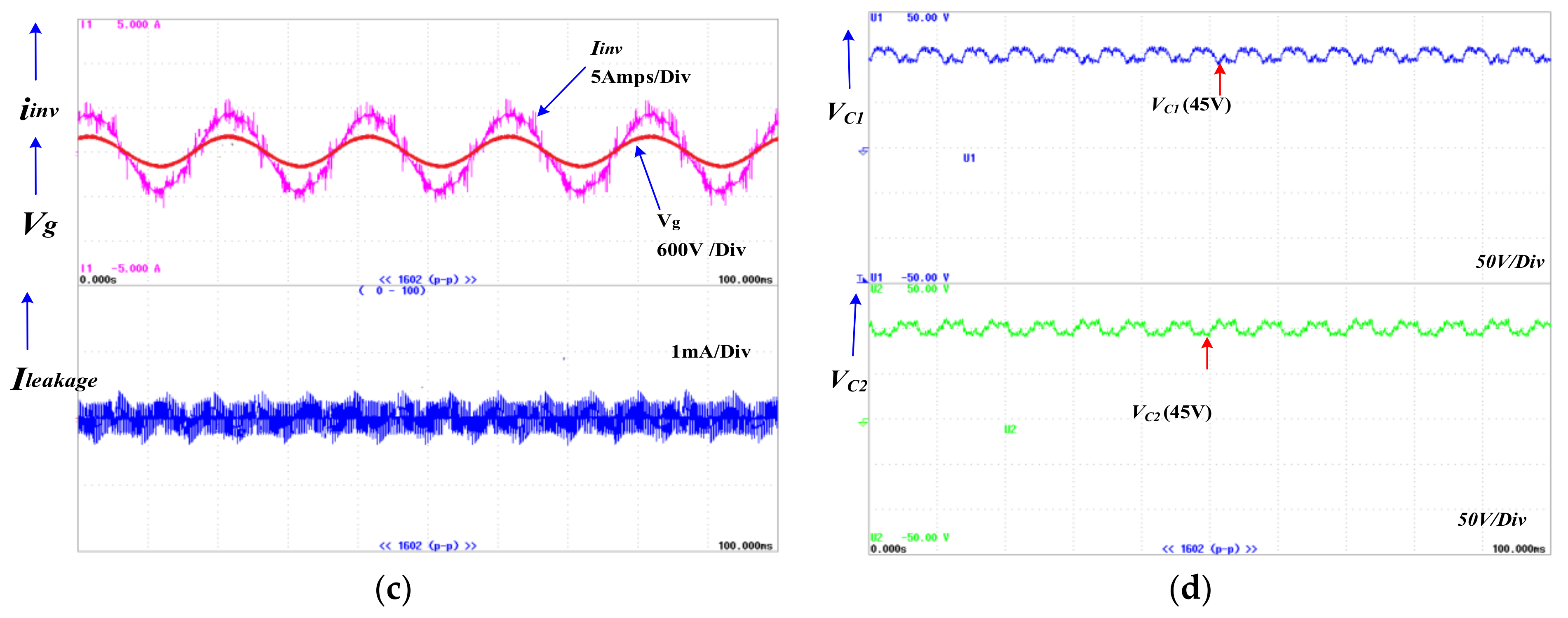

5. Hardware Implementation and Experimental Result

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ϴg | grid angle |

| ΔLie | error of inductor current |

| fs | Switching Frequency |

| iact | Actual Current |

| iL | Inductor Current |

| iLref | Reference current |

| iLact | Actual Current |

| iref | Reference Current |

| VCM-DM | Total Common-Mode Voltage and Differential Mode Voltage |

| VPV | Output Voltage Of PV |

| VTCM | Transformer less Common-Mode Voltage |

| CMV(VCM) | Common Mode Voltage |

| CPV | Parasitic Capacitance |

| DB-HBI | Dual-Buck Half-Bridge Inverter |

| DMV(VDM) | Differential Mode Voltage |

| FWD | Free Wheeling Diode |

| HCC | Hysteresis Current Controls |

| IGBT | Insulated Gate Bipolar Transistor |

| MLI | Multi-Level Inverter |

| MPPT | Maximum Power Point Tracking |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| NEC | National Electrical Code |

| NPC | Neutral Point Clamped |

| PLL | Phase Locked Loop |

| P&O | Perturb & Observe |

| SDPF | Switching Device Power Factor |

| TL | Transformer Less |

| TNP | T’ Type NPC |

| ZCD | Zero-Crossing Detection |

References

- Yu, H.J.J.; Popiolek, N.; Geoffron, P. Solar photovoltaic energy policy and globalization: A multiperspective approach with case studies of Germany, Japan, and China. Prog. Photovolt. Res. Appl. 2014, 24, 458–476. [Google Scholar] [CrossRef]

- Makrides, G.; Zinsser, B.; Norton, M.; Georghiou, G.E.; Schubert, M.; Werner, J.H. Potential of photovoltaic systems in countries with high solar irradiation. Renew. Sustain. Energy Rev. 2010, 14, 754–762. [Google Scholar] [CrossRef]

- Zeb, K.; Islam, S.U.; Din, W.U.; Khan, I.; Ishfaq, M.; Busarello, T.D.C.; Kim, H.J. Design of Fuzzy-PI and Fuzzy-Sliding Mode Controllers for Single-Phase Two-Stages Grid-ConnectedTransformerless Photovoltaic Inverter. Electronics 2019, 8, 520. [Google Scholar] [CrossRef]

- Kjaer, S.B.; Pedersen, K.; Blaabjerg, F. A Review of Single-Phase Grid-Connected Inverters for Photovoltaic Modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Koutroulis, E.; Blaabjerg, F. Design Optimization of Transformerless Grid-Connected PV Inverters Including Reliability. IEEE Trans. Power Electron. 2013, 28, 325–335. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Klumpner, C.; Sumner, M.; Floricau, D.; Rodriguez, P. Evaluation of three-phase transformerless photovoltaic inverter topologies. Eur. Conf. Power Electron. Appl. 2007, 24, 2202–2211. [Google Scholar] [CrossRef]

- Li, W.; Gu, Y.; Luo, H.; Cui, W.; He, X.; Xia, C. Topology Review and Derivation Methodology of Single-Phase Transformerless Photovoltaic Inverters for Leakage Current Suppression. IEEE Trans. Ind. Electron. 2015, 62, 4537–4551. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Rocabert, J.; Rodriguez, P.; Alepuz, S.; Bordonau, J. Multilevel Diode-Clamped Converter for Photovoltaic Generators With Independent Voltage Control of Each Solar Array. IEEE Trans. Ind. Electron. 2008, 55, 2713–2723. [Google Scholar] [CrossRef]

- Bharatiraja, C.; Mohan, V.; Jeevananthan, S.; Latha, R. Vector selection approach-based hexagonal hysteresis space vector current controller for a three phase diode clamped MLI with capacitor voltage balancing. IET Power Electron. 2016, 9, 1350–1361. [Google Scholar] [CrossRef]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel Inverter Topologies for Stand-Alone PV Systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Feng, L.; Wu, H.; Xing, Y. A Family of Neutral Point Clamped Full-Bridge Topologies for Transformerless Photovoltaic Grid-Tied Inverters. IEEE Trans. Power Electron. 2013, 28, 730–739. [Google Scholar] [CrossRef]

- Lopez, O.; Teodorescu, R.; Doval-Gandoy, J. Multilevel transformerless topologies for single-phase grid-connected converters. In Proceedings of the IECON 2006-32nd Annual Conference on IEEE Industrial Electronics 2006, Paris, France, 7–10 November 2006. [Google Scholar] [CrossRef]

- Li, J.; Liu, J.; Boroyevich, D.; Mattavelli, P.; Xue, Y. Three-level Active Neutral-Point-Clamped Zero-Current-Transition Converter for Sustainable Energy Systems. IEEE Trans. Power Electron. 2011, 26, 3680–3693. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S. Leakage Current Analytical Model and Application in Single-Phase Transformerless Photovoltaic Grid-Connected Inverter. IEEE Trans. Electromagn. Compat. 2010, 52, 902–913. [Google Scholar] [CrossRef]

- Gonzalez, R.; Gubia, E.; Lopez, J.; Marroyo, L. Transformerless Single-Phase Multilevel-Based Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2008, 55, 2694–2702. [Google Scholar] [CrossRef]

- Zargari, N.R.; Ziogas, D.; Joos, G. A two-switch high-performance current regulated DC/AC converter module. IEEE Trans. Ind. Appl. 1995, 31, 583–589. [Google Scholar] [CrossRef]

- Wang, Y.; Li, R. Novel High-Efficiency Three-Level Stacked-Neutral-Point-Clamped Grid-Tied Inverter. IEEE Trans. Ind. Electron. 2013, 60, 3765–3774. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Borup, U. Transformerless Photovoltaic Inverters Connected to the Grid. In Proceedings of the APEC 07—Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 25 February–1 March 2007. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S. Transformerless Split-Inductor Neutral Point Clamped Three-Level PV Grid-Connected Inverter. IEEE Trans. Power Electron. 2012, 27, 1799–1808. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Padmanaban, S.; Blaabjerg, F.; Wheeler, P. Optimized carrier based multilevel generated modified dual three-phase open-winding inverter for medium power application. In Proceedings of the IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Busan, Korea, 1–4 July 2016. [Google Scholar] [CrossRef]

- Petrella, R.; Buonocunto, N.; Revelant, A.; Stocco, P. DC bus voltage equalization in single-phase split-capacitor three-level neutral-point-clamped half-bridge inverters for PV applications. In Proceedings of the 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. High efficiency drive system with 3-level T-type inverter. In Proceedings of the 14th European Conference on Power Electronics and Applications (EPE), Birmingham, UK, 30 August–1 September 2011. [Google Scholar]

- Park, Y.; Sul, S.-K.; Lim, C.-H.; Kim, W.-C.; Lee, S.-H. Asymmetric Control of DC-Link Voltages for Separate MPPTs in Three-Level Inverters. IEEE Trans. Power Electron. 2013, 28, 2760–2769. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Gubía, E.; Sanchis, P.; Ursúa, A.; López, J.; Marroyo, L. Ground currents in single-phase transformerless photovoltaic systems. Prog. Photovolt. Res. Appl. 2007, 15, 629–650. [Google Scholar] [CrossRef]

- Chokkalingam, B.; Bhaskar, M.S.; Padmanaban, S. Investigations of Multi-Carrier Pulse Width Modulation Schemes for Diode Free Neutral Point Clamped Multilevel Inverters. J. Power Electron. 2019, 19, 702–713. [Google Scholar] [CrossRef]

- Kang, J.-W.; Hyun, S.-W.; Kan, Y.; Lee, H.; Lee, J.-H. A Novel Zero Dead-Time PWM Method to Improve the Current Distortion of a Three-Level NPC Inverter. Electronics 2020, 9, 2195. [Google Scholar] [CrossRef]

- Suresh, K.; Nallaperumal, C.; Bharatiraja, C.; Sanjeevikumar, P.; Blaabjerg, F.; Nielsen, J.B.H. Cost-efficient nonisolated three-port DC-DC converter for EV/HEV applications with energy storage. Int. Trans. Electr. Energy Syst. 2019, 29, e12088. [Google Scholar] [CrossRef]

- Bharatiraja, C.; Jeevananthan, S.; Munda, J.L. Timing Correction Algorithm for SVPWM Based Diode-Clamped MLI Operated in over modulation Region. IEEE J. Sel. Top. Power Electron. Appl. 2018, 6, 233–245. [Google Scholar] [CrossRef]

- Timbus, A.; Liserre, M.; Teodorescu, R.; Rodriguez, P.; Blaabjerg, F. Evaluation of Current Controllers for Distributed Power Generation Systems. IEEE Trans. Power Electron. 2009, 24, 654–664. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P.; Malesani, L. Current control techniques for three-phase voltage-source PWM converters: A survey. IEEE Trans. Ind. Electron. 1998, 45, 691–703. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Hysteresis modulation of multilevel inverters. IEEE Trans. Power Electron. 2011, 26, 1396–1409. [Google Scholar] [CrossRef]

- Shen, M.; Joseph, A.; Wang, J.; Peng, F.Z.; Adams, D.J. Comparison of traditional inverters and Z-source inverter for fuel cell vehicles. IEEE Trans. Power Electron. 2007, 22, 1453–1463. [Google Scholar] [CrossRef]

- Hassaine, L.; OLias, E.; Quintero, J.; Salas, V. Overview of power inverter topologies and control structures for grid-connected photovoltaic systems. Renew. Sustain. Energy Rev. 2014, 30, 796–807. [Google Scholar] [CrossRef]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors Voltage Switching Ripple in Three-Phase Three-Level Neutral Point Clamped Inverters with Self-Balancing Carrier-Based Modulation. Energies 2018, 11, 3244. [Google Scholar] [CrossRef]

- Wang, Y.; Shi, W.W.; Xie, N.; Wang, C.M. Diode-Free T-Type Three-Level Neutral-Point-Clamped Inverter for Low-Voltage Renewable Energy System. IEEE Trans. Ind. Electron. 2014, 61, 6168–6174. [Google Scholar] [CrossRef]

- Bharatiraja, C.; Jeevananthan, S.; Latha, R. FPGA based practical implementation of NPC-MLI with SVPWM for an autonomous operation PV system with capacitor balancing. Int. J. Electr. Power Energy Syst. 2014, 61, 489–509. [Google Scholar] [CrossRef]

- Kadam, A.; Shukla, A. A 5-level high efficiency low cost Hybrid Neutral Point Clamped transformerless inverter for grid connected photovoltaic application. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 3189–3194. [Google Scholar] [CrossRef]

- Sebaaly, F.; Kanaan, H.Y.; Moubayed, N. Three-level neutral-point-clamped inverters in transformerless PV systems—State of the art. In Proceedings of the MELECON 2014—2014 17th IEEE Mediterranean Electrotechnical Conference, Beirut, Lebanon, 13–16 April 2014; pp. 1–7. [Google Scholar] [CrossRef]

- Santhakumar, C.; Shivakumar, R.; Bharatiraja, C.; Sanjeevikumar, P. Carrier Shifting Algorithms for the Mitigation of Circulating Current in Diode Clamped MLI Fed Induction Motor Drive. Int. J. Power Electron. Drive Syst. (IJPEDS) 2017, 8, 844–852. [Google Scholar] [CrossRef]

- Bharatiraja, C.; Sanjeevikumar, P.; Blaabjerg, F. Investigation and Comparative Analysis of Advanced PWM Techniques for Three-Phase Three-Level NPC-MLI Drives. Electr. Power Compon. Syst. 2018, 46. [Google Scholar] [CrossRef]

- Bharatiraja, C.; Munda, J.L.; Sriramsai, N.; Sai Navaneesh, T. Investigation of the Common Mode Voltage for a Neutral-Point-Clamped Multilevel Inverter Drive and its Innovative Elimination through SVPWM Switching-State Redundancy. Int. J. Power Electron. Drive Syst. 2016, 3, 892–900. [Google Scholar] [CrossRef]

| Vg > 0 (0 to π) | |

|---|---|

| S1000(Vg = +Vdc/2) | S0110(Vg = 0) |

| ig > 0 (Inverting mode) | |

|  |

| ig < 0 (Rectifying mode) | |

|  |

| Vg < 0 (π to 2π) | |

| S0110 (Vg = +Vdc/2) | S0001 (Vg = +Vdc/2) |

| ig < 0 (Inverting mode) | |

|  |

| ig > 0 (Rectifying mode) | |

|  |

| Positive Voltage and Positive Current | Negative Voltage and Positive Current |

|  |

| Positive Voltage and Negative Current | Negative Voltage and Negative Current |

|  |

| Parameters | Values |

|---|---|

| PV module design/W | 1250 W |

| Grid voltage/V and grid frequency/Hz | 240 V/50 Hz |

| Inverter power rating/W | 1000 W |

| dc-link capacitors (C1 and C2)/μF | 470 μF/500 V |

| Filter inductors (L1 and L2)/mH | 4 mH |

| CM Capacitance (CY1 and CY2)/nF | 2.2 nF |

| Parasitic Capacitance (CPV1 and CPV2)/μF | 0.2 μF |

| Inverter Topology. | No. of Switch/Leg | No. Of Clamping Diode/Leg | Top and Bottom Switch Voltage Rating | Inner Switch Voltage Rating | Short Circuit Problems |

|---|---|---|---|---|---|

| I-Type NPC MLI [13] | 4 | 2 | 1200 V | 1200 V | Possible |

| T-Type NPC MLI [19] | 4 | 0 | 1200 V | 600 V | Possible |

| Diode Free NPC-MLI [33] | 6 | 0 | 1200 V | 1200 V | Possible |

| DBHBI-MLI [11] | 4 | 2 | 1200 V | 1200 V | No |

| Proposed | 4 | 0 | 600 V | 600 V | No |

| Parameters. | Units/Rating | [16] | [11] | [19] | (Proposed) |

|---|---|---|---|---|---|

| Switches | No. of switch | 2 | 4 | 4 | 4 |

| VDS(Peak)/V | 800 | 400 | 400 | 400 | |

| ID(rms)/A | 2.54 | 2.16/ 2.95 | 2.16/ 2.95 | 2.16/ 2.95 | |

| Switch SDPF/kVA | 4.009 | 4.008 | 4.008 | 4.008 | |

| Inner switch voltage rating | 1200 V | 1200 V | 1200 V | 600 V | |

| Top and Bottom switch voltage rating | 1200 V | 1200 V | 1200 V | 1200 V | |

| Clamping diodes | No of Diode | 2 | 2 | 2 | 0 |

| VKA(peak)/V | 800 | 400 | 400 | - | |

| IA(rms)/A | 0.47 | 0.93 | 0.94 | - | |

| Diode-SDPF/kVA | 0.752 | 0.744 | 0.744 | 0 | |

| Total SDPF/kVA | SDPF/kVA | 4.816 | 4.832 | 4.832 | 4.008 |

| Inductor details | No. of inductor | 2 | 1 | 2 | 2 |

| L value-L/mH | 16 | 4 | 4 | 4 | |

| Short circuit problems ( Shoot through) | Possible | Possible | No | No | |

| Leakage current | No | No | No | No | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Madasamy, P.; Verma, R.; Rameshbabu, A.; Murugesan, A.; Umamageswari, R.; Munda, J.L.; Bharatiraja, C.; Mihet-Popa, L. Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System. Electronics 2021, 10, 977. https://doi.org/10.3390/electronics10080977

Madasamy P, Verma R, Rameshbabu A, Murugesan A, Umamageswari R, Munda JL, Bharatiraja C, Mihet-Popa L. Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System. Electronics. 2021; 10(8):977. https://doi.org/10.3390/electronics10080977

Chicago/Turabian StyleMadasamy, P., Rajesh Verma, A. Rameshbabu, A. Murugesan, R. Umamageswari, Josiah Lange Munda, C. Bharatiraja, and Lucian Mihet-Popa. 2021. "Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System" Electronics 10, no. 8: 977. https://doi.org/10.3390/electronics10080977

APA StyleMadasamy, P., Verma, R., Rameshbabu, A., Murugesan, A., Umamageswari, R., Munda, J. L., Bharatiraja, C., & Mihet-Popa, L. (2021). Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System. Electronics, 10(8), 977. https://doi.org/10.3390/electronics10080977