Variable Clock and EM Signal Generation Scheme for Foveation-Based Driving OLED Head-Mounted Displays

Abstract

1. Introduction

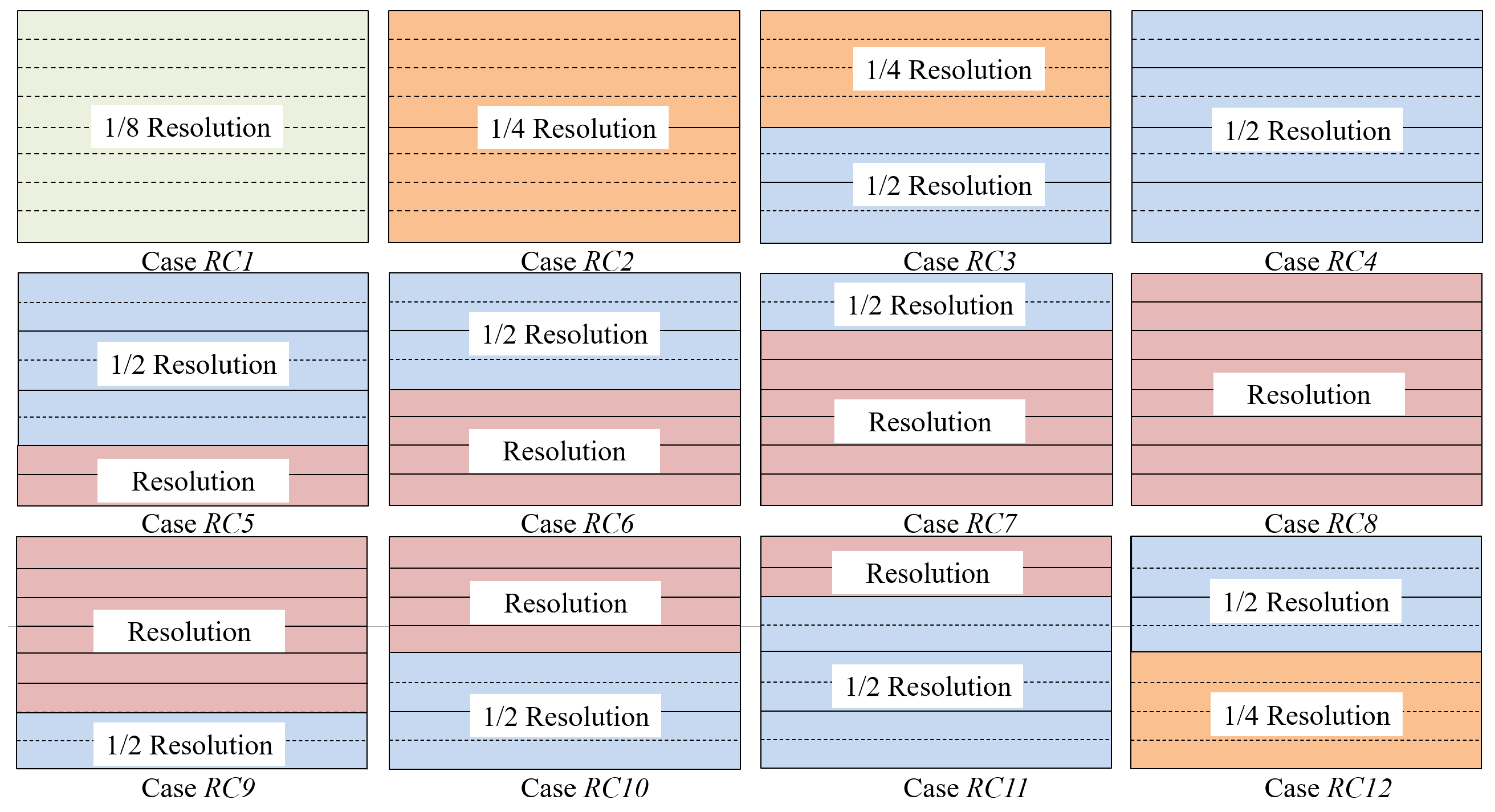

2. Previous Foveation-Based Driving Scheme

3. Variable Clock Generation

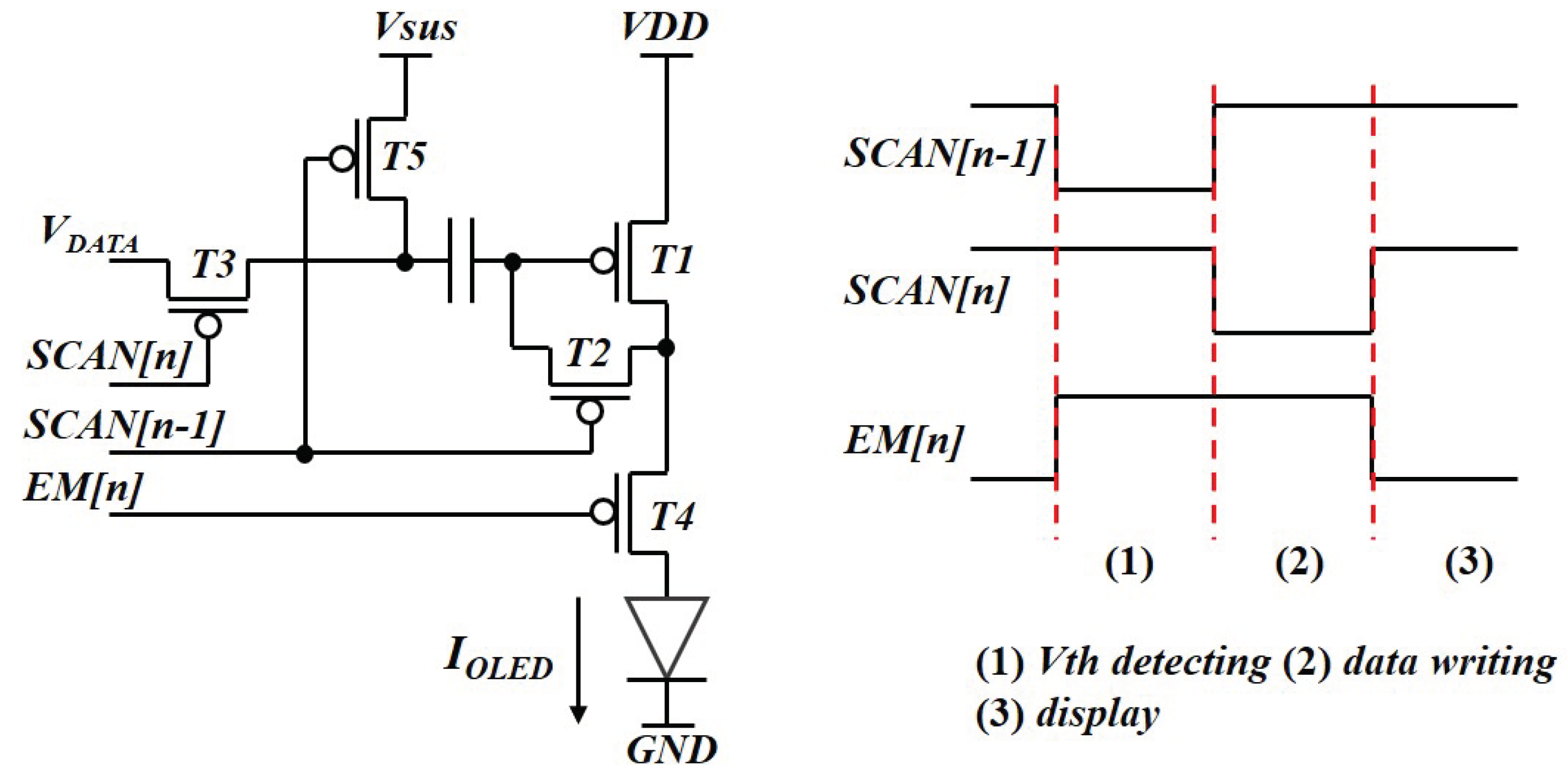

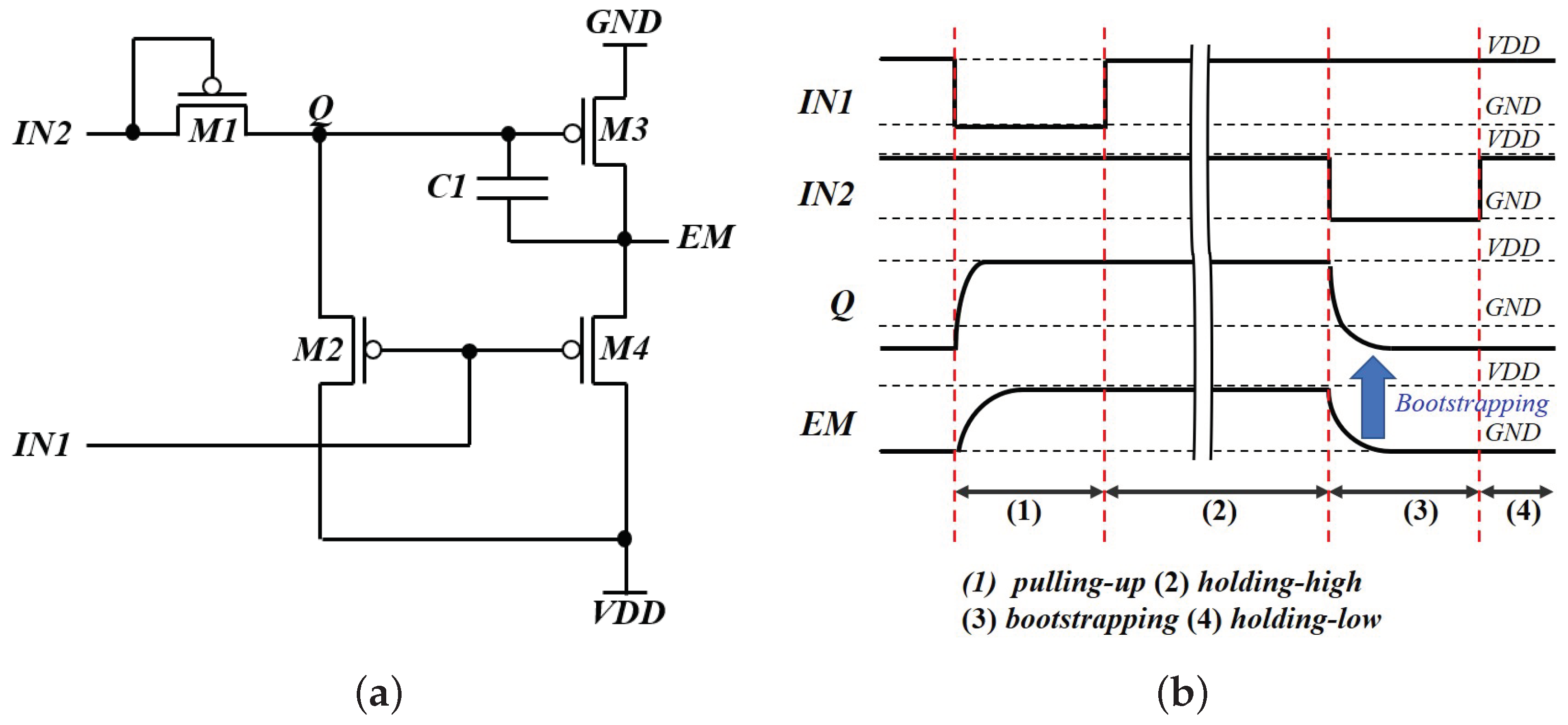

4. EM Signal Generation for OLED Pixels

5. Evaluation Results

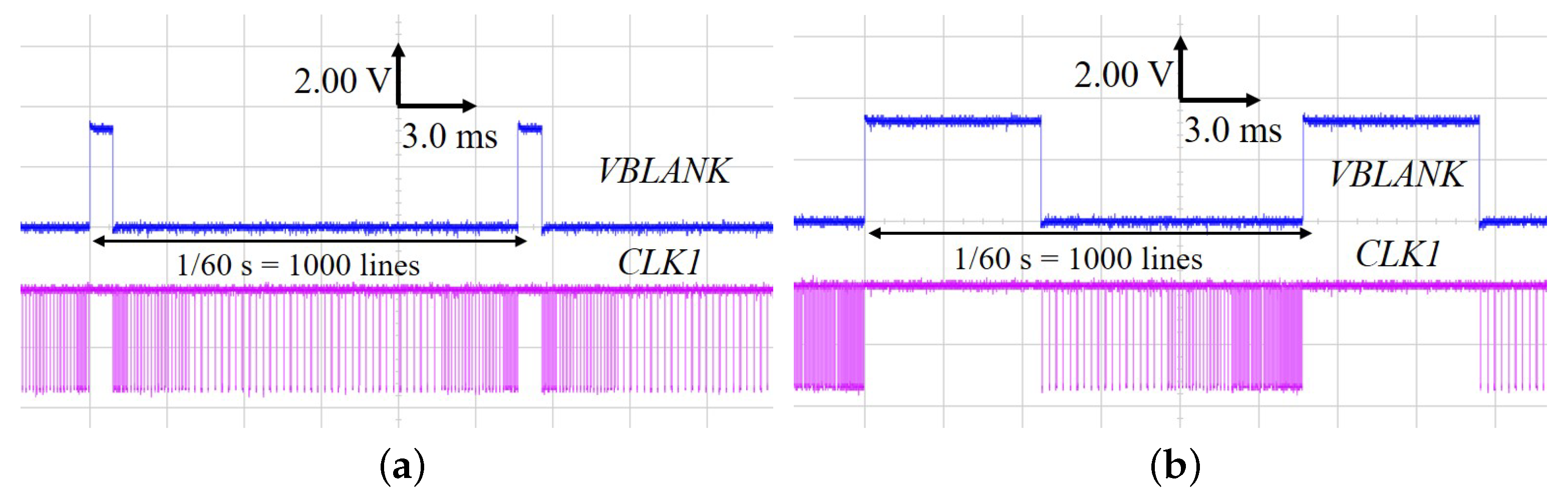

5.1. Variable Clock Generation

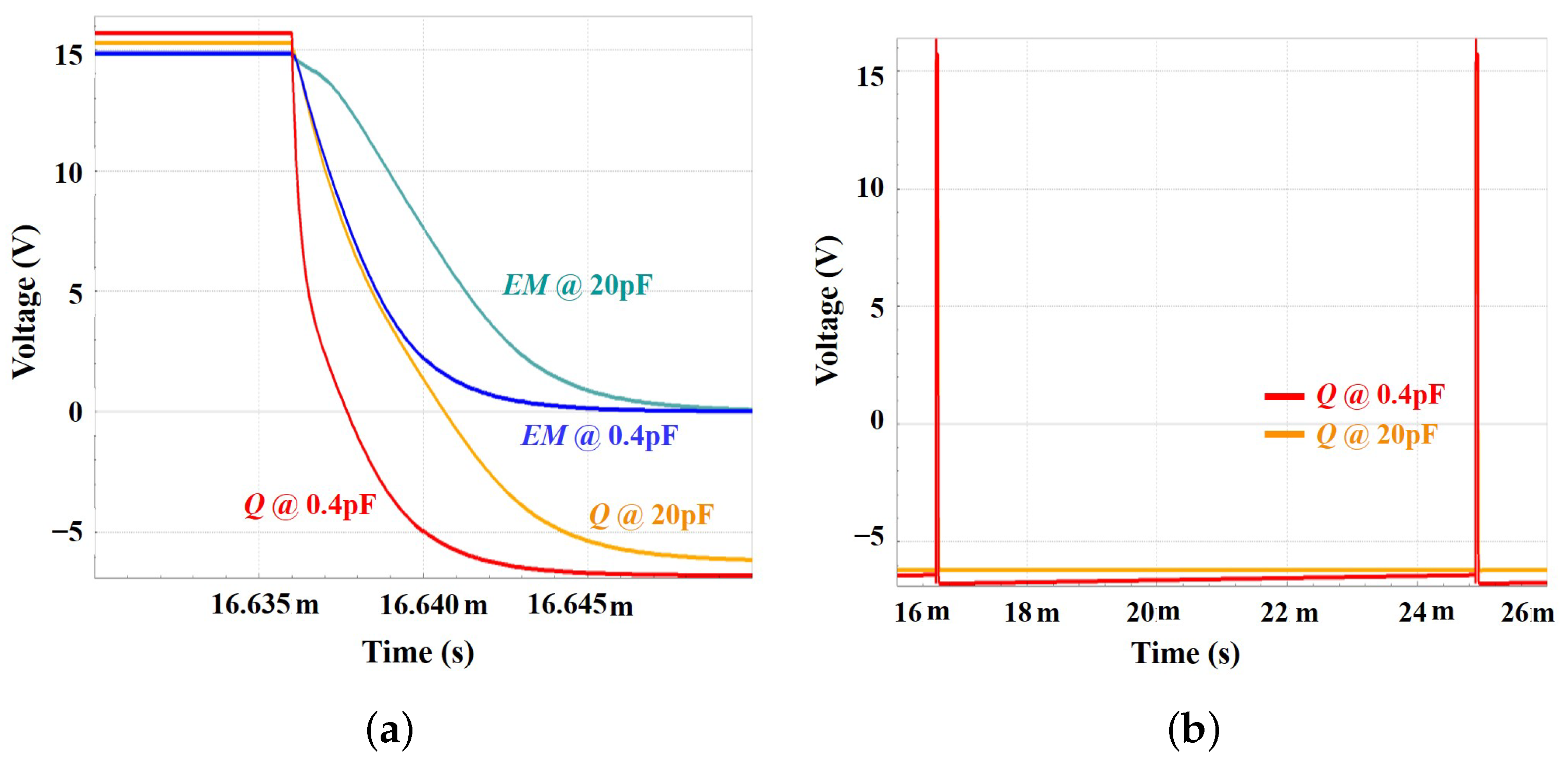

5.2. EM Signal Generation

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Singh, R.P.; Javaid, M.; Kataria, R.; Tyagi, M.; Haleem, A.; Suman, R. Significant applications of virtual reality for COVID-19 pandemic. Diabetes Metab. Syndr. 2020, 14, 661–664. [Google Scholar] [CrossRef]

- Kogan, M.; Klein, S.E.; Hannon, C.P.; Nolte, M.T. Orthopaedic Education During the COVID-19 Pandemic. J. Am. Acad. Orthop. Surg. 2020, 28, e456–e464. [Google Scholar] [CrossRef] [PubMed]

- Dwivedi, Y.K.; Hughes, D.L.; Coombs, C.; Constanntiou, I.; Duan, Y.; Edwards, J.S.; Gupta, B.; Lal, B.; Misra, S.; Prashant, P.; et al. Impact of COVID-19 pandemic on information management research and practice: Transforming education, work and life. Int. J. Inform. Manag. 2020, 55, 102211. [Google Scholar] [CrossRef]

- Barnes, S.J. Information management research and practice in the post-COVID-19 world. Int. J. Inform. Manag. 2020, 55, 102175. [Google Scholar] [CrossRef] [PubMed]

- Porpiglia, F.; Checcucci, E.; Autorino, R.; Amparore, D.; Cooperberg, M.R.; Ficarra, V.; Novara, G. Traditional and Virtual Congress Meetings During the COVID-19 Pandemic and the Post-COVID-19 Era: Is it Time to Change the Paradigm? Eur. Urol. 2020, 78, 301–303. [Google Scholar] [CrossRef] [PubMed]

- Bastani, B.; Turner, E.; Vieri, C.; Jiang, H.; Funt, B.; Balram, N. Foveated Pipeline for AR/VR Head-Mounted Displays. Inf. Disp. 2017, 33, 14–35. [Google Scholar] [CrossRef]

- Young, B. OLED Displays and the Immersive Experience. Inf. Disp. 2018, 34, 16–36. [Google Scholar] [CrossRef]

- Bhowmik, A.K. Advances in Virtual, Augmented, and Mixed Reality Technologies. Inf. Disp. 2018, 34, 18–21. [Google Scholar] [CrossRef]

- Albert, R.; Patney, A.; Luebke, D.; Kim, J. Latency Requirements for Foveated Rendering in Virtual Reality. ACM Trans. Appl. Percept. 2017, 14, 25. [Google Scholar] [CrossRef]

- Jang, H.J.; Lee, J.Y.; Kwak, J.; Lee, D.; Park, J.H.; Lee, B.; Noh, Y.Y. Progress of display performances: AR, VR, QLED, OLED, and TFT. J. Inf. Disp. 2019, 20, 1–8. [Google Scholar] [CrossRef]

- Patney, A.; Salvi, M.; Kim, J.; Kaplanyan, A.; Wyman, C.; Benty, N.; Luebke, D.; Lefohn, A. Towards foveated rendering for gaze-tracked virtual reality. ACM Trans. Graph. 2016, 35, 179. [Google Scholar] [CrossRef]

- Vieri, C.; Lee, G.; Balram, N.; Jung, S.H.; Yang, J.Y.; Yoon, S.Y.; Kang, I.B. An 18 megapixel 4.3” 1443 ppi 120 Hz OLED display for wide field of view high acuity head mounted displays. J. Soc. Inf. Disp. 2018, 26, 314–324. [Google Scholar] [CrossRef]

- Menon, H.; Ramachandrappa, A.; Kesinger, J. Deep-Learning Based Approaches to Visual-Inertial Odometry for Autonomous Tracking Applications. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Los Angeles, CA, USA, 2018; pp. 471–474. [Google Scholar]

- Park, S.; Kim, Y.I.; Nam, H. Foveation-based reduced resolution driving scheme for immersive virtual reality displays. Opt. Express 2019, 27, 29594–29605. [Google Scholar] [CrossRef] [PubMed]

- Han, M.K. AM backplane for AMOLED. In Proceedings of the 9th Asian Symposium on Information Display, New Delhi, India, 8–12 October 2006; pp. 53–58. [Google Scholar]

- Lee, J.H.; Nam, W.J.; Kim, B.K.; Choi, H.S.; Ha, Y.M.; Han, M.K. A New Poly-Si TFT Current-Mirror Pixel for Active Matrix Organic Light Emitting Diode. IEEE Electron Device Lett. 2006, 27, 830–833. [Google Scholar] [CrossRef]

- Lee, B.W.; Ji, I.H.; Han, S.M.; Sung, S.D.; Shin, K.S.; Lee, J.D.; Kim, B.H.; Berkeley, B.H.; Kim, S.S. Novel Simultaneous Emission Driving Scheme for Crosstalk-free 3D AMOLED TV. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Seattle, WA, USA, 2010; pp. 758–761. [Google Scholar]

- In, H.J.; Kwon, O.K. A Simple Pixel Structure Using Polycrystalline-Silicon Thin-Film Transistors for High-Resolution Active-Matrix Organic Light-Emitting Diode Displays. IEEE Electron Device Lett. 2012, 33, 1018–1020. [Google Scholar] [CrossRef]

- Song, E.; Nam, H. Novel voltage programming n-channel TFT pixel circuit for low power and high performance AMOLED displays. Displays 2014, 35, 118–125. [Google Scholar] [CrossRef]

- Seol, K.H.; Kim, Y.I.; Park, S.; Nam, H. Simultaneous Emission AC-OLED Pixel Circuit for Extended Lifetime of OLED Display. IEEE J. Electron Devices Soc. 2018, 6, 835–840. [Google Scholar] [CrossRef]

- Wang, Z.; Bovik, A.C. Embedded Foveation Image Coding. IEEE Trans. Image Process. 2001, 10, 1397–1410. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.; Park, S.J.; Nam, H. Node-sharing low-temperature poly silicon TFT shift register without bootstrapping degradation for narrow bezel displays. Electron. Lett. 2018, 54, 1162–1164. [Google Scholar] [CrossRef]

- Kim, Y.I.; Nam, H. Clocked control scheme of separating TFTs for a node-sharing LTPS TFT shift register with large number of outputs. J. Soc. Inf. Disp. 2020, 28. [Google Scholar] [CrossRef]

- Slavenburg, G.A.; Janssens, M.; Lucas, L.; Schutten, R.J.; Verbeure, T. Variable Refresh Rate Displays. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Los Angeles, CA, USA, 2020; pp. 669–672. [Google Scholar]

- You, B.; Nam, H.; Lee, H. Image Adaptive Refresh Rate Technology for Ultra Low Power Consumption. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Los Angeles, CA, USA, 2020; pp. 676–679. [Google Scholar]

- Watson, A.B.; Ahumada, A.J. Flicker visibility: A perceptual metric for display flicker. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Los Angeles, CA, USA, 2011; pp. 957–959. [Google Scholar]

- Kim, Y.W.; Kwak, W.K.; Lee, J.Y.; Choi, W.S.; Lee, K.Y.; Kim, S.C.; Yoo, E.J. 40 Inch FHD AM-OLED Display with IR Drop Compensation Pixel Circuit. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: San Antonio, TX, USA, 2009; pp. 85–87. [Google Scholar]

- Song, E.; Nam, H. Shoot-through current reduction scheme for low power LTPS TFT programmable shift register. J. Soc. Inf. Disp. 2014, 22, 18–22. [Google Scholar] [CrossRef]

- Song, E.; Nam, H. Low Power Programmable Shift Register with Depletion Mode Oxide TFTs for High Resolution and High Frame Rate AMFPDs. J. Disp. Technol. 2014, 10, 834–838. [Google Scholar] [CrossRef]

- Song, E.; Song, S.J.; Nam, H. Pulse-width-independent low power programmable low temperature poly-Si thin-film transistor shift register. Solid State Electron. 2015, 107, 35–39. [Google Scholar] [CrossRef]

- Oh, J.H.; Hur, J.H.; Son, Y.D.; Kim, K.M.; Kim, S.H.; Kim, E.H.; Choi, J.W.; Hong, S.M.; Kim, J.O.; Bae, B.S.; et al. 2.0 inch a-Si:H TFT-LCD with Low Noise Integrated Gate Driver. In Society for Information Display Symposium Digest of Technical Papers; Society for Information Display: Boston, MA, USA, 2005; pp. 942–945. [Google Scholar]

- Tobii Tech. Tobii Eye Tracker 4L. Available online: https://tech.tobii.com/products/ (accessed on 21 December 2020).

- Cypress Semiconductor Corporation. PSoC 5LP. Available online: http://www.cypress.com/products/32-bit-arm-cortex-m3-psoc-5lp/ (accessed on 21 December 2020).

- Terasic Inc. Altera DE2-115. Available online: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=502 (accessed on 21 December 2020).

- Silvaco, Inc. SmartSpice. Available online: https://silvaco.com/spice-simulation/parallel-spice-simulator/ (accessed on 21 December 2020).

- Wang, Z.; Chen, J.; Hoi, S.C. Deep learning for image super-resolution: A survey. IEEE Trans. Pattern Anal. Mach. Intell. 2021, in press. [Google Scholar] [CrossRef] [PubMed]

| PMOS Characteristics | Threshold Voltage | Mobility | Overlap Capacitance |

| −1.7 V | 31 /V·s | 3.02 /μm | |

| Transistor Sizes | Channel Length | Channel Width | |

| 7 μm | 10 μm@M1, M2 100 μm@M3, M4 | ||

| Simulation Setup | Supply Voltage | Output Load | Line Time |

| 15 V@VDD 0 V@GND | 2.2 k 120 pF | 4.14 μs @120 Hz | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

Short Biography of Authors

| Jina Bae is currently pursuing the M.S. degree in the Department of Information Display, Kyung Hee University, Seoul, South Korea, where she also received the B.S. degree in 2019. Her current research is focused on integrated circuits for flat panel display applications and machine learning applications. |

| Junhee Lee received the B.S. degree from the Department of Information Display, Kyung Hee University, Seoul, South Korea, in 2020, where he is currently pursuing the M.S. degree. His current research is focused on gate driver circuits and EM circuits. |

| Hyoungsik Nam received his B.S., M.S. and Ph.D. degrees in EECS from Korea Advance Institute of Science and Technology (KAIST), Daejon Korea, in 1996, 1998, and 2004. He joined Samsung Electronics as a senior engineer in 2005, where he had worked on Active-Matrix Liquid-Crystal Displays. He is currently a professor in the department of Information Display at Kyung Hee University, Seoul Korea. His current research interests are low power technologies, integrated circuits, signal/user interfaces for flat panel displays, and machine learning application. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, J.; Lee, J.; Nam, H. Variable Clock and EM Signal Generation Scheme for Foveation-Based Driving OLED Head-Mounted Displays. Electronics 2021, 10, 538. https://doi.org/10.3390/electronics10050538

Bae J, Lee J, Nam H. Variable Clock and EM Signal Generation Scheme for Foveation-Based Driving OLED Head-Mounted Displays. Electronics. 2021; 10(5):538. https://doi.org/10.3390/electronics10050538

Chicago/Turabian StyleBae, Jina, Junhee Lee, and Hyoungsik Nam. 2021. "Variable Clock and EM Signal Generation Scheme for Foveation-Based Driving OLED Head-Mounted Displays" Electronics 10, no. 5: 538. https://doi.org/10.3390/electronics10050538

APA StyleBae, J., Lee, J., & Nam, H. (2021). Variable Clock and EM Signal Generation Scheme for Foveation-Based Driving OLED Head-Mounted Displays. Electronics, 10(5), 538. https://doi.org/10.3390/electronics10050538