Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit

Abstract

1. Introduction

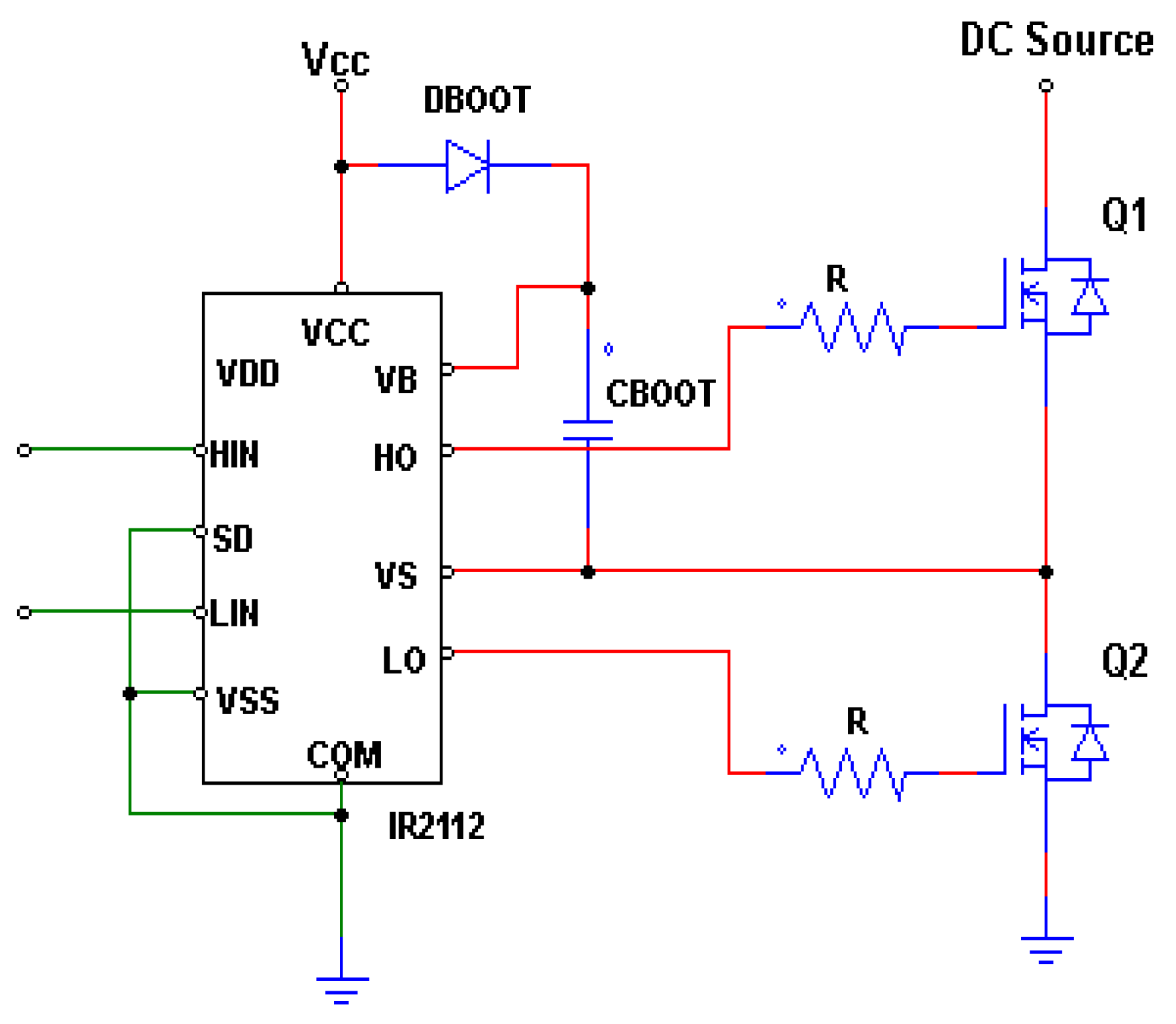

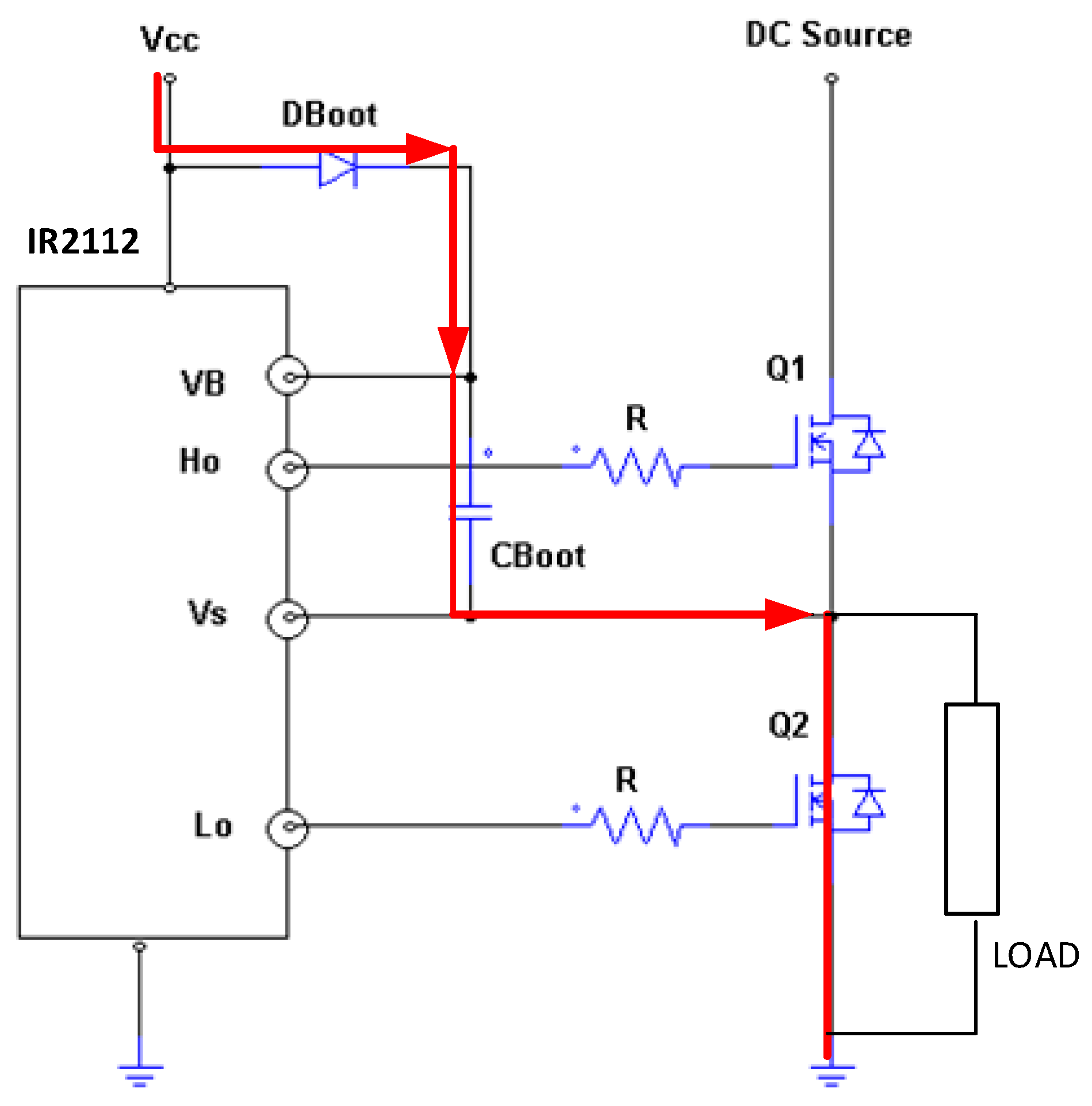

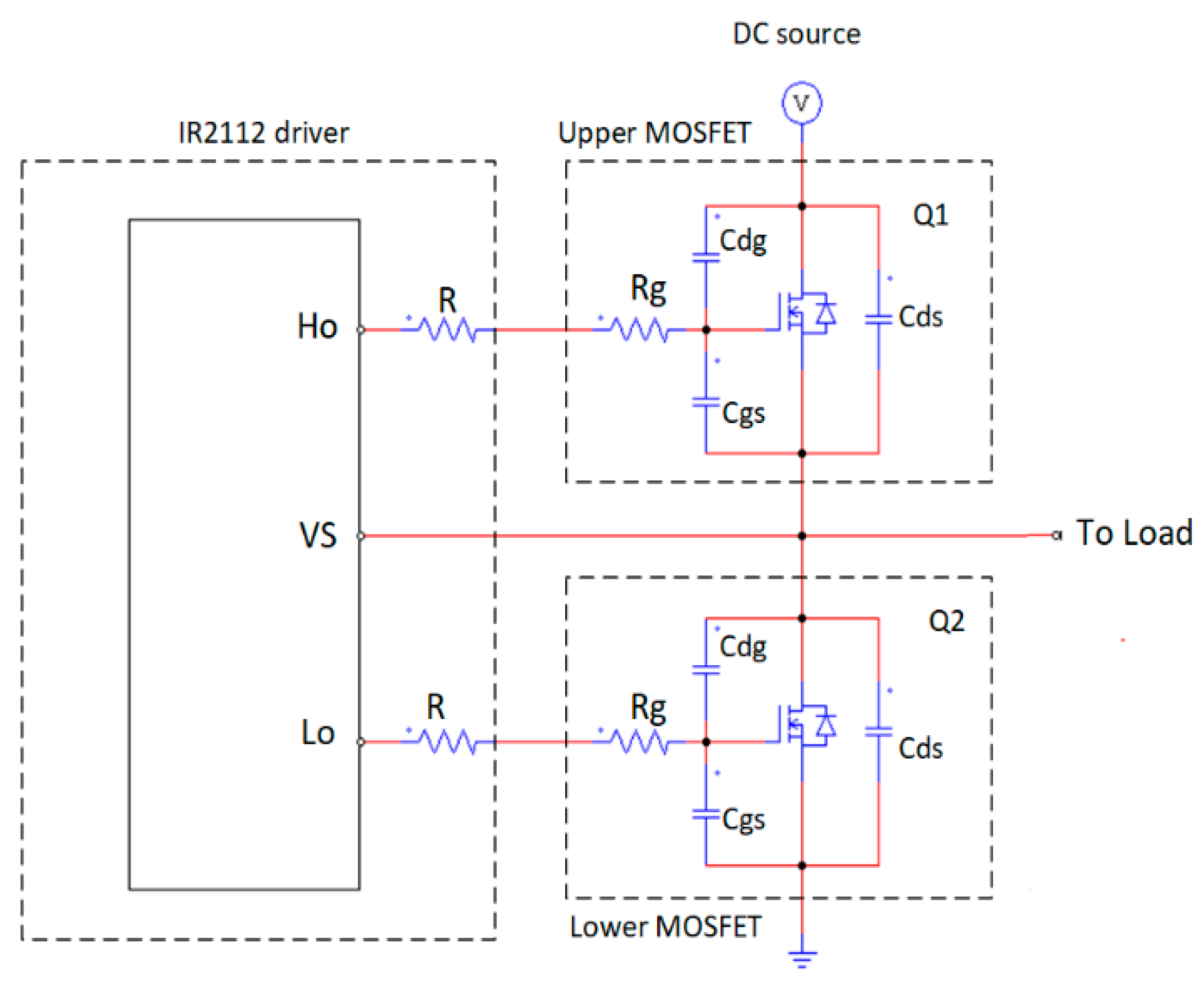

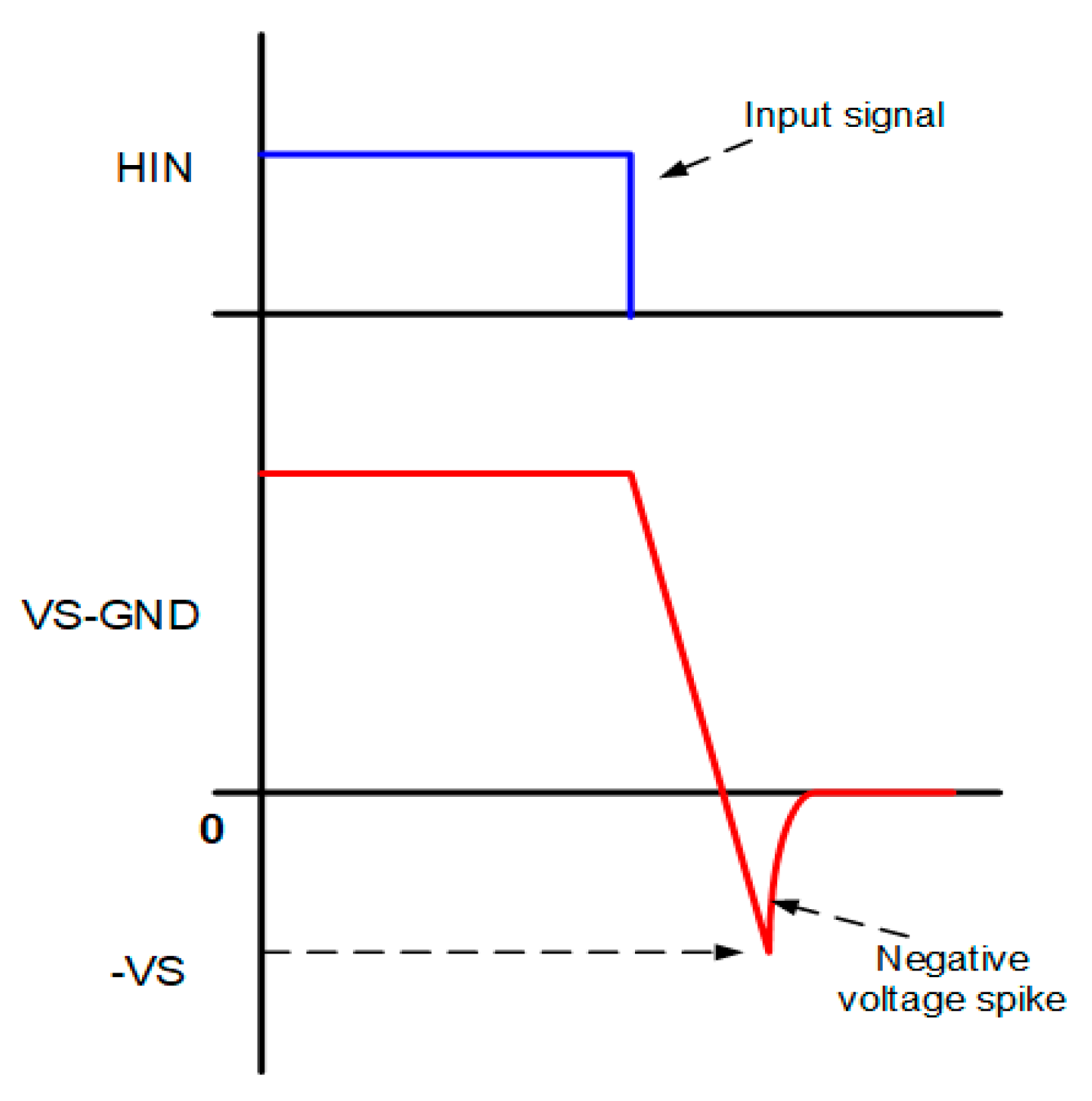

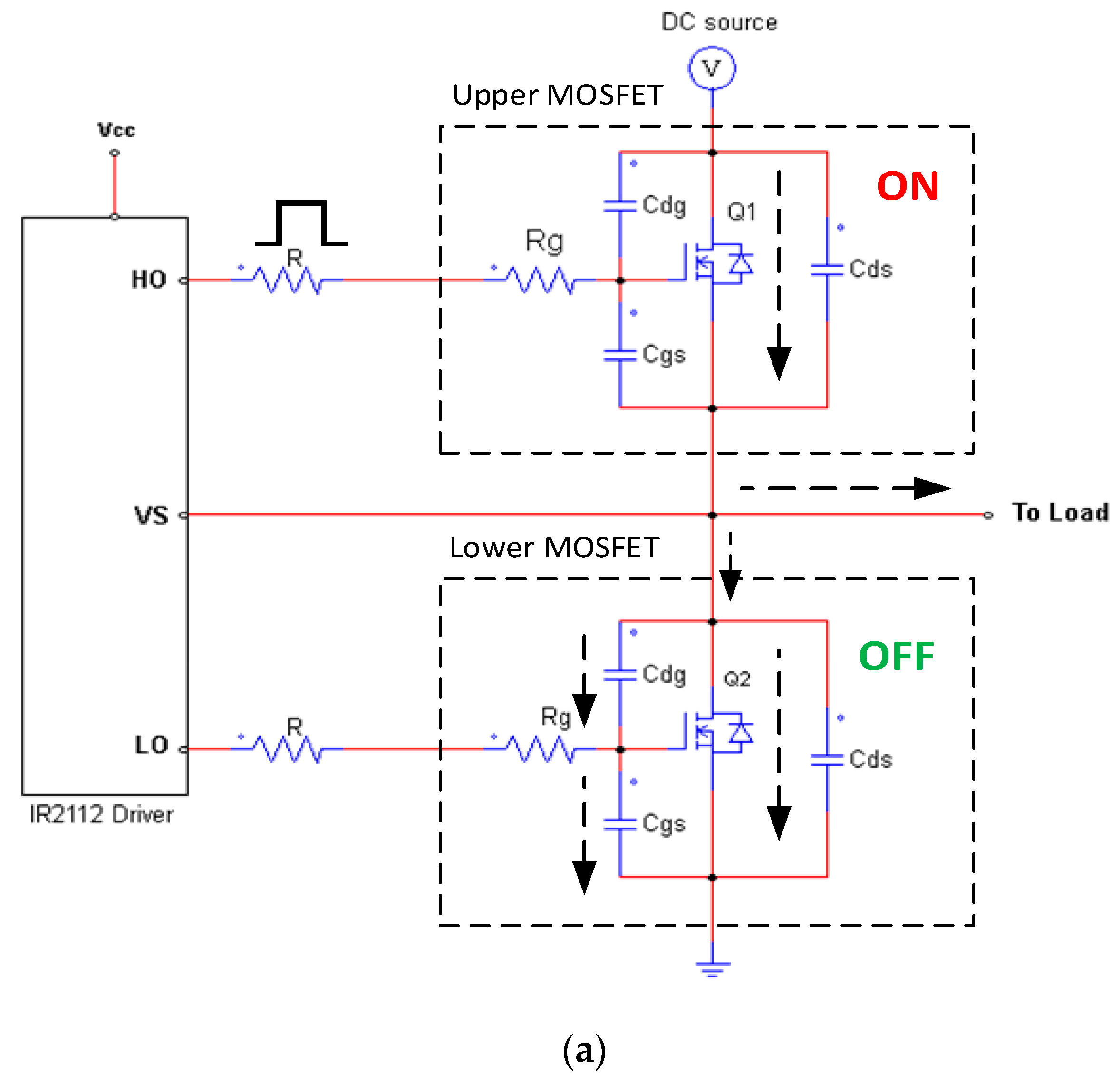

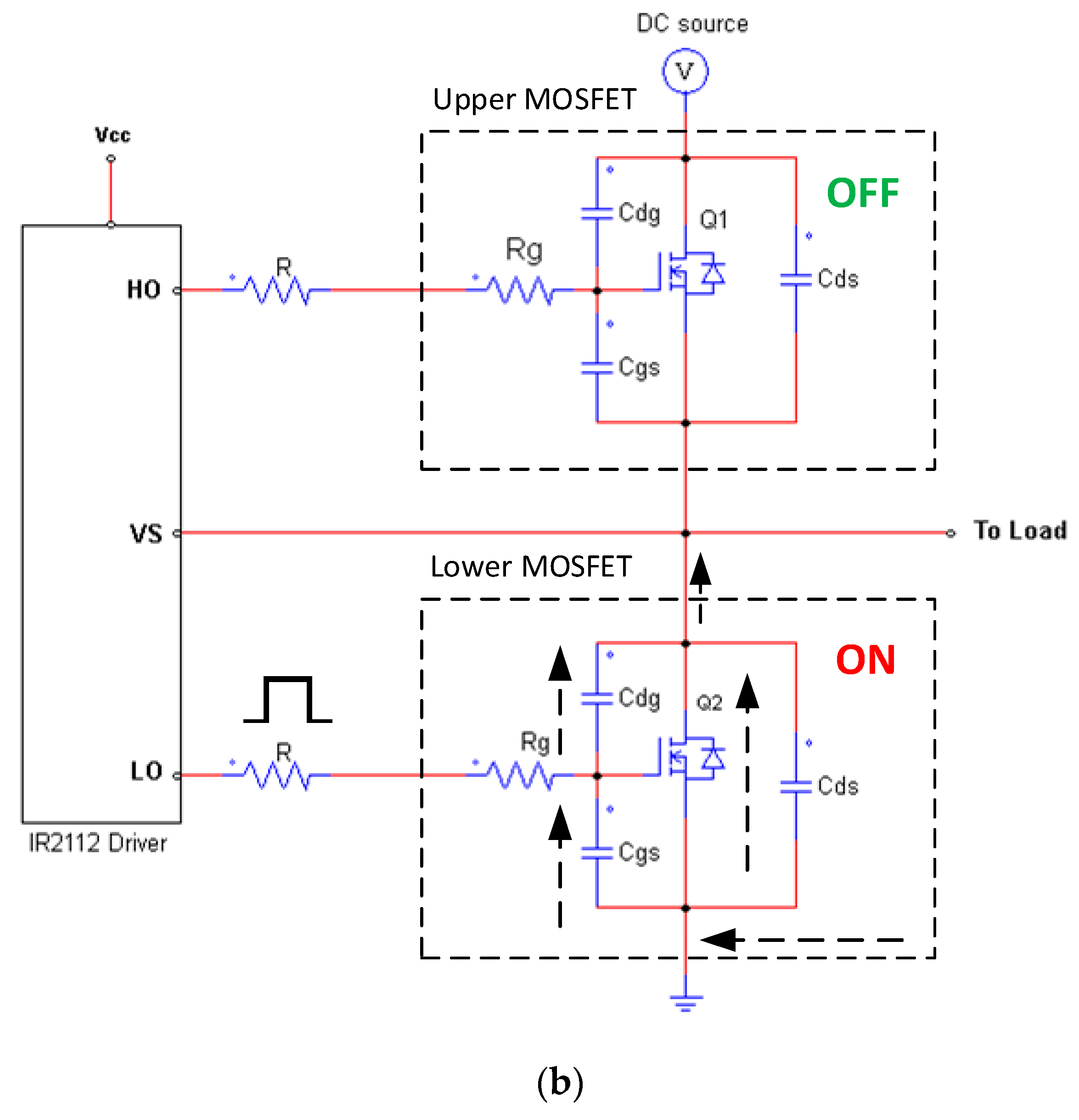

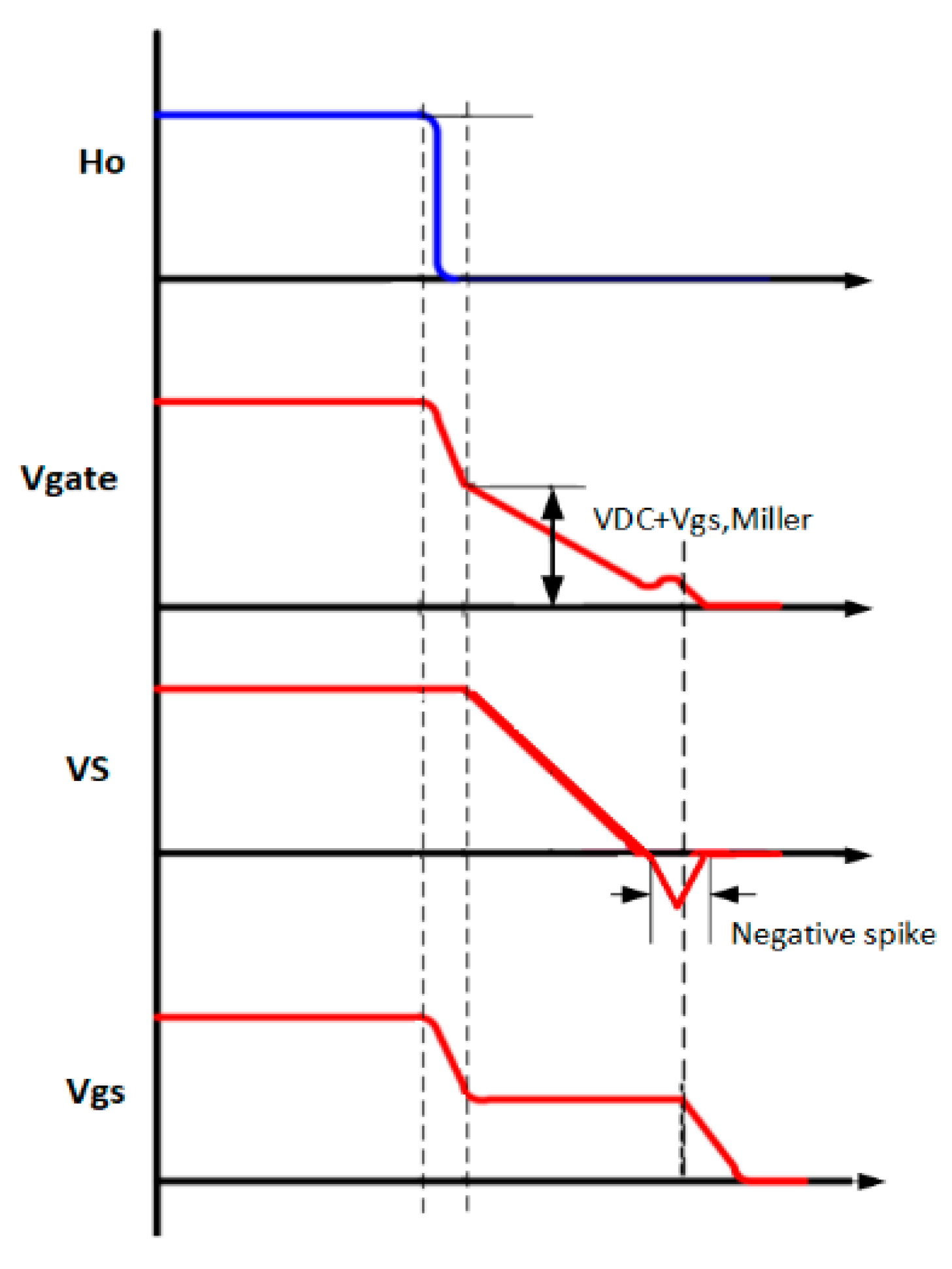

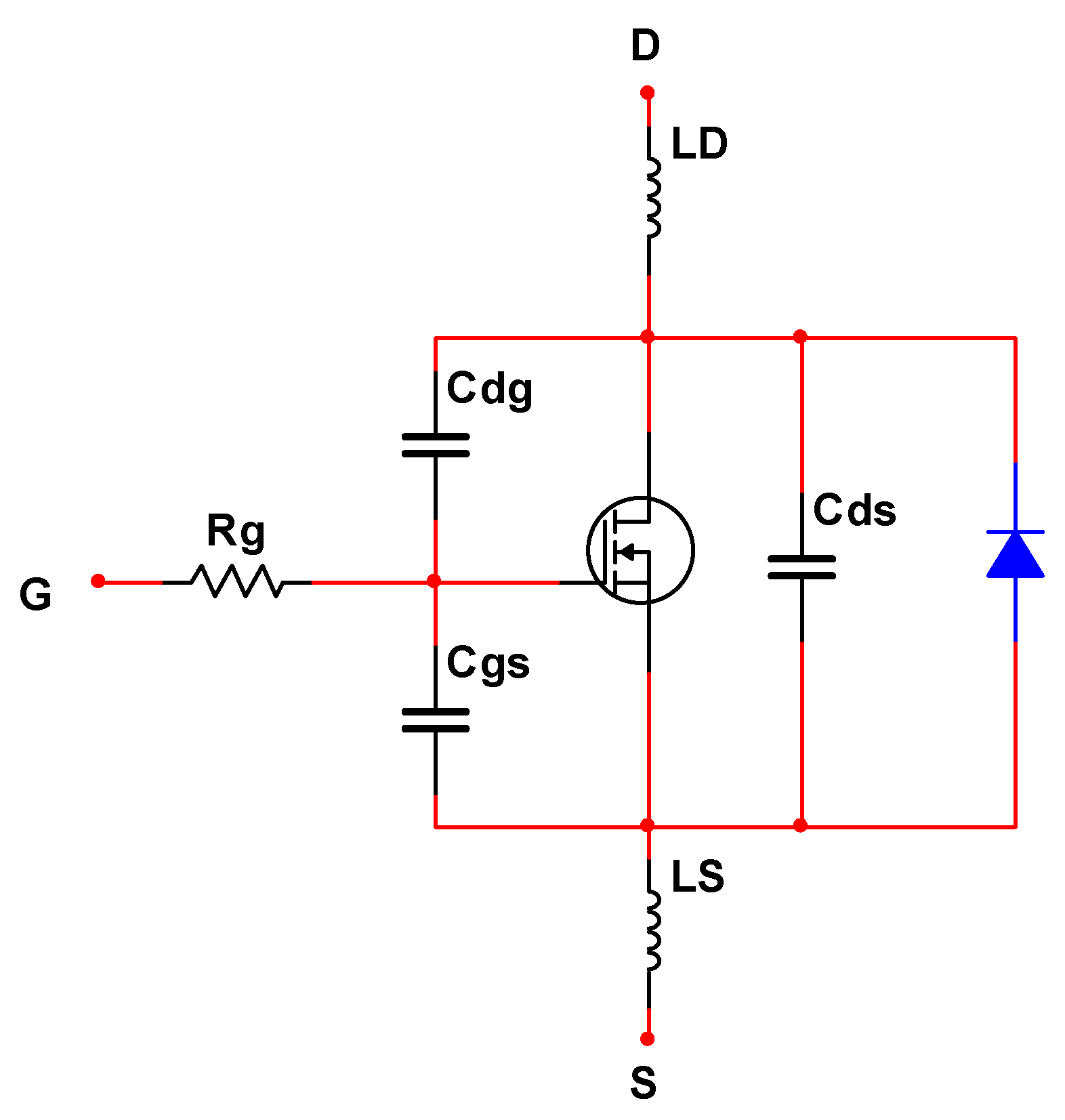

2. H-Bridge Inverter

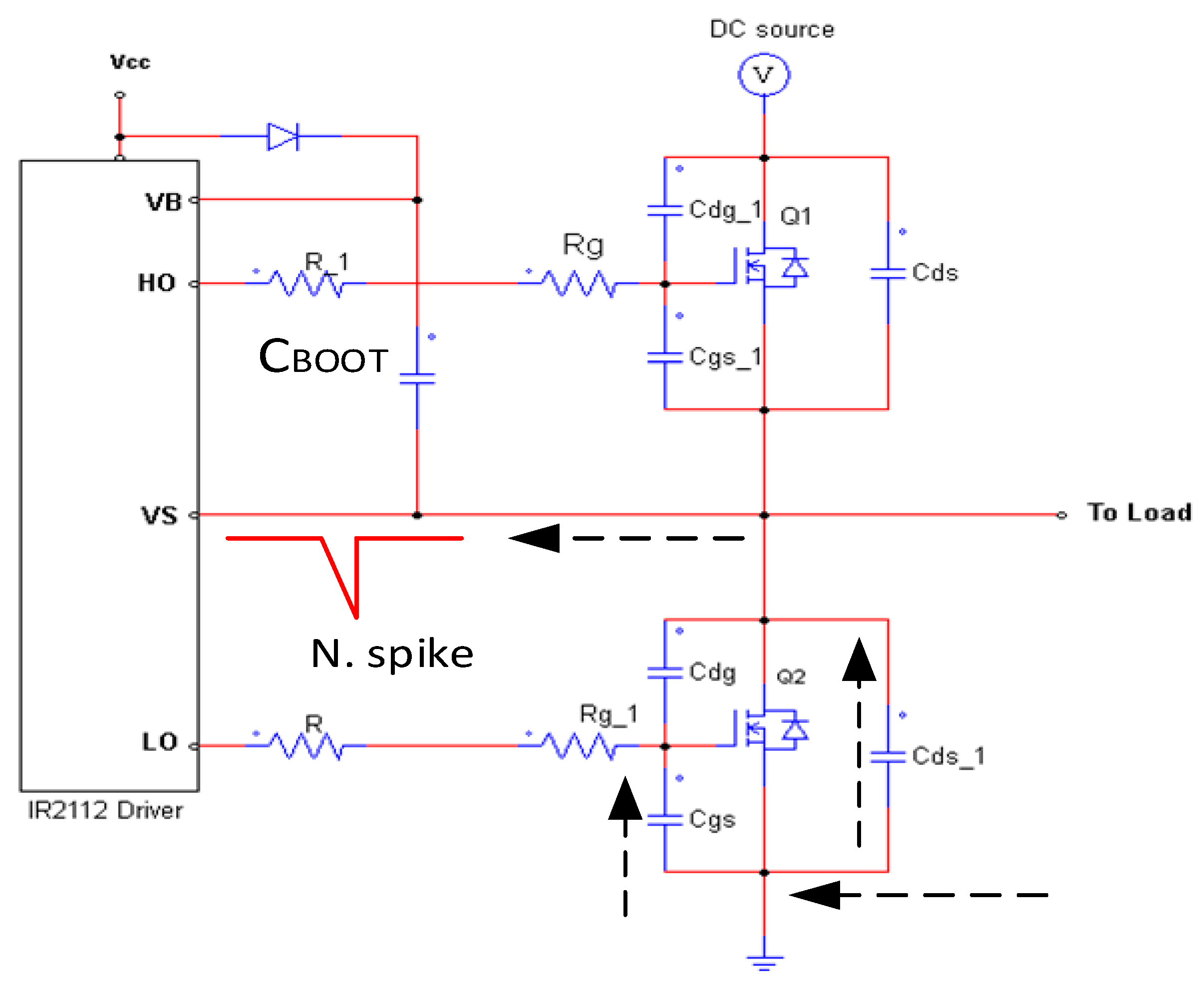

3. Proposed Technique

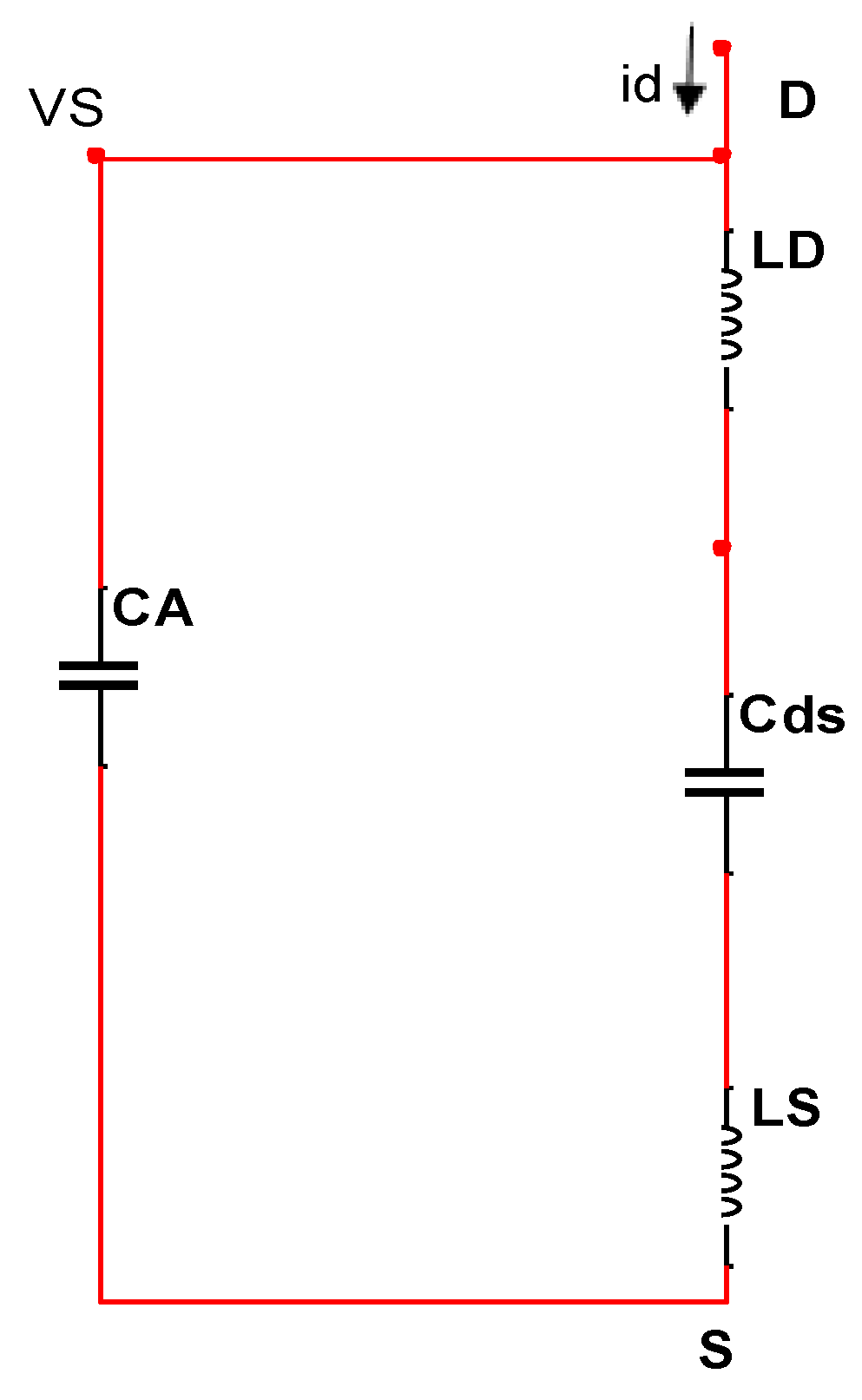

Operating Principle

4. Proposed Design to Suppress Voltage Spikes

- t1 and t2 is the ON time at the period time of PWM; LD MOSFET Internal Drain Inductance;

- LS is the Internal Source Inductance; CA is the external capacitor; VS is the voltage at VS pin.

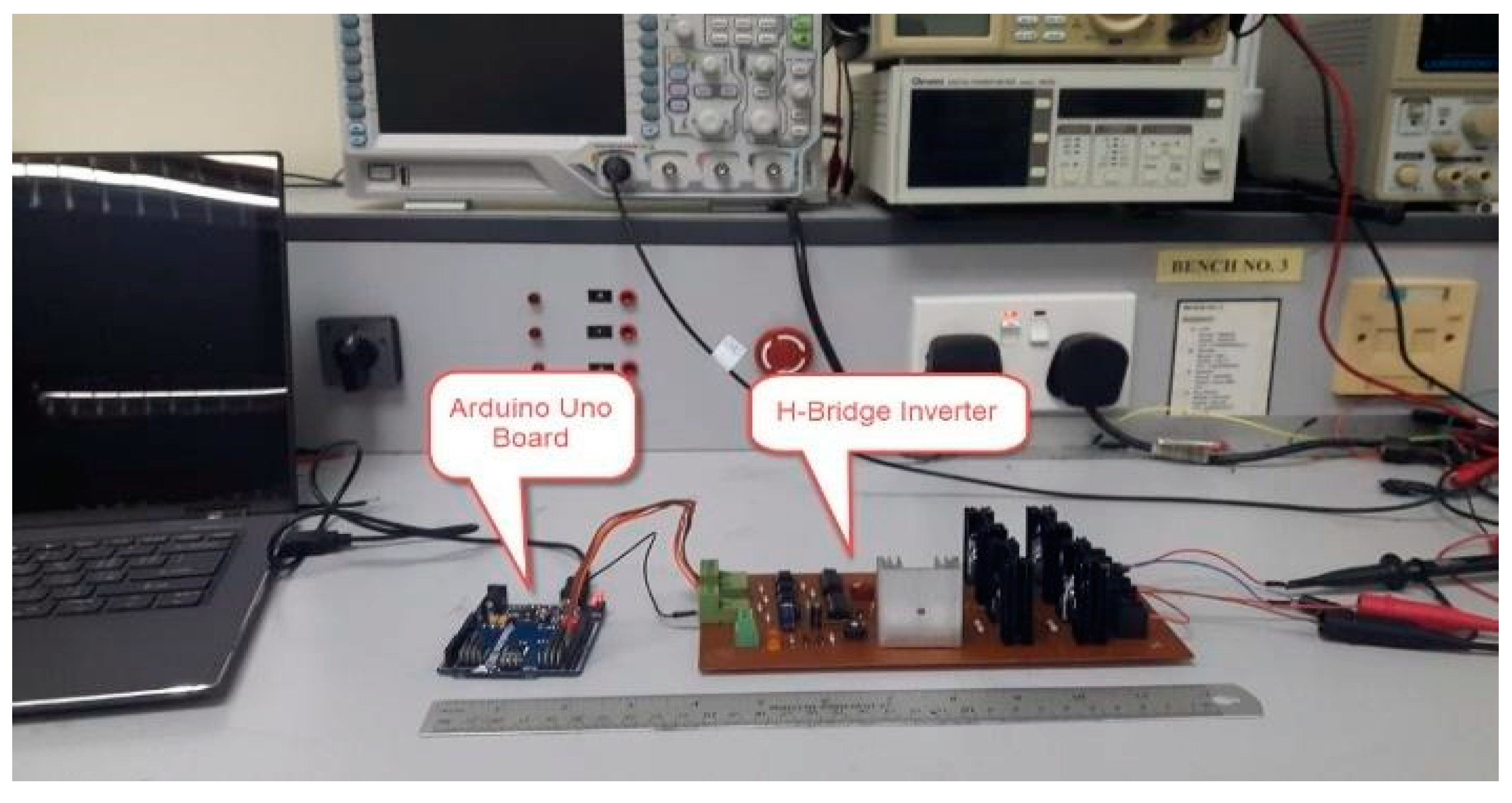

5. Experimental Verification

6. Experimental Results

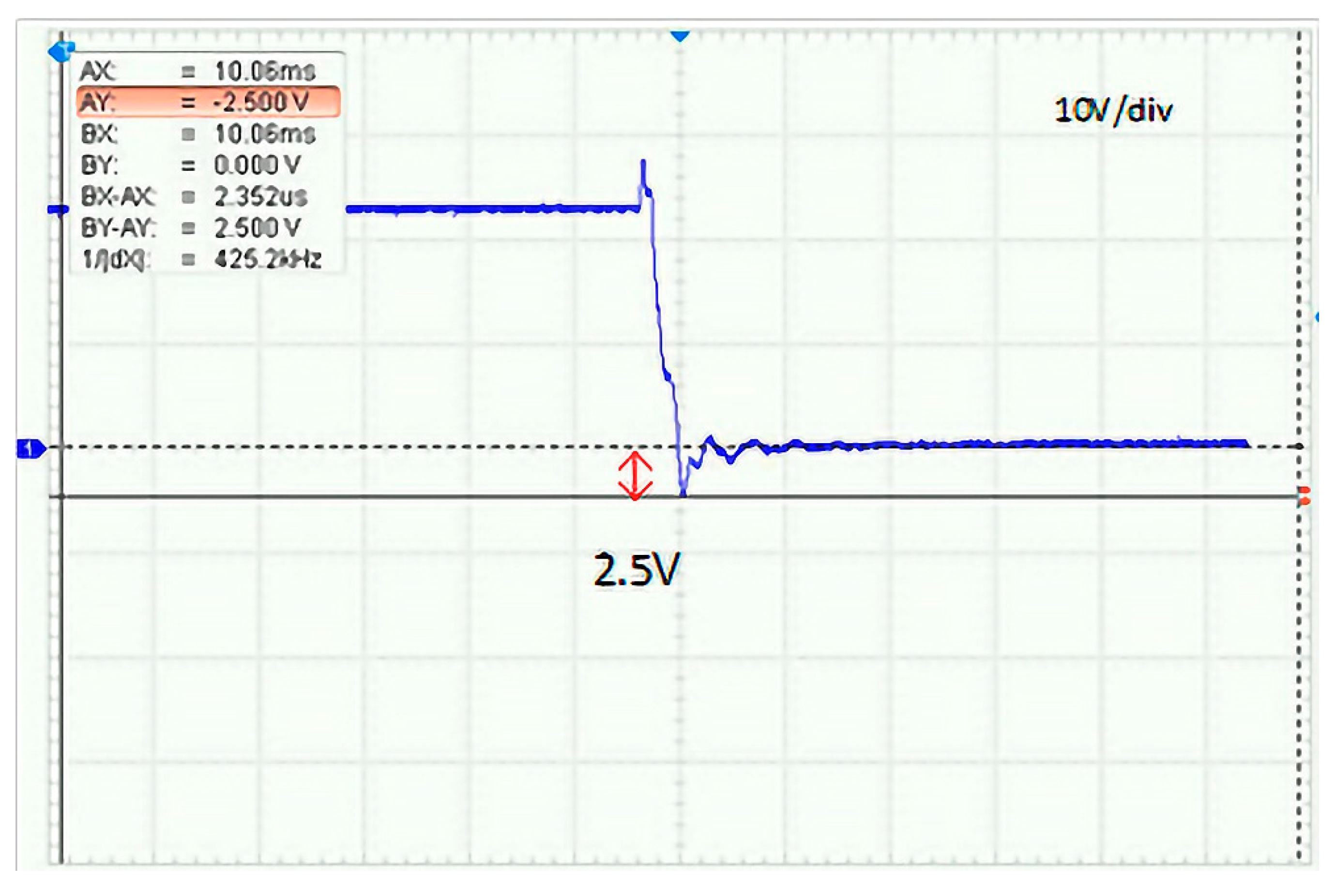

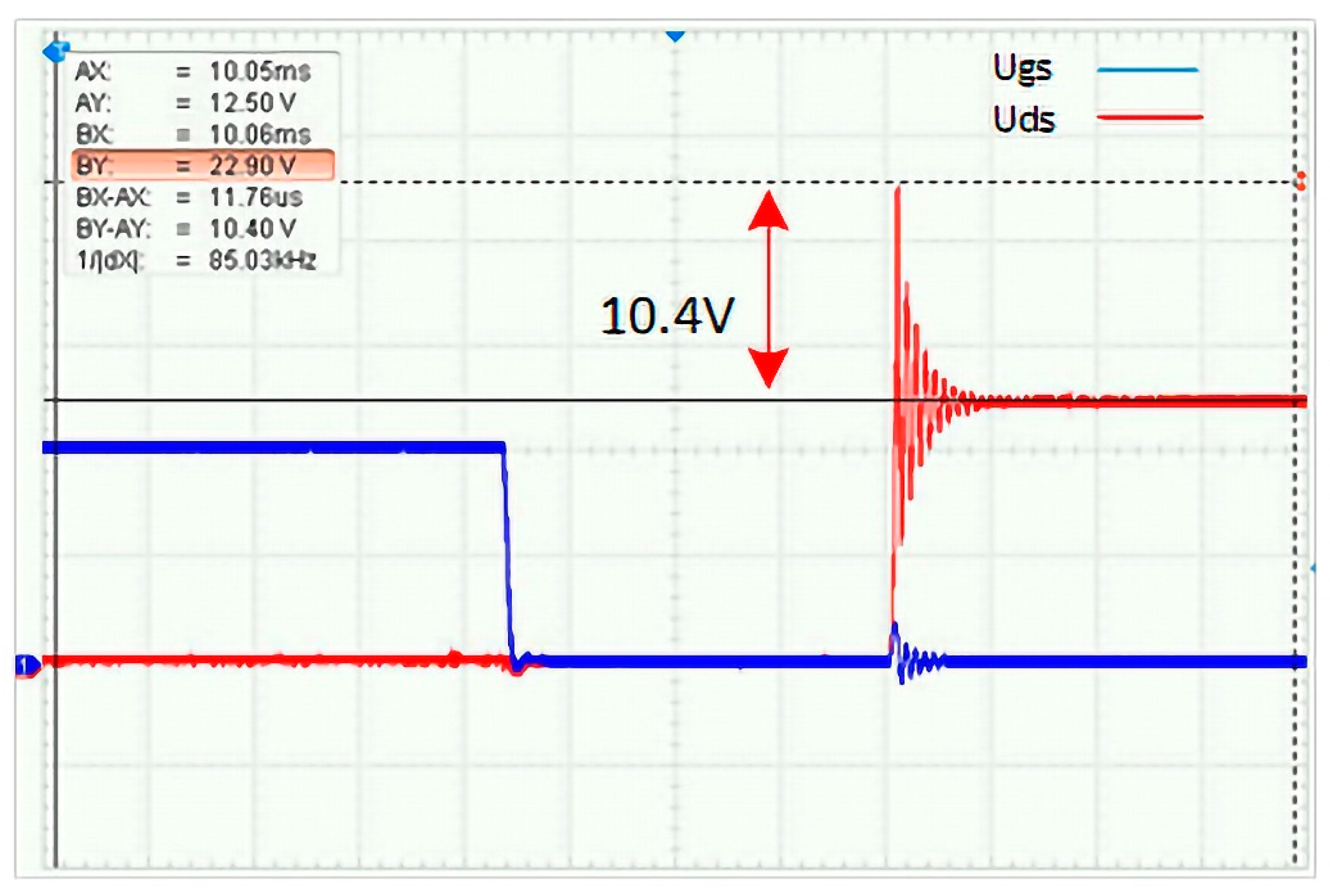

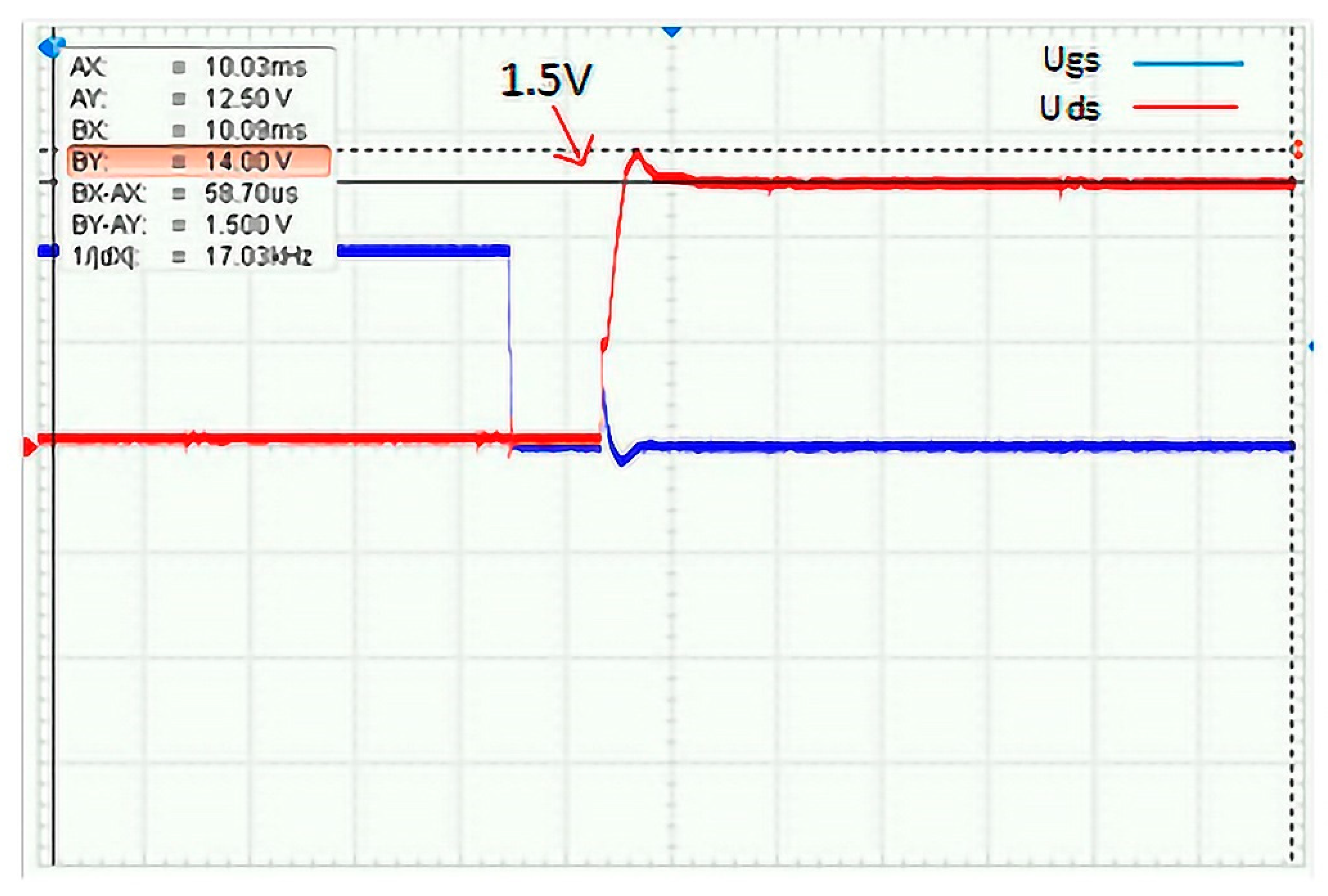

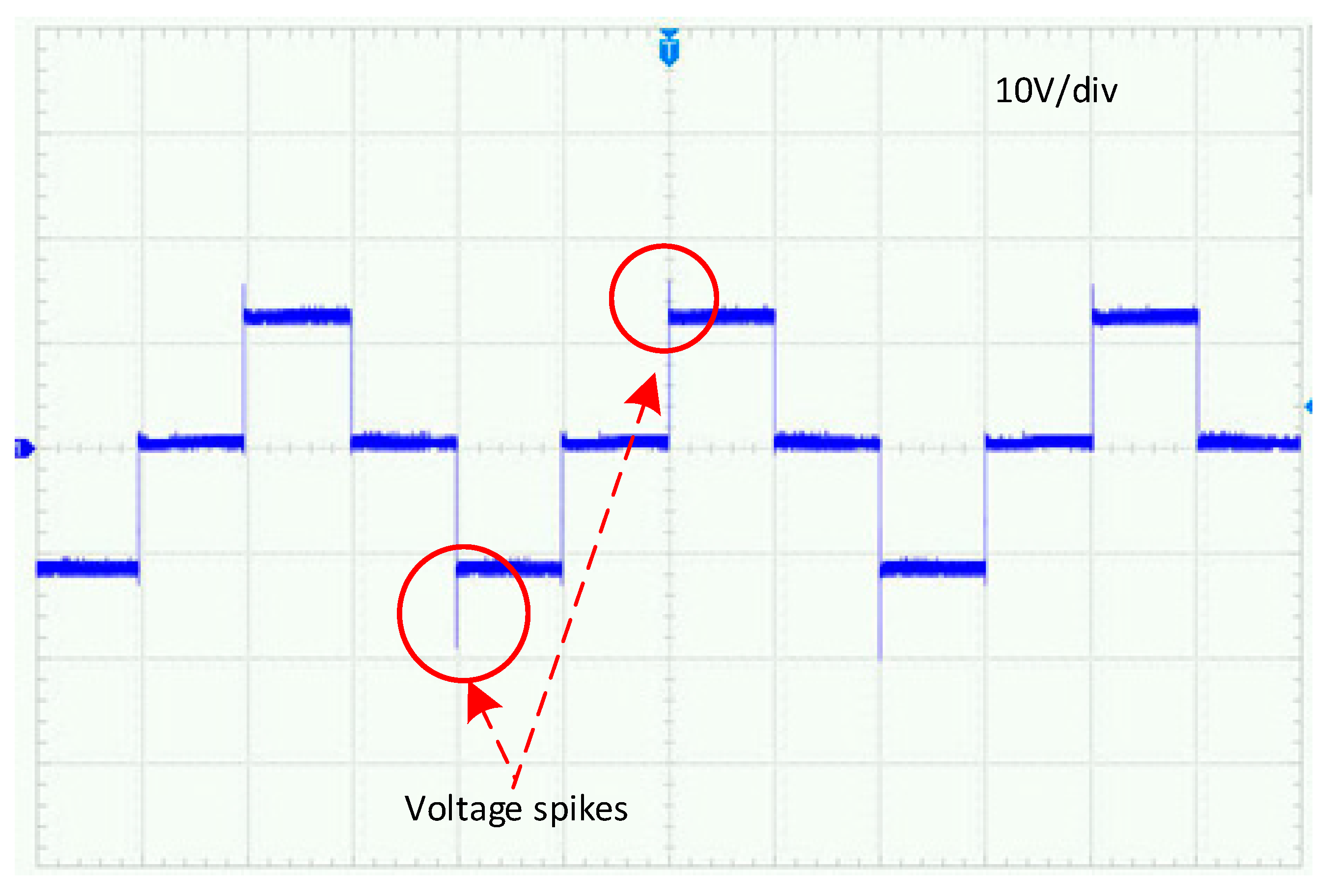

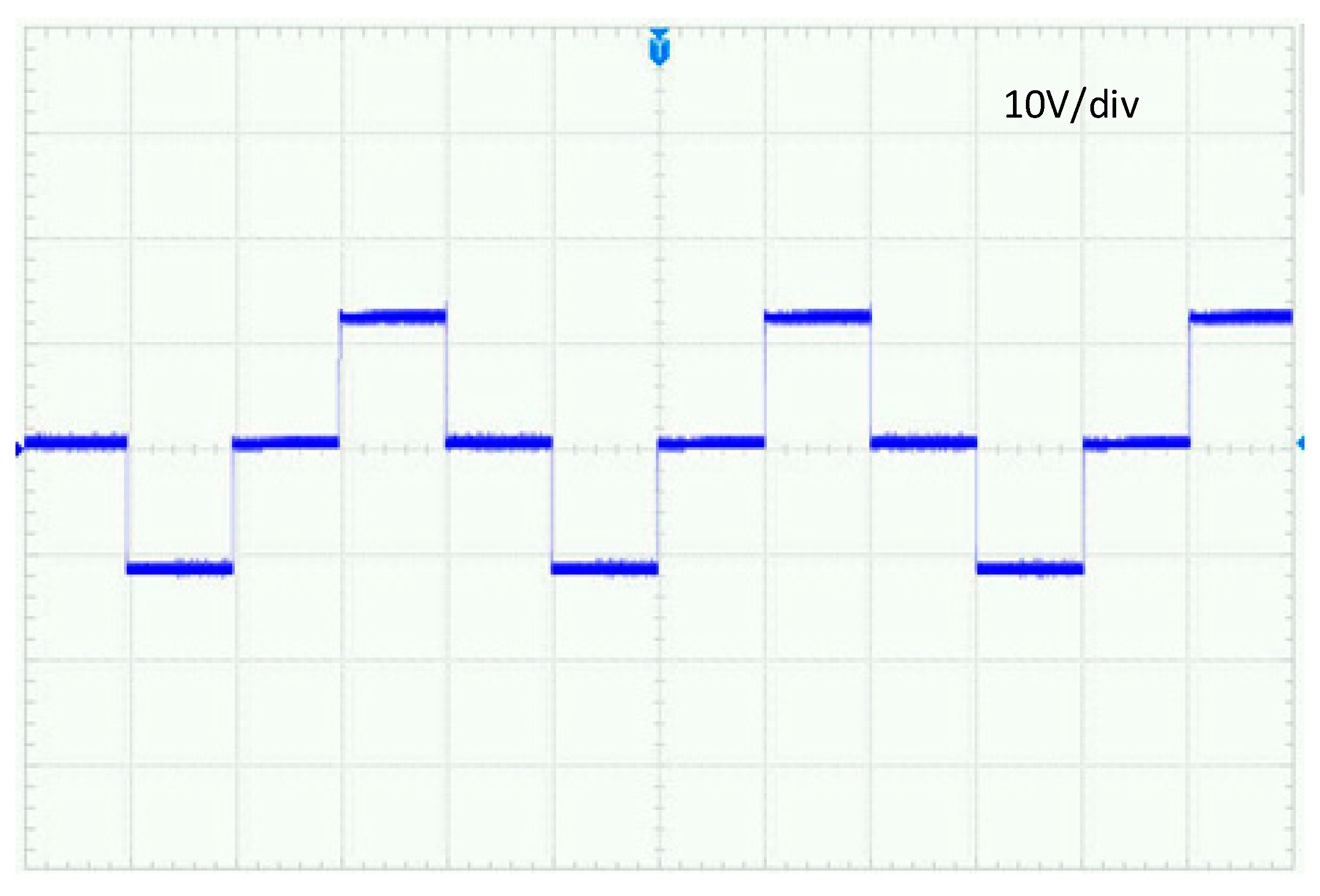

6.1. 50 Hz Switching Results

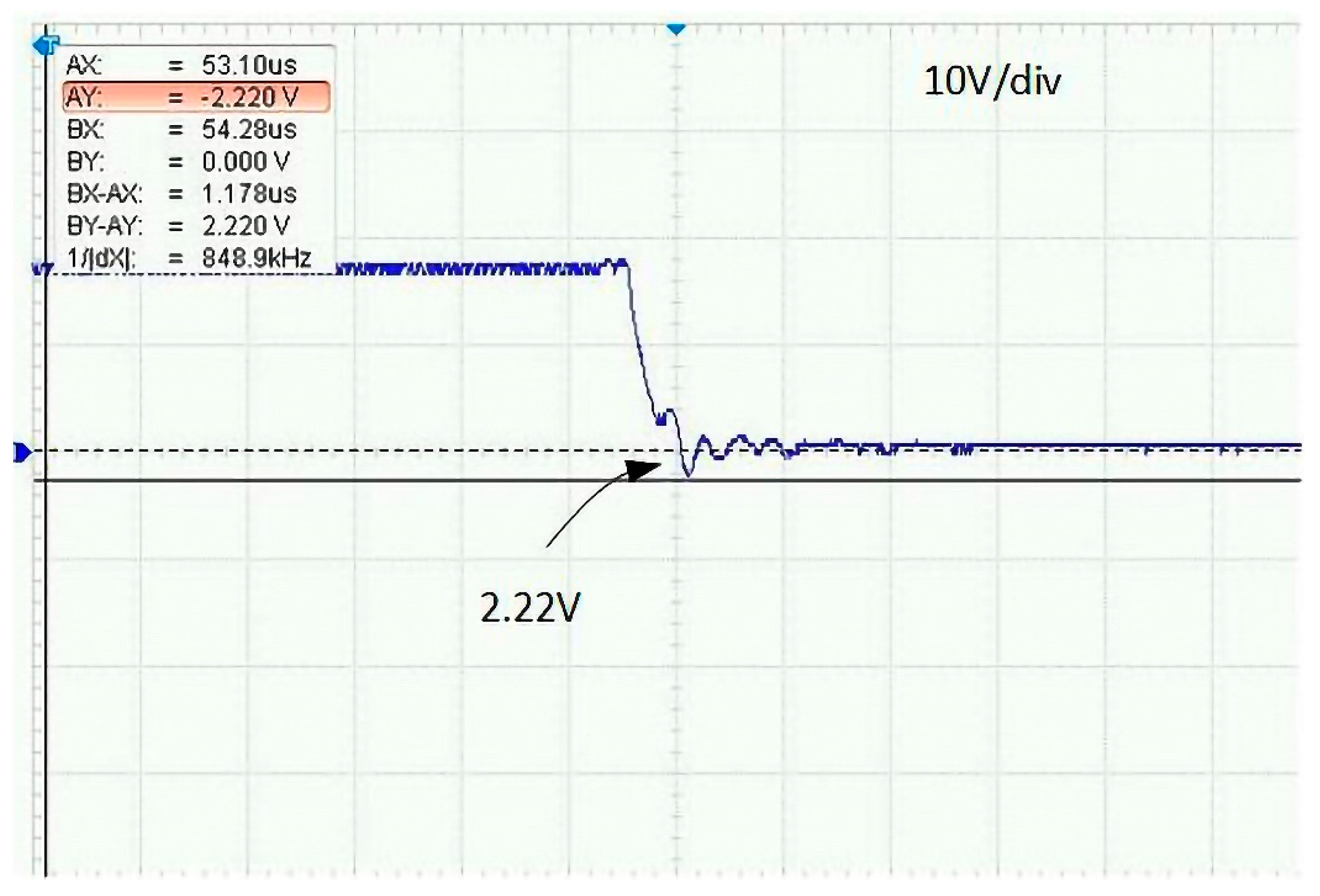

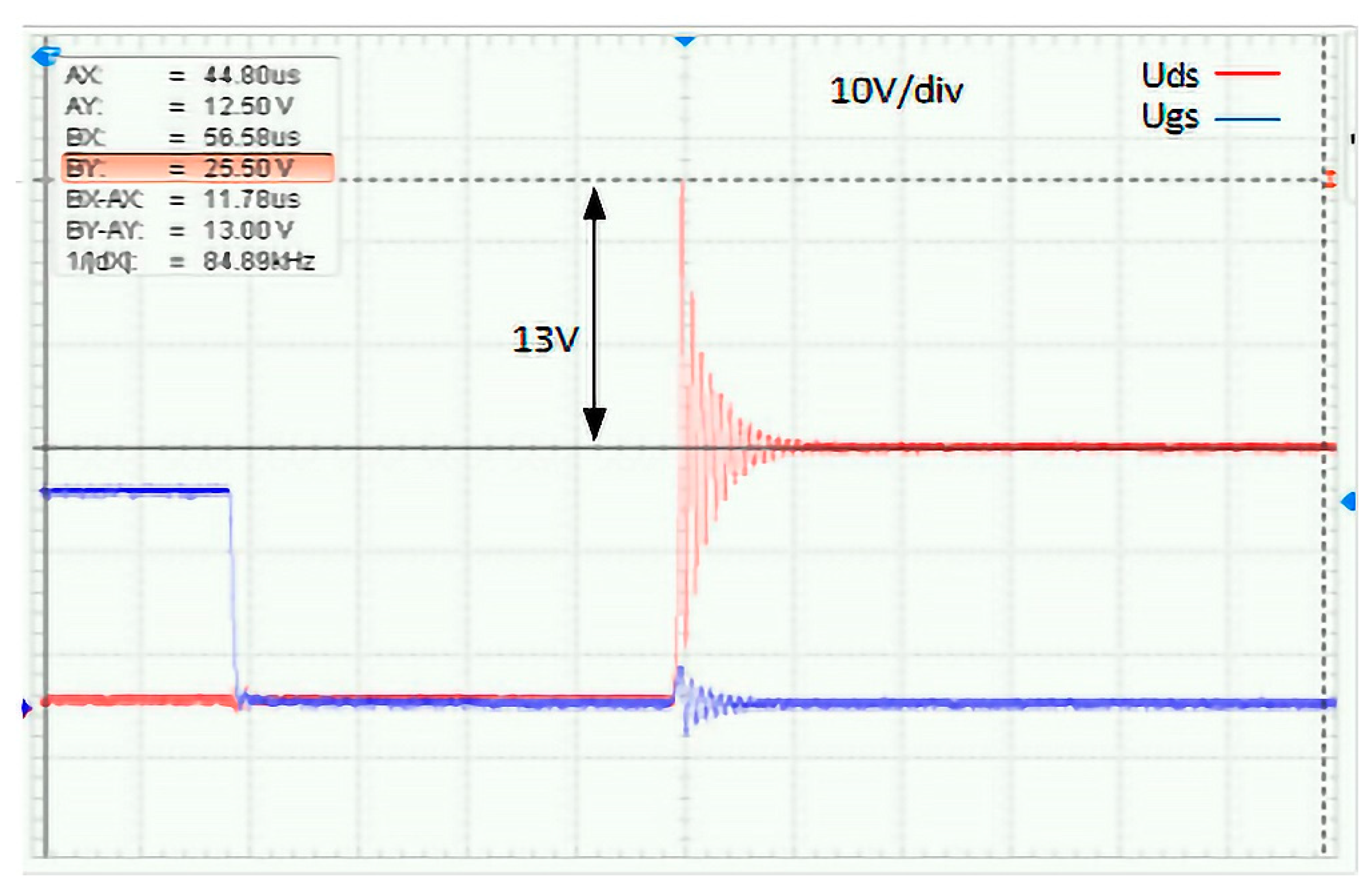

6.2. 10 KHz Switching Frequency

7. Comparison of MOSFET Gate Driver Techniques for Suppressing Voltage Spikes

8. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Gautam, S.P.; Kumar, L.; Gupta, S. Single-phase multilevel inverter topologies with self-voltage balancing capabilities. IET Power Electron. 2018, 11, 844–855. [Google Scholar] [CrossRef]

- Aboadla, E.H.E.; Khan, S.; Habaebi, M.H.; Gunawan, T.; Hamidah, B.A.; Tohtayong, M. Modulation Optimization Effect on Total Harmonic Distortion of Single Phase H-Bridge Inverter Based Selective Harmonics Elimination Technique. In Proceedings of the 2016 International Conference on Computer and Communication Engineering (ICCCE), Kuala Lumpur, Malaysia, 26–27 July 2016; pp. 200–203. [Google Scholar]

- Roshankumar, P.; Rajeevan, P.P.; Mathew, K.; Gopakumar, K.; Leon, J.I.; Franquelo, L.G. A five-level inverter topology with single-DC supply by cascading a flying capacitor inverter and an H-Bridge. IEEE Trans. Power Electron. 2012, 27, 3505–3512. [Google Scholar] [CrossRef]

- Qi, C.; Tu, P.; Wang, P.; Zagrodnik, M.A. Random nearest level modulation strategy of multilevel cascaded H-Bridge inverters. IET Power Electron. 2016, 9, 2706–2713. [Google Scholar] [CrossRef]

- Bae, C.H.; Ryu, J.H.; Lee, K.W. Suppression of Harmonic Spikes in Switching Converter Output Using Dithered Sigma–Delta Modulation. IEEE Trans. Ind. Appl. 2002, 38, 159–166. [Google Scholar]

- Chen, Z.; Yao, Y.; Boroyevich, D.; Ngo, K.; Mattavelli, P. Exploration of a switching loop snubber for parasitic ringing suppression. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition, Pittsburgh, PA, USA, 14–18 September 2014; pp. 1605–1612. [Google Scholar]

- Yatsugi, K.; Nomura, K.; Hattori, Y. Analytical Technique for Designing an RC Snubber Circuit for Ringing Suppression in a Phase-Leg Configuration. IEEE Trans. Power Electron. 2018, 33, 4736–4745. [Google Scholar] [CrossRef]

- Tian, Y.; Yang, X.; Xie, R.; Huang, L.; Liu, T.; Wang, J.; Hao, X. A Passive Component Based Gate Drive Scheme for Negative Gate Voltage Spike Mitigation in a SiC-Based Dual-Active Bridge. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 1841–1845. [Google Scholar]

- Ahmed, M.M.; Hasan, M.K.; Yusoff, N.S.F. Dynamic Load Modeling and Parameter Estimation of 132/275 KV Using PMU-Based Wide Area Measurement System. In International Conference on Innovative Computing and Communications; Springer: Berlin/Heidelberg, Germany, 2020; pp. 1151–1164. [Google Scholar]

- Hasan, M.K.; Ahmed, M.M.; Musa, S.S. Measurement and Modeling of DTCR Software Parameters Based on Intranet Wide Area Measurement System for Smart Grid Applications. In International Conference on Innovative Computing and Communications; Springer: Berlin/Heidelberg, Germany, 2020; pp. 1139–1150. [Google Scholar]

- Akhtaruzzaman, M.; Hasan, M.K.; Kabir, S.R.; Abdullah, S.N.H.S.; Sadeq, M.J.; Hossain, E. HSIC Bottleneck Based Distributed Deep Learning Model for Load Forecasting in Smart Grid With a Comprehensive Survey. IEEE Access 2020, 8, 222977–223008. [Google Scholar] [CrossRef]

- Habib, A.A.; Motakabber, S.; Ibrahimy, M.; Hasan, M. Active voltage balancing circuit using single switched-capacitor and series LC resonant energy carrier. Electron. Lett. 2020, 56, 1036–1039. [Google Scholar] [CrossRef]

- Habib, A.K.M.A.; Hasan, M.K.; Motakabber, S.; Mahmud, M.; Islam, S. A Review: Energy Storage System and Balancing Circuits for Electric Vehicle Application. IET Power Electron. 2020, 14, 1–16. [Google Scholar] [CrossRef]

- Kim, S.H.; Lee, K.B. Elimination of harmonic spikes using second-order Space Dithered Sigma-Delta Modulation. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10. [Google Scholar]

- Vinod, B.R.; Shiny, G.; Baiju, M.R. Space vector direct torque control for five-level open-end winding induction motor drive to suppress harmonic spikes. In Proceedings of the 2017 IEEE Region 10 Symposium (TENSYMP), Cochin, India, 14–16 July 2017; pp. 1–5. [Google Scholar]

- Ishikawa, K.; Ogawa, K.; Yukutake, S.; Kameshiro, N.; Kono, Y. Traction Inverter that applies compact 3.3kV/1200A SiC hybrid module. In Proceedings of the 2014 International Power Electronics Conference, Shanghai, China, 5–8 November 2014; pp. 2140–2144. [Google Scholar]

- Wang, J.; Chung, H.S.H. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration. IEEE Trans. Power Electron. 2015, 30, 976–984. [Google Scholar] [CrossRef]

- He, X.; Chen, A.; Wu, H.; Deng, Y.; Zhao, R. Simple passive lossless snubber for high-power multilevel inverters. IEEE Trans. Ind. Electron. 2006, 53, 727–735. [Google Scholar]

- Yamamoto, M.; Shinji, S.; Mutsuo, N. A Novel Voltage Clamped Snubber Circuit Topology Suitable for a Multilevel Inverter with Lowered Power Loss Performance. Electr. Eng. Jpn. 2005, 150, 995–1003. [Google Scholar] [CrossRef]

- Fu, J.; Li, C.; Zhu, C. Influence of RCD snubber circuit on the commutation process of high-power three-level inverter with 4.5 kV IEGTs. In Proceedings of the 2016 19th International Conference on Electrical Machines and Systems (ICEMS), Chiba, Japan, 13–16 November 2016; pp. 1–6. [Google Scholar]

- Pronin, M.V.; Vorontsov, A.G.; Grigoryan, A.S.; Mamutov, A.R.; Dikun, I.A. Modeling of IGBT-converters by interconnected subsystems with considering of snubber circuit and switching transistor time. In Proceedings of the 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), Moscow, Russia, 29 January–1 February 2018; pp. 748–753. [Google Scholar]

- Lee, Y.; Kim, J.; Cho, E. Design of Bus-Side RCD Snubber Circuit for Three-Phase High-Power Inverters. Can. J. Electr. Comput. Eng. 2018, 41, 55–61. [Google Scholar]

- Kim, J.H.; Park, D.H.; Kim, J.B.; Kwon, B.H. An active gate drive circuit for high power inverter system to reduce turn-off spike voltage of IGBT. In Proceedings of the 2007 7th International Conference on Power Electronics, Daegu, Korea, 22–26 October 2007; pp. 127–131. [Google Scholar]

- Gao, F.; Zhou, Q.; Wang, P.; Zhang, C. A gate driver of SiC MOSFET for suppressing the negative voltage spikes in a bridge circuit. IEEE Trans. Power Electron. 2017, 33, 2339–2353. [Google Scholar] [CrossRef]

- Jiang, Y.; Feng, C.; Yang, Z.; Zhao, X.; Li, H. A new active gate driver for MOSFET to suppress turn-off spike and oscillation. Chin. J. Electr. Eng. 2018, 4, 43–49. [Google Scholar]

- Zushi, Y.; Sato, S.; Matsui, K.; Murakami, Y.; Tanimoto, S. A novel gate assist circuit for quick and stable driving of SiC-JFETs in a 3-phase inverter. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 1734–1739. [Google Scholar]

- Yamaguchi, K.; Katsura, K.; Yamada, T.; Sato, Y. Comprehensive study on gate driver for SiC-MOSFETs with gate boost. IEEJ J. Ind. Appl. 2018, 7, 218–228. [Google Scholar] [CrossRef]

- Yin, S.; Tseng, K.J.; Tong, C.F.; Simanjorang, R.; Gajanayake, C.J.; Gupta, A.K. A novel gate assisted circuit to reduce switching loss and eliminate shoot-through in SiC half bridge configuration. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 3058–3064. [Google Scholar]

- Zaman, H.; Wu, X.; Zheng, X.; Khan, S.; Ali, H. Suppression of switching crosstalk and voltage oscillations in a SiC MOSFET based half-bridge converter. Energies 2018, 11, 3111. [Google Scholar] [CrossRef]

- Li, H.; Liao, X.; Hu, Y.; Huang, Z.; Wang, K. Analysis of voltage variation in silicon carbide MOSFETs during turn-on and turn-off. Energies 2017, 10, 1456. [Google Scholar] [CrossRef]

- Aboadla, E.H.; Khan, S.; Habaebi, M.H.; Gunawan, T.S.; Hamida, B.A.; Yaacob, M.B.; Aboadla, A. A novel optimization harmonic elimination technique for cascaded multilevel inverter. Bull. Electr. Eng. Inform. 2019, 8, 405–413. [Google Scholar] [CrossRef]

- Wang, L.; Wu, Q.H.; Tang, W. Novel cascaded switched-diode multilevel inverter for renewable energy integration. IEEE Trans. Energy Convers. 2017, 32, 1574–1582. [Google Scholar] [CrossRef]

- HV Floating MOS-Gate Driver ICs. Available online: https://www.infineon.com/dgdl/Infineon-HV_Floating_MOS_Gate_Drivers-ApplicationNotes-v01_00-EN.pdf?fileId=5546d4626c1f3dc3016c47de609d140a (accessed on 6 January 2021).

- Semiconductor, F. Design and Application Guide of Bootstrap Circuit for High-Voltage Gate-Drive IC. Available online: https://www.eeweb.com/wp-content/uploads/articles-app-notes-files-design-and-application-guide-of-bootstrap-circuit-for-high-voltage-gate-drive-ic.pdf (accessed on 6 January 2021).

- Yu, S.; Zhu, J.; Lu, Y.; Li, D.; Wang, Y.; Xiang, Z.; Zhang, Y.; Zhang, L.; Sun, W. A self-adaptive pulse generator to realize extremely low power consumption and high reliability of high voltage gate driver IC. Analog Integr. Circuits Signal Process. 2020, 105, 13–20. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| DC voltage | 12 V |

| Switching frequency | 50 Hz & 10 kHz |

| Load inductance | 100 µH |

| Load Resistance | 100 Ω |

| Gate resistor R | 10 Ω |

| Reference | Proposed Technique | Suppressing of Positive Voltage Spike | Suppressing of Negative Voltage Spike |

|---|---|---|---|

| [9] | A new gate drive based on adjustment of magnetic bead’s | No | Yes |

| [18] | RCD level-shifter for bridge-leg configuration | Yes | No |

| [25] | A passive triggered transistor with a series capacitor to suppress the negative voltage spikes | Yes | Yes |

| [26] | Active Gate Driver for MOSFET to Suppress Turn-Off Spike and Oscillation | No | Yes |

| The proposed | Improvement of gate driver circuit for MOSFET | Yes | Yes |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aboadla, E.H.; Khan, S.; Abdul Kadir, K.; Md Yusof, Z.; Habaebi, M.H.; Habib, S.; Islam, M.; Hasan, M.K.; Hossain, E. Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit. Electronics 2021, 10, 390. https://doi.org/10.3390/electronics10040390

Aboadla EH, Khan S, Abdul Kadir K, Md Yusof Z, Habaebi MH, Habib S, Islam M, Hasan MK, Hossain E. Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit. Electronics. 2021; 10(4):390. https://doi.org/10.3390/electronics10040390

Chicago/Turabian StyleAboadla, Ezzidin Hassan, Sheroz Khan, Kushsairy Abdul Kadir, Zulkhairi Md Yusof, Mohamed Hadi Habaebi, Shabana Habib, Muhammad Islam, Mohammad Kamrul Hasan, and Eklas Hossain. 2021. "Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit" Electronics 10, no. 4: 390. https://doi.org/10.3390/electronics10040390

APA StyleAboadla, E. H., Khan, S., Abdul Kadir, K., Md Yusof, Z., Habaebi, M. H., Habib, S., Islam, M., Hasan, M. K., & Hossain, E. (2021). Suppressing Voltage Spikes of MOSFET in H-Bridge Inverter Circuit. Electronics, 10(4), 390. https://doi.org/10.3390/electronics10040390