Body-Effect-Free OLED-on-Silicon Pixel Circuit Based on Capacitive Division to Extend Data Voltage Range

Abstract

:1. Introduction

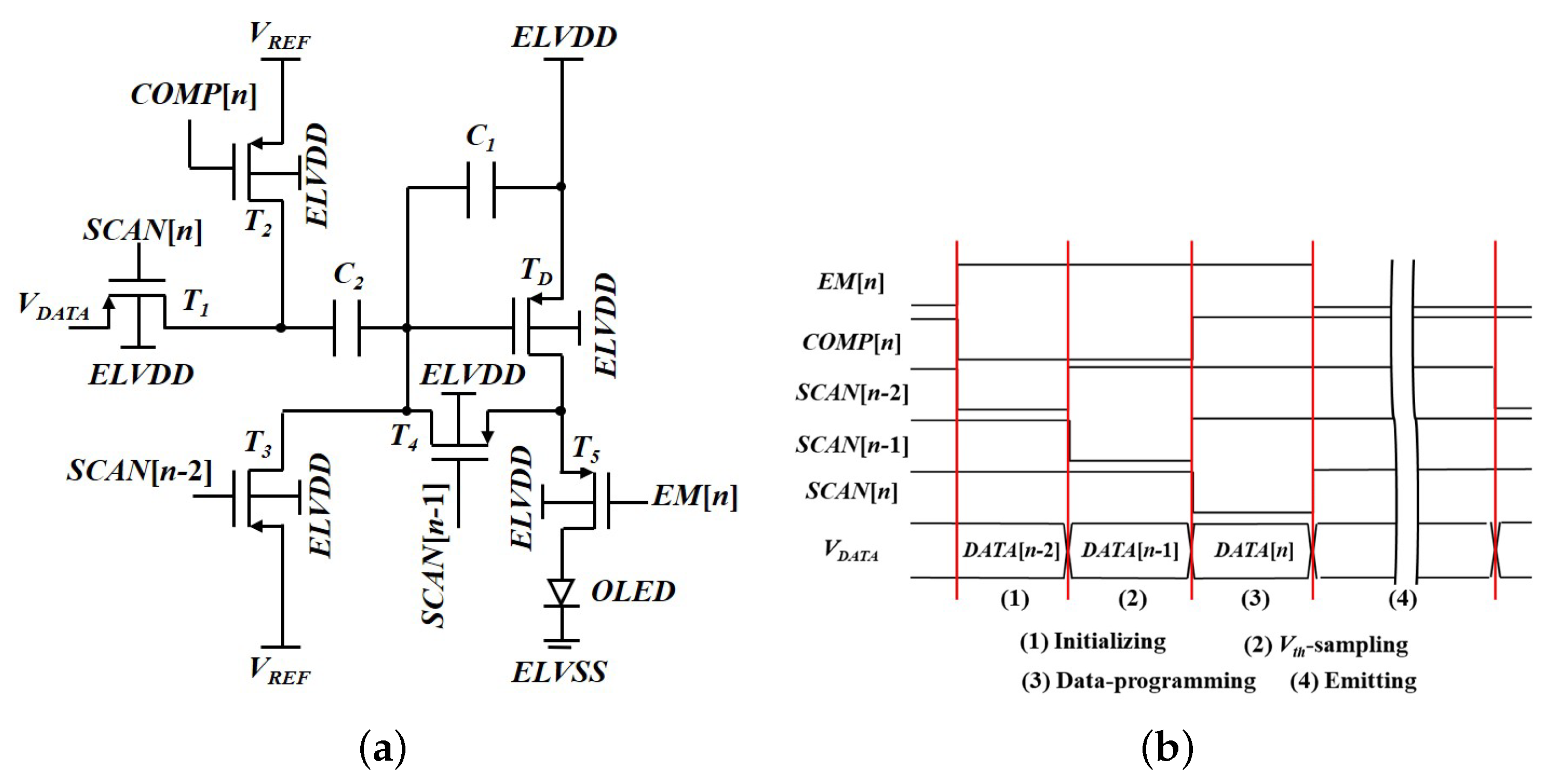

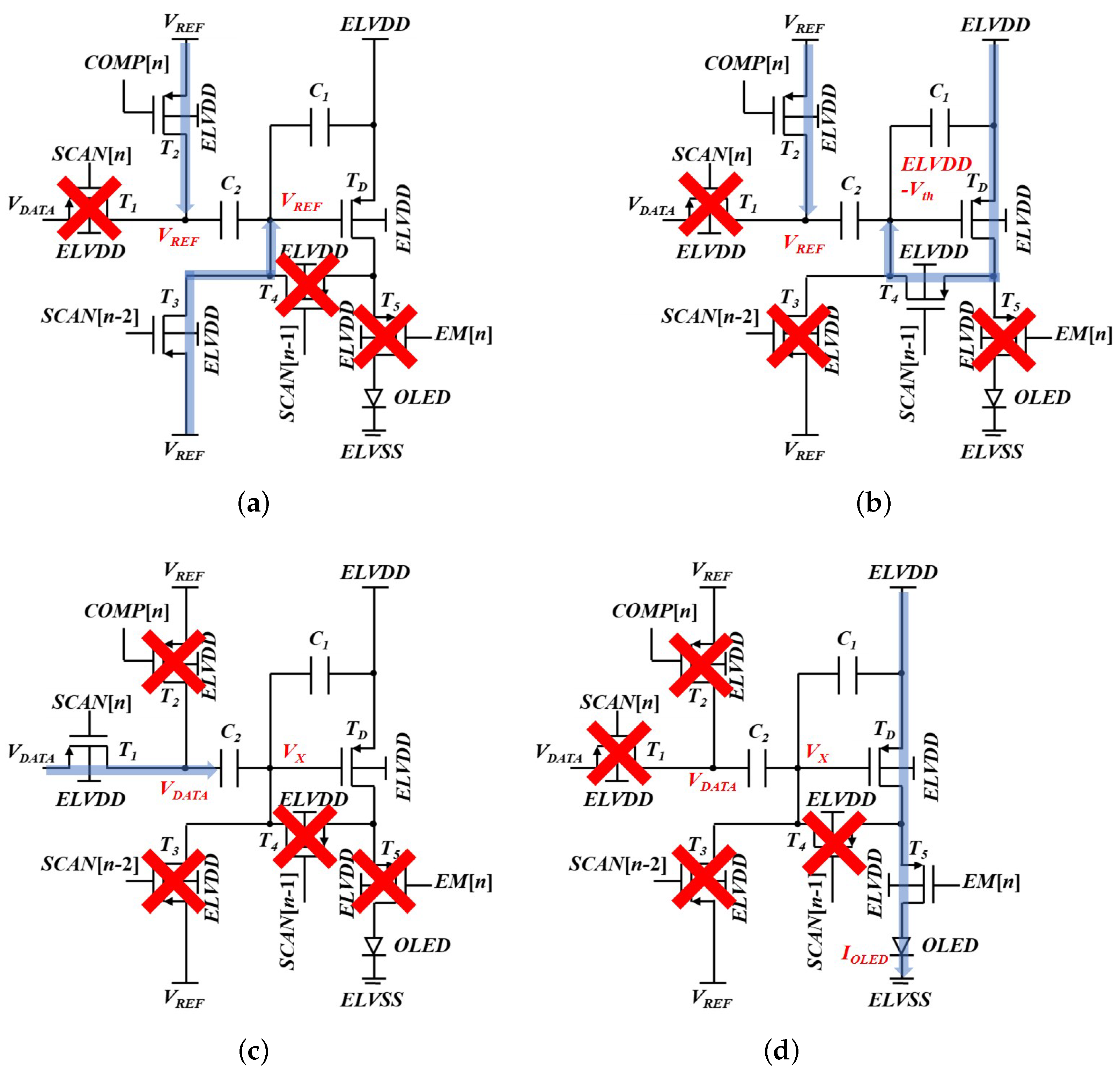

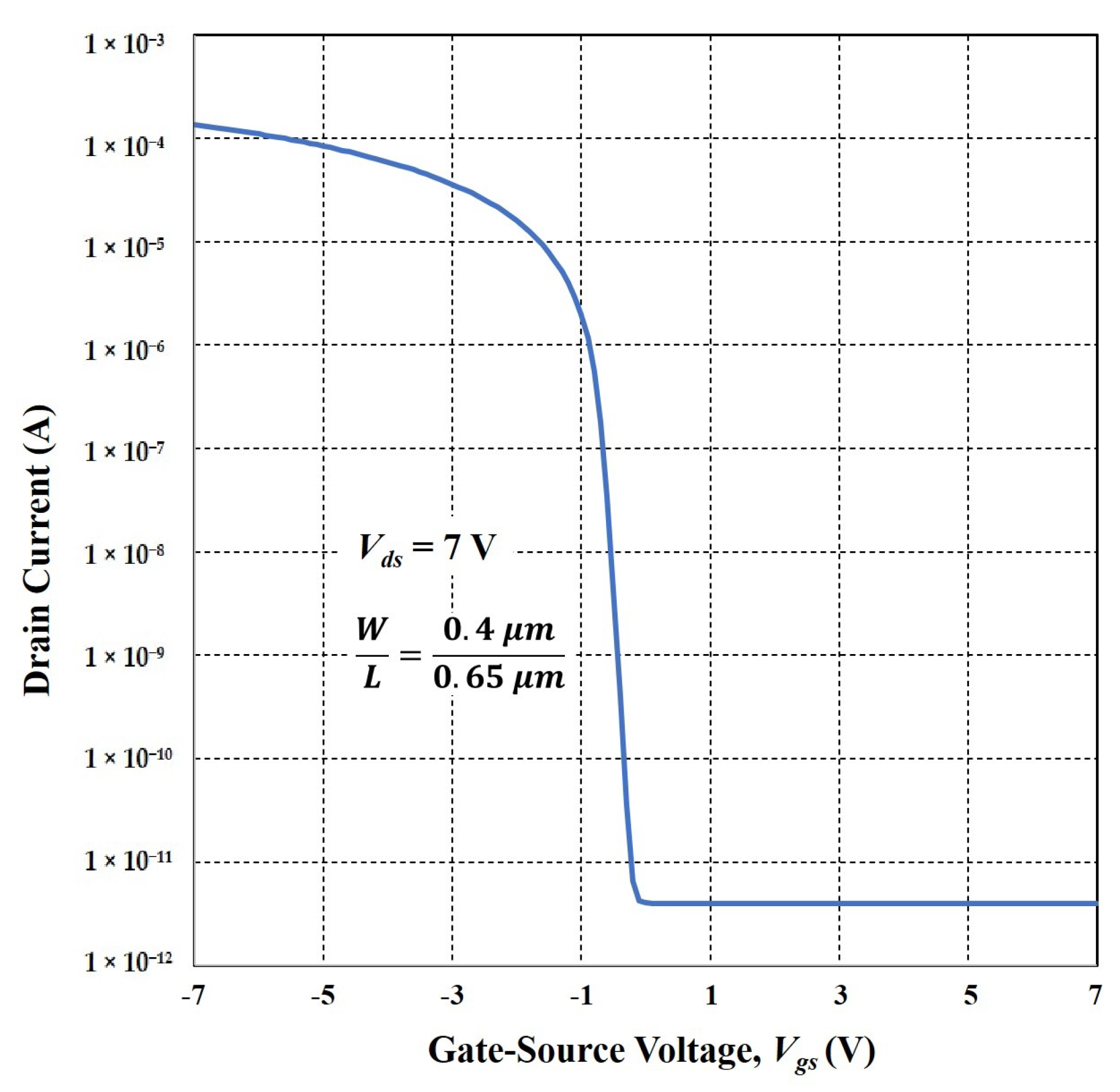

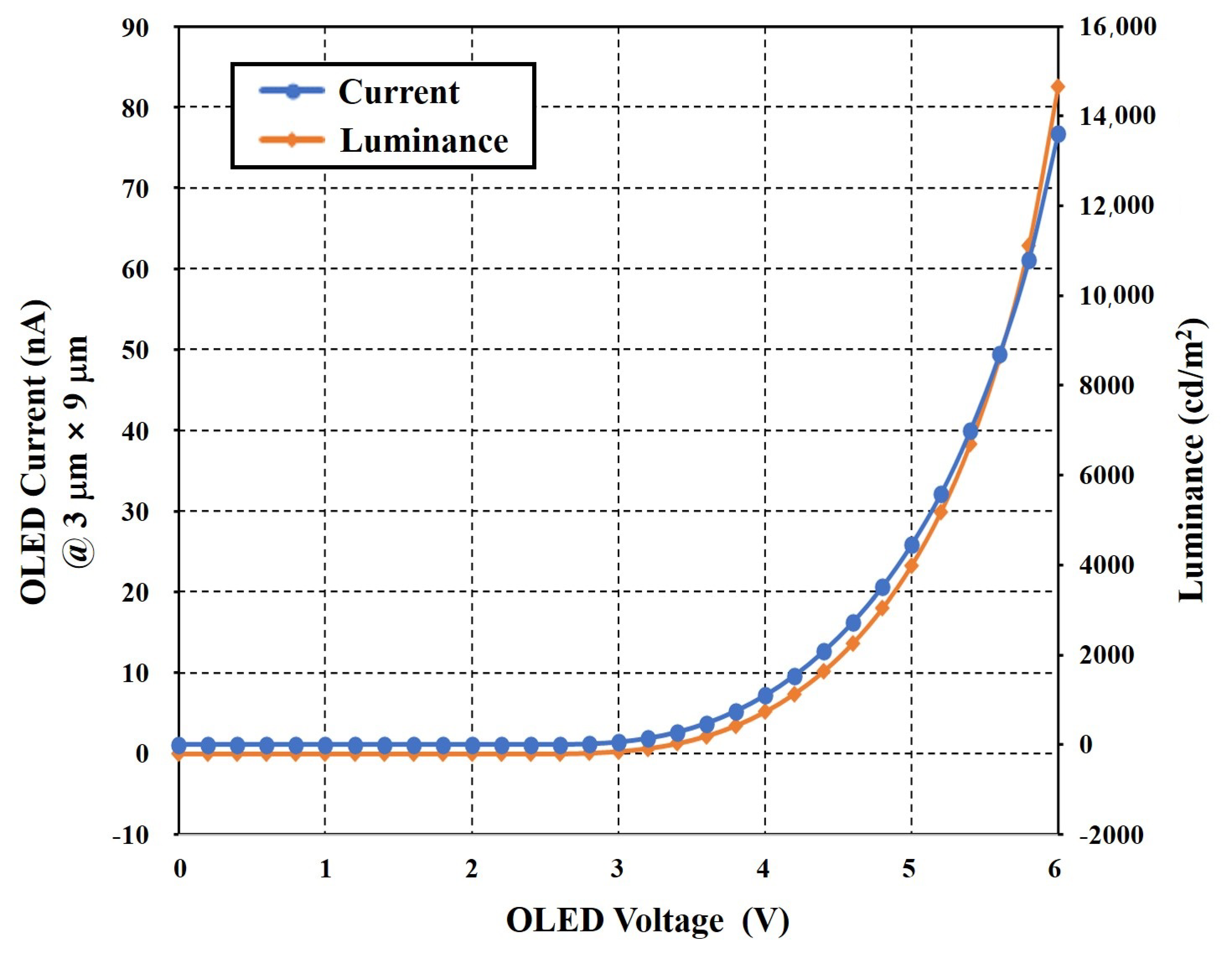

2. Proposed OLEDoS Pixel Circuit

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Paavilainen, J.; Korhonen, H.; Alha, K.; Stenros, J.; Koskinen, E.; Mayra, F. The Pokémon GO Experience: A Location-Based Augmented Reality Mobile Game Goes Mainstream. Proc. CHI 2017, 2017, 2493–2498. [Google Scholar]

- Al-Azawi, R.; Shakkah, M.S. Embedding augmented and virtual reality in educational learning method: Present and future. In Proceedings of the ICICS 2018, Lille, France, 29–31 October 2018; pp. 218–222. [Google Scholar]

- Farshid, M.; Paschen, J.; Eriksson, T.; Kietzmann, J. Go boldly!: Explore augmented reality (AR), virtual reality (VR), and mixed reality (MR) for business. Bus. Horiz. 2018, 61, 657–663. [Google Scholar] [CrossRef]

- Lungu, A.J.; Swinkels, W.; Claesen, L.; Tu, P.; Egger, J.; Chen, X. A review on the applications of virtual reality, augmented reality and mixed reality in surgical simulation: An extension to different kinds of surgery. Expert Rev. Med. Devices 2020, in press. [Google Scholar] [CrossRef]

- Izard, S.G.; Méndez, J.A.J.; Palomera, P.R.; García-Peñalvo, F.J. Applications of Virtual and Augmented Reality in Biomedical Imaging. J. Med. Syst. 2019, 43, 102. [Google Scholar] [CrossRef] [PubMed]

- Yung, R.; Khoo-Lattimore, C. New realities: A systematic literature review on virtual reality and augmented reality in tourism research. Curr. Issues Tour. 2019, 22, 2056–2081. [Google Scholar] [CrossRef]

- Muñoz-Saavedra, L.; Miró-Amarante, L.; Domínguez-Morales, M. Augmented and Virtual Reality Evolution and Future Tendency. Appl. Sci. 2020, 10, 322. [Google Scholar] [CrossRef] [Green Version]

- Zhan, T.; Yin, K.; Xiong, J.; He, Z.; Wu, S.T. Augmented Reality and Virtual Reality Displays: Perspectives and Challenges. iScience 2020, 23, 101397. [Google Scholar] [CrossRef] [PubMed]

- Han, M.K. AM backplane for AMOLED. In Proceedings of the ASID, New Delhi, India, 8–12 October 2006; pp. 53–58. [Google Scholar]

- Lee, J.H.; Nam, W.J.; Kim, B.K.; Choi, H.S.; Ha, Y.M.; Han, M.K. A New Poly-Si TFT Current-Mirror Pixel for Active Matrix Organic Light Emitting Diode. IEEE Electron. Device Lett. 2006, 27, 830–833. [Google Scholar] [CrossRef]

- Kim, Y.W.; Kwak, W.K.; Lee, J.Y.; Choi, W.S.; Lee, K.Y.; Kim, S.C.; Yoo, E.J. 40 Inch FHD AM-OLED Display with IR Drop Compensation Pixel Circuit. In Proceedings of the SID, San Antonio, TX, USA, 1–5 June 2009; pp. 85–87. [Google Scholar]

- Lee, B.W.; Ji, I.H.; Han, S.M.; Sung, S.D.; Shin, K.S.; Lee, J.D.; Kim, B.H.; Berkeley, B.H.; Kim, S.S. Novel Simultaneous Emission Driving Scheme for Crosstalk-free 3D AMOLED TV. In Proceedings of the SID, Seattle, WA, USA, 25–27 May 2010; pp. 758–761. [Google Scholar]

- In, H.J.; Kwon, O.K. A Simple Pixel Structure Using Polycrystalline-Silicon Thin-Film Transistors for High-Resolution Active-Matrix Organic Light-Emitting Diode Displays. IEEE Electron. Device Lett. 2012, 33, 1018–1020. [Google Scholar] [CrossRef]

- Song, E.; Nam, H. Novel voltage programming n-channel TFT pixel circuit for low power and high performance AMOLED displays. Displays 2014, 35, 118–125. [Google Scholar] [CrossRef]

- Seol, K.H.; Kim, Y.I.; Park, S.; Nam, H. Simultaneous Emission AC-OLED Pixel Circuit for Extended Lifetime of OLED Display. IEEE J. Electron. Devices Soc. 2018, 6, 835–840. [Google Scholar] [CrossRef]

- Kim, H.; Kwak, B.C.; Lim, H.S.; Kwon, O.K. Pixel Circuit for Organic Light-Emitting Diode-on Silicon Microdisplays Using the Source Follower Structure. Jpn. J. Appl. Phys. 2010, 49, 03CD05. [Google Scholar] [CrossRef]

- Kwak, B.C.; Lim, H.S.; Kwon, O.K. Organic Light-Emitting Diode-on-Silicon Pixel Circuit Using the Source Follower Structure with Active Load for Microdisplays. Jpn. J. Appl. Phys. 2011, 50, 03CC05. [Google Scholar] [CrossRef]

- Liu, B.; Ding, D.; Zhou, T.; Zhang, M. A Novel Pixel Circuit Providing Expanded Input Voltage Range for OLEDoS Microdisplays. In Proceedings of the SID, Los Angeles, CA, USA, 23–26 May 2017; pp. 1438–1441. [Google Scholar]

- Hong, S.W.; Kwak, B.C.; Na, J.S.; Hong, S.K.; Kwon, O.K. Simple pixel circuits for high resolution and high image quality organic light emitting diode-on-silicon microdisplays with wide data voltage range. J. Soc. Inf. Disp. 2016, 24, 110–116. [Google Scholar] [CrossRef]

- Huo, X.; Liao, C.; Wu, J.; Yi, S.; Wang, Y.; Jiao, H.; Zhang, M.; Zhang, S. An OLEDoS Pixel Circuit with Extended Data Voltage Range for High Resolution Micro-Displays. In Proceedings of the SID, Los Angeles, CA, USA, 22–25 May 2018; pp. 1373–1376. [Google Scholar]

- Na, J.S.; Hong, S.K.; Kwon, O.K. A 4410-ppi Resolution Pixel Circuit for High Luminance Uniformity of OLEDoS Microdisplays. IEEE J. Electron. Devices Soc. 2019, 7, 1026–1032. [Google Scholar] [CrossRef]

| Simulation Parameters | Value |

|---|---|

| −0.7688 V | |

| n @ sub-threshold | 1.42 |

| @ sub-threshold | A |

| Channel Length | 0.65 m |

| Channel Width | 0.4 m |

| 26 fF | |

| 4 fF | |

| / | 7 V/0 V |

| 4 V | |

| Maximum | 8 nA |

| Frame Rate | 60 Hz @ FHD |

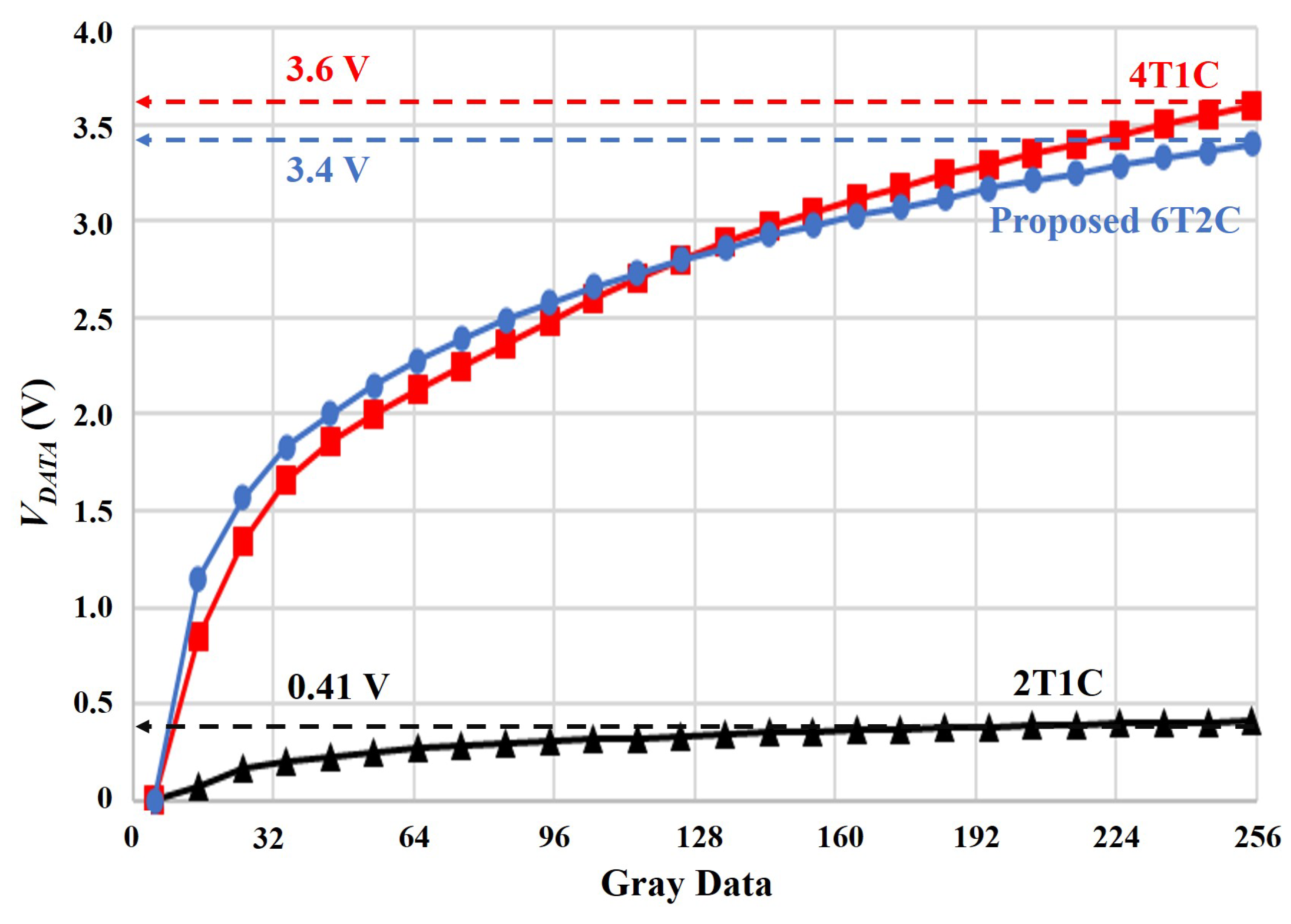

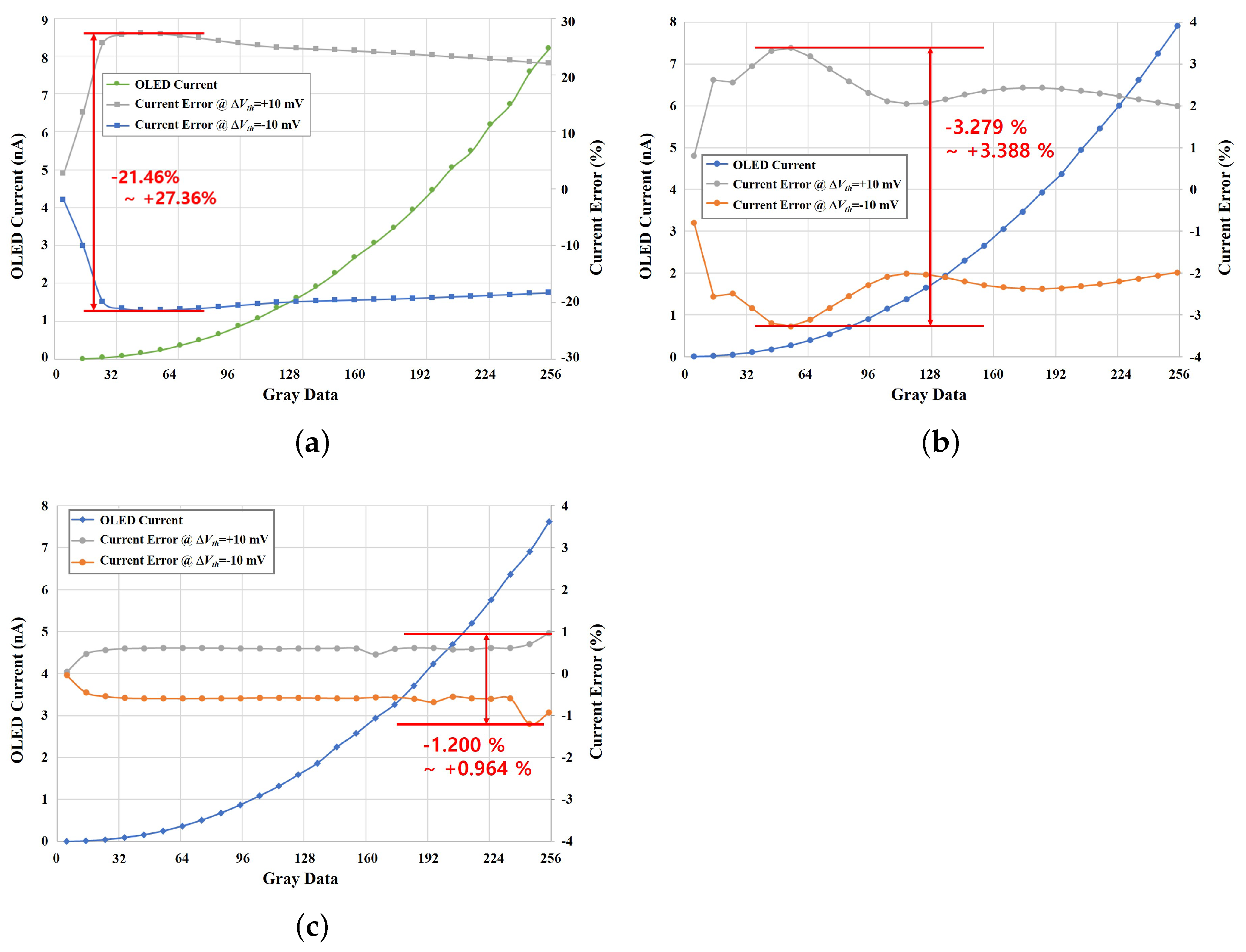

| 2T1C | 4T1C [21] | This Work (6T2C) | |

|---|---|---|---|

| Range | 0.41 V | 3.6 V | 3.4 V |

| Region Control | Not Applicable | Not Applicable | Separate |

| Error | −21.46% to 27.36% | −3.279% to 3.388% | −1.200% to 0.964% |

| Body Effect | No | Yes | No |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, J.; Nam, H. Body-Effect-Free OLED-on-Silicon Pixel Circuit Based on Capacitive Division to Extend Data Voltage Range. Electronics 2021, 10, 2351. https://doi.org/10.3390/electronics10192351

Bae J, Nam H. Body-Effect-Free OLED-on-Silicon Pixel Circuit Based on Capacitive Division to Extend Data Voltage Range. Electronics. 2021; 10(19):2351. https://doi.org/10.3390/electronics10192351

Chicago/Turabian StyleBae, Jina, and Hyoungsik Nam. 2021. "Body-Effect-Free OLED-on-Silicon Pixel Circuit Based on Capacitive Division to Extend Data Voltage Range" Electronics 10, no. 19: 2351. https://doi.org/10.3390/electronics10192351

APA StyleBae, J., & Nam, H. (2021). Body-Effect-Free OLED-on-Silicon Pixel Circuit Based on Capacitive Division to Extend Data Voltage Range. Electronics, 10(19), 2351. https://doi.org/10.3390/electronics10192351