A Chopper-Embedded BGR Composite Noise Reduction Circuit for Clock Generator

Abstract

:1. Introduction

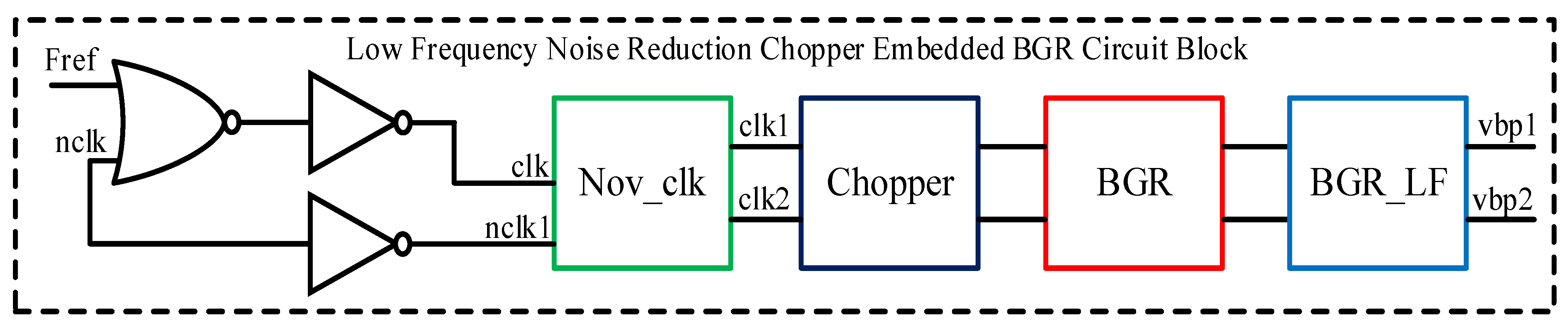

2. Chopper-Stabilized Composite BGR Scheme

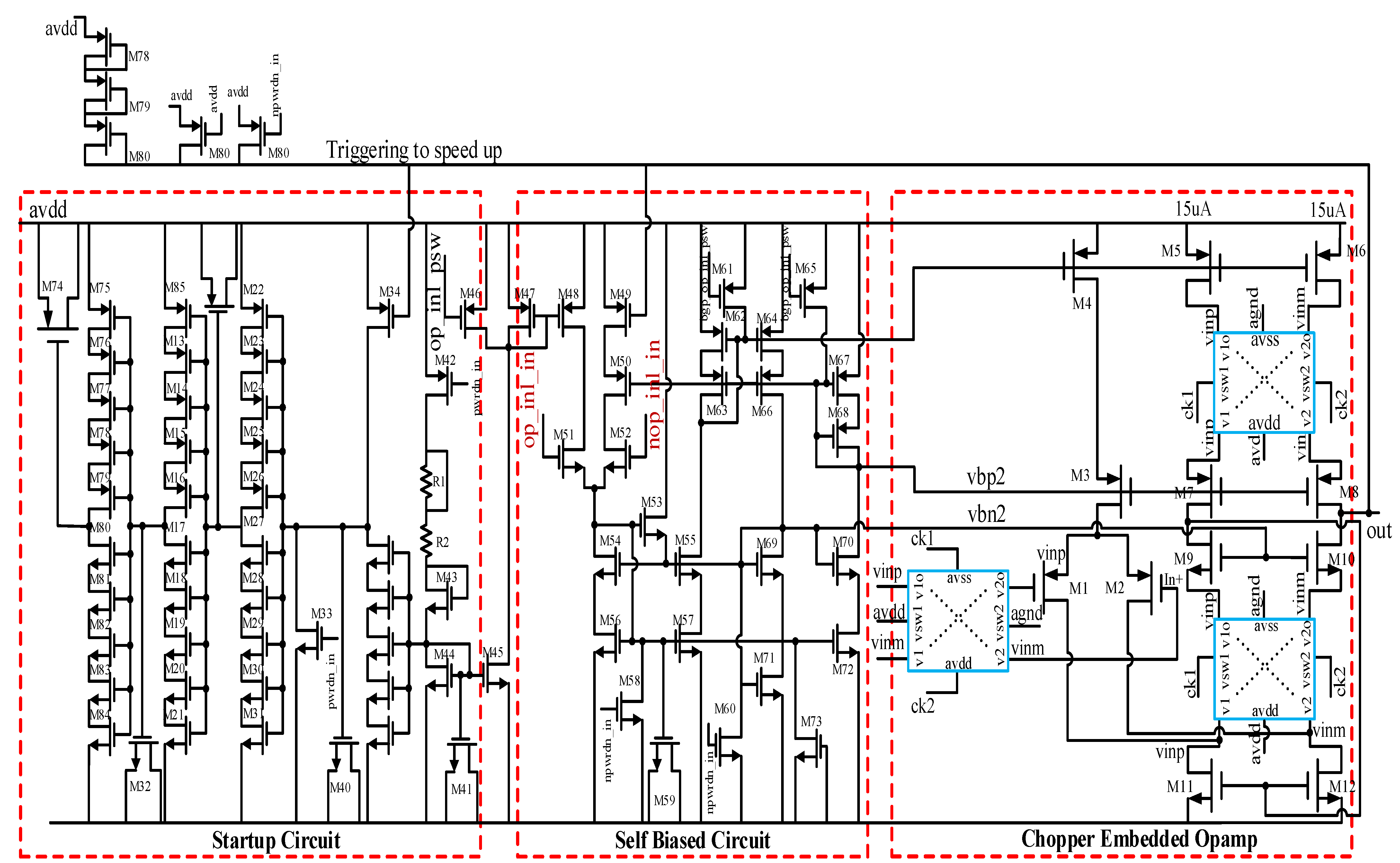

2.1. BGR Chopper-Embedded OTA with Startup and Self-Biasing Circuit

2.1.1. Operational Transconductance Amplifier

2.1.2. Startup Circuit

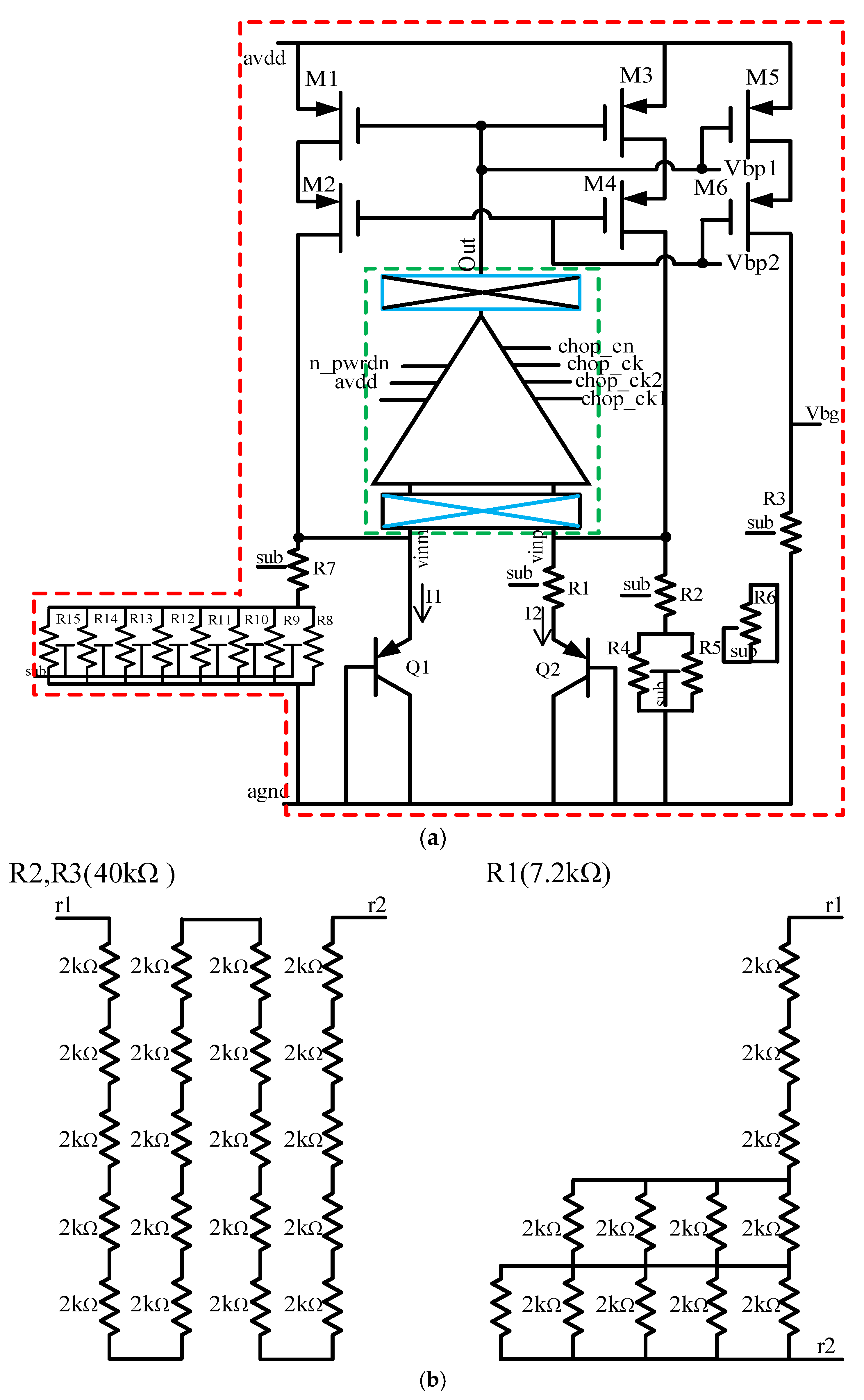

2.2. BGR Operating Principle

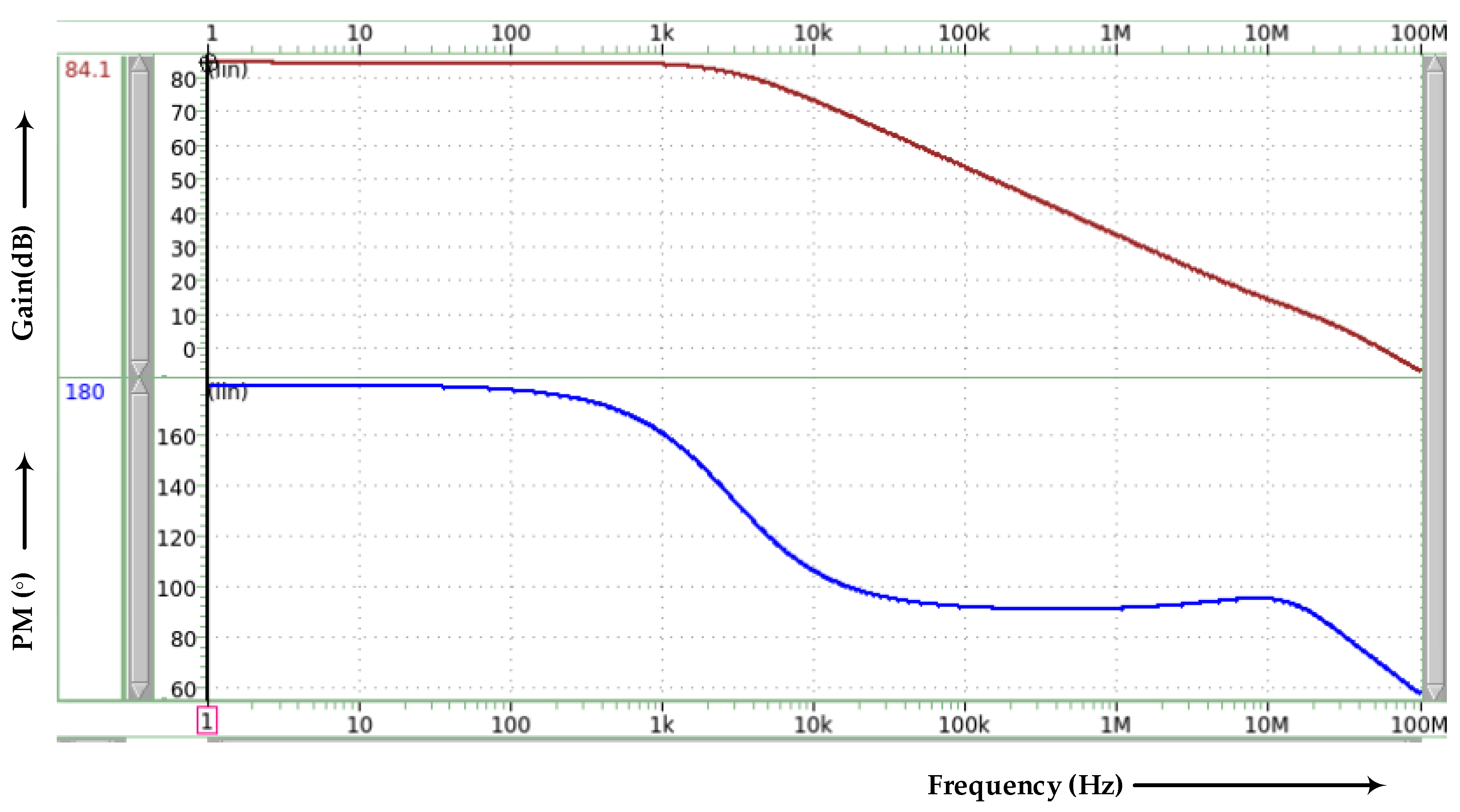

Operational Amplifier Analysis

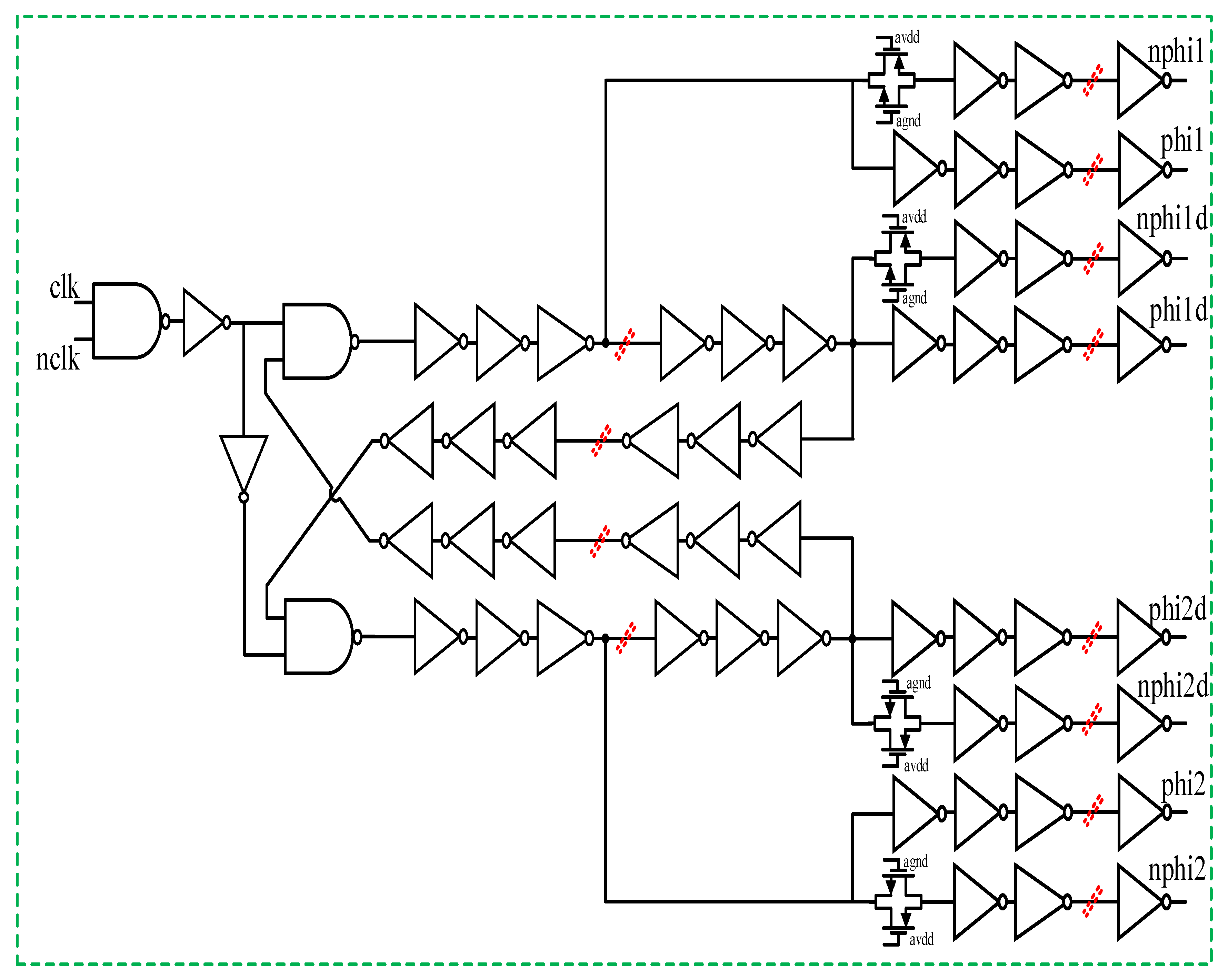

2.3. Non-Overlapping Clock Implementation

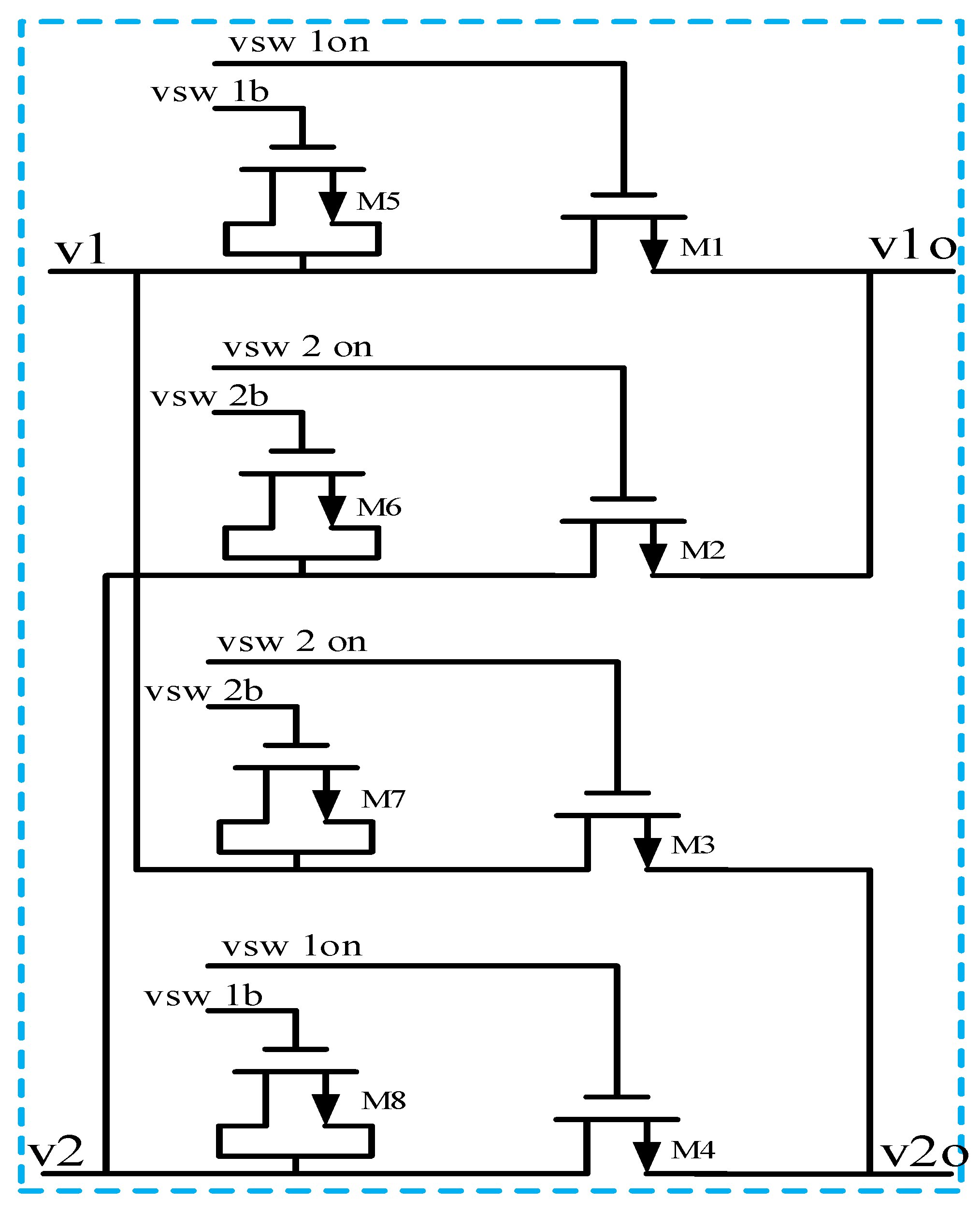

2.4. Chopper Circuit Embedded in the OTA

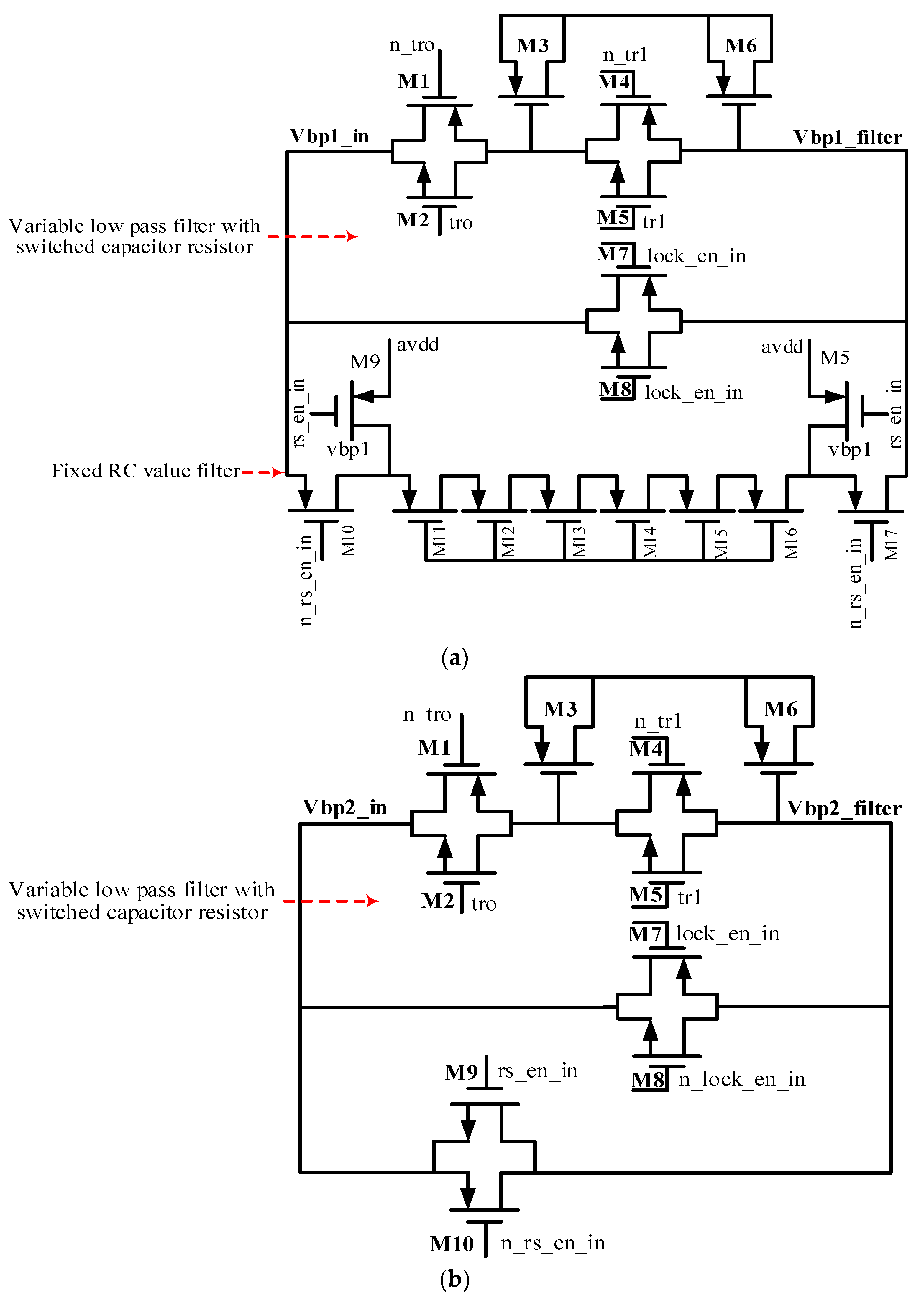

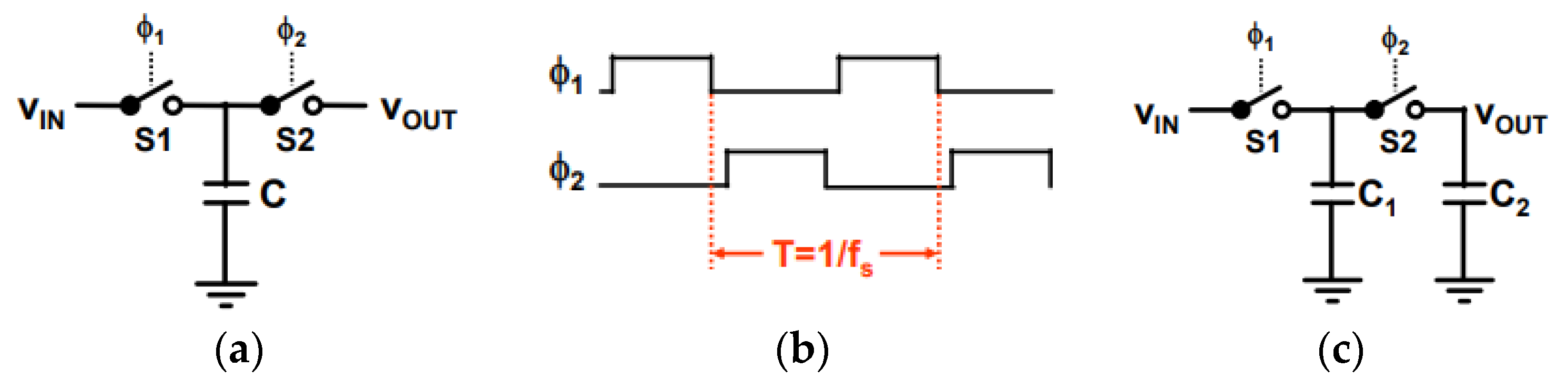

2.5. Switched Capacitor Resistor and Low-Pass Filter

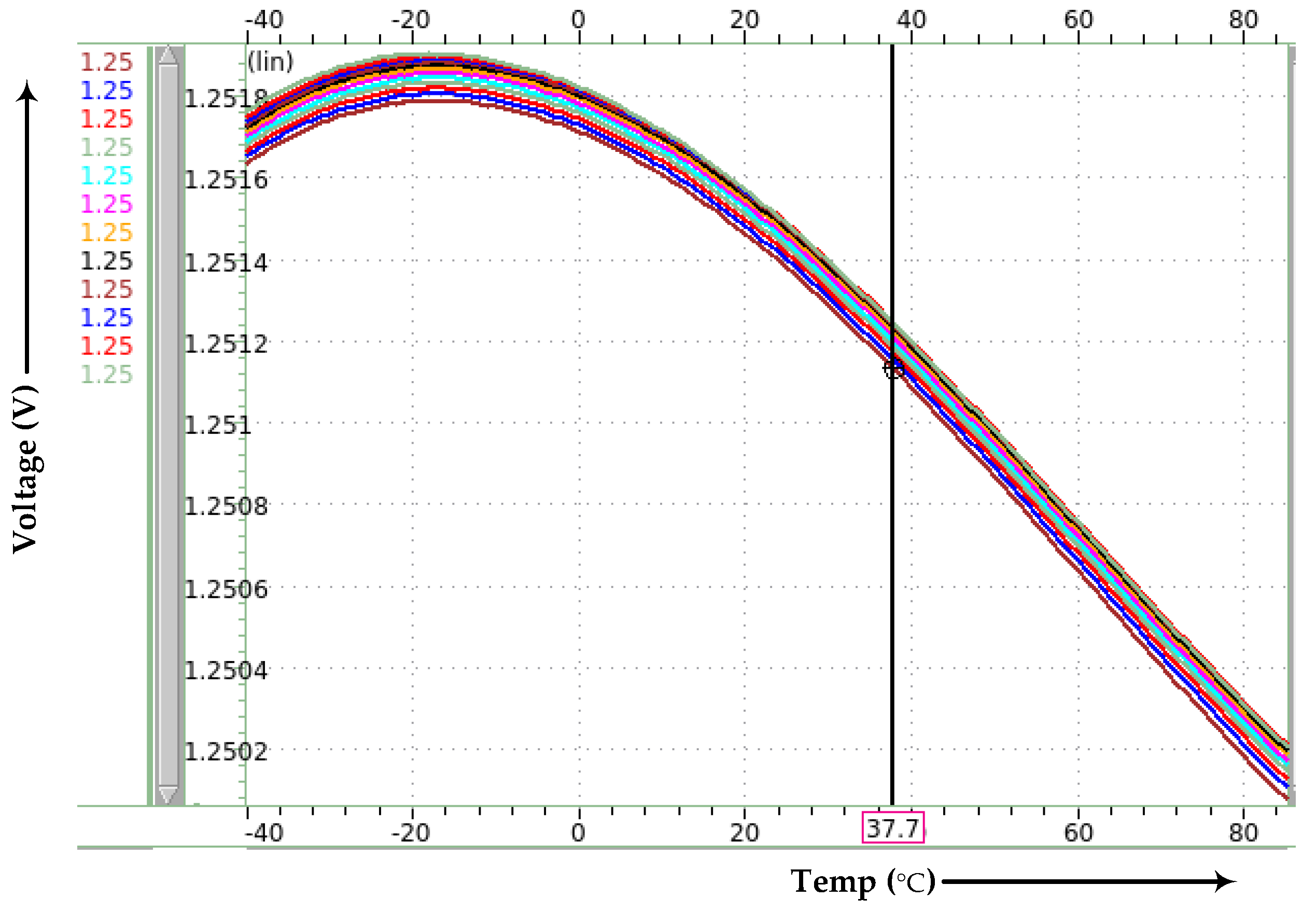

2.6. Chopper-Enabled Bias Pre- and Post-Simulation

3. Chopper-Embedded BGR Layout

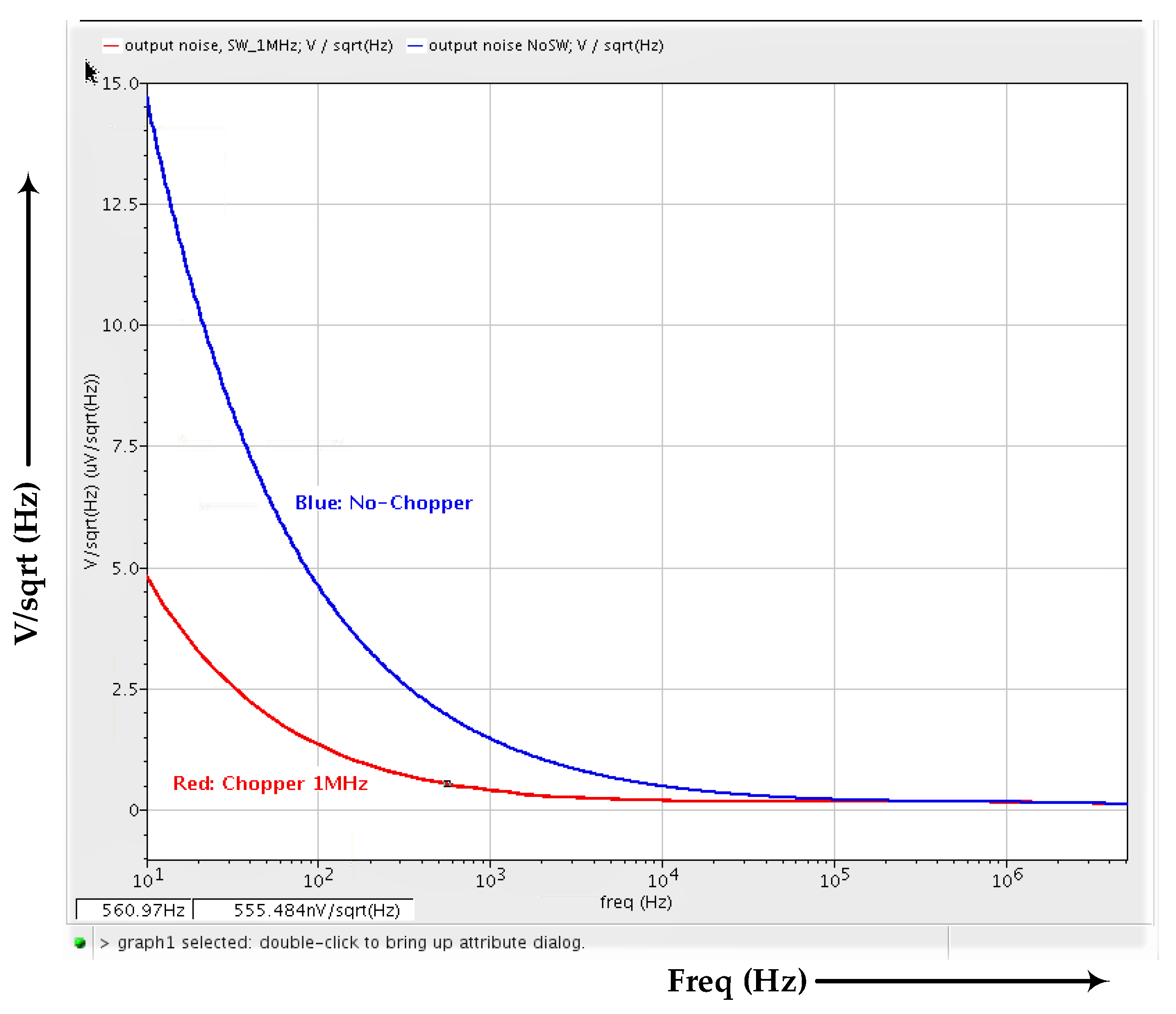

4. Composite BGR Frequency Domain Noise Analysis Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Razavi, B. Design of Analog CMOS Integrated Circuits, 1st ed.; McGraw-Hill: New York, NY, USA, 2002. [Google Scholar]

- Gray, P.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 4th ed.; John Willey & Sons: New York, NY, USA, 2001. [Google Scholar]

- Bakker, A.; Thiele, K.; Huijsing, J.H. A CMOS nested-chooper instrumentation amplifier with 100-nV offset. IEEE J. Solid-State Circuits 2000, 35, 1877–1883. [Google Scholar] [CrossRef]

- Razavi, B. Phase-Locked Loops, Design of Analog CMOS Integrated Circuit, 2nd ed.; McGraw Hill Education Private Limited: New York, NY, USA, 2002; pp. 532–576. [Google Scholar]

- Sanborn, K.; Ma, D.; Ivanov, V. A sub-1-V low-noise bandgap voltage reference. IEEE J. Solid-State Circuits 2007, 42, 2466–2481. [Google Scholar] [CrossRef]

- Um, J.-Y. Calibration of bandgap voltage reference using chopping technique and IIR filter. Electron. Lett. 2016, 52, 1104–1106. [Google Scholar] [CrossRef]

- Yu, C.; Siek, L. An area-efficient current-mode bandgap reference with intrinsic robust start-up behavior. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 937–941. [Google Scholar] [CrossRef]

- Chen, H.M.; Lee, C.C.; Jheng, S.H.; Chen, W.C.; Lee, B.Y. A sub-1 ppm/°C precision bandgap reference with adjusted temperature curvature compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1308–1317. [Google Scholar] [CrossRef]

- Roh, H.D.; Roh, J.; Duanquanzhen, Q.D. All MOS transistors bandgap reference using chopper stabilization technique. In Proceedings of the 2010 International SoC Design Conference, Incheon, Korea, 22–23 November 2010; pp. 353–357. [Google Scholar] [CrossRef]

- Li, C.; Han, B.; Guo, Z.; Wu, L. High-Precision Bandgap Voltage Generation Method with Chopper Stabilization Technique. In Proceedings of the 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 12–14 June 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Hayatleh, K.; Lidgey, F.J.; Parta, S. Degradation mechanisms in operational amplifier precision rectifiers. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1995, 42, 479–485. [Google Scholar] [CrossRef]

- Ming, X.; Ma, Y.-Q.; Zhou, Z.-K.; Zhang, B. A high-precision compensated CMOS bandgap voltage reference without resistors. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 767–771. [Google Scholar] [CrossRef]

- Banba, H.; Shiga, H. A CMOS Bandgap Reference Circuit with Sub I-V operation. IEEE J. Solid-State Circuits 1999, 34, 670–674. [Google Scholar] [CrossRef] [Green Version]

- Hunter, B.L.; Matthews, W.E. A ±3 ppm/°C single-trim switched capacitor bandgap reference for battery monitoring applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 777–786. [Google Scholar] [CrossRef]

- Nagulapalli, R.; Palani, R.K.; Bhagavatula, S. A 24.4 ppm/°C Voltage Mode Bandgap Reference with a 1.05 V Supply. IEEE Trans. Circuits and Syst. II Express Briefs 2021, 68, 1088–1092. [Google Scholar] [CrossRef]

- Agarwal, N.; Agarwal, N.; Lu, C.-W.; Oh-e, M. A 33 MHz Fast-Locking PLL with Programmable VCO and Automatic Band Selection for Clock Generator Application. Electronics 2021, 10, 1743. [Google Scholar] [CrossRef]

- Yang, X.; Chan, C.-H.; Zhu, Y.; Martins, R.P. Calibration-Free Ring-Oscillator PLL with Gain Tracking Achieving 9% Jitter Variation Over PVT. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3753–3763. [Google Scholar] [CrossRef]

- Jang, T.; Jeong, S.; Jeon, D.; Choo, K.D.; Sylvester, D.; Blaauw, D. A noise reconfigurable all-digital phase-locked loop using a switched capacitor-based frequency-locked loop and a noise detector. IEEE J. Solid-State Circuits 2018, 53, 50–65. [Google Scholar] [CrossRef]

- Yu, X.-P.; Fang, Y.; Shi, Z. 2.5 mW 2.73 GHz non-overlapping multiphase clock generator with duty-cycle correction in 0.13 μm CMOS. Electron. Lett. 2016, 52, 1261–1262. [Google Scholar] [CrossRef]

- Zhou, Z.-K.; Shi, Y.; Wang, Y.; Li, N.; Xiao, Z.; Wang, Y.; Liu, X.; Wang, Z.; Zhang, B. A Resistor less High-Precision Compensated CMOS Bandgap Voltage Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 428–437. [Google Scholar] [CrossRef]

- Chi-Wa, U.; Zeng, W.-L.; Law, M.-K.; Lam, C.-S.; Martins, R.P. A 0.5-V Supply, 36 nW Bandgap Reference with 42 ppm/°C Average Temperature Coefficient Within −40 °C to 120 °C. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3656–3669. [Google Scholar]

- Ming, X.; Hu, L.; Xin, Y.-L.; Zhang, X.; Gao, D.; Zhang, B. A High-Precision Resistor-Less CMOS Compensated Bandgap Reference Based on Successive Voltage-Step Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 4086–4096. [Google Scholar] [CrossRef]

- Zhu, G.; Yang, Y.; Zhang, Q. A 4.6-ppm/°C high-order curvature compensated bandgap reference for BMIC. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1492. [Google Scholar] [CrossRef]

- Kamath, U.; Cullen, E.; Yu, T.; Jennings, J.; Wu, S.; Lim, P.; Farley, B.; Staszewski, R.B. A 1-V bandgap reference in 7-nm FinFET with a programmable temperature coefficient and inaccuracy of ±0.2% from −45 °C to 125 °C. IEEE J. Solid-State Circuits 2019, 54, 1830–1840. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit With a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

| Component | Parameter |

|---|---|

| M1 | W = 10 µm, L = 4 µm, m = 8 |

| M2 | W = 10 µm, L = 1 µm, m = 8 |

| M3 | W = 10 µm, L = 1 µm, m = 2 |

| M4 | W = 10 µm, L = 1 µm, m = 2 |

| M5 | W = 10 µm, L = 4 µm, m = 2 |

| M6 | W = 10 µm, L = 1 µm, m = 2 |

| R1 | 7.2 kΩ |

| R2 | 40 kΩ |

| R3 | 40 kΩ |

| R4 | 2 kΩ |

| R5 | 2 kΩ |

| R6 | 2 kΩ |

| R7 | 10 kΩ |

| R8 | 250 Ω |

| S.N. | TT | SS | FF |

|---|---|---|---|

| Vdd (Voltage) | 3.3 V | 2.97 V | 3.63 V |

| Temp (°C) | 50 | 125 | −40 |

| Gain (dB) | 84.1 | 80.06 | 89.12 |

| PM (Degree) | 59.48 | 55.57 | 66.52 |

| S.N. | TT | SS | FF |

|---|---|---|---|

| Vdd (Voltage) | 3.3 V | 2.97 V | 3.63 V |

| Temp (°C) | 50 | 125 | −40 |

| Freq = 1 KHz | 7.89574 μV | 7.131022 μV | 6.676753 μV |

| Freq = 10 KHz | 92.72738 nV | 67.98714 nV | 118.9222 nV |

| Freq = 100 KHz | 143.3527 pV | 95.01332 pV | 195.6376 pV |

| Chopper Enabled | Pre_TT | Post_TT |

|---|---|---|

| Voltage | Pre | Post |

| Vbg | 1.2314 V | 1.2302 V |

| Vbp1 | 1.9474 V | 1.9428 V |

| Vbp2 | 1.1281 V | 1.1232 V |

| Vbp1_filter | 1.9474 V | 1.9428 V |

| Vbp2_filter | 1.1281 V | 1.1232 V |

| Current | TT/3.3 V/50 °C | SS/2.97 V/125 °C | FF/3.63 V/−40 °C |

|---|---|---|---|

| 3.75 μA | 3.7872 μA | 3.4434 μA | 4.1977 μA |

| 7.5 μA | 7.6112 μA | 6.9713 μA | 8.3593 μA |

| 15 μA | 15.253 μA | 14.021 μA | 16.675 μA |

| 30 μA | 30.505 μA | 28.0424 μA | 33.348 μA |

| 60 μA | 61.009 μA | 56.083 μA | 66.692 μA |

| Current | TT/3.3 V/50 °C | SS/2.97 V/125 °C | FF/3.63 V/−40 °C |

|---|---|---|---|

| 3.75 μA | 3.8868 μA | 3.52155 μA | 4.3288 μA |

| 7.5 μA | 7.8594 μA | 7.16935 μA | 8.682 μA |

| 15 μA | 15.1114 μA | 13.9025 μA | 16.497 μA |

| 30 μA | 30.4494 μA | 27.9886 μA | 33.284 μA |

| 60 μA | 60.4294 μA | 55.5984 μA | 65.962 μA |

| Type | Proposed | [12] | [14] | [20] | [22] | [23] |

|---|---|---|---|---|---|---|

| Supply voltage (V) | 2.8 | 3.6 | 5.2 | 26~5 | 2.5~5 | 3.5–5 |

| Vbg (V) | 1.25 | 1.23 | 3.65 | 1.14 | 1.196 | 3.11 |

| Temp range (°C) | −40~125 | −40~120 | −40~100 | −40~125 | −10~130 | −40~130 |

| Trimming method | No-trim | Yes | Single-trim | Multi-trim | Multi-trim | Yes |

| Current consumption (μA) | 30 | 180 | 750 | 33 | 38 | 108 |

| Min TC (ppm/°C) | 4.36 | 11.8 | 3 | 1.01 | 3.98 | 4.6 |

| Line regulation(mV/V) | N.A. | N.A. | N.A. | 2 | 0.19 | 0.31 |

| PSRR (dB) | −68.8 | −31.8 | −127 | −61 | −84 | −74 |

| Chip area (mm2) Technology | 0.03 0.18 μm CMOS | 0.1 0.13 μm CMOS | 0.28 0.18 μm Bi CMOS | 0.04 0.35 μm CMOS | 0.053 0.5 μm CMOS | 0.223 0.18 μm CMOS |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Agarwal, N.; Agarwal, N.; Lu, C.-W.; Oh-e, M. A Chopper-Embedded BGR Composite Noise Reduction Circuit for Clock Generator. Electronics 2021, 10, 2257. https://doi.org/10.3390/electronics10182257

Agarwal N, Agarwal N, Lu C-W, Oh-e M. A Chopper-Embedded BGR Composite Noise Reduction Circuit for Clock Generator. Electronics. 2021; 10(18):2257. https://doi.org/10.3390/electronics10182257

Chicago/Turabian StyleAgarwal, Neeru, Neeraj Agarwal, Chih-Wen Lu, and Masahito Oh-e. 2021. "A Chopper-Embedded BGR Composite Noise Reduction Circuit for Clock Generator" Electronics 10, no. 18: 2257. https://doi.org/10.3390/electronics10182257

APA StyleAgarwal, N., Agarwal, N., Lu, C.-W., & Oh-e, M. (2021). A Chopper-Embedded BGR Composite Noise Reduction Circuit for Clock Generator. Electronics, 10(18), 2257. https://doi.org/10.3390/electronics10182257