Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies

Abstract

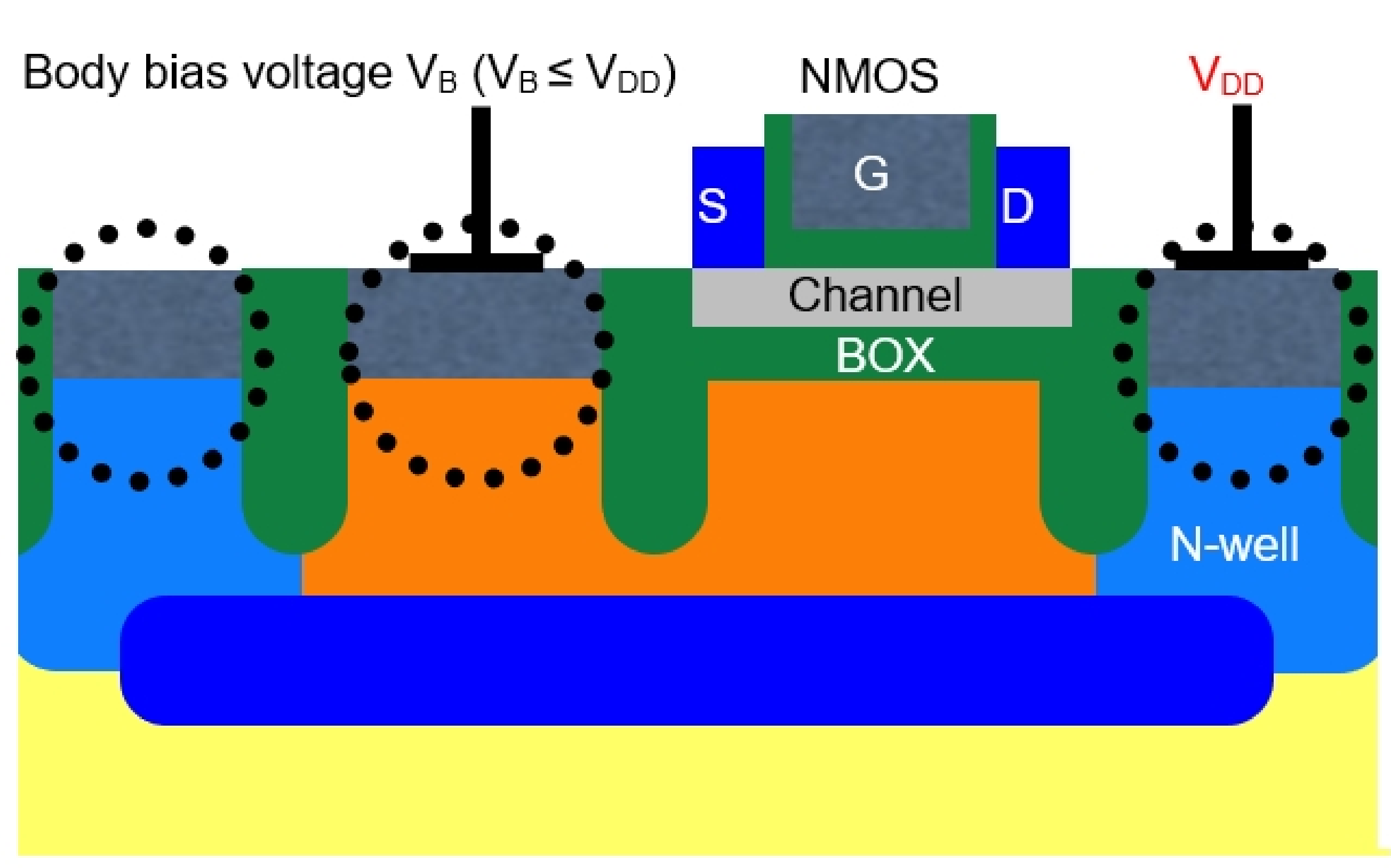

:1. Introduction

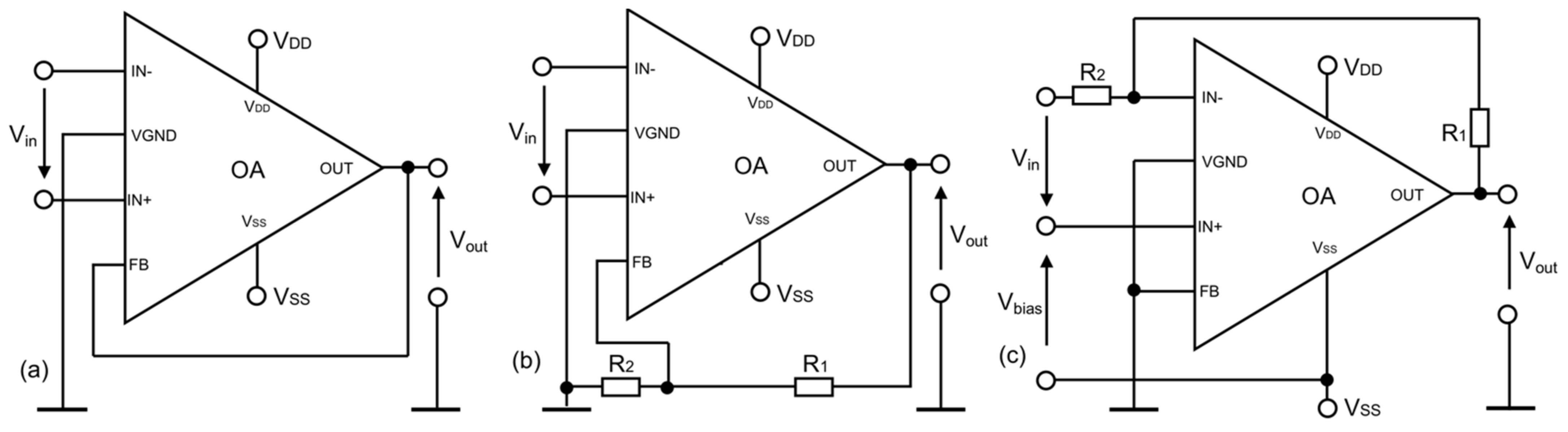

2. Opamp Linearization Technique: The Concept and Theory

3. Experimental Results

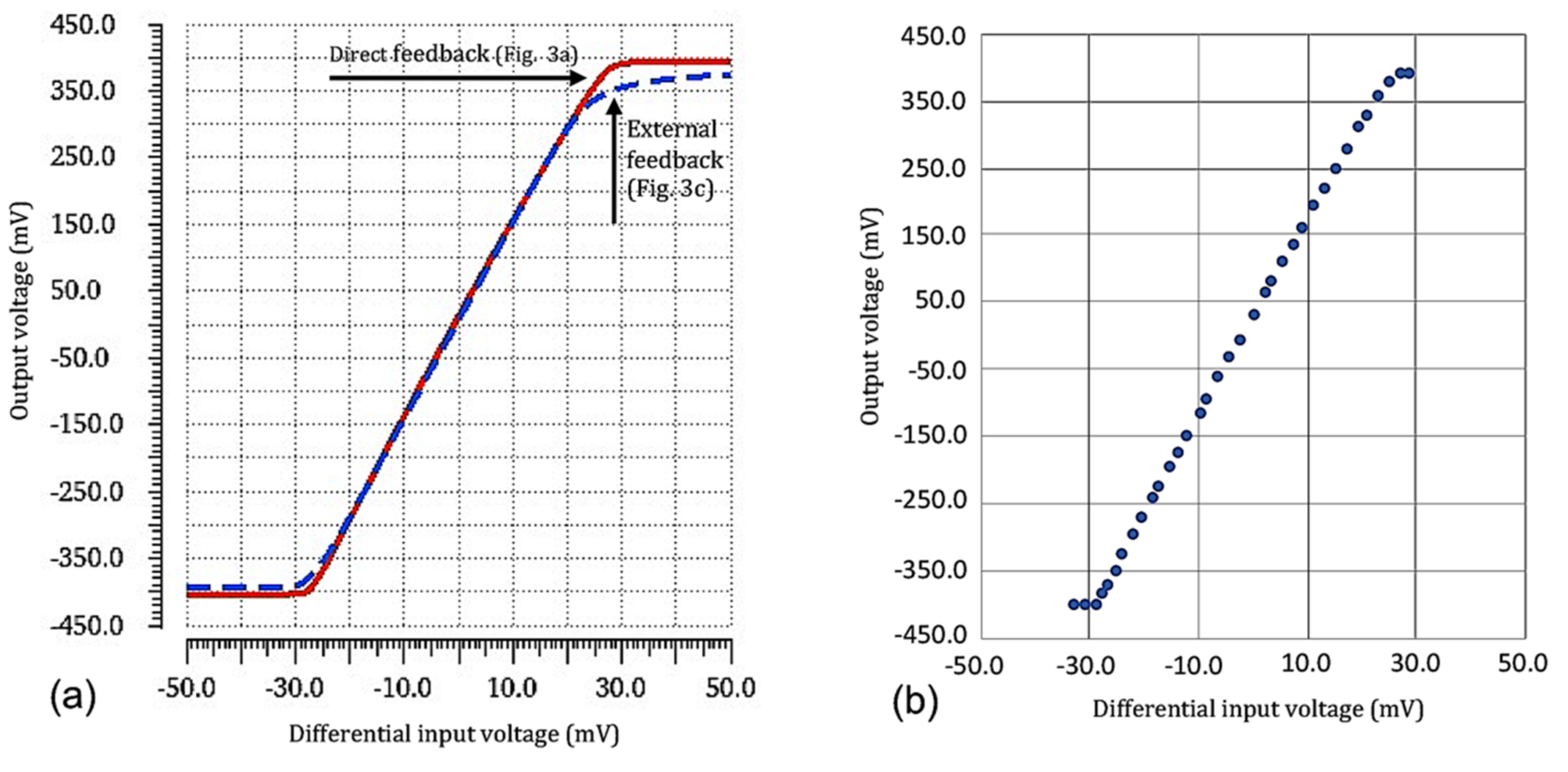

3.1. The First Amplifier

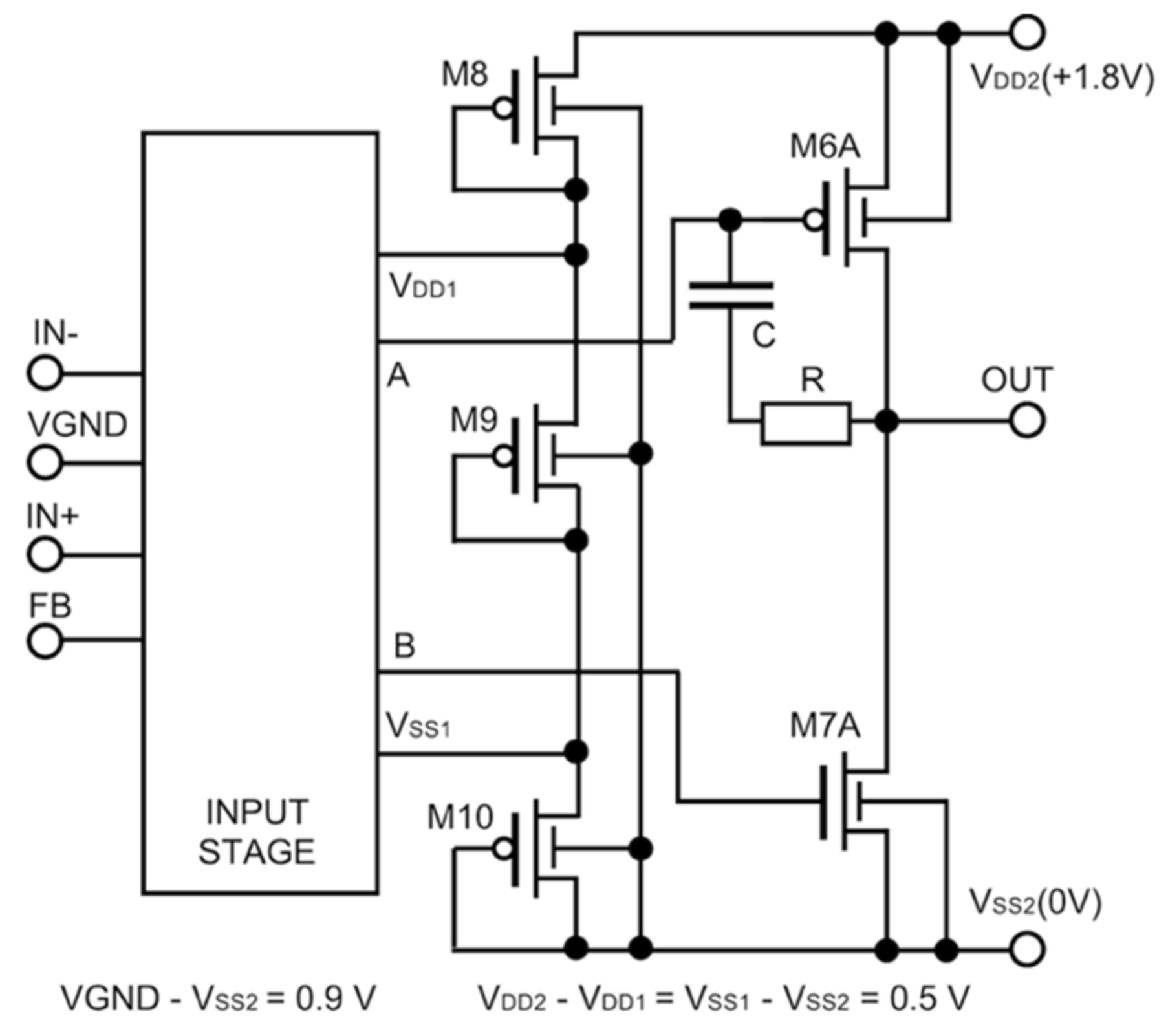

3.2. The Second Amplifier

3.3. Frequency Response

3.4. Variability

4. Discussion and Conclusions

Funding

Conflicts of Interest

Appendix A

References

- Cathelin, A. Fully Depleted Silicon on Insulator Devices CMOS: The 28-nm Node Is the Perfect Technology for Analog, RF, mmW, and Mixed-Signal System-on-Chip Integration. IEEE Solid State Circuits Mag. 2017, 9, 18–26. [Google Scholar] [CrossRef]

- Planes, N.; Weber, O.; Barral, V.; Haendler, S.; Noblet, D.; Croain, D.; Bocat, M.; Sassoulas, P.-O.; Federspiel, X.; Cros, A.; et al. 28nm FDSOI Technology Platform for High-Speed Low-Voltage Digital Applications. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 133–134. [Google Scholar]

- Nagata, H.; Wada, T.; Ikeda, H.; Arai, Y.; Ohno, M.; Nagase, K. Development of Cryogenic Readout Electronics for Far-Infrared Astronomical Focal Plane Array. IEICE Trans. Commun. 2011, 11, 2952–2960. [Google Scholar] [CrossRef] [Green Version]

- Wada, T.; Nagata, H.; Ikeda, H.; Arai, Y.; Ohno, M.; Nagase, K. Development of Low Power Cryogenic Readout Integrated Circuits Using Fully-Depleted-Silicon-on-Insulator CMOS Technology for Far-Infrared Image Sensors. J. Low Temp. Phys. 2012, 167, 602–608. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Pennisi, S.; Venezia, C. High-Frequency Low-Current Second-Order Bandpass Active Filter Topology and Its Design in 28-nm FD-SOI CMOS. J. Low Power Electron. Appl. 2020, 10, 27. [Google Scholar] [CrossRef]

- Wołodźko, M.; Kuźmicz, W. A Low Power Input Amplifier for Bio-Signal Acquisition in 28 nm FDSOI Technology. In Proceedings of the 20th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Dresden, Germany, 19–21 April 2017; pp. 79–82. [Google Scholar] [CrossRef]

- Kuzmicz, W. A Simple Ultra-Low Power Opamp in 22 nm FDSOI. In Proceedings of the 26th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Rzeszów, Poland, 27–29 June 2019; pp. 167–170. [Google Scholar] [CrossRef]

- Yang, E.; Lehmann, T. High Gain Operational Amplifiers in 22 nm CMOS. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019. [Google Scholar] [CrossRef]

- Harikumar, P.; Wikner, J.J.; Alvandpour, A. An Ultra-Low-Voltage OTA in 28 nm UTBB FDSOI CMOS Using Forward Body Bias. In Proceedings of the 2015 Nordic Circuits and Systems Conference (NORCAS), Oslo, Norway, 26–28 October 2015. [Google Scholar] [CrossRef]

- Harikumar, P.; Wikner, J.J.; Alvandpour, A. A Fully-Differential OTA in 28 nm UTBB FDSOI CMOS for PGA Applications. In Proceedings of the 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, Norway, 24–26 August 2015. [Google Scholar] [CrossRef]

- Jaworski, Z. A fully differential OTA with dynamic offset cancellation in 28 nm FD-SOI process. Proc. SPIE 2016, 10175, 1017509. [Google Scholar] [CrossRef]

- Sansen, W. Distortion in elementary transistor circuits. IEEE Trans. Circuits Syst. II Anal. Dig. Signal Proc. 1999, 46, 315–325. [Google Scholar] [CrossRef]

- Zhang, H.; Sánchez-Sinencio, E. Linearization Techniques for CMOS Low Noise Amplifiers: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 22–36. [Google Scholar] [CrossRef]

- Coppejans, P.; Steyaert, M. Dynamic Biasing: A Low Power Linearisation Technique. In Proceedings of the 29th European Solid-State Circuits Conference (ESSCIRC 2004), Estoril, Portugal, 16–18 September 2003; pp. 369–372. [Google Scholar] [CrossRef]

- Hernes, B.; Moldsvor, Ø.; Sœther, T. A 80dB HD3 Opamp in 3.3V CMOS Technology using Tail Current Compensation. In Proceedings of the 2001 IEEE International Symposium on Circuits and Systems (ISCAS 2001), Sydney, Australia, 6–9 May 2001; pp. 216–219. [Google Scholar] [CrossRef]

- Barbieri, A.; Pernici, S. A Differential Difference Amplifier with Dynamic Resistive Degeneration for MEMS Microphones. In Proceedings of the 42nd European Solid-State Circuits Conference (ESSCIRC 2016), Lausanne, Switzerland, 12–15 September 2016; pp. 285–288. [Google Scholar] [CrossRef]

- Popa, C.; Coada, D. A New Linearization Technique for a CMOS Differential Amplifier Using Bulk-Driven Weak Inversion MOS Transistors. In Proceedings of the International Symposium on Signals, Circuits and Systems (SCS 2003), Iasi, Romania, 10–11 July 2003; pp. 589–592. [Google Scholar] [CrossRef]

- Yodtean, A.; Isarasena, P.; Thanachayanont, A. 0.8-µW CMOS Bulk-Driven Linear Operational Transconductance Amplifier in 0.35-µm Technology. In Proceedings of the 2010 IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur, Malaysia, 6–9 December 2010; pp. 784–787. [Google Scholar] [CrossRef]

- Zhang, L.; Zhang, X.; El-Masry, E.; Zhang, Y. A Low-Voltage High Linear Body-Driven Operational Transconductance Amplifier and Its Applications. In Proceedings of the 2007 Canadian Conference on Electrical and Computer Engineering, Vancouver, BC, Canada, 22–26 April 2007; pp. 534–537. [Google Scholar] [CrossRef]

- El Ghouli, S.; Rideau, D.; Monsieur, F.; Scheer, P.; Gouget, G.; Juge, A.; Poiroux, T.; Sallese, J.-M.; Lallement, C. Experimental gm/ID Invariance Assessment for Asymmetric Double-Gate FDSOI MOSFET. IEEE Trans. Electron. Devices 2018, 65, 11–18. [Google Scholar] [CrossRef]

- Khateb, F.; Biolek, D.; Khatib, N.; Vávra, J. Utilizing the Bulk-driven Technique in Analog Circuit Design. In Proceedings of the 13th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Vienna, Austria, 14–16 April 2010; pp. 16–19. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Duque-Carrillo, J.F.; Torelli, G. Design Considerations on CMOS Bulk-Driven Differential Input Stages. In Proceedings of the 2012 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Seville, Spain, 19–21 September 2012; pp. 85–88. [Google Scholar] [CrossRef]

- Grech, I.; Micallef, I.; Azzopardi, G.; Debono, C.J. A low-voltage wide-input-range bulk-input CMOS OTA. Analog Integr. Circ. Signal Process. 2005, 43, 127–136. [Google Scholar] [CrossRef]

- Raikos, G.; Vlassis, S. 0.8 V Bulk-Driven Variable Gain Amplifier. In Proceedings of the 17th IEEE International Conference on Electronics, Circuits and Systems, Athens, Greece, 12–15 December 2010; pp. 343–346. [Google Scholar] [CrossRef]

- Tai, C.-F.; Lai, J.-L.; Chen, R.-J. Using Bulk-driven Technology Operate in Subthreshold Region to Design a Low Voltage and Low Current Operational Amplifier. In Proceedings of the 2006 IEEE International Symposium on Consumer Electronics, Saint Petersburg, Russia, 28 June–1 July 2006; pp. 562–566. [Google Scholar] [CrossRef]

- Rakús, M.; Stopjaková, V.; Daniel, A. Analysis of Bulk-Driven Technique for Low-Voltage IC Design in 130 nm CMOS Technology. In Proceedings of the 15th International Conference on Emerging eLearning Technologies and Applications (ICETA), Starý Smokovec, Slovakia, 26–27 October 2017; pp. 385–390. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kuzmicz, W. Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies. Electronics 2021, 10, 1800. https://doi.org/10.3390/electronics10151800

Kuzmicz W. Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies. Electronics. 2021; 10(15):1800. https://doi.org/10.3390/electronics10151800

Chicago/Turabian StyleKuzmicz, Wieslaw. 2021. "Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies" Electronics 10, no. 15: 1800. https://doi.org/10.3390/electronics10151800

APA StyleKuzmicz, W. (2021). Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies. Electronics, 10(15), 1800. https://doi.org/10.3390/electronics10151800