Implementing Adaptive Voltage Over-Scaling: Algorithmic Noise Tolerance vs. Approximate Error Detection

Abstract

:1. Introduction

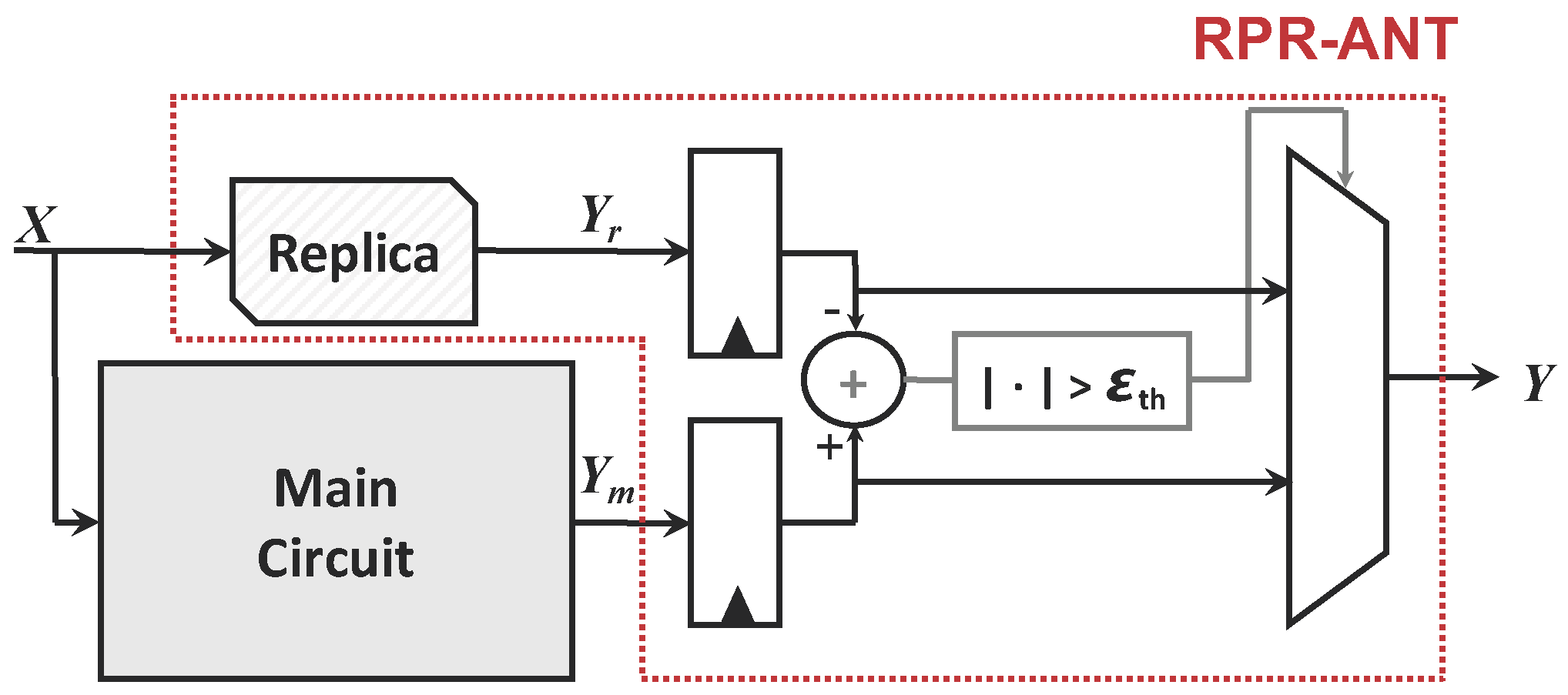

2. Algorithmic Noise Tolerance (ANT) via Reduced Precision Redundancy (RPR)

2.1. Implementation

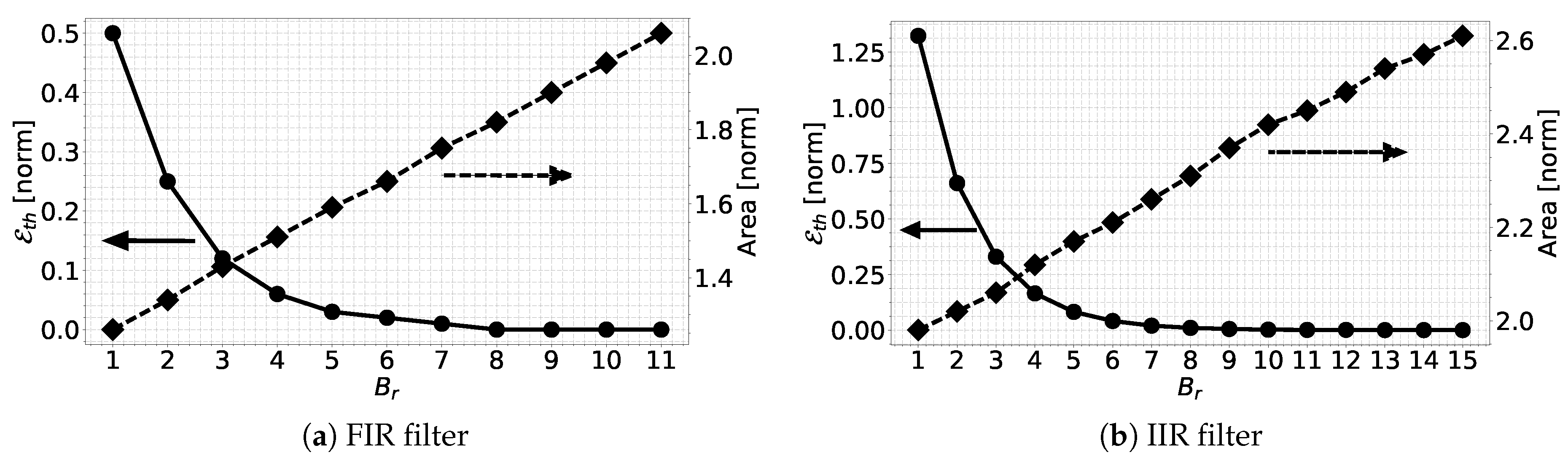

2.2. Design and Area Overhead

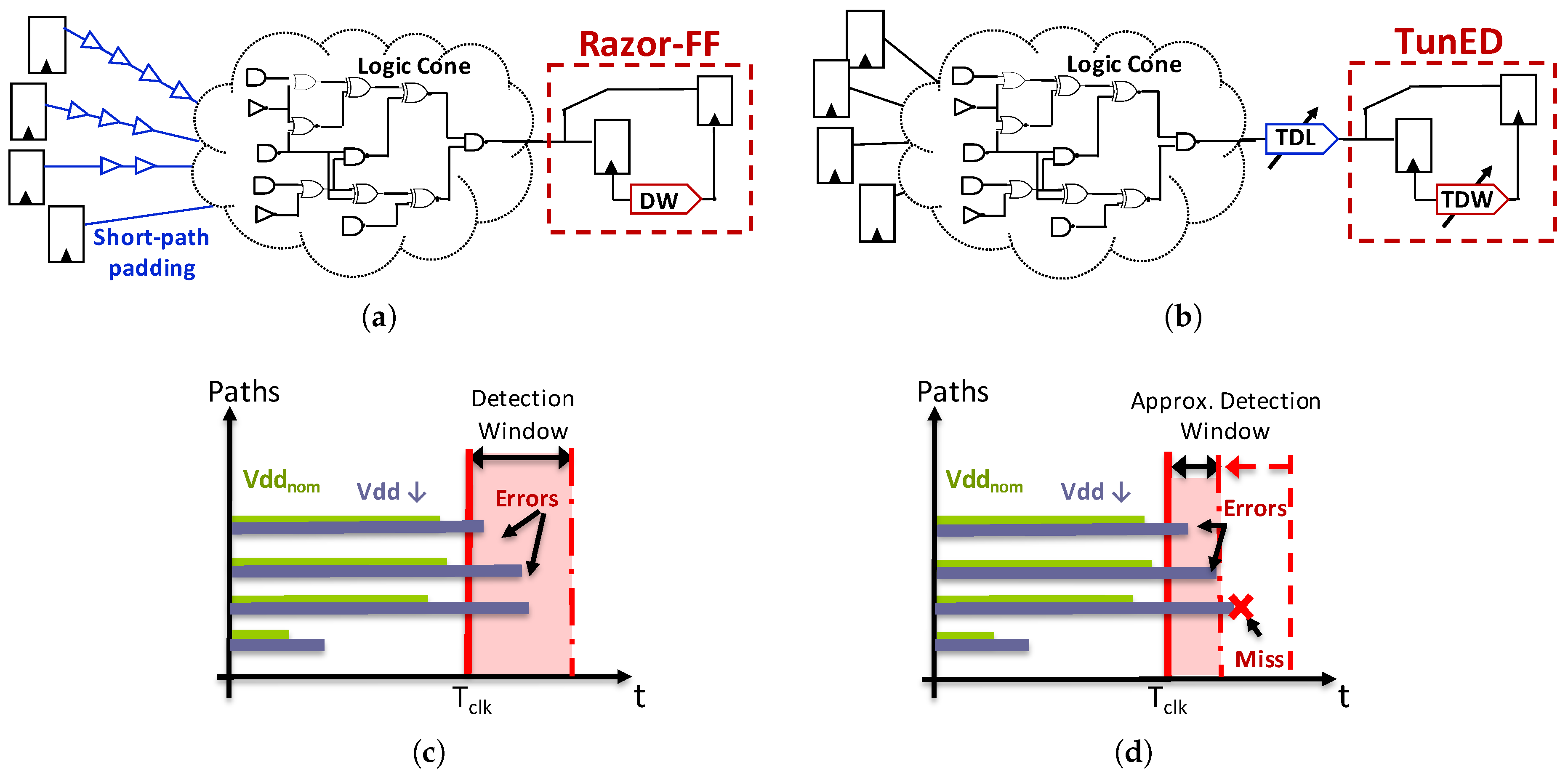

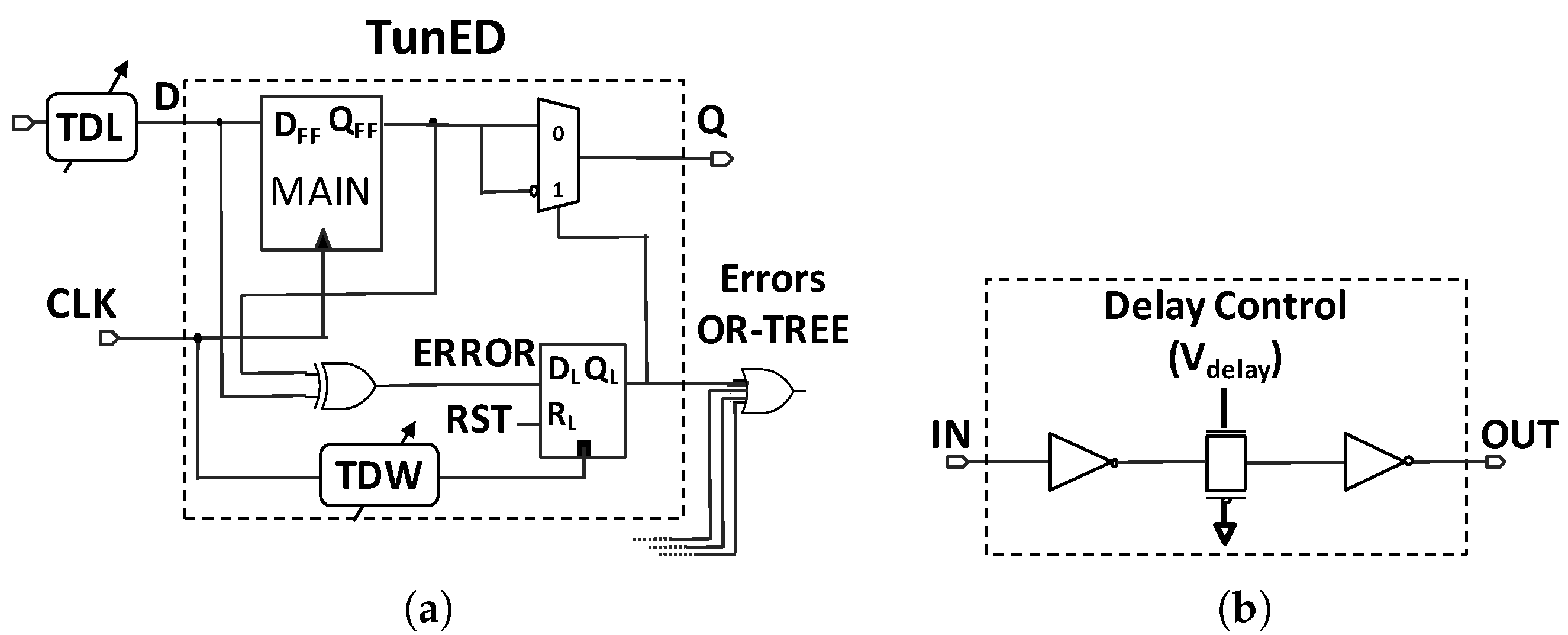

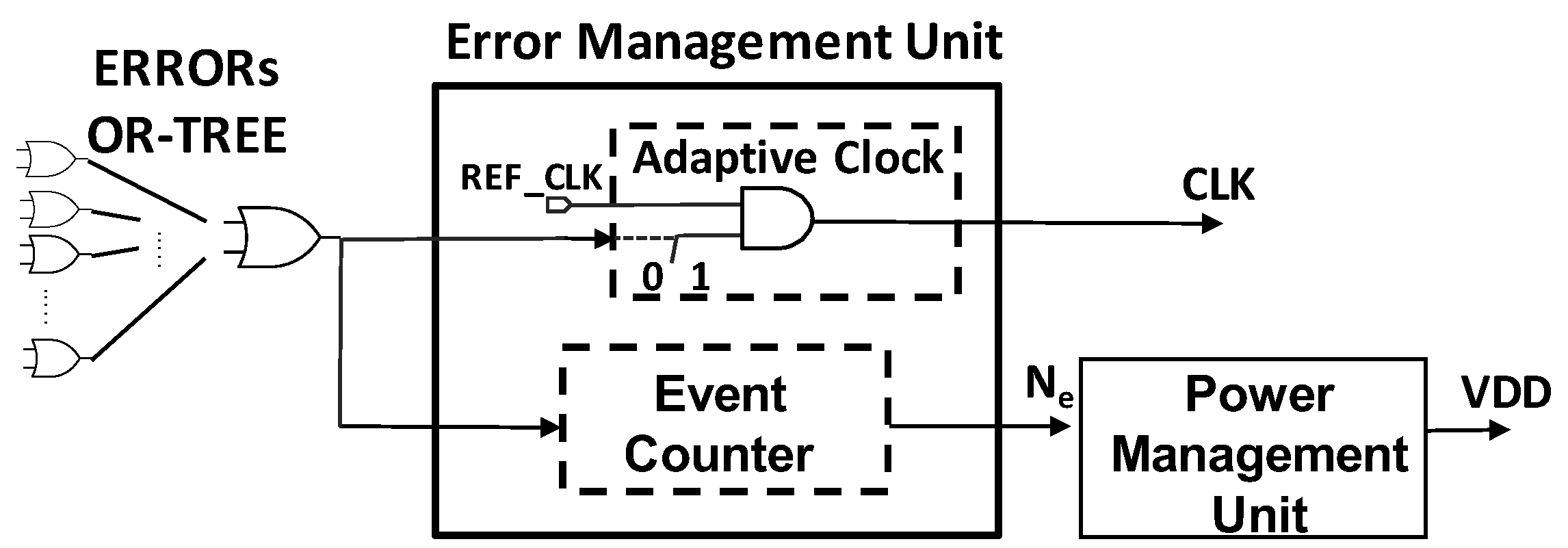

3. Approximate Error Detection-Correction (AED-C) via Tunable Error-Detection (TunED)

3.1. Implementation

3.1.1. From Razor to AED-C

3.1.2. Understanding the Short-Path Race and the Dynamic Short-Path Padding

3.1.3. Circuit-Level Details

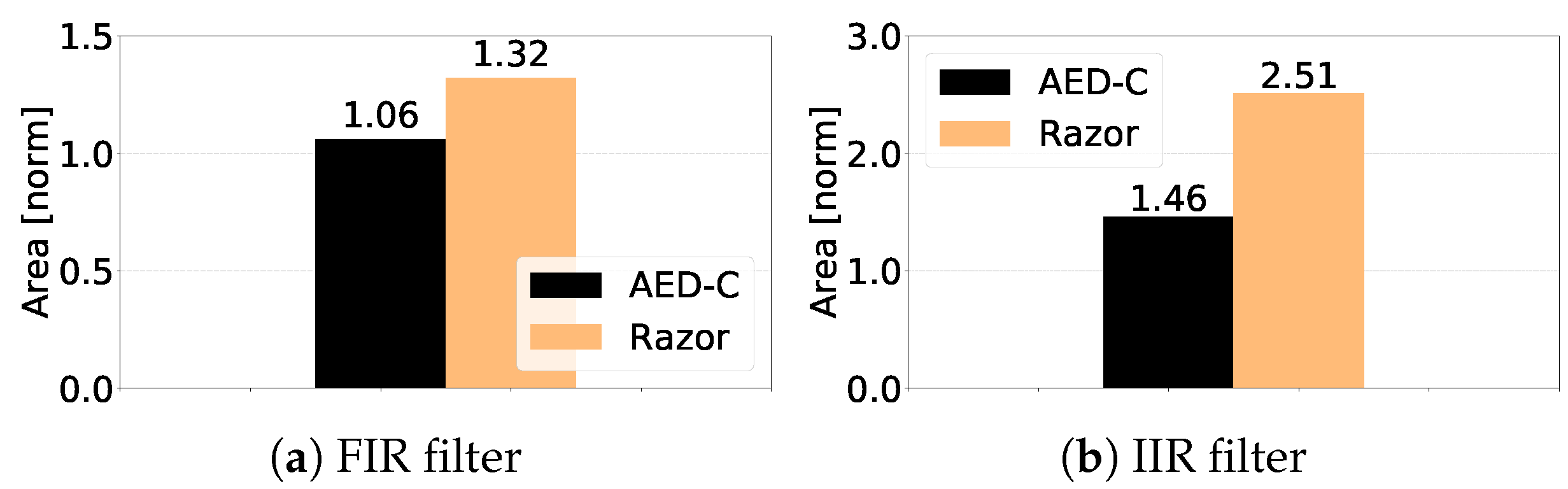

3.2. Area Overhead Characterization

4. Experimental Setup

4.1. Benchmarking

- -1: Noiseless voice recording; the switching activity of the LSBs is very low for a long portion of the stream.

- -2: Taken from an office conversation recording; samples present low noise and inputs have homogeneous switching activity.

- -3: Outdoor conversation; the recording is noisy and the switching activity of the inputs quite irregular, due to abrupt changes of input workload.

4.2. Voltage Over-Scaling Simulation Framework

4.3. Figures of Merit

- : The average obtained during test bench voltage over-scaling simulation for AED-C based timing speculation. For RPR-ANT, the average voltage corresponded to the employed during the test bench simulation.

- Energy per Operation (EPO): The ratio of energy consumed to the number of operations completed.

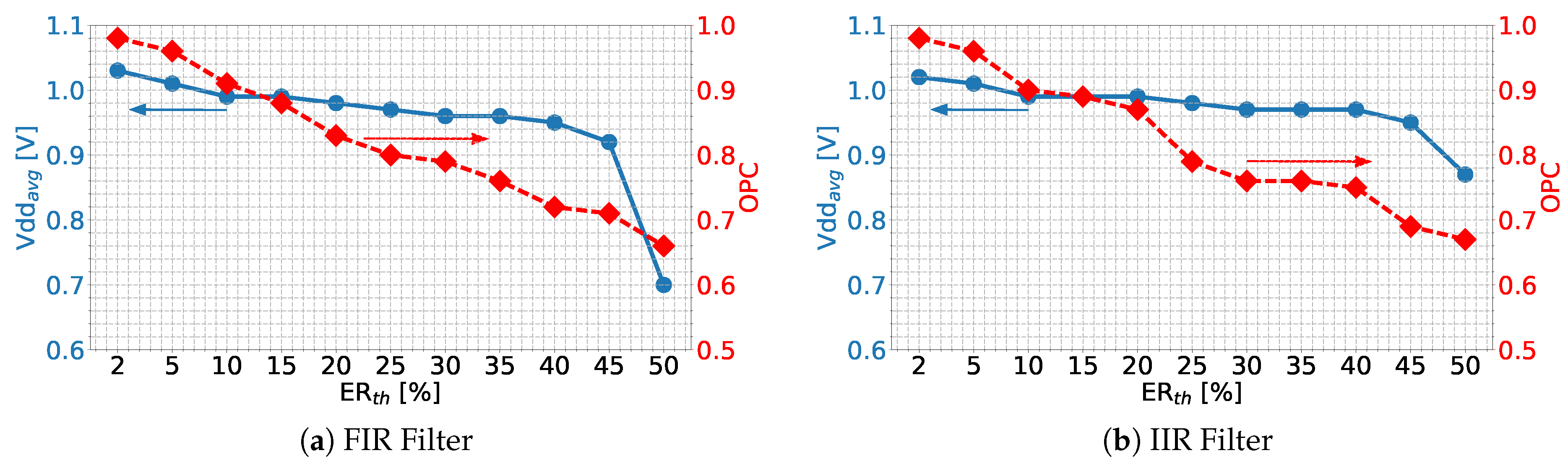

- Operation per Clock Cycle (OPC): The ratio of the number of executed operations to the total number of clock cycles, considering that in AED-C techniques error corrections through logic masking need a cycle of clock gating. For RPR-ANT, the OPC was always 1, since no performance loss was conceived.

- Normalized Root Mean Squared Error (NRMSE):with y the value sampled at the output of the circuit, the right output value, and n the total number of operations. The absolute values of the the maximum and minimum of difference defined the output dynamic range. quantified the quality of results.

- Maximum Absolute Error (MAE): expressed in form,with y the value sampled at the output of the circuit and the right output value. This metric representation collapses the maximum error on a single bit of the output.

5. Experimental Results

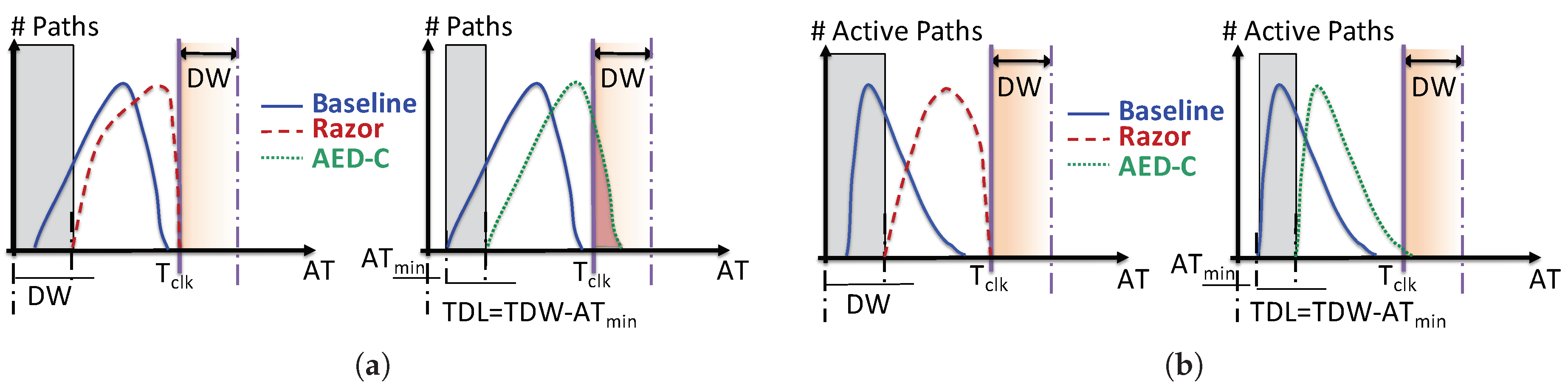

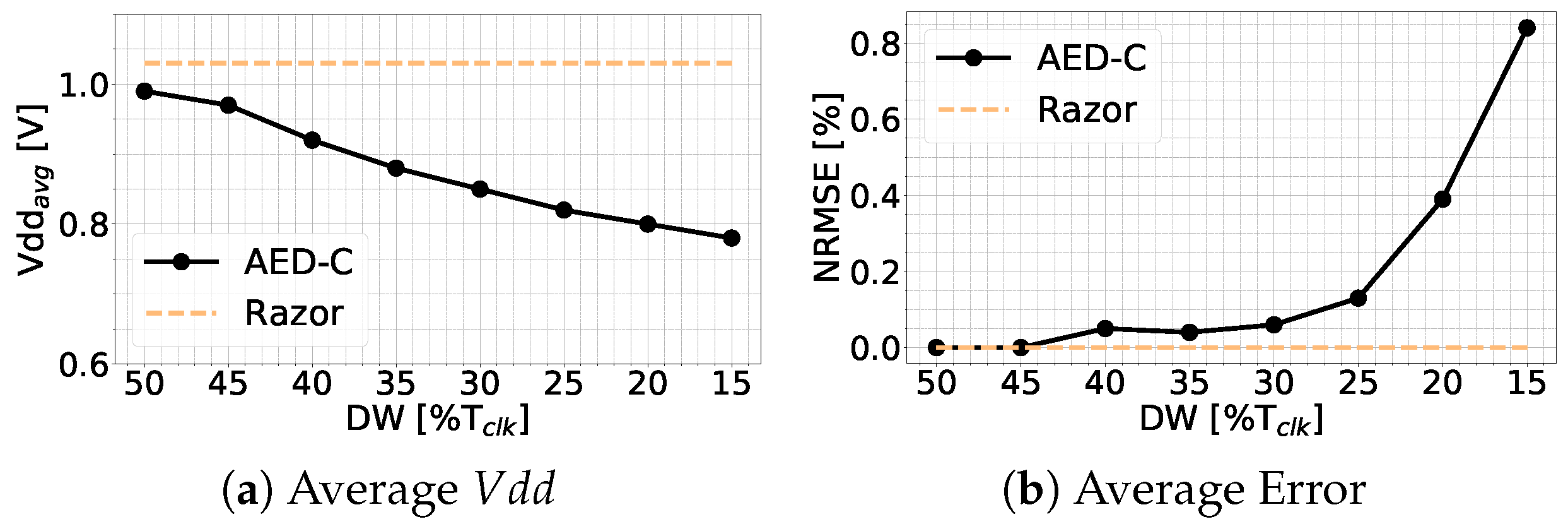

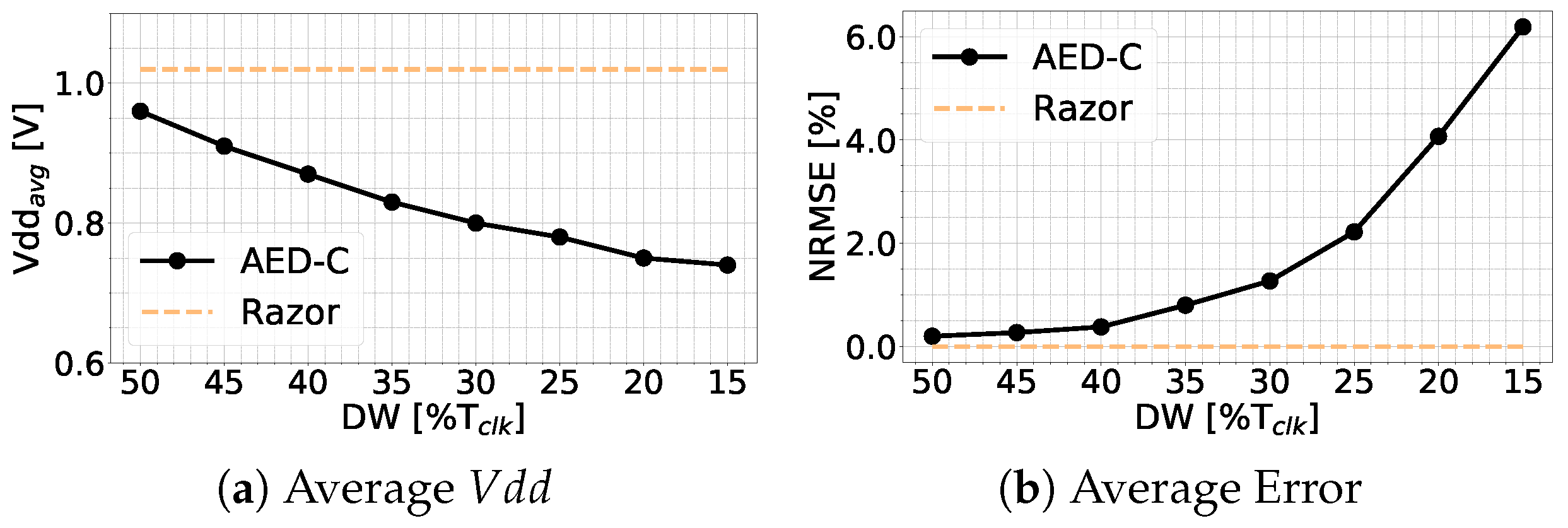

5.1. Razor vs. AED-C

- Detection Window:;

- Monitoring period:N = 10 clock cycles; and

- Error Rate Threshold: = 2%.

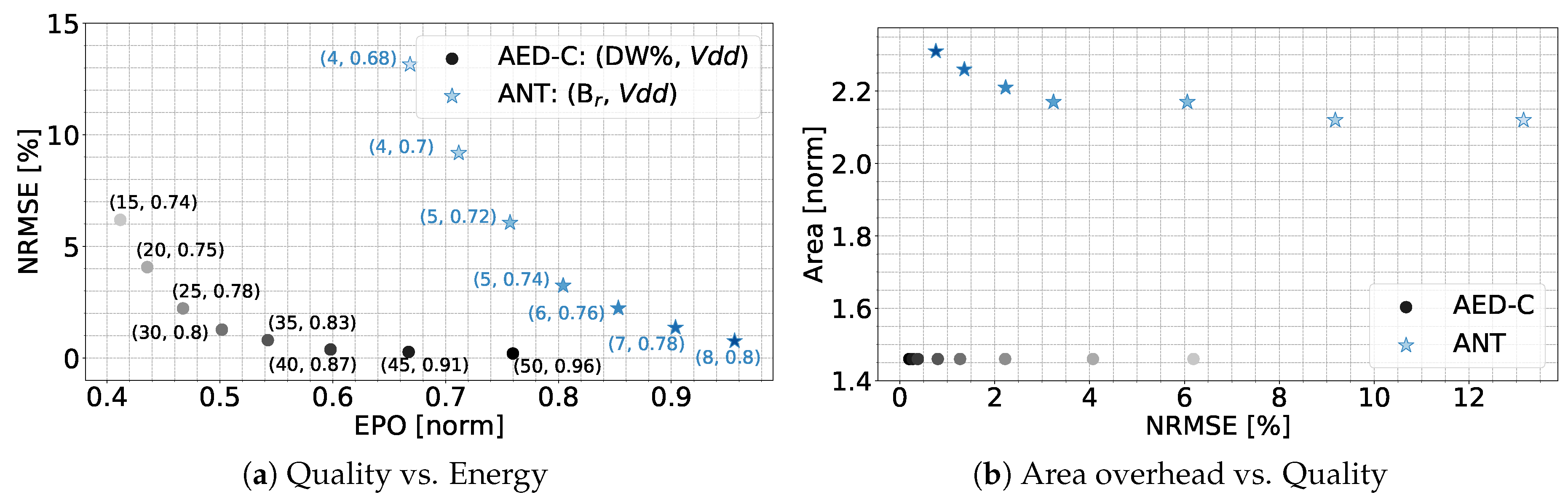

5.2. ANT Vs. AED-C

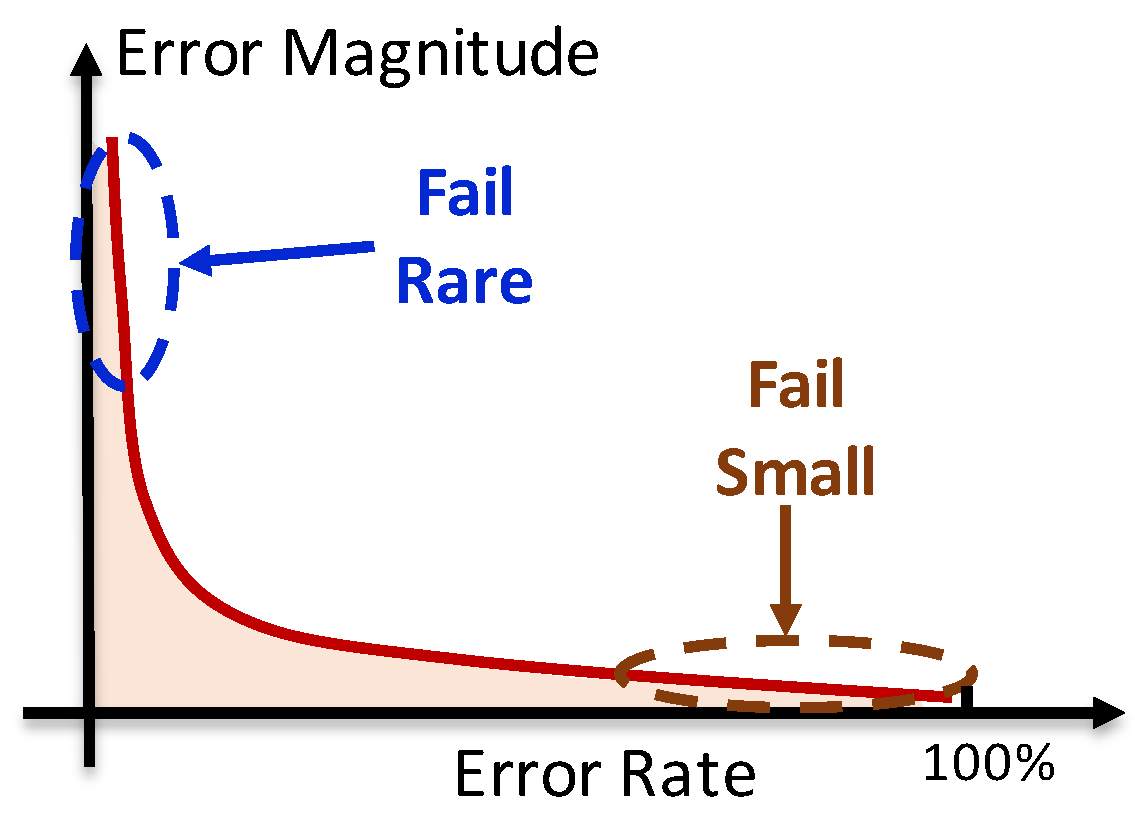

5.2.1. Qualitative Analysis

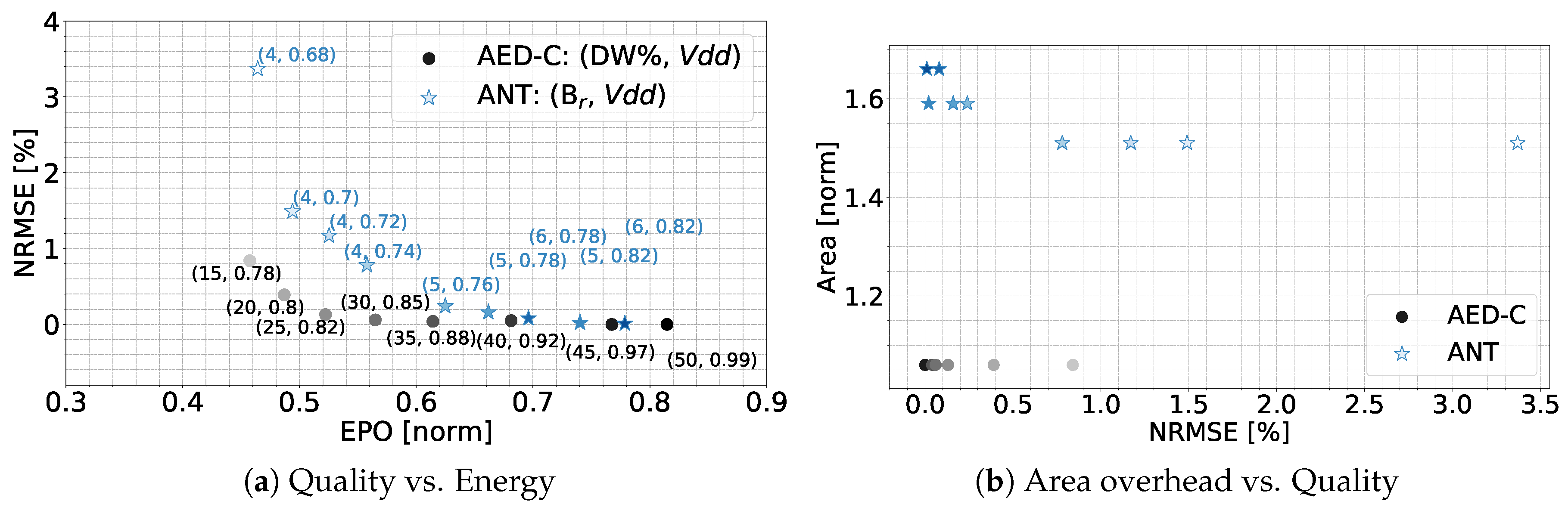

5.2.2. Quantitative Analysis

5.2.3. On the AED-C Expendability

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Benini, L.; Castelli, G.; Macii, A.; Macii, B.; Scarai, R. Battery-driven dynamic power management of portable systems. In Proceedings of the 13th International Symposium on System Synthesis, Madrid, Spain, 20–22 September 2000; pp. 25–30. [Google Scholar]

- Alioto, M. Ultra Low Power Design approaches for IoT. In Proceedings of the 2014 IEEE Hot Chips 26 Symposium (HCS), Cupertino, CA, USA, 10–12 August 2014; pp. 1–57. [Google Scholar]

- Hameed, A.; Khoshkbarforoushha, A.; Ranjan, R.; Jayaraman, P.P.; Kolodziej, J.; Balaji, P.; Zeadally, S.; Malluhi, Q.M.; Tziritas, N.; Vishnu, A.; et al. A survey and taxonomy on energy efficient resource allocation techniques for cloud computing systems. Computing 2016, 98, 751–774. [Google Scholar] [CrossRef]

- Zakarya, M.; Gillam, L. Energy efficient computing, clusters, grids and clouds: A taxonomy and survey. Sustain. Comput. Inform. Syst. 2017, 14, 13–33. [Google Scholar] [CrossRef]

- Herbert, S.; Marculescu, D. Analysis of dynamic voltage/frequency scaling in chip-multiprocessors. In Proceedings of the 2007 IEEE International Symposium on Low Power Electronics and Design (ISLPED’07), Portland, OR, USA, 27–29 August 2007; pp. 38–43. [Google Scholar]

- Choi, K.; Soma, R.; Pedram, M.; Pedram, M.; Pedram, M.; Pedram, M. Dynamic Voltage and Frequency Scaling Based on Workload Decomposition. In Proceedings of the 2004 International Symposium on Low Power Electronics and Design, Newport Beach, CA, USA, 9–11 August 2004; ACM: New York, NY, USA, 2004; pp. 174–179. [Google Scholar] [CrossRef]

- Peluso, V.; Rizzo, R.G.; Calimera, A.; Macii, E.; Alioto, M. Beyond Ideal DVFS Through Ultra-Fine Grain Vdd-Hopping. In Proceedings of the IFIP/IEEE International Conference on Very Large Scale Integration-System on a Chip, Tallinn, Estonia, 26–28 September 2016; Springer: Cham, Switzerland, 2016; pp. 152–172. [Google Scholar]

- Martin, S.M.; Flautner, K.; Mudge, T.; Blaauw, D. Combined dynamic voltage scaling and adaptive body biasing for lower power microprocessors under dynamic workloads. In Proceedings of the 2002 IEEE/ACM International Conference On Computer-Aided Design, San Jose, CA, USA, 10–14 November 2002; pp. 721–725. [Google Scholar]

- Hemantha, S.; Dhawan, A.; Kar, H. Multi-threshold CMOS design for low power digital circuits. In Proceedings of the TENCON 2008 IEEE Region 10 Conference, Hyderabad, India, 19–21 November 2008; pp. 1–5. [Google Scholar]

- Calimera, A.; Pullini, A.; Sathanur, A.V.; Benini, L.; Macii, A.; Macii, E.; Poncino, M. Design of a family of sleep transistor cells for a clustered power-gating flow in 65 nm technology. In Proceedings of the 17th ACM Great Lakes Symposium on VLSI, Lago Maggiore, Italy, 11–13 March 2007; pp. 501–504. [Google Scholar]

- Kahng, A.B.; Kang, S.; Kumar, R.; Sartori, J. Slack redistribution for graceful degradation under voltage overscaling. In Proceedings of the 2010 Asia and South Pacific Design Automation Conference, Taipei, Taiwan, 18–21 January 2010; pp. 825–831. [Google Scholar]

- Ghosh, S.; Bhunia, S.; Roy, K. CRISTA: A new paradigm for low-power, variation-tolerant, and adaptive circuit synthesis using critical path isolation. IEEE Trans. Comput.-Aided Des. Integrated Circuits Syst. 2007, 26, 1947–1956. [Google Scholar] [CrossRef]

- Austin, T.; Bertacco, V.; Blaauw, D.; Mudge, T. Opportunities and Challenges for Better Than Worst-case Design. In Proceedings of the 2005 Asia and South Pacific Design Automation Conference, Shanghai, China, 18–21 January 2005; ACM: New York, NY, USA, 2005; pp. 2–7. [Google Scholar] [CrossRef]

- Bortolotti, D.; Rossi, D.; Bartolini, A.; Benini, L. A variation tolerant architecture for ultra low power multi-processor cluster. In Proceedings of the 2013 23rd International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), Karlsruhe, Germany, 9–11 September 2013; pp. 32–38. [Google Scholar]

- Ernst, D.; Das, S.; Lee, S.; Blaauw, D.; Austin, T.; Mudge, T.; Kim, N.S.; Flautner, K. Razor: Circuit-level correction of timing errors for low-power operation. IEEE Micro 2004, 24, 10–20. [Google Scholar] [CrossRef]

- Ernst, D.; Kim, N.S.; Das, S.; Pant, S.; Rao, R.; Pham, T.; Ziesler, C.; Blaauw, D.; Austin, T.; Flautner, K.; et al. Razor: A low-power pipeline based on circuit-level timing speculation. In Proceedings of the 36th Annual IEEE/ACM International Symposium on Microarchitecture, San Diego, CA, USA, 3–5 December 2003; pp. 7–18. [Google Scholar]

- Das, S.; Roberts, D.; Lee, S.; Pant, S.; Blaauw, D.; Austin, T.; Flautner, K.; Mudge, T. A self-tuning DVS processor using delay-error detection and correction. IEEE J. Solid-State Circuits 2006, 41, 792–804. [Google Scholar] [CrossRef]

- Valadimas, S.; Tsiatouhas, Y.; Arapoyanni, A. Timing error tolerance in nanometer ICs. In Proceedings of the 2010 IEEE 16th International On-Line Testing Symposium, Corfu, Greece, 5–7 July 2010; pp. 283–288. [Google Scholar]

- Das, S.; Tokunaga, C.; Pant, S.; Ma, W.H.; Kalaiselvan, S.; Lai, K.; Bull, D.M.; Blaauw, D.T. RazorII: In situ error detection and correction for PVT and SER tolerance. IEEE J. Solid-State Circuits 2009, 44, 32–48. [Google Scholar] [CrossRef]

- Krause, P.K.; Polian, I. Adaptive voltage over-scaling for resilient applications. In Proceedings of the 2011 Design, Automation Test in Europe, Grenoble, France, 14–18 March 2011; pp. 1–6. [Google Scholar] [CrossRef]

- Alioto, M. Energy-quality scalable adaptive VLSI circuits and systems beyond approximate computing. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, 27–31 March 2017; pp. 127–132. [Google Scholar] [CrossRef]

- Shim, B.; Shanbhag, N.R. Reduced precision redundancy for low-power digital filtering. In Proceedings of the Conference Record of Thirty-Fifth Asilomar Conference on Signals, Systems and Computers (Cat. No. 01CH37256), Pacific Grove, CA, USA, 4–7 November 2001; Volume 1, pp. 148–152. [Google Scholar]

- Shim, B.; Sridhara, S.R.; Shanbhag, N.R. Reliable low-power digital signal processing via reduced precision redundancy. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2004, 12, 497–510. [Google Scholar] [CrossRef]

- Rizzo, R.G.; Calimera, A.; Zhou, J. Approximate Error Detection-Correction for efficient Adaptive Voltage Over-Scaling. Integration 2018, 63, 220–231. [Google Scholar] [CrossRef]

- Rizzo, R.G.; Calimera, A. Tunable Error Detection-Correction for Efficient Adaptive Voltage Over-Scaling. In Proceedings of the 2017 IEEE 1st International New Generation of Circuits and Systems Conference (NGCAS), Genoa, Italy, 6–9 September 2017. [Google Scholar]

- Hegde, R.; Shanbhag, N.R. Energy-efficient signal processing via algorithmic noise-tolerance. In Proceedings of the 1999 International Symposium on Low Power Electronics and Design (Cat. No.99TH8477), San Diego, CA, USA, 17 August 1999; pp. 30–35. [Google Scholar]

- Hegde, R.; Shanbhag, N.R. A low-power digital filter IC via soft DSP. In Proceedings of the IEEE 2001 Custom Integrated Circuits Conference (Cat. No.01CH37169), San Diego, CA, USA, 9 May 2001; pp. 309–312. [Google Scholar]

- Rizzo, R.G.; Peluso, V.; Calimera, A.; Zhou, J.; Liu, X. Early Bird Sampling: A Short-Paths Free Error Detection-Correction Strategy for Data-Driven VOS. In Proceedings of the 2017 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Abu Dhabi, UAE, 23–25 October 2017. [Google Scholar]

- Bowman, K.A.; Tschanz, J.W.; Kim, N.S.; Lee, J.C.; Wilkerson, C.B.; Lu, S.L.L.; Karnik, T.; De, V.K. Energy-efficient and metastability-immune resilient circuits for dynamic variation tolerance. IEEE J. Solid-State Circuits 2009, 44, 49–63. [Google Scholar] [CrossRef]

- Kim, S.; Seok, M. Variation-tolerant, ultra-low-voltage microprocessor with a low-overhead, within-a-cycle in-situ timing-error detection and correction technique. IEEE J. Solid-State Circuits 2015, 50, 1478–1490. [Google Scholar] [CrossRef]

- Chippa, V.K.; Chakradhar, S.T.; Roy, K.; Raghunathan, A. Analysis and characterization of inherent application resilience for approximate computing. In Proceedings of the 50th Annual Design Automation Conference, Austin, TX, USA, 29 May–7 June 2013; p. 113. [Google Scholar]

- Nogues, E.; Menard, D.; Pelcat, M. Algorithmic-level approximate computing applied to energy efficient hevc decoding. IEEE Trans. Emerg. Top. Comput. 2016, 7, 5–7. [Google Scholar] [CrossRef]

| Technique | Vdd | EPO | OPC | N. Errors | NRMSE | MAE | Area |

|---|---|---|---|---|---|---|---|

| [V] | [norm] | [%] | [norm] | [norm] | |||

| Min. EPO point | |||||||

| AED-C (DW = 15%) | 0.78 | 0.46 | 0.98 | 3226 | 0.84 | 21 | 1.06 |

| ANT (B = 4) | 0.68 | 0.46 | 1.00 | 1,382,023 | 3.37 | 17 | 1.51 |

| NRMSE-EPO Knee point | |||||||

| AED-C (DW = 25%) | 0.82 | 0.52 | 0.98 | 114 | 0.13 | 20 | 1.06 |

| ANT (B = 5) | 0.78 | 0.66 | 1.00 | 97,664 | 0.16 | 16 | 1.59 |

| Min. NRMSE point | |||||||

| AED-C (DW = 50%) | 0.99 | 0.81 | 0.98 | 16 | 0.01 | 17 | 1.06 |

| ANT (B = 6) | 0.82 | 0.78 | 1.00 | 11,746 | 0.01 | 16 | 1.66 |

| Technique | Vdd | EPO | OPC | N. Errors | NRMSE | MAE | Area |

|---|---|---|---|---|---|---|---|

| [V] | [norm] | [%] | [norm] | [norm] | |||

| Min. EPO point | |||||||

| AED-C (DW = 15%) | 0.74 | 0.41 | 0.98 | 93387 | 6.19 | 30 | 1.46 |

| ANT (B = 4) | 0.68 | 0.67 | 1.00 | 4586948 | 13.15 | 26 | 2.12 |

| NRMSE-EPO Knee point | |||||||

| AED-C (DW = 35%) | 0.83 | 0.54 | 0.98 | 11759 | 0.80 | 30 | 1.46 |

| ANT (B = 5) | 0.72 | 0.76 | 1.00 | 2316127 | 6.01 | 25 | 2.17 |

| Min. NRMSE point | |||||||

| AED-C (DW = 50%) | 0.96 | 0.76 | 0.98 | 1548 | 0.20 | 27 | 1.46 |

| ANT (B = 8) | 0.80 | 0.96 | 1.00 | 99872 | 0.76 | 21 | 2.31 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rizzo, R.G.; Calimera, A. Implementing Adaptive Voltage Over-Scaling: Algorithmic Noise Tolerance vs. Approximate Error Detection. J. Low Power Electron. Appl. 2019, 9, 17. https://doi.org/10.3390/jlpea9020017

Rizzo RG, Calimera A. Implementing Adaptive Voltage Over-Scaling: Algorithmic Noise Tolerance vs. Approximate Error Detection. Journal of Low Power Electronics and Applications. 2019; 9(2):17. https://doi.org/10.3390/jlpea9020017

Chicago/Turabian StyleRizzo, Roberto Giorgio, and Andrea Calimera. 2019. "Implementing Adaptive Voltage Over-Scaling: Algorithmic Noise Tolerance vs. Approximate Error Detection" Journal of Low Power Electronics and Applications 9, no. 2: 17. https://doi.org/10.3390/jlpea9020017

APA StyleRizzo, R. G., & Calimera, A. (2019). Implementing Adaptive Voltage Over-Scaling: Algorithmic Noise Tolerance vs. Approximate Error Detection. Journal of Low Power Electronics and Applications, 9(2), 17. https://doi.org/10.3390/jlpea9020017