Characterization of the Power Distribution Network for Commercialized STM32s Using a Resonance Frequency Measurement Method †

Abstract

1. Introduction

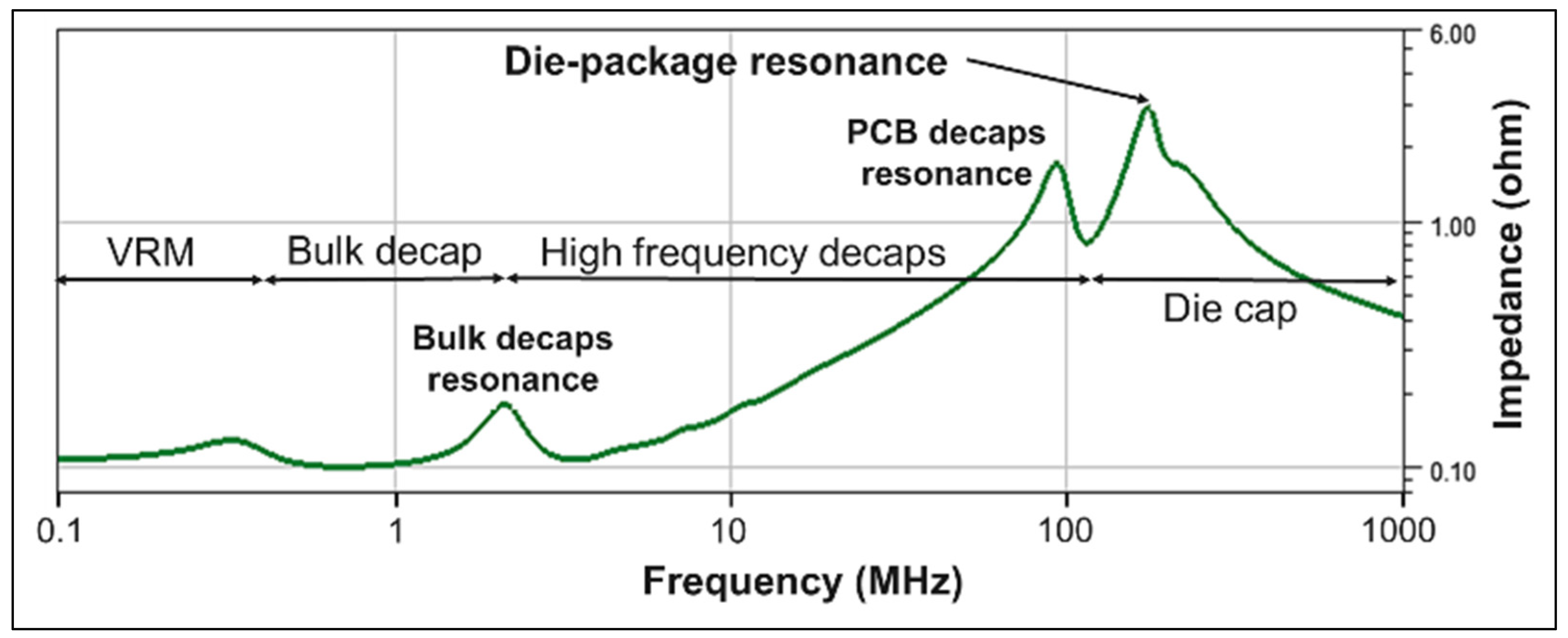

2. Power Integrity Context

2.1. Power Distribution Network

2.2. Power Integrity Risks

2.3. PDN Diagnosis

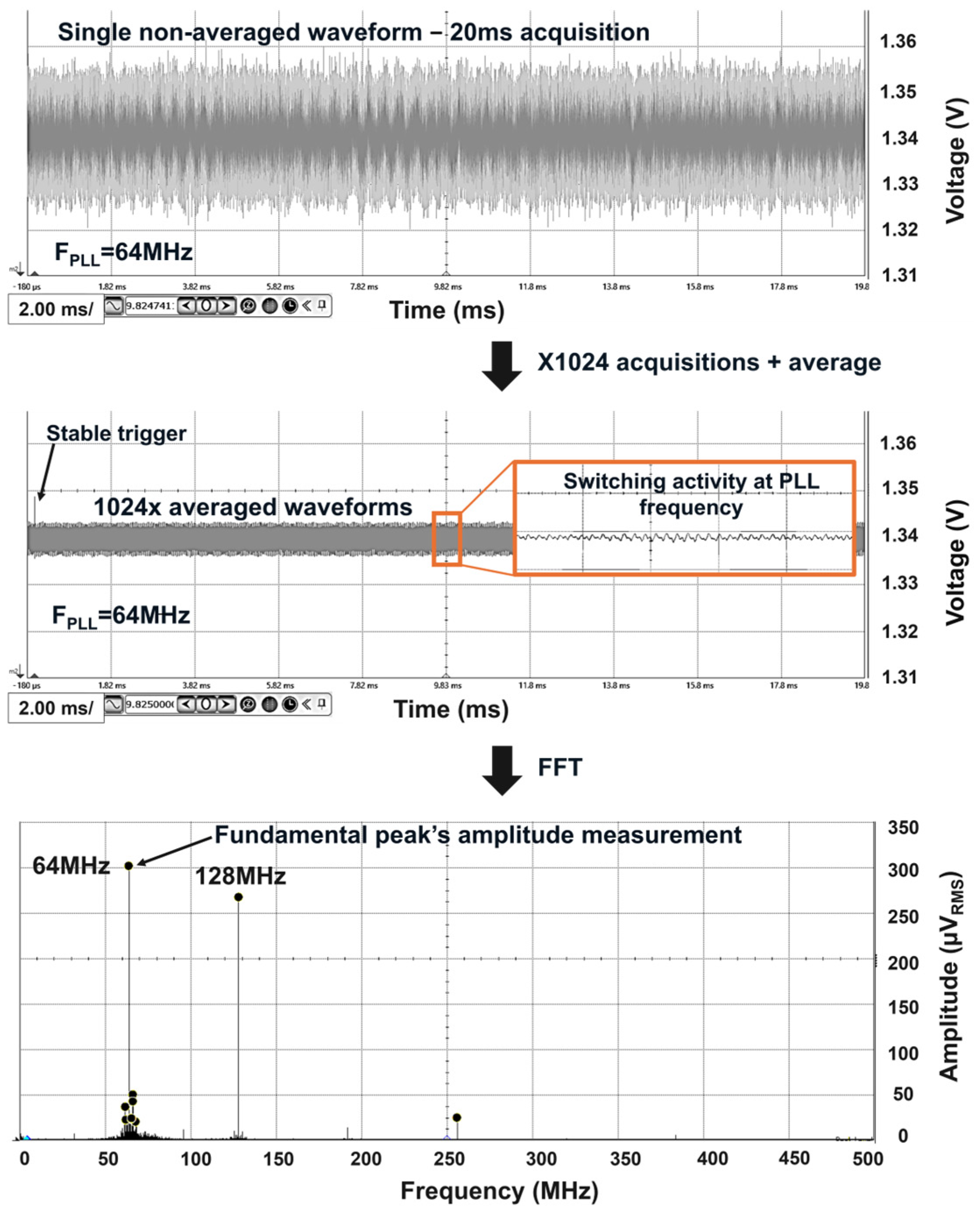

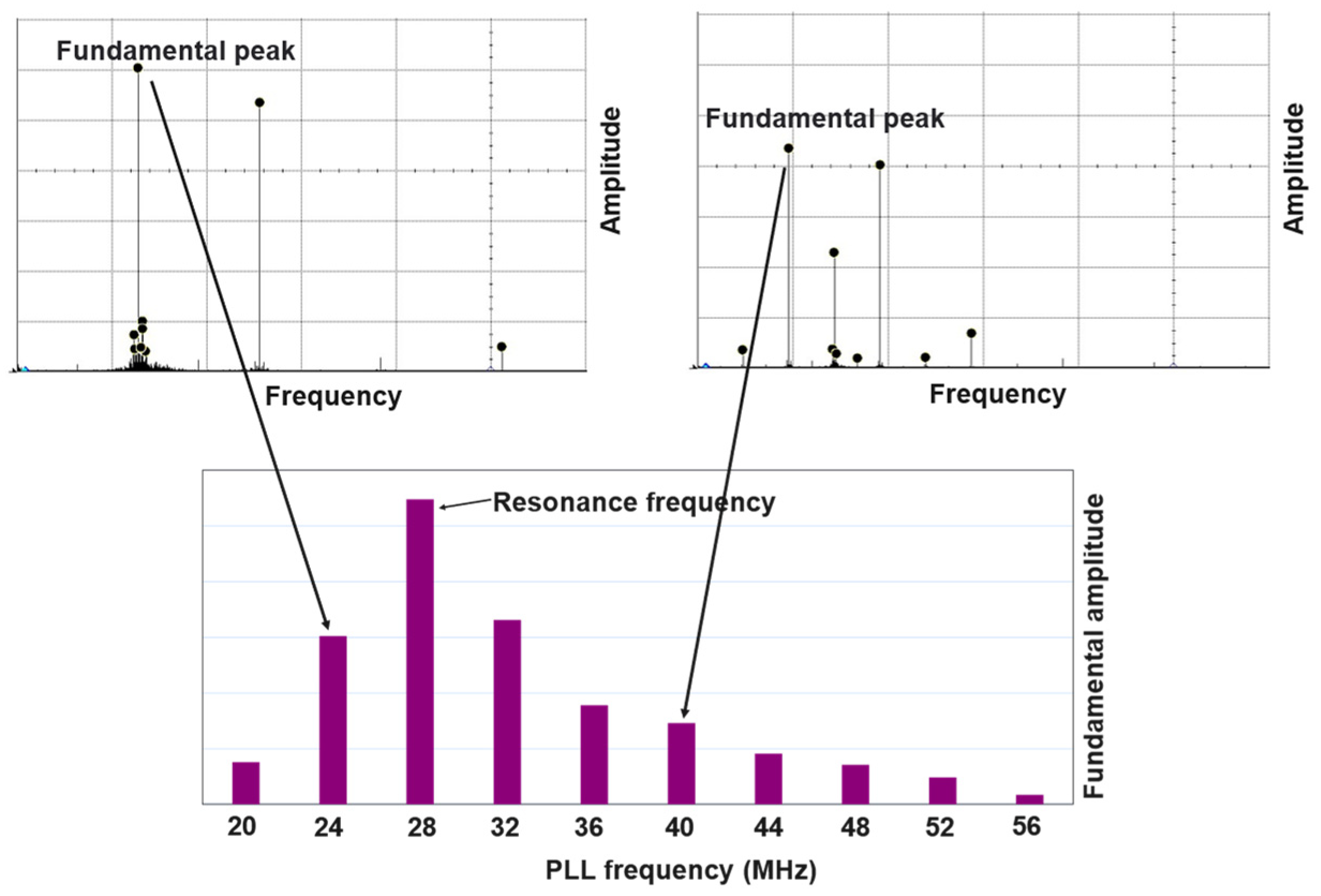

3. Resonance Frequency Measurement Method

3.1. Principle

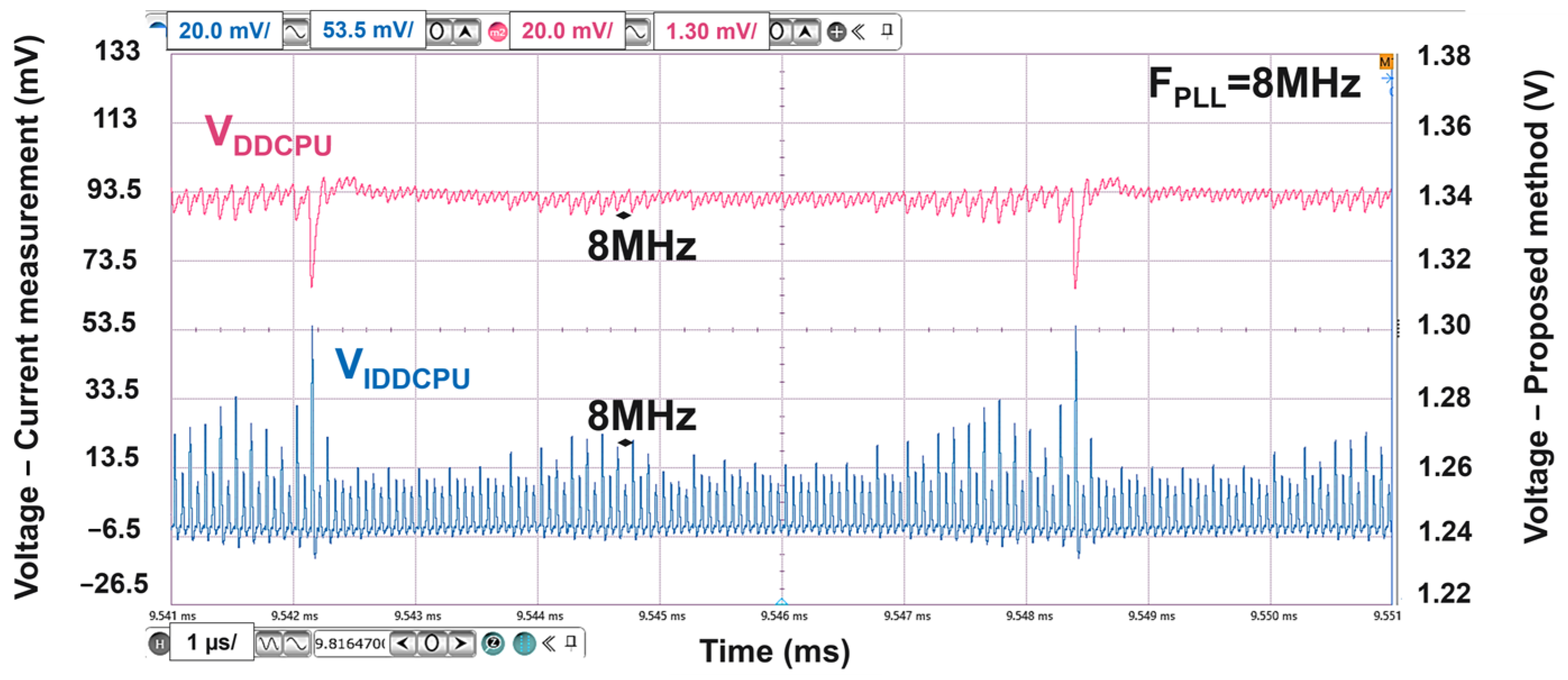

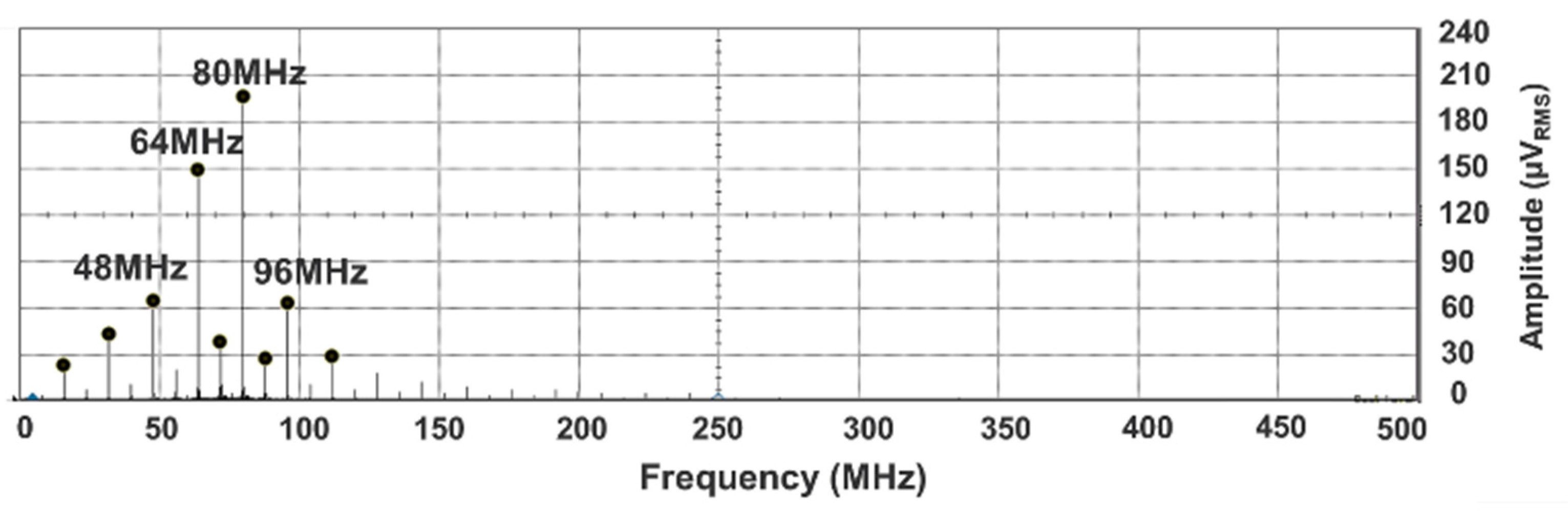

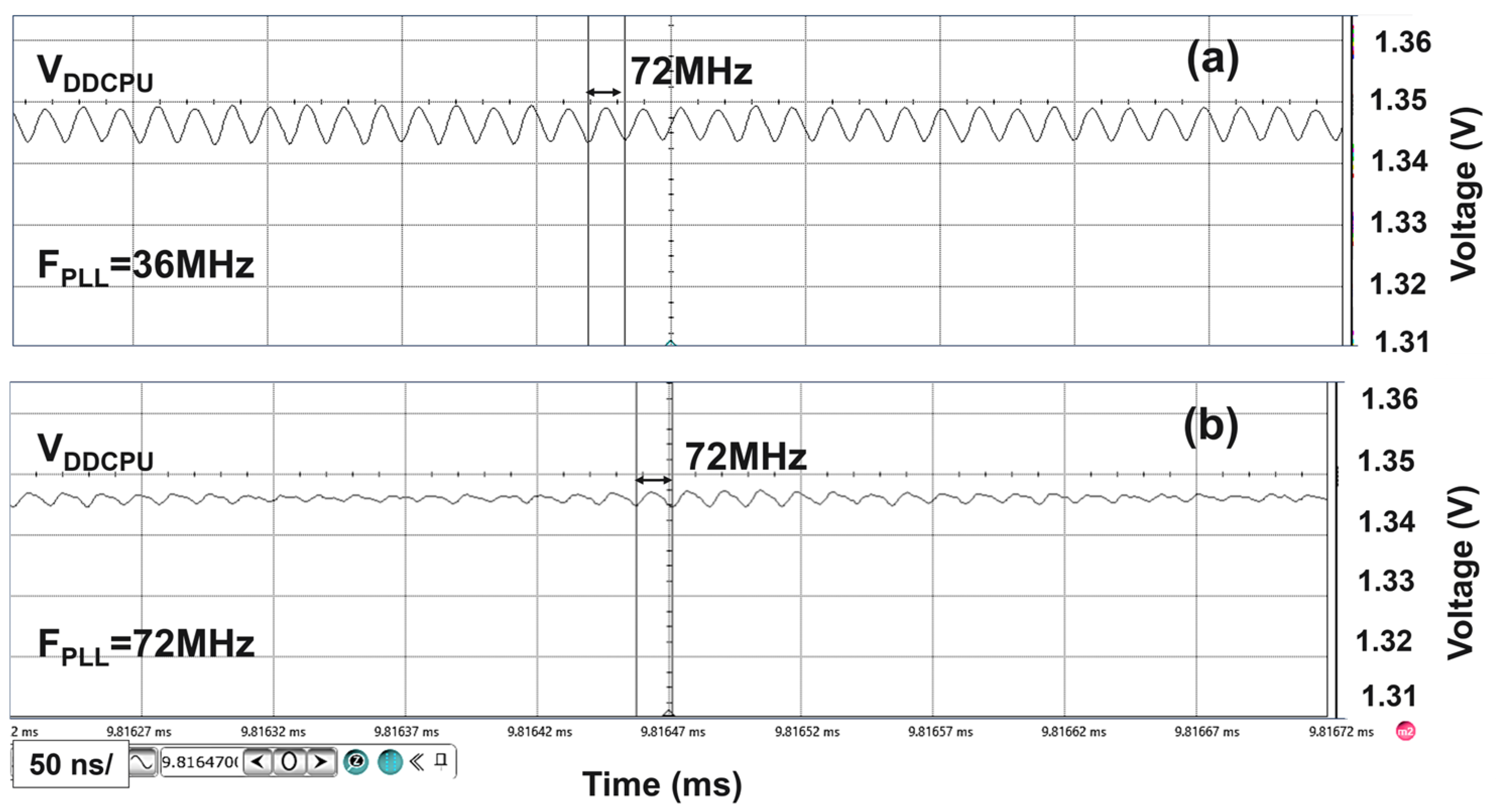

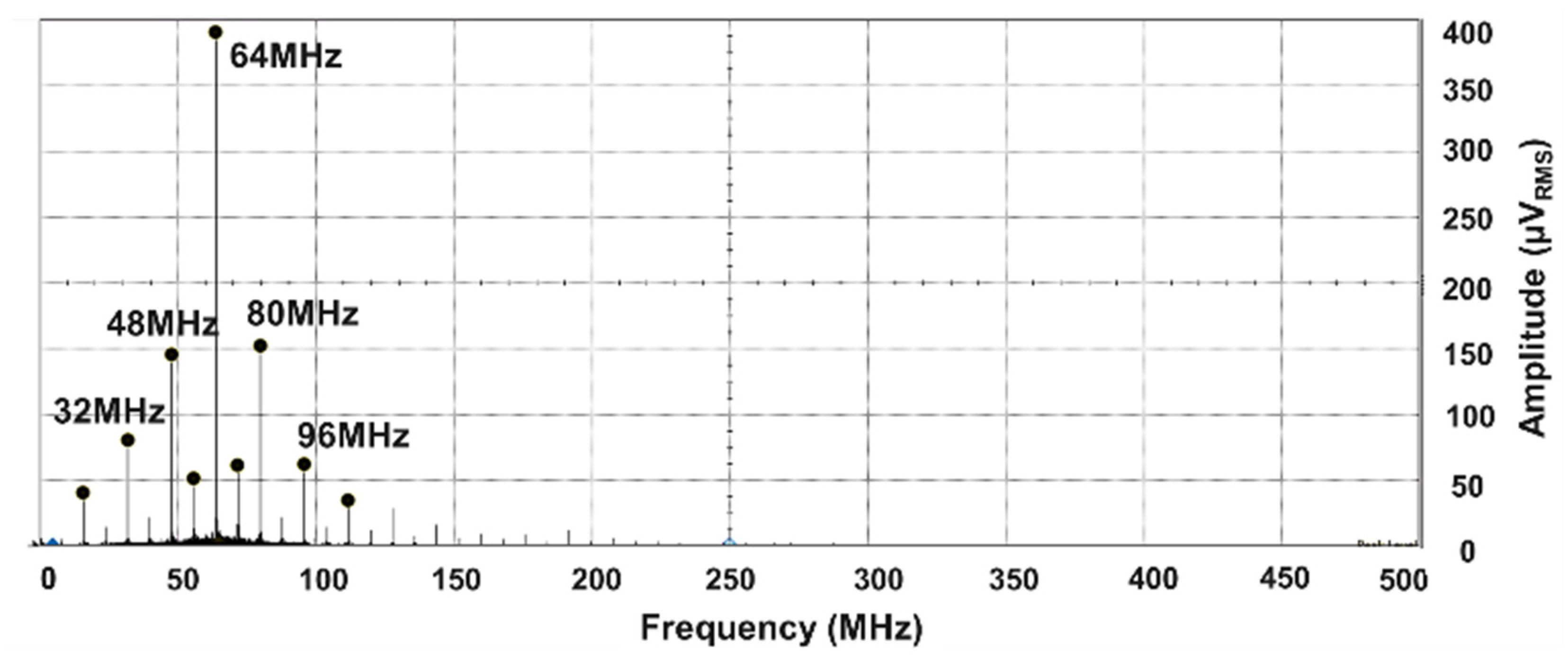

- Sweep the PLL frequency within the main resonance frequency range (10 MHz–200 MHz);

- Measure and average the power supply noise at each frequency;

- Apply a fast Fourier transform (FFT) to the averaged voltage;

- Identify the main resonance frequency using the measured noise and its spectrum.

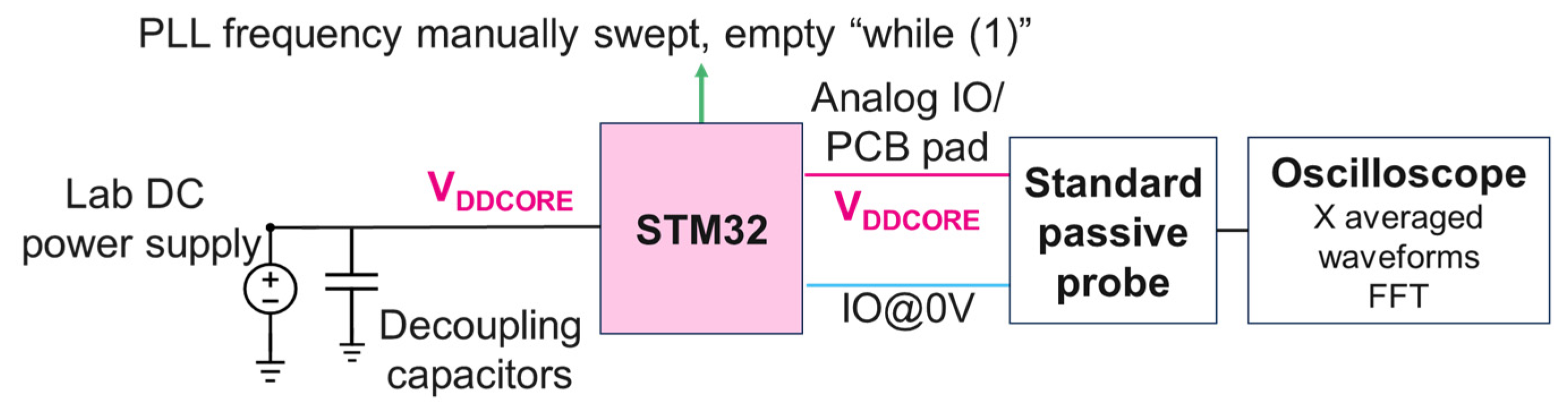

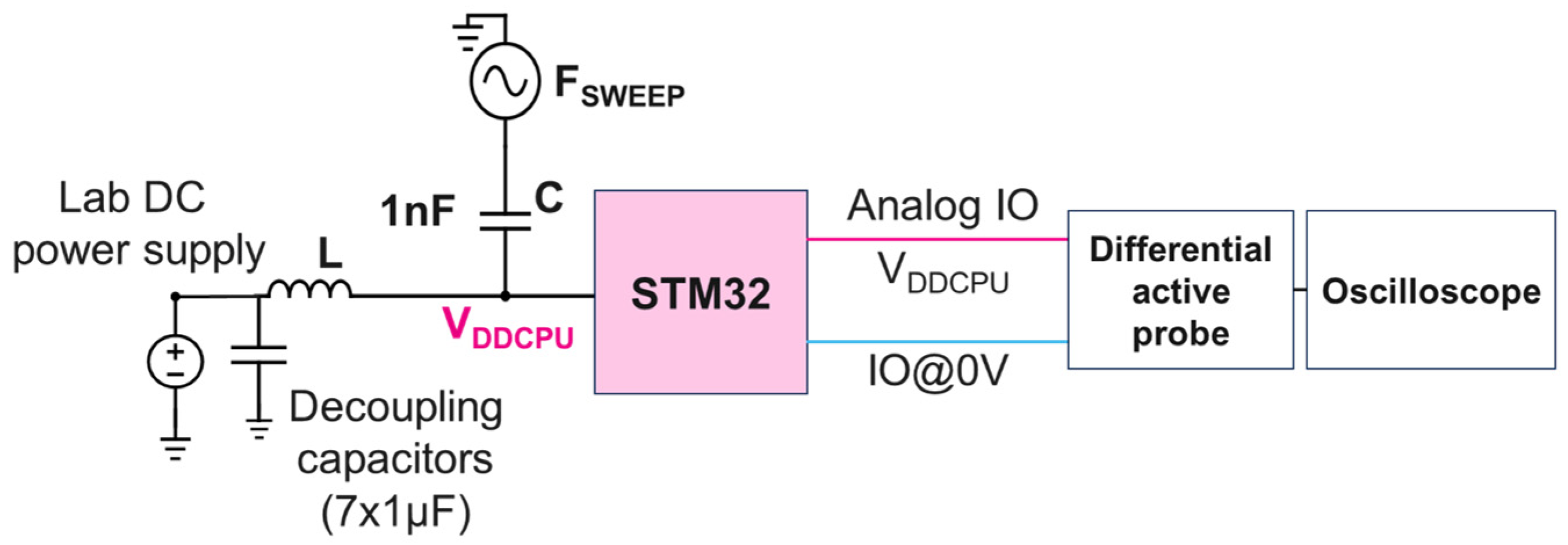

3.2. Measurement Setup

3.3. Setup Validation

4. Validation on a High-Power MPU

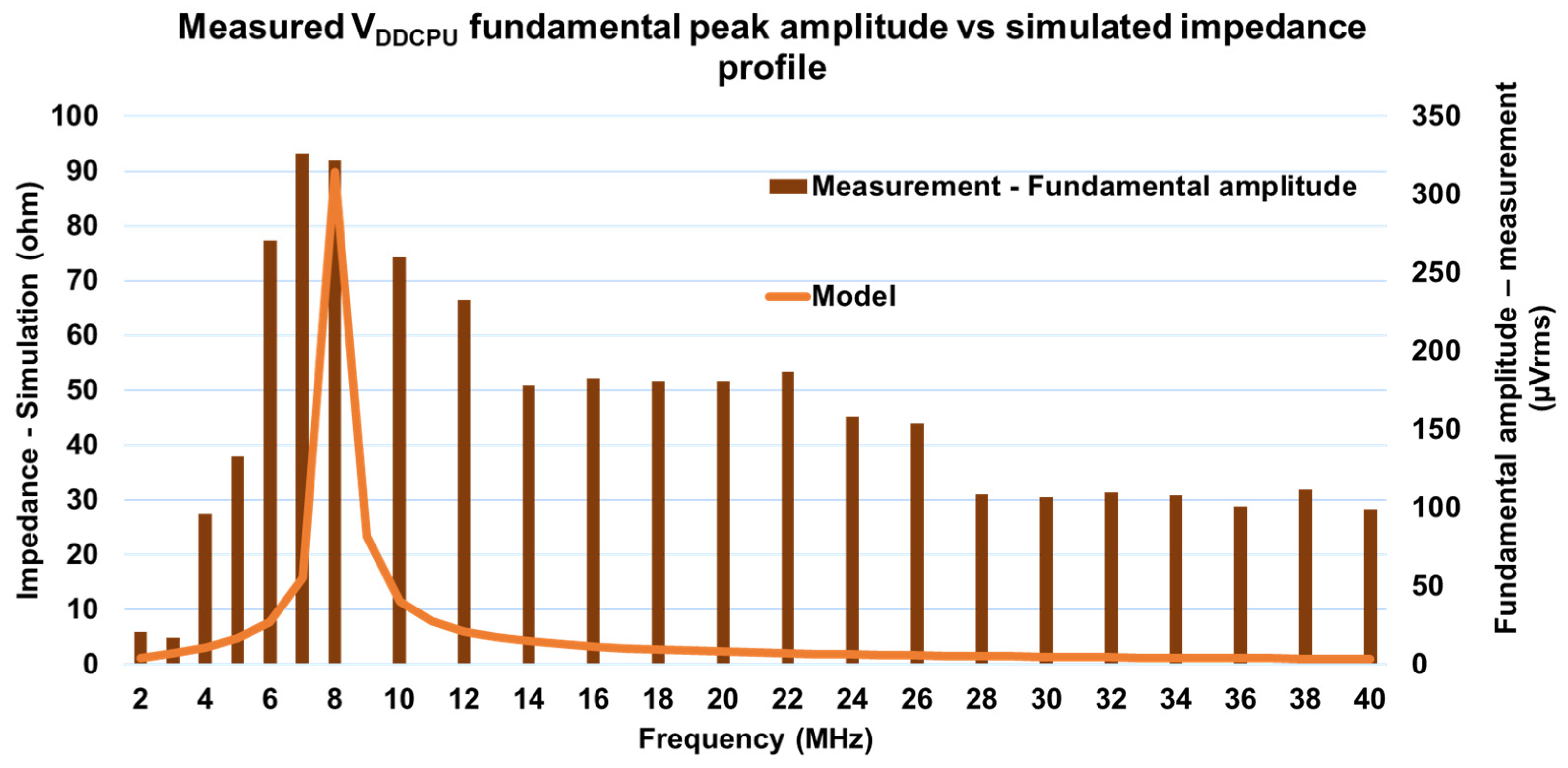

4.1. Comparison with a Previously Validated Method [21]

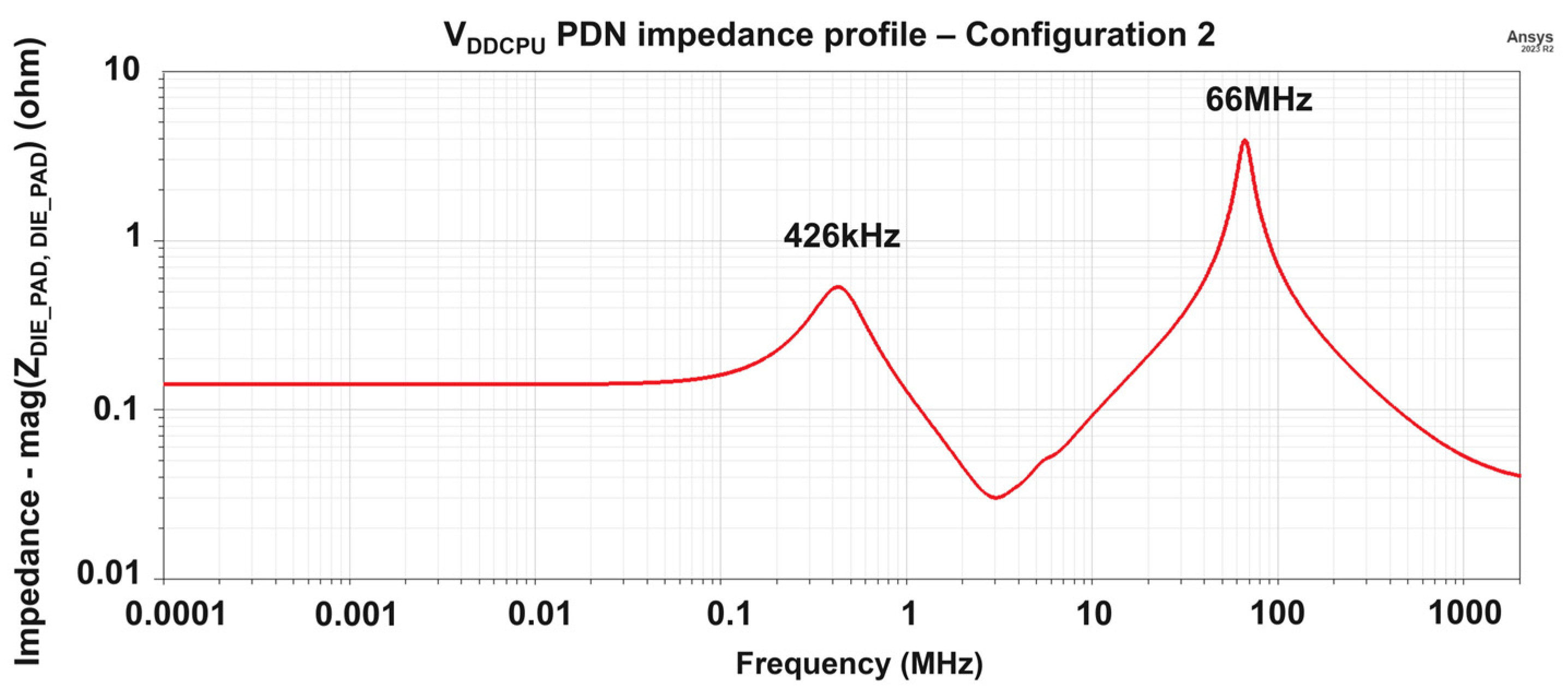

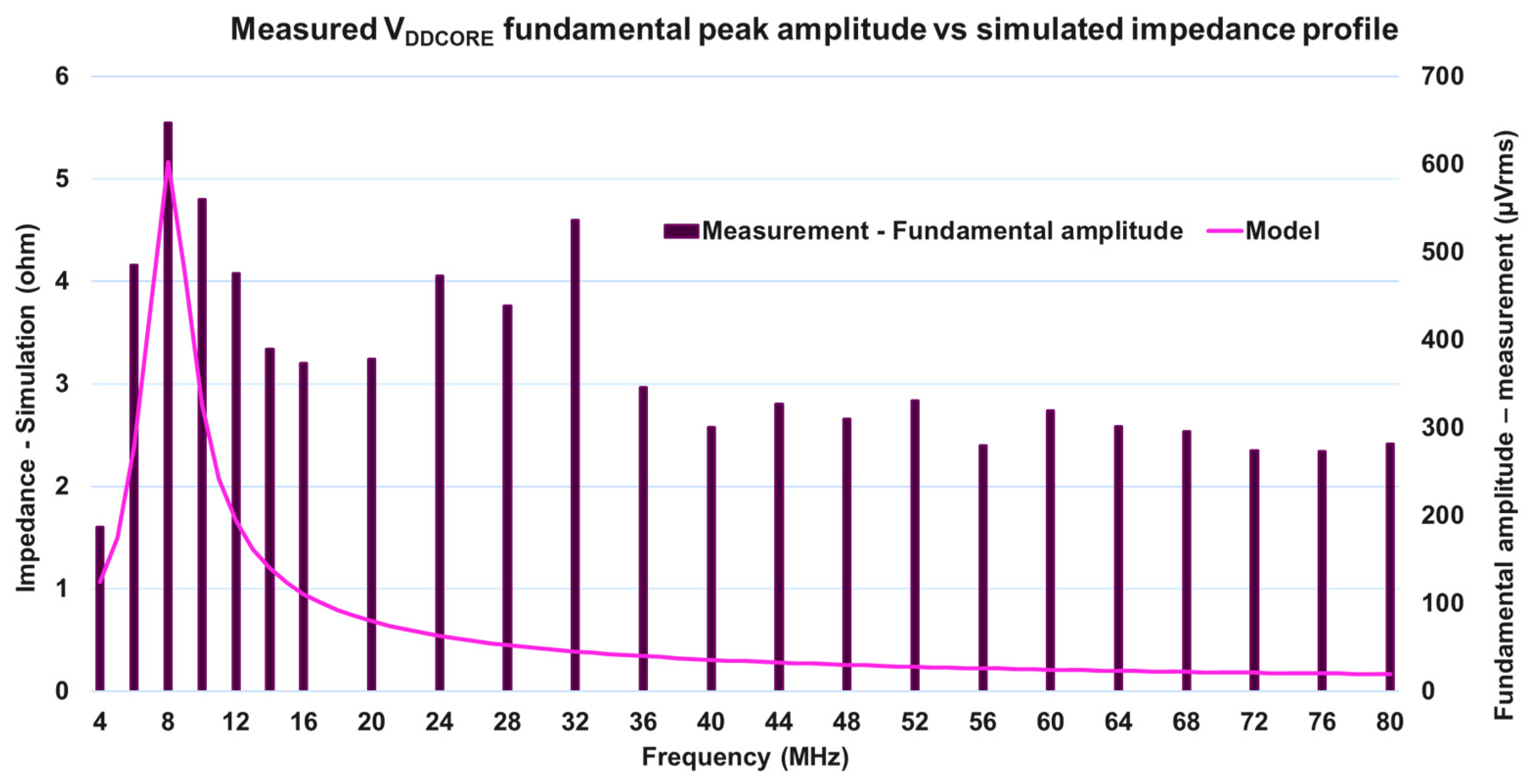

4.2. Modeling and Simulation

4.3. Model Refinement

5. Mid-Range-Power MCU Case Study

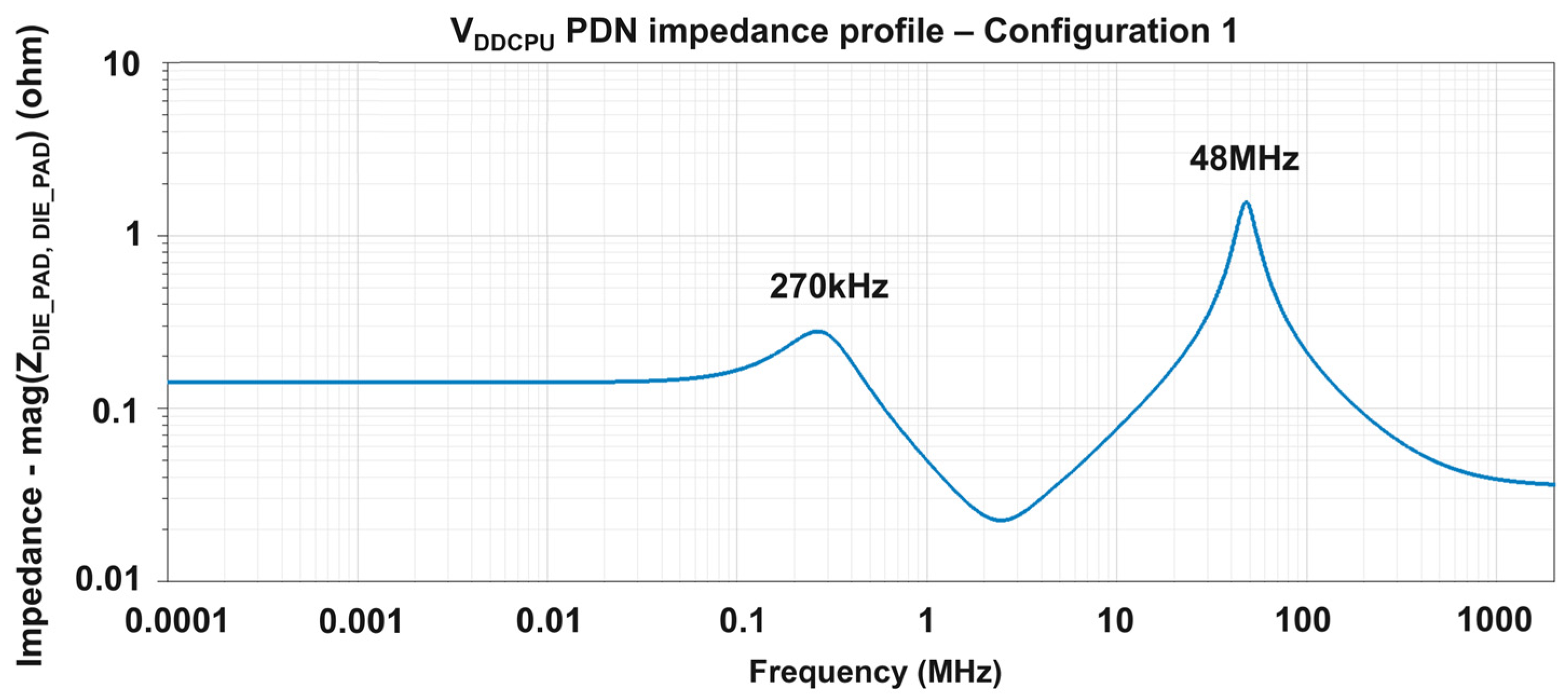

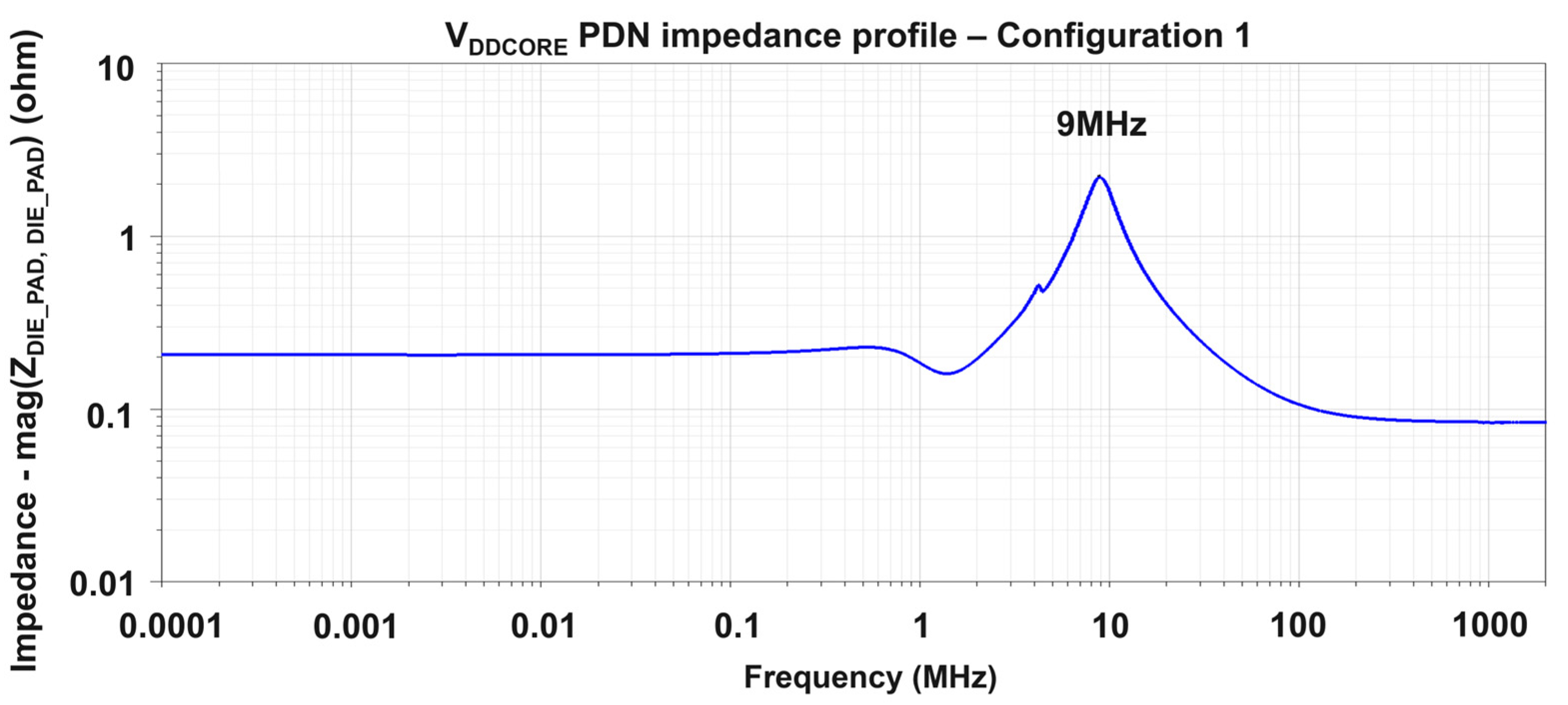

5.1. Modeling and Simulation

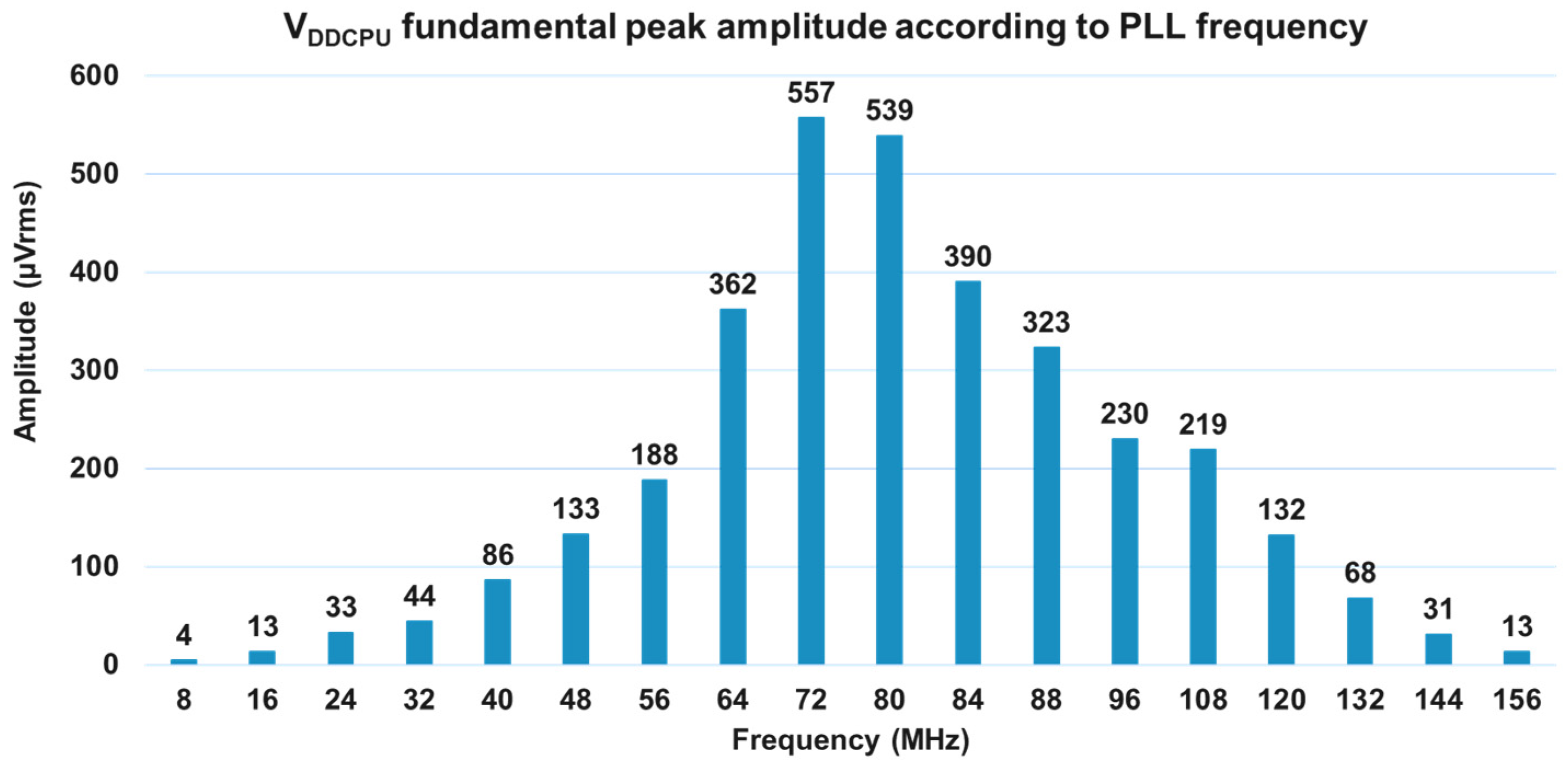

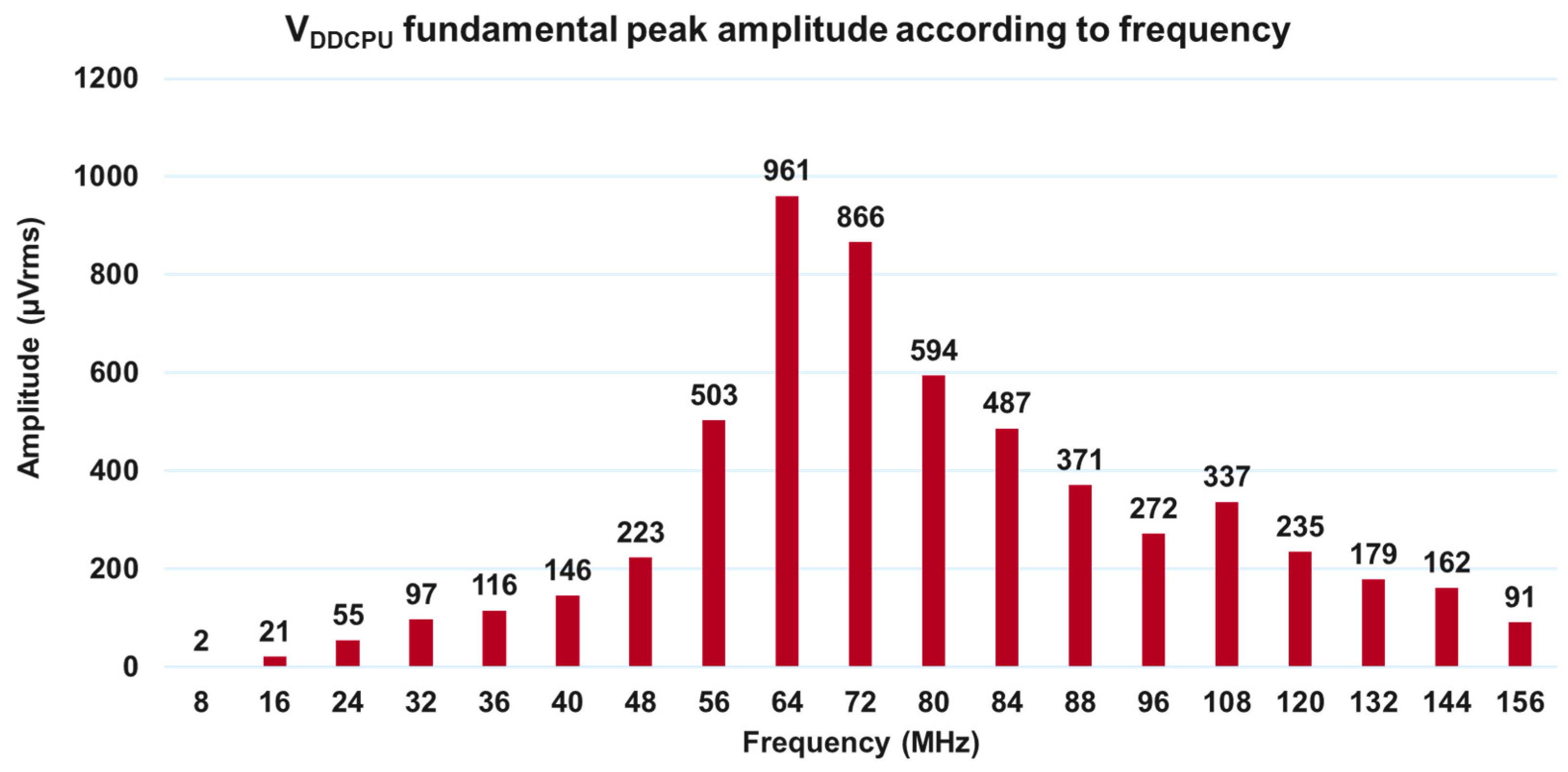

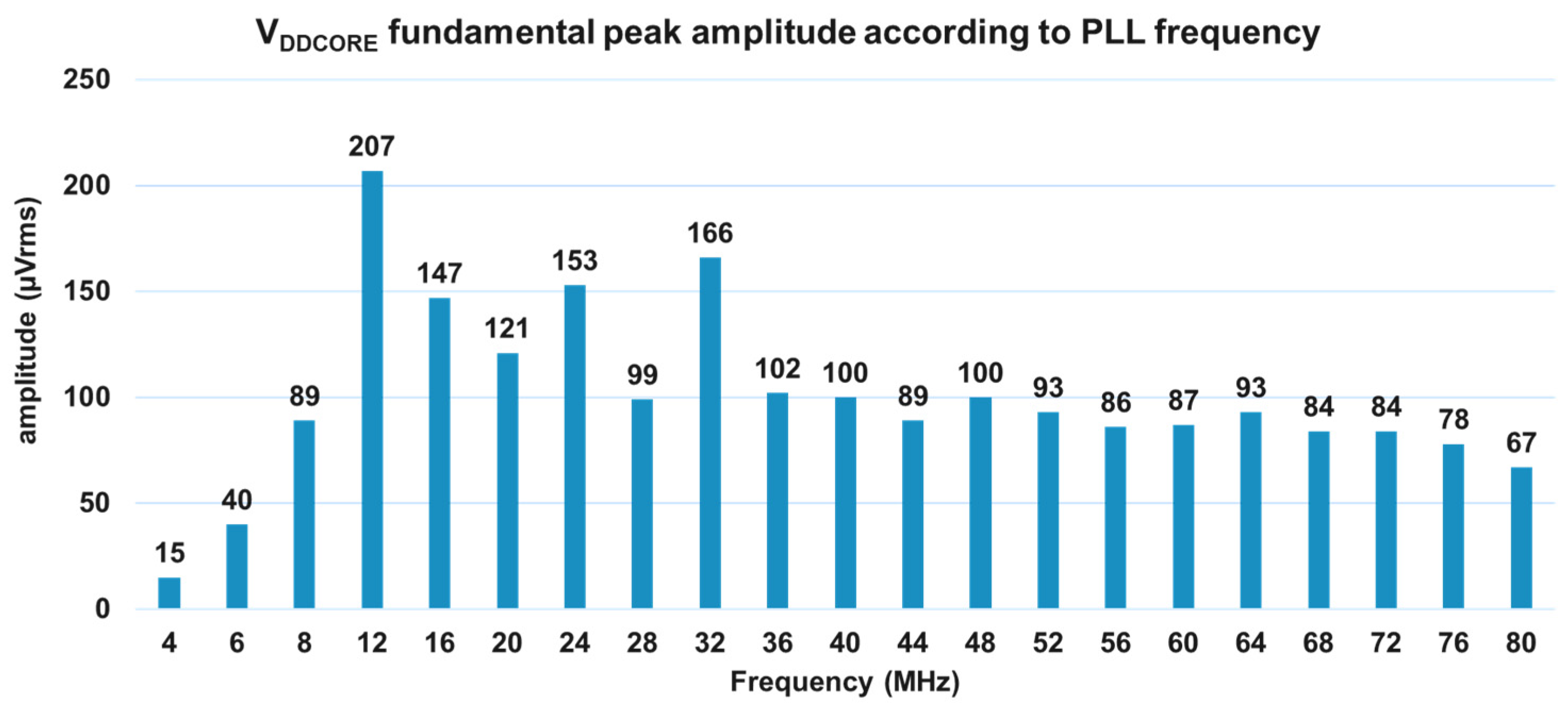

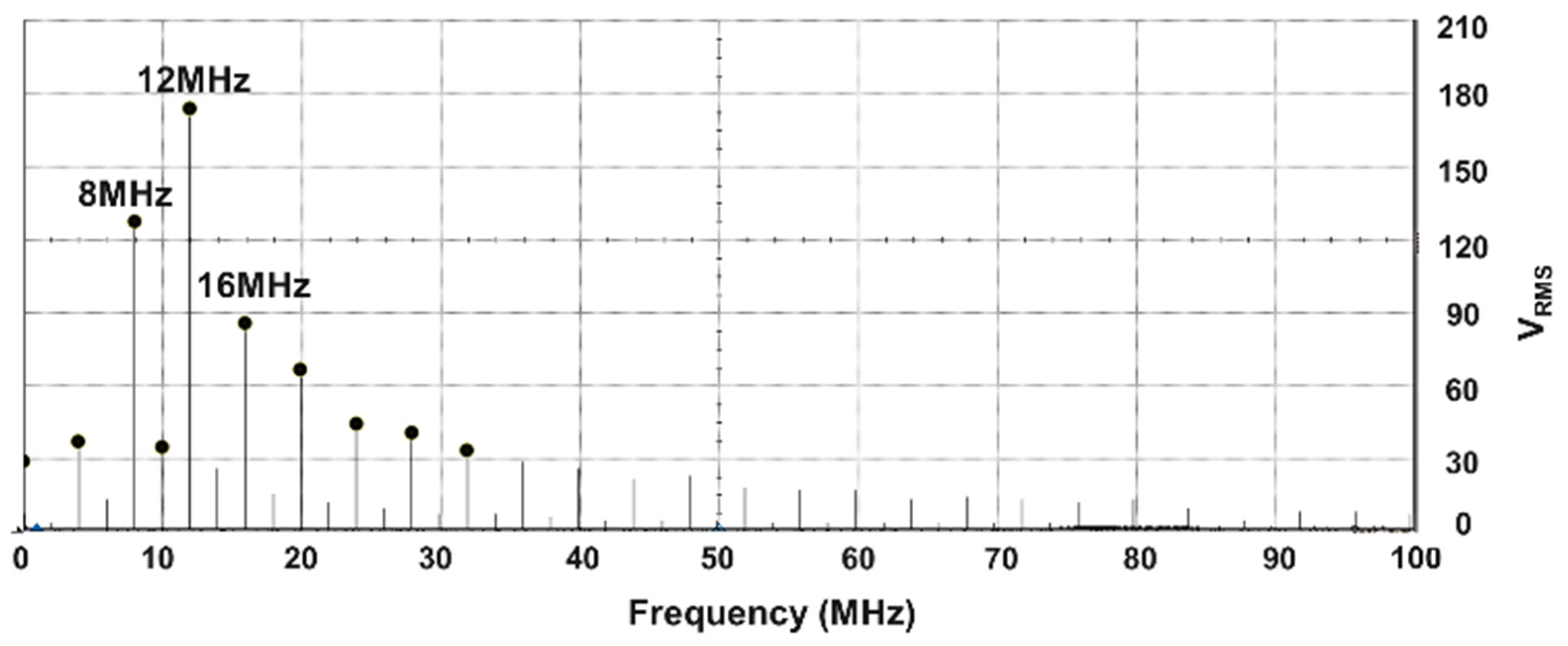

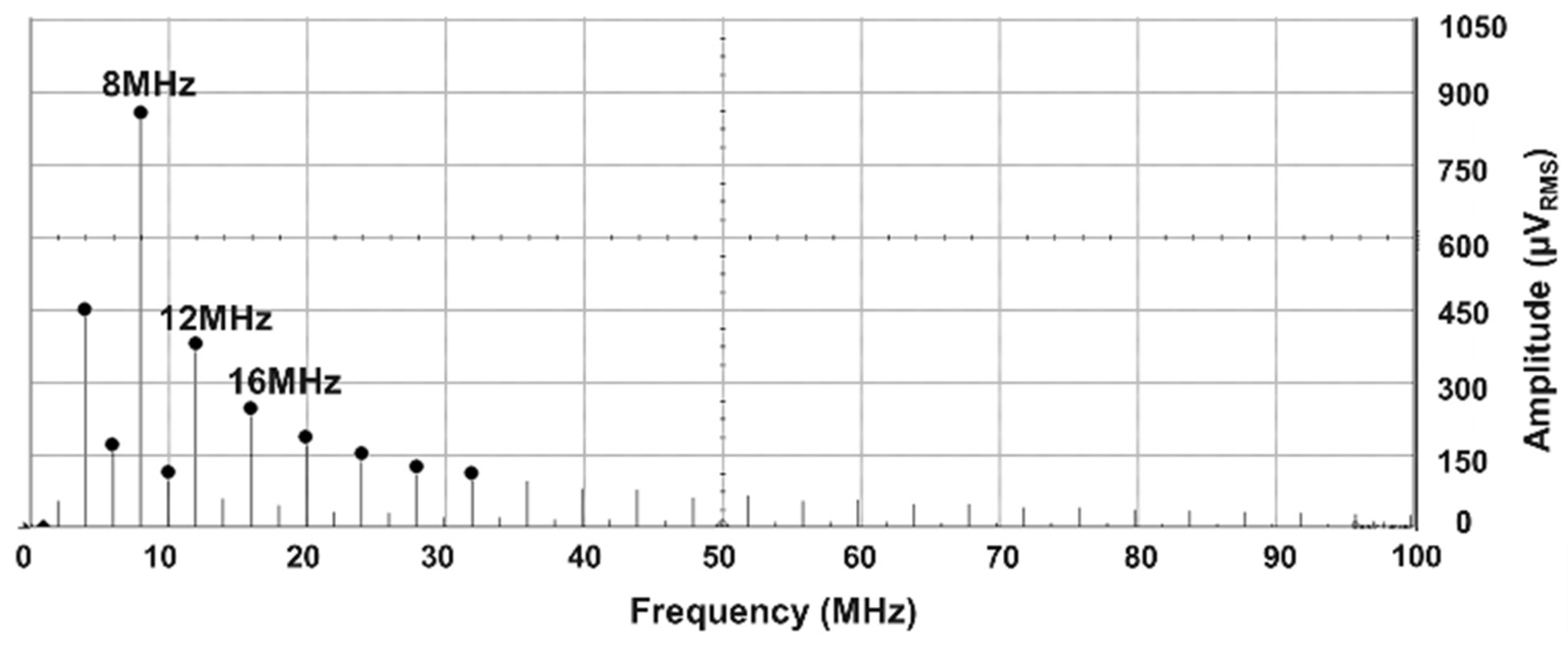

5.2. Experimental Results

5.3. Model Correction

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Peyrard, M.; Jacquemod, G.; Froidevaux, N.; Moign, M. Die capacitance and Power Distribution Network modeling method through measurement of resonant frequency. In Proceedings of the 2023 IEEE Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMC + SIPI), Grand Rapids, MI, USA, 29 July–4 August 2023. [Google Scholar]

- Sun, S.; Smith, L.D.; Boyle, P. On-Chip PDN Noise Characterization and Modeling. In Proceedings of the Desing Con 2010, Santa Clara, CA, USA, 1–4 February 2010. [Google Scholar]

- Das, S.; Whatmough, P.; Bull, D. Modeling and Characterization of the System-Level Power Delivery Network for a Dual-Core ARM Cortex-A57 Cluster in 28 nm CMOS. In Proceedings of the IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), Rome, Italy, 22–24 July 2015. [Google Scholar]

- Dannan, B.; Kuszewski, J.; Vincent, R.; Wu, S.; McCaffrey, W. Improved Methodology to Accurately Perform System Level Power Integrity Analysis Including an ASIC die. In Proceedings of the Design Con 2022, Santa Clara, CA, USA, 5–7 April 2022. [Google Scholar]

- Peyrard, M.; Jacquemod, G.; Froidevaux, N.; Moign, M. Novel measurement method to estimate the main resonance of a Power Distribution Network. In Proceedings of the 2023 IEEE 14th Latin America Symposium on Circuits and Systems (LASCAS), Quito, Ecuador, 28 February–3 March 2023; pp. 1–4. [Google Scholar]

- Larsson, P. Power supply noise in future IC’s: A crystal ball reading. In Proceedings of the IEEE 1999 Custom Integrated Circuits Conference, San Diego, CA, USA, 16–19 May 1999; pp. 467–474. [Google Scholar]

- Novak, I. Systematic Estimation of Worst-Case PDN Noise. In Proceedings of the Desing Con 2015, Oracle, CA, USA, 27–30 January 2015. [Google Scholar]

- Takamiya, M.; Mizuno, M.; Nakamura, K. An on-chip 100 GHz-Sampling rate 8-channel sampling oscilloscope with embedded sampling clock generator. In Proceedings of the IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2002. [Google Scholar]

- Zheng, Y.; Shepard, K.L. On-chip oscilloscopes for noninvasive time-domain measurement of waveforms in digital integrated circuits. IEEE Trans. Very Large-Scale Integr. VLSI Syst. 2003, 11, 336–344. [Google Scholar] [CrossRef]

- Pant, S.; Blaauw, D. Circuit techniques for suppression and measurement of on-chip inductive supply noise. In Proceedings of the ESSCIRC 2008—34th European Solid-State Circuits Conference, Edinburgh, UK, 15–19 September 2008. [Google Scholar]

- Takamiya, M.; Mizuno, M. A sampling oscilloscope macro toward feedback physical design methodology. In Proceedings of the 2004 Symposium on VLSI Circuits, Digest of Technical Papers, Honolulu, HI, USA, 17–19 June 2004. [Google Scholar]

- Noguchi, K.; Nagata, M. An On-Chip Multichannel Waveform Monitor for Diagnosis of Systems-on-a-Chip Integration. IEEE Trans. Very Large-Scale Integr. VLSI Syst. 2007, 15, 1101–1110. [Google Scholar] [CrossRef]

- Hsueh, T.C.; O’Mahony, F.; Mansuri, M.; Casper, B. An on-die all-digital power supply noise analyzer with enhanced spectrum measurements. IEEE J. Solid-State Circuits 2015, 50, 1711–1721. [Google Scholar] [CrossRef]

- Hashida, T.; Nagata, M. An On-Chip Waveform Capturer and Application to Diagnosis of Power Delivery in SoC Integration. IEEE J. Solid-State Circuits 2011, 46, 789–796. [Google Scholar] [CrossRef]

- Whatmough, P.N.; Das, S.; Hadjilambrou, Z.; Bull, D.M. Power Integrity Analysis of a 28 nm Dual-Core ARM Cortex-A57 Cluster Using an All-Digital Power Delivery Monitor. IEEE J. Solid-State Circuits 2017, 52, 1643–1654. [Google Scholar] [CrossRef]

- Waizman, A.; Livshitz, M.; Sotman, M. Integrated Power Supply Frequency Domain Impedance Meter (IFDIM). In Proceedings of the Electrical Performance of Electronic Packaging, Portland, OR, USA, 25–27 October 2004. [Google Scholar]

- Weekly, R.; Chun, S.; Haridass, A.; O’Reilly, C.; Jordan, J.; O’Connell, F. Optimum design of power distribution system via clock modulation. In Proceedings of the Electrical Performance of Electrical Packaging (IEEE Cat. No. 03TH8710), Princeton, NJ, USA, 27–29 October 2003; pp. 45–48. [Google Scholar]

- Xu, J.; Hazucha, P.; Huang, M.; Aseron, P.; Paillet, F.; Schrom, G.; Tschanz, J.; Zhao, C.; De, V.; Karnik, T.; et al. On-Die Supply-Resonance Suppression Using Band-Limited Active Damping. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 286–603. [Google Scholar]

- Gu, J.; Eom, H.; Kim, C.H. On-Chip Supply Noise Regulation Using a Low-Power Digital Switched Decoupling Capacitor Circuit. IEEE J. Solid-State Circuits 2009, 44, 1765–1775. [Google Scholar] [CrossRef]

- Kantorovich, I.; Houghton, C.; Root, S.; Laurent, J.S. Measurement of low impedance on chip power supply loop. IEEE Trans. Adv. Packag. 2004, 27, 10–14. [Google Scholar] [CrossRef]

- Quazzo, L.; Bacher, Y.; Froidevaux, N.; Braquet, H.; Jacquemod, G. Resonance Analysis Methods for Estimation of FTB Propagation in Integrated Circuits. In Proceedings of the 2018 IEEE Radio and Antenna Days of the Indian Ocean (RADIO), Wolmar, Mauritius, 15–18 October 2018. [Google Scholar]

- Sandler, S.; Smith, L.D.; Bogatin, E. VRM Modeling: A Strategy to Survive the Collision of Three Worlds. In Proceedings of the EDI CON, Santa Clara, CA, USA, 17–19 October 2018. [Google Scholar]

| Configuration 1 | Configuration 2 | Configuration 3 | Configuration 4 |

|---|---|---|---|

| 7 × 1 µF (all decaps) | 3 × 7 µF (3 decaps) | 1 × 1 µF (1 decap) | No decap |

| Method Used | Main resonance in Configuration 1 | Main Resonance in Configuration 2 |

|---|---|---|

| Former method | ~75–80 MHz | ~70 MHz |

| This work | ~80 MHz | ~64 MHz |

| Setup Element | Parasitic Impedance | Parasitic Capacitance | Parasitic Inductance |

|---|---|---|---|

| Oscilloscope | 1 MΩ | 14 pF | - |

| Passive probe | 9 MΩ | 9.5 pF | 20 nH |

| Supply wires | 62 mΩ | - | 46 nH |

| Configuration | Measurement | Simulation | Relative Error |

|---|---|---|---|

| Configuration 1 | 75 MHz | 76 MHz | 1.3% |

| Configuration 2 | 66 MHz | 66 MHz | 0% |

| Configuration 3 | 38 MHz | 38 MHz | 0% |

| Configuration 4 | 7 MHz–8 MHz (7.5 MHz) | 8 MHz | 6.3% |

| Configuration 1 | Configuration 2 |

|---|---|

| 2 × 1 µF | 1 × 1 µF |

| Configuration | Measurement | Simulation | Relative Error |

|---|---|---|---|

| Configuration 1 | 12 MHz | 12 MHz | 0% |

| Configuration 2 | 8 MHz | 8 MHz | 0% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Peyrard, M.; Jacquemod, G.; Froidevaux, N. Characterization of the Power Distribution Network for Commercialized STM32s Using a Resonance Frequency Measurement Method. J. Low Power Electron. Appl. 2024, 14, 52. https://doi.org/10.3390/jlpea14040052

Peyrard M, Jacquemod G, Froidevaux N. Characterization of the Power Distribution Network for Commercialized STM32s Using a Resonance Frequency Measurement Method. Journal of Low Power Electronics and Applications. 2024; 14(4):52. https://doi.org/10.3390/jlpea14040052

Chicago/Turabian StylePeyrard, Marie, Gilles Jacquemod, and Nicolas Froidevaux. 2024. "Characterization of the Power Distribution Network for Commercialized STM32s Using a Resonance Frequency Measurement Method" Journal of Low Power Electronics and Applications 14, no. 4: 52. https://doi.org/10.3390/jlpea14040052

APA StylePeyrard, M., Jacquemod, G., & Froidevaux, N. (2024). Characterization of the Power Distribution Network for Commercialized STM32s Using a Resonance Frequency Measurement Method. Journal of Low Power Electronics and Applications, 14(4), 52. https://doi.org/10.3390/jlpea14040052