Power-to-Noise Optimization in the Design of Neural Recording Amplifier Based on Current Scaling, Source Degeneration Resistor, and Current Reuse

Abstract

1. Introduction

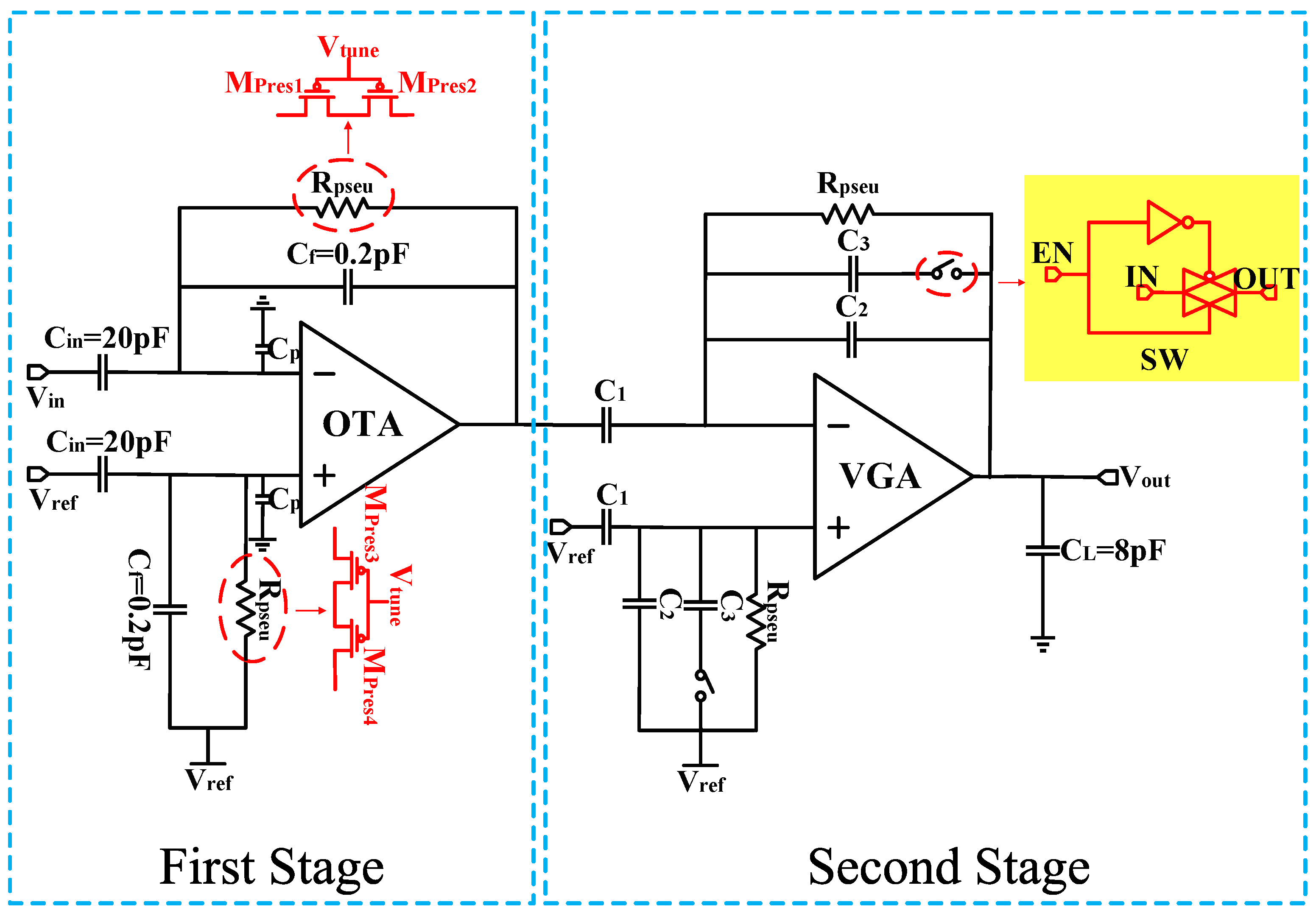

2. Overall System Architecture

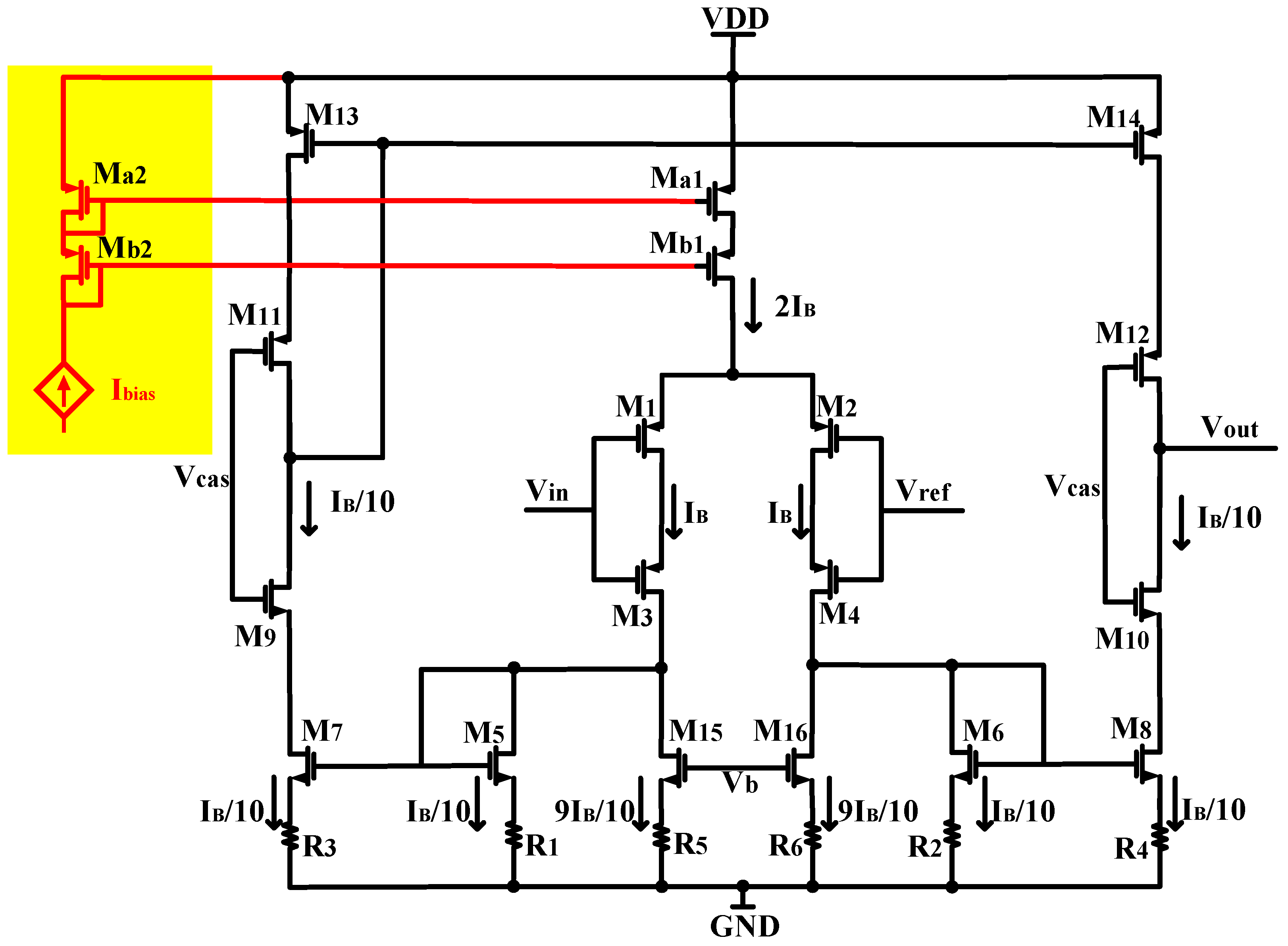

3. The Proposed Low-Power, Low-Noise OTA

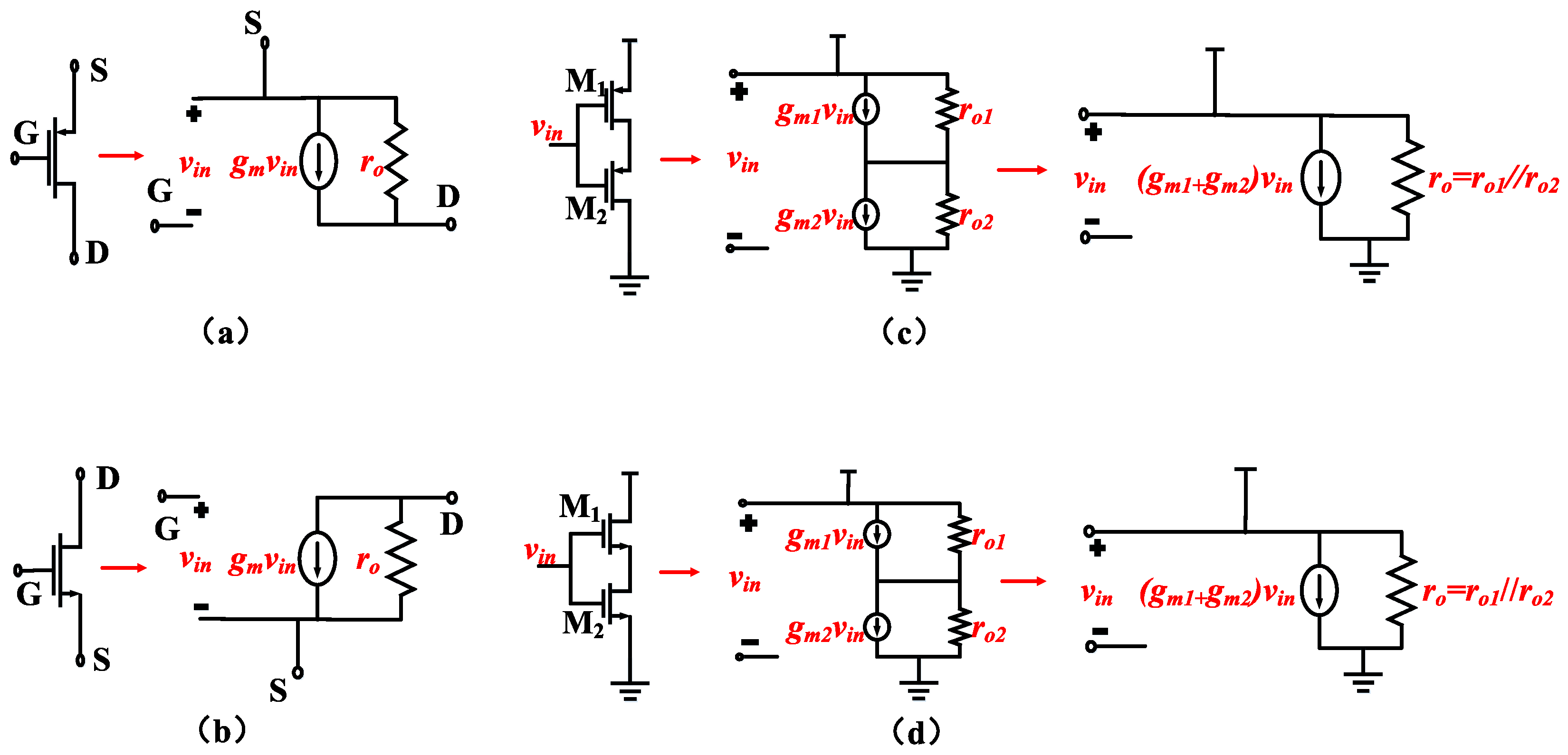

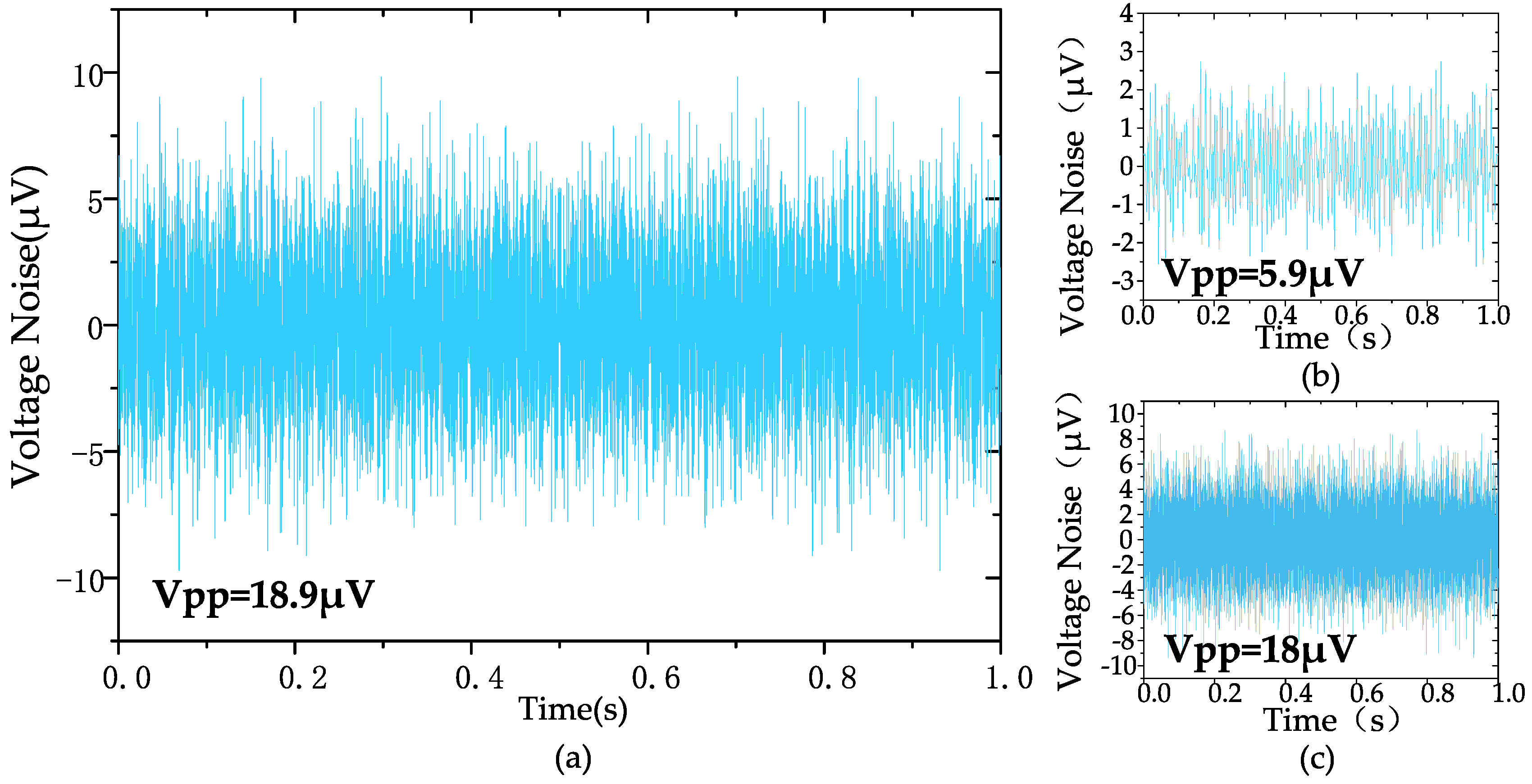

3.1. Proposed OTA

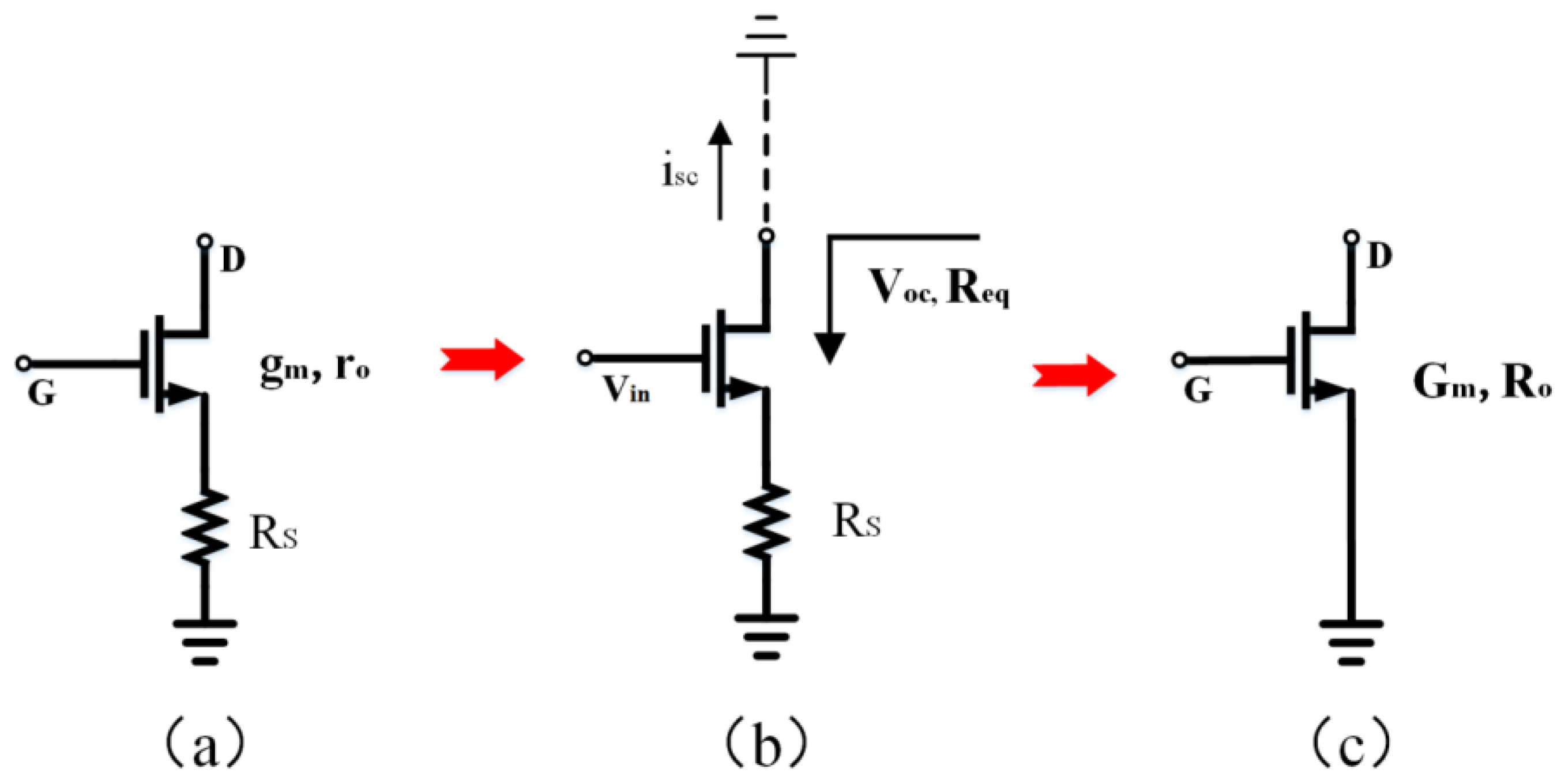

3.2. Maximizing Gm Analysis and Noise Analysis

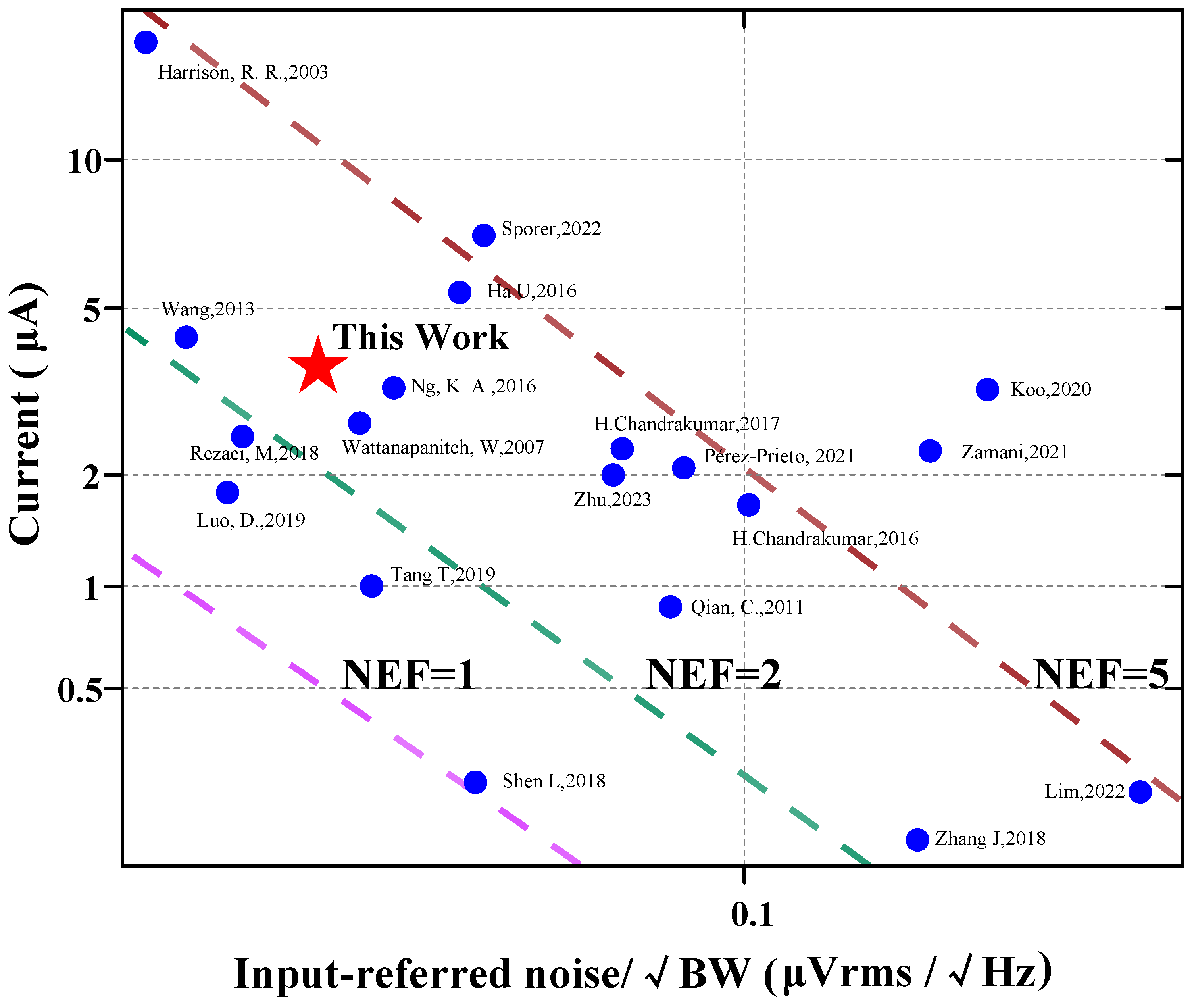

3.3. Noise Efficiency Factor

4. Detailed Circuit Implementation

5. Measurement Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Pais-Vieira, M.; Yadav, A.P.; Moreira, D.; Guggenmos, D.; Santos, A.; Lebedev, M.; Nicolelis, M.A.L. A Closed Loop Brain-machine Interface for Epilepsy Control Using Dorsal Column Electrical Stimulation. Sci Rep. 2016, 6, 32814. [Google Scholar] [CrossRef]

- Guo, L.; Guvanasen, G.S.; Liu, X.; Tuthill, C.; Nichols, T.R.; DeWeerth, S.P. A PDMS-Based Integrated Stretchable Microelectrode Array (isMEA) for Neural and Muscular Surface Interfacing. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 1–10. [Google Scholar]

- Lebedev, M.A.; Nicolelis, M.A. Brain-machine interfaces: Past, present and future. Trends Neurosci. 2006, 29, 536–546. [Google Scholar] [CrossRef]

- Steyaert, M.S.J.; Sansen, W.M.C. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Harrison, R.R.; Watkins, P.T.; Kier, R.J.; Lovejoy, R.O.; Black, D.J.; Greger, B.; Solzbacher, F. A Low-Power Integrated Circuit for a Wireless 100-Electrode Neural Recording System. IEEE J. Solid-State Circuits 2007, 42, 123–133. [Google Scholar] [CrossRef]

- Wattanapanitch, W.; Fee, M.; Sarpeshkar, R. An Energy-Efficient Micropower Neural Recording Amplifier. IEEE Trans. Biomed. Circuits Syst. 2007, 2, 136–147. [Google Scholar] [CrossRef] [PubMed]

- Rezaei, M.; Maghsoudloo, E.; Bories, C.; De Koninck, Y.; Gosselin, B. A Low-Power Current-Reuse Analog Front-End for High-Density Neural Recording Implants. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 271–280. [Google Scholar] [CrossRef]

- Johnson, B.; Molnar, A. An Orthogonal Current-Reuse Amplifier for Multi-Channel Sensing. IEEE J. Solid-State Circuits 2013, 48, 1487–1496. [Google Scholar] [CrossRef]

- Wang, T.-Y.; Lai, M.-R.; Twigg, C.M.; Peng, S.-Y. A Fully Reconfigurable Low-Noise Biopotential Sensing Amplifier with 1.96 Noise Efficiency Factor. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 411–422. [Google Scholar] [CrossRef] [PubMed]

- Chandrakumar, H.; Marković, D. A High Dynamic-Range Neural Recording Chopper Amplifier for Simultaneous Neural Recording and Stimulation. IEEE J. Solid-State Circuits 2017, 52, 645–656. [Google Scholar] [CrossRef]

- Lee, H.S.; Eom, K.; Park, M.; Ku, S.B.; Lee, K.; Lee, H.M. High-density neural recording system design. Biomed. Eng. Lett. 2022, 12, 251–261. [Google Scholar] [CrossRef]

- Dutta, B.; Andrei, A.; Harris, T.D.; Lopez, C.M.; O’Callahan, J.; Putzeys, J.; Raducanu, B.C.; Severi, S.; Stavisky, S.D.; Trautmann, E.M.; et al. The Neuropixels probe: A CMOS based integrated microsystems platform for neuroscience and brain-computer interfaces. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 10.1.1–10.1.4. [Google Scholar]

- Qian, C.; Parramon, J.; Sanchez-Sinencio, E. A Micropower Low-Noise Neural Recording Front-End Circuit for Epileptic Seizure Detection. IEEE J. Solid-State Circuits 2011, 46, 1392–1405. [Google Scholar] [CrossRef]

- Chang, S.-I.; AlAshmouny, K.; McCormick, M.; Chen, Y.-C.; Yoon, E. BioBolt: A minimally-invasive neural interface for wireless epidural recording by intra-skin communication. In Proceedings of the 2011 Symposium on VLSI Circuits—Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011; pp. 146–147. [Google Scholar]

- Ng, K.A.; Xu, Y.P. A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs with CMFB Through Supply Rails. IEEE J. Solid-State Circuits 2016, 51, 724–737. [Google Scholar]

- Luo, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. IEEE J. Solid-State Circuits 2019, 54, 2255–2265. [Google Scholar] [CrossRef]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Nemirovsky, Y.; Brouk, I.; Jakobson, C.G. 1/f noise in CMOS transistors for analog applications. IEEE Trans. Electron. Devices 2001, 48, 921–927. [Google Scholar] [CrossRef]

- Hall, D.A.; Makinwa, K.A.A.; Jang, T. Quantifying Biomedical Amplifier Efficiency: The noise efficiency factor. IEEE Solid-State Circuits Mag. 2023, 15, 28–33. [Google Scholar] [CrossRef]

- Zhang, J.; Zhang, H.; Sun, Q.; Zhang, R. A Low-Noise, Low-Power Amplifier with Current-Reused OTA for ECG Recordings. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 700–708. [Google Scholar] [CrossRef]

- Shen, L.; Lu, N.; Sun, N. A 1V 0.25μW inverter-stacking amplifier with 1.07 noise efficiency factor. IEEE J. Solid-State Circuits 2018, 53, 896–905. [Google Scholar] [CrossRef]

- Tang, T.; Goh, W.L.; Yao, L.; Cheong, J.H.; Gao, Y. An Integrated Multi-Channel Biopotential Recording Analog Front-End IC with Area-Efficient Driven-Right-Leg Circuit. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 297–304. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Marković, D. 5.5 A 2µW 40mVpp linear-input-range chopper- stabilized bio-signal amplifier with boosted input impedance of 300MΩ and electrode-offset filtering. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 96–97. [Google Scholar]

- Chandrakumar, H.; Markovic, D. 27.1 A 2.8µW 80mVpp-linear-input-range 1.6GΩ-input impedance bio-signal chopper amplifier tolerant to common-mode interference up to 650mVpp. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 448–449. [Google Scholar]

- Ha, U.; Yoo, H.-J. An EEG-NIRS ear-module SoC for wearable drowsiness monitoring system. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 193–196. [Google Scholar]

- Lim, J.; Lee, J.; Moon, E.; Barrow, M.; Atzeni, G.; Letner, J.G.; Costello, J.T.; Nason, S.R.; Patel, P.R.; Sun, Y.; et al. A Light-Tolerant Wireless Neural Recording IC for Motor Prediction with Near-Infrared-Based Power and Data Telemetry. IEEE J. Solid-State Circuits 2022, 57, 1061–1074. [Google Scholar] [CrossRef] [PubMed]

- Pérez-Prieto, N.; Rodríguez-Vázquez, Á.; Álvarez-Dolado, M.; Delgado-Restituto, M. A 32-Channel Time-Multiplexed Artifact-Aware Neural Recording System. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 960–977. [Google Scholar] [CrossRef]

- Zhu, L.; Zhou, Z.; Wang, W.; Xie, S.; Meng, Q.; Wang, Z. A High CMRR Differential Difference Amplifier Employing Combined Input Pairs for Neural Signal Recordings. IEEE Trans. Biomed. Circuits Syst. 2024, 18, 100–110. [Google Scholar] [CrossRef]

- Sporer, M.; Reich, S.; Kauffman, J.G.; Ortmanns, M. A Direct Digitizing Chopped Neural Recorder Using a Body-Induced Offset Based DC Servo Loop. IEEE Trans. Biomed. Circuits Syst. 2022, 16, 409–418. [Google Scholar] [CrossRef] [PubMed]

- Koo, N.; Cho, S. A 24.8-μW Biopotential Amplifier Tolerant to 15-VPP Common-Mode Interference for Two-Electrode ECG Recording in 180-nm CMOS. IEEE J. Solid-State Circuits 2021, 56, 591–600. [Google Scholar] [CrossRef]

- Zamani, M.; Rezaeiyan, Y.; Huynh, H.A.; Ronchini, M.; Farkhani, H.; Moradi, F. A 2.3-μW Capacitively Coupled Chopper-Stabilized Neural Amplifier with Input Impedance of 6.7 GΩ. IEEE Solid-State Circuits Lett. 2021, 4, 133–136. [Google Scholar] [CrossRef]

- Mondal, S.; Hall, D.A. A 13.9-nA ECG Amplifier Achieving 0.86/0.99 NEF/PEF Using AC-Coupled OTA-Stacking. IEEE J. Solid-State Circuits 2020, 55, 414–425. [Google Scholar] [CrossRef]

- Denison, T.; Consoer, K.; Santa, W.; Avestruz, A.-T.; Cooley, J.; Kelly, A. A 2μW 100nV/rtHz Chopper-Stabilized Instrumentation Amplifier for Chronic Measurement of Neural Field Potentials. IEEE J. Solid-State Circuits 2007, 42, 2934–2945. [Google Scholar] [CrossRef]

- Lopez, C.M.; Andrei, A.; Mitra, S.; Welkenhuysen, M.; Eberle, W.; Bartic, C.; Puers, R.; Yazicioglu, R.F.; Gielen, G.G. An Implantable 455-Active-Electrode 52-Channel CMOS Neural Probe. IEEE J. Solid-State Circuits 2014, 49, 248–261. [Google Scholar] [CrossRef]

- Lopez, C.M.; Mitra, S.; Putzeys, J.; Raducanu, B.; Ballini, M.; Andrei, A.; Severi, S.; Welkenhuysen, M.; Van Hoof, C.; Musa, S.; et al. 22.7 A 966-electrode neural probe with 384 configurable channels in 0.13µm SOI CMOS. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 392–393. [Google Scholar]

- Wu, H.; Chen, J.; Liu, X.; Zou, W.; Yang, J.; Sawan, M. An Energy-Efficient Small-Area Configurable Analog Front-End Interface for Diverse Biosignals Recording. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 818–830. [Google Scholar] [CrossRef]

| Devices | ID (μA) | gm (μs) | gm/ID | Operating Region |

|---|---|---|---|---|

| M1, M2 | 1.6 | 41.95 | 26.2 | Sub-threshold |

| M3, M4 | 1.6 | 43.12 | 27 | Sub-threshold |

| M5, M7, M6, M8 | 0.16 | 2.16 | 13.5 | Strong inversion |

| M9, M10 | 0.16 | 3.89 | 24.3 | Sub-threshold |

| M11, M12 | 0.16 | 4.12 | 25.7 | Sub-threshold |

| M13, M14 | 0.16 | 1.2 | 7.5 | Strong inversion |

| M15, M16 | 1.44 | 8.53 | 5.9 | Strong inversion |

| [13] | [17] | [19] | [22] | [28] | [31] | [33] | [34] | [35] | [36] | This Work | |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Technology (μm) | 0.6 | 1.5 | 0.35 | 0.18 | 0.18 | 0.18 | 0.8 | 0.18 | 0.13 | 0.04 | 0.18 |

| CMRR (dB) | >66 | >83 | >65 | 110 | >103 | 75 | >100 | 60 | 60 | 107 | 66 |

| PSRR (dB) | >80 | >85 | >70 | - | 84 | 68 | - | 76 | 70 | >70 | 84 |

| Input-referred noise (μVrms) | 3.07 (0.5 Hz–30 kHz) | 2.2 | 2.05 (0.1 Hz–10 kHz) | 4.2 (1 Hz–10 kHz) | 7.5 | 2.1 (1 Hz–200 Hz) | 0.98 (0.05 Hz–100 Hz) | 3.2 | 6.36 | 1.7 (1 Hz–260 Hz) | 3.1 (1 Hz–6.1 kHz) |

| Bandwidth (Hz) | 0.36–1300 | 0.025–7200 | 0.2–200 | HP: 0.15/0.26 LP: 9400/12,100 | 10–10,000 | 0.9–900 | 0.05–180 | 0.5–6000 | 0.3–10,000 | HP: 0.2–550 LP: 260–3800 | 0.54–6100 |

| Gain (dB) | 39.4 | 39.5 | 39.8 | 60/54 | 46 | 80 | 50.5/41 | 29.5–72 | 68 | 37 | 46/40 |

| Current (μA) & Power (μW) | 0.872 & 2.4 | 16 & 80 | 0.16 & 0.32 | 1 & 1 | 2 &3.6 | 2.3 & 2.3 | 1 & 2 | 3.9 & 7.02 | 40.9 & 49 | 2.06 & 2.47 | 3.8 & 6.84 |

| NEF | 3.09 | 4 | 2.26 | 1.7 | 6.27 | 8.6 | 4.6 | 3.08 | 3.8 | 4.1 | 2.97 |

| PEF | 26.7 | 80 | 10.2 | 2.89 | 20.3 | 8.6 | 38.1 | 17.13 | 17.33 | 20.17 | 10.17 |

| Area (mm²) | 0.13 | 0.16 | 0.18 | 0.09 | 0.07 | 0.051 | 0.8 | 0.19 | 0.12 | 0.048 | 0.082 |

| Topology | CCIA | CCIA | CCIA | CCIA | DDA | Chopper | Chopper | CCIA | CCIA | Chopper | CCIA |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Wang, X.; Shu, G.; Yin, M.; Huang, S.; Yin, M. Power-to-Noise Optimization in the Design of Neural Recording Amplifier Based on Current Scaling, Source Degeneration Resistor, and Current Reuse. Biosensors 2024, 14, 111. https://doi.org/10.3390/bios14020111

Wang Z, Wang X, Shu G, Yin M, Huang S, Yin M. Power-to-Noise Optimization in the Design of Neural Recording Amplifier Based on Current Scaling, Source Degeneration Resistor, and Current Reuse. Biosensors. 2024; 14(2):111. https://doi.org/10.3390/bios14020111

Chicago/Turabian StyleWang, Zhen, Xiao Wang, Guijun Shu, Meng Yin, Shoushuang Huang, and Ming Yin. 2024. "Power-to-Noise Optimization in the Design of Neural Recording Amplifier Based on Current Scaling, Source Degeneration Resistor, and Current Reuse" Biosensors 14, no. 2: 111. https://doi.org/10.3390/bios14020111

APA StyleWang, Z., Wang, X., Shu, G., Yin, M., Huang, S., & Yin, M. (2024). Power-to-Noise Optimization in the Design of Neural Recording Amplifier Based on Current Scaling, Source Degeneration Resistor, and Current Reuse. Biosensors, 14(2), 111. https://doi.org/10.3390/bios14020111