High-Performance Multilevel and Ambipolar Nonvolatile Organic Transistor Memory Using Small-Molecule SFDBAO and PS as Charge Trapping Elements

Abstract

1. Introduction

2. Experimental Section

3. Results and Discussion

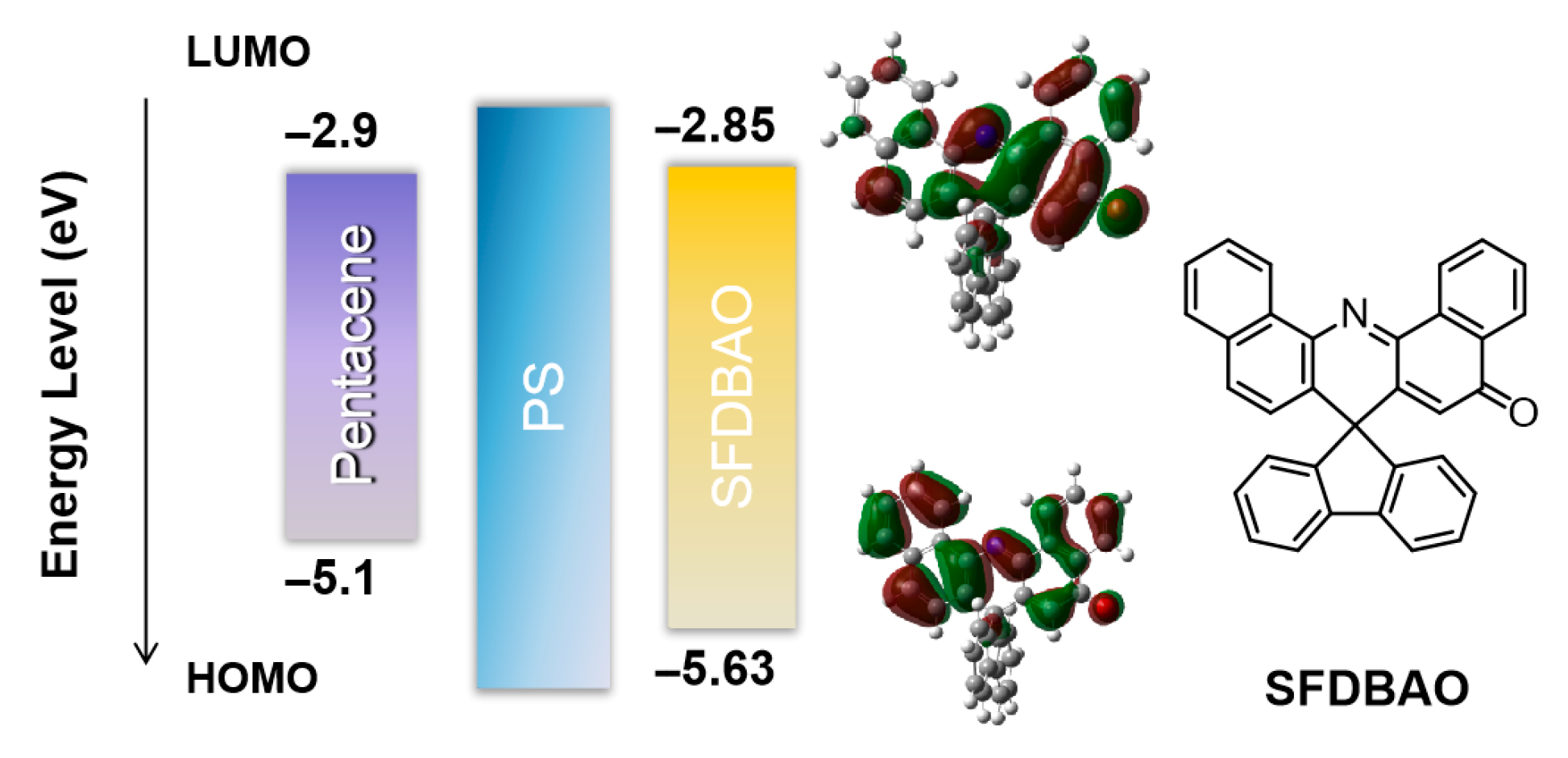

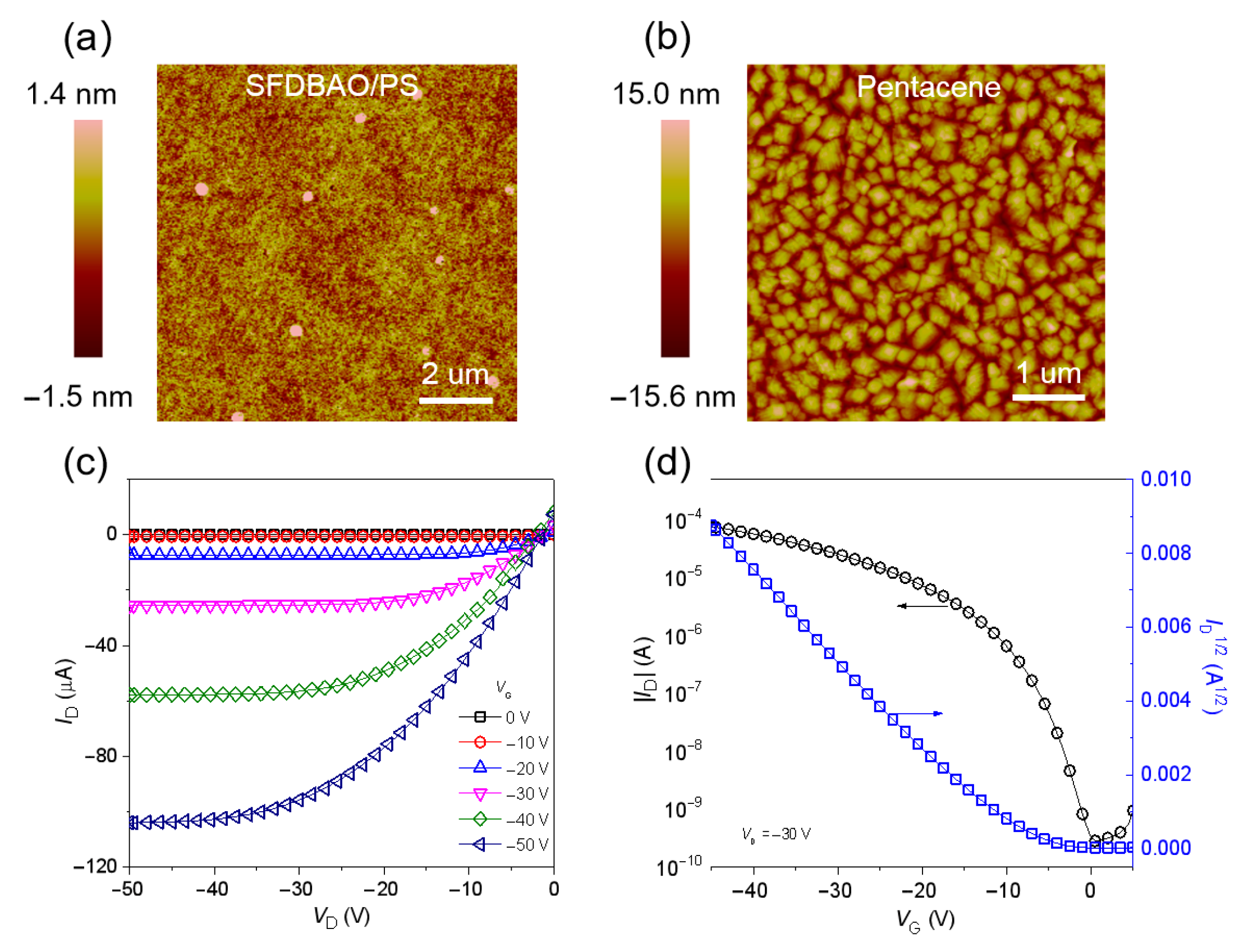

3.1. Memory Devices Based on SFDBAO Molecule Thin Films

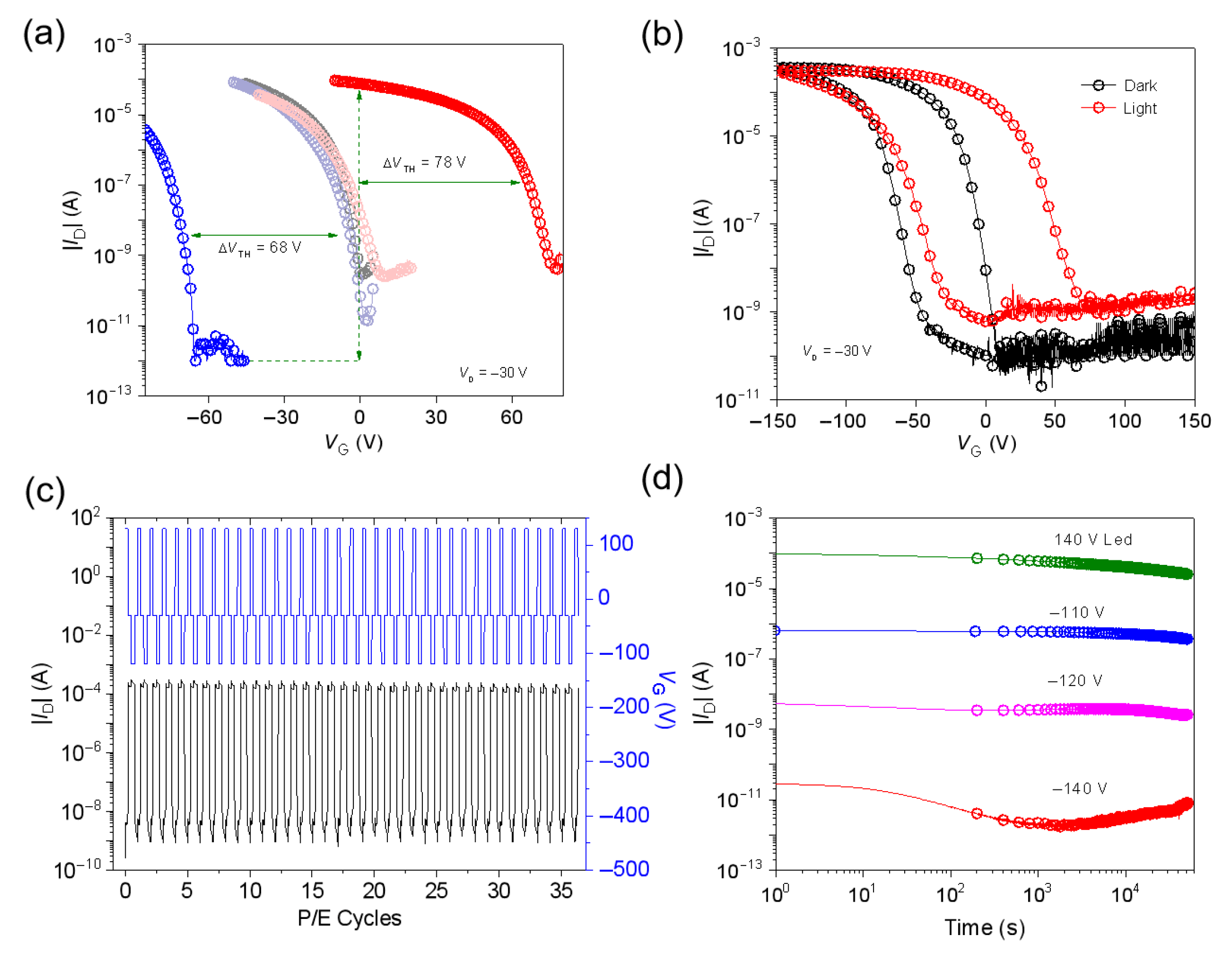

3.2. Memory Devices Based on SFDBAO/PS Composite Thin Films

3.3. Memory Mechanism

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ouyang, J.; Chu, C.W.; Szmanda, C.R.; Ma, L.; Yang, Y. Programmable polymer thin film and non-volatile memory device. Nat. Mater. 2004, 3, 918. [Google Scholar] [CrossRef] [PubMed]

- Ling, Q.; Liaw, D.; Zhu, C.; Chan, D.; Kang, E.; Neoh, K. Polymer electronic memories: Materials, devices and mechanisms. Prog. Polym. Sci. 2008, 33, 917. [Google Scholar] [CrossRef]

- Heremans, P.; Gelinck, G.; Muller, R.; Baeg, K.; Kim, D.; Noh, Y. Polymer and organic nonvolatile memory devices. Chem. Mater. 2011, 23, 341. [Google Scholar] [CrossRef]

- Sekitani, T.; Yokota, T.; Zschieschang, U.; Klauk, H.; Bauer, S.; Takeuchi, K.; Takamiya, M.; Sakurai, T.; Someya, T. Organic nonvolatile memory transistors for flexible sensor arrays. Science 2009, 326, 1516. [Google Scholar] [CrossRef]

- Liu, C.; Yin, Z.; Liu, Y.; Zheng, Q. Flexible polyelectrolyte hybrid dielectrics for multilevel nonvolatile low-voltage organic transistor memories. Chem. Eng. J. 2025, 504, 158625. [Google Scholar] [CrossRef]

- Shih, C.; Chiu, Y.; Lee, W.; Chen, J.; Chen, W. Conjugated polymer nanoparticles as nano floating gate electrets for high performance nonvolatile organic transistor memory devices. Adv. Funct. Mater. 2015, 25, 1511. [Google Scholar] [CrossRef]

- Chen, Z.; Chen, S.; Jiang, T.; Chen, S.; Jia, R.; Xiao, Y.; Pan, J.; Jie, J.; Zhang, X. A floating-gate field-effect transistor memory device based on organic crystals with a built-in tunneling dielectric by a one-step growth strategy. Nanoscale 2024, 16, 3721. [Google Scholar] [CrossRef] [PubMed]

- Wang, H.; Guo, H.; Guzman, R.; JiaziLa, N.; Wu, K.; Wang, A.; Liu, X.; Liu, L.; Wu, L.; Chen, J.; et al. Ultrafast Non-Volatile Floating-Gate Memory Based on All-2D Materials. Adv. Mater. 2024, 36, 2311652. [Google Scholar] [CrossRef]

- Wang, W.; Shi, J.; Ma, D. Organic thin-film transistor memory with nanoparticle floating gate. IEEE Trans. Electron Devices 2009, 56, 1036. [Google Scholar] [CrossRef]

- Lee, J. Progress in non-volatile memory devices based on nanostructured materials and nanofabrication. J. Mater. Chem. 2011, 21, 14097. [Google Scholar] [CrossRef]

- Chen, H.; Zhou, Y.; Han, S.T. Recent advances in metal nanoparticle-based floating gate memory. Nano Select. 2021, 2, 1245. [Google Scholar] [CrossRef]

- Wang, Q.; Tang, X.; Liang, Z.; Liu, J.; Wang, S.; Bu, L.; Lu, G. Non-volatile optoelectronic memory with “self-refined” n-type conjugated polymer floating gate for multistate storage. ACS Appl. Mater. Interfaces 2025, 17, 17153–17163. [Google Scholar] [CrossRef]

- Chiang, Y.; Hung, C.; Lin, Y.; Chiu, Y.; Isono, T.; Satoh, T.; Chen, W. High-performance nonvolatile organic photonic transistor memory devices using conjugated rod–coil materials as a floating gate. Adv. Mater. 2020, 32, 2002638. [Google Scholar] [CrossRef] [PubMed]

- Ercan, E.; Chen, J.; Shih, C.; Chueh, C.; Chen, W. Influence of polymeric electrets on the performance of derived hybrid perovskite-based photo-memory devices. Nanoscale 2018, 10, 18869–18877. [Google Scholar] [CrossRef]

- Niu, W.; Zou, X.; Tang, L.; Bu, T.; Zhang, S.; Jiang, B.; Dang, M.; Hong, X.; Ma, C.; He, P.; et al. Van der Waals gap enabled robust retention of MoS2 floating-gate memory for logic-in-memory operations. Adv. Funct. Mater. 2024, 35, 2422120. [Google Scholar] [CrossRef]

- Kim, C.; Song, J.M.; Lee, J.S.; Lee, M.J. All-solution-processed nonvolatile flexible nano-floating gate memory devices. Nanotechnology 2013, 25, 014016. [Google Scholar] [CrossRef]

- Xu, T.; Fan, S.; Cao, M.; Liu, T.; Su, J. Flexible organic field-effect transistor nonvolatile memory enabling bipolar charge storage by small-molecule floating gate. Appl. Phys. Lett. 2022, 120, 073301. [Google Scholar] [CrossRef]

- Gu, X.; Qin, Y.; Sun, S.; Guo, L.; Zhu, X.; Sun, X. High-performance floating-gate organic phototransistors based on n-type core-expanded naphthalene diimides. Chin. Chem. Lett. 2023, 34, 107306. [Google Scholar] [CrossRef]

- Yamamoto, M.; Azuma, Y.; Sakamoto, M.; Teranishi, T.; Ishii, H.; Majima, Y.; Noguchi, Y. Molecular floating-gate single-electron transistor. Sci. Rep. 2017, 7, 1589. [Google Scholar] [CrossRef]

- Zhu, H.; Li, Q. Novel Molecular Non-Volatile Memory: Application of Redox-Active Molecules. Appl. Sci. 2016, 6, 7. [Google Scholar] [CrossRef]

- Xu, T.; Guo, S.; Xu, M.; Li, S.; Xie, W.; Wang, W. Organic transistor nonvolatile memory with an integrated molecular floating-gate/tunneling layer. Appl. Phys. Lett. 2018, 113, 243301. [Google Scholar] [CrossRef]

- Ji, J.; Liu, J.; Wang, Y.; Zhang, F.; Zhao, M.; Yan, S.; Guo, X.; Zhang, W.; Sang, S.; Chai, X.; et al. Liquid-solid heterojunction constructing bio-sensory floating-gate OECTs. Nano Energy 2024, 128, 109962. [Google Scholar] [CrossRef]

- Zhuang, W.; Jang, H.; Sui, X.; Ryu, B.; Wang, Y.; Pu, H.; Chen, J. Enhancing Electrochemical Sensing through Molecular Engineering of Reduced Graphene Oxide–Solution Interfaces and Remote Floating-Gate FET Analysis. ACS Appl. Mater. Interfaces 2024, 16, 27961. [Google Scholar] [CrossRef] [PubMed]

- Jeon, S.; Sun, C.; Yu, S.; Kwon, S.; Chung, D.; Jeong, Y.; Kim, Y. Synthesis of Cyclopentadithiophene–Diketopyrrolopyrrole Donor–Acceptor Copolymers for High-Performance Nonvolatile Floating-Gate Memory Transistors with Long Retention Time. ACS Appl. Mater. Interfaces 2020, 12, 2743. [Google Scholar] [CrossRef]

- Wu, Z.; Sun, W.; Tian, H.; Yu, Z.; Guo, R.; Shao, X.; Zhang, H. 9,10-imide-pyrene-fused pyrazaacenes (IPPA) as N-type doping materials for high-performance nonvolatile organic field effect transistor memory devices. Adv. Electron. Mater. 2019, 5, 1800598. [Google Scholar] [CrossRef]

- Liu, D.; Zhang, Y.; Li, X.; Xiao, Q.; Sun, W.; Shao, X.; Zhang, H. Nonvolatile organic field-effect transistor memory from pyrene-fused azaindacene regioisomers. J. Mater. Chem. C 2021, 9, 6560. [Google Scholar] [CrossRef]

- Zhang, C.; Ning, J.; Wang, B.; Wang, D.; Zhang, J.; Hao, Y. A Dual-Mode Programing Nonvolatile Floating-Gate Memory with Convertible Ohmic and Schottky Contacts. Adv. Electron. Mater. 2024, 10, 2300503. [Google Scholar] [CrossRef]

- Liu, Y.; Shao, Z.; Li, Y.; Liu, J.; Jin, L.; Wang, Y.; Li, W.; Xie, L.; Ling, H. Solution-Processed Sterically Hindered Donor–Acceptor Small Molecules as Molecular Floating-Gates for High-Efficiency Ambipolar Charge Trapping Memory. Adv. Electron. Mater. 2025, 2500095. [Google Scholar] [CrossRef]

- Wei, Y.; Tang, L.; Zhong, C.; Xie, X.; Sun, P.; Sun, C.; Zhang, H.; Zheng, X.; Wang, X.; Xie, L.J. Photooxygenations and Self-Sensitizations of Naphthylamines: Efficient Access to Iminoquinones. J. Chem. 2018, 2018, 9180671. [Google Scholar] [CrossRef]

- Kim, C.; Quinn, J.R.; Facchetti, A.; Marks, T.J. Pentacene transistors fabricated on photocurable polymer gate dielectrics: Tuning surface viscoelasticity and device response. Adv. Mater. 2010, 22, 342. [Google Scholar] [CrossRef]

- Wang, J.; Wang, X.; Xu, W.J.; Xie, L.H.; Liu, Y.Y.; Yi, M.D.; Huang, W. Detection of trapped charges in the blend films of polystyrene/SFDBAO electrets by electrostatic and Kelvin probe force microscopy. Phys. Chem. Chem. Phys. 2016, 18, 9412. [Google Scholar] [CrossRef] [PubMed]

- Steudel, S.; De Vusser, S.; De Jonge, S.; Janssen, D.; Verlaak, S.; Genoe, J.; Heremans, P. Influence of the dielectric roughness on the performance of pentacene transistors. Appl. Phys. Lett. 2004, 85, 4400. [Google Scholar] [CrossRef]

- Xiang, L.; Ying, J.; Han, J.; Zhang, L.; Wang, W. High reliable and stable organic field-effect transistor nonvolatile memory with a poly (4-vinyl phenol) charge trapping layer based on a pn-heterojunction active layer. Appl. Phys. Lett. 2016, 108, 173301. [Google Scholar] [CrossRef]

- Qian, Y.; Li, J.; Li, W.; Song, Z.; Yu, H.; Feng, Z.; Shi, W.; Huang, W.; Yi, M. High-performance multilevel nonvolatile organic field-effect transistor memory based on multilayer organic semiconductor heterostructures. J. Mater. Chem. C 2024, 12, 16092. [Google Scholar] [CrossRef]

- Wu, W.; Zhang, H.; Wang, Y.; Ye, S.; Guo, Y.; Di, C.; Yu, G.; Zhu, D.; Liu, Y. High-performance organic transistor memory elements with steep flanks of hysteresis. Adv. Funct. Mater. 2008, 18, 2593. [Google Scholar] [CrossRef]

| Materials | Mobility [cm2 V−1 s−1] | Negative Window [V] | Positive Window [V] | ION/IOFF |

|---|---|---|---|---|

| 5% SFDBAO/PS | 0.50 | 47 | 78 | 6.12 × 105 |

| 10% SFDBAO/PS | 0.53 | 68 | 78 | 2.00 × 105 |

| 20% SFDBAO/PS | 0.38 | 51 | 72 | 7.16 × 104 |

| 25% SFDBAO/PS | 0.44 | 27 | 49 | 1.56 × 105 |

| 10% C60/PS | 0.69 | 43 | 40 | 3.54 × 105 |

| 10% Alq3/PS | 0.07 | 33 | 60 | 2.67 × 104 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jin, L.; Xu, W.; Qian, Y.; Ji, T.; Wu, K.; Huang, L.; Chen, F.; Huang, N.; Xing, S.; Shao, Z.; et al. High-Performance Multilevel and Ambipolar Nonvolatile Organic Transistor Memory Using Small-Molecule SFDBAO and PS as Charge Trapping Elements. Nanomaterials 2025, 15, 1072. https://doi.org/10.3390/nano15141072

Jin L, Xu W, Qian Y, Ji T, Wu K, Huang L, Chen F, Huang N, Xing S, Shao Z, et al. High-Performance Multilevel and Ambipolar Nonvolatile Organic Transistor Memory Using Small-Molecule SFDBAO and PS as Charge Trapping Elements. Nanomaterials. 2025; 15(14):1072. https://doi.org/10.3390/nano15141072

Chicago/Turabian StyleJin, Lingzhi, Wenjuan Xu, Yangzhou Qian, Tao Ji, Kefan Wu, Liang Huang, Feng Chen, Nanchang Huang, Shu Xing, Zhen Shao, and et al. 2025. "High-Performance Multilevel and Ambipolar Nonvolatile Organic Transistor Memory Using Small-Molecule SFDBAO and PS as Charge Trapping Elements" Nanomaterials 15, no. 14: 1072. https://doi.org/10.3390/nano15141072

APA StyleJin, L., Xu, W., Qian, Y., Ji, T., Wu, K., Huang, L., Chen, F., Huang, N., Xing, S., Shao, Z., Li, W., Liu, Y., & Xie, L. (2025). High-Performance Multilevel and Ambipolar Nonvolatile Organic Transistor Memory Using Small-Molecule SFDBAO and PS as Charge Trapping Elements. Nanomaterials, 15(14), 1072. https://doi.org/10.3390/nano15141072