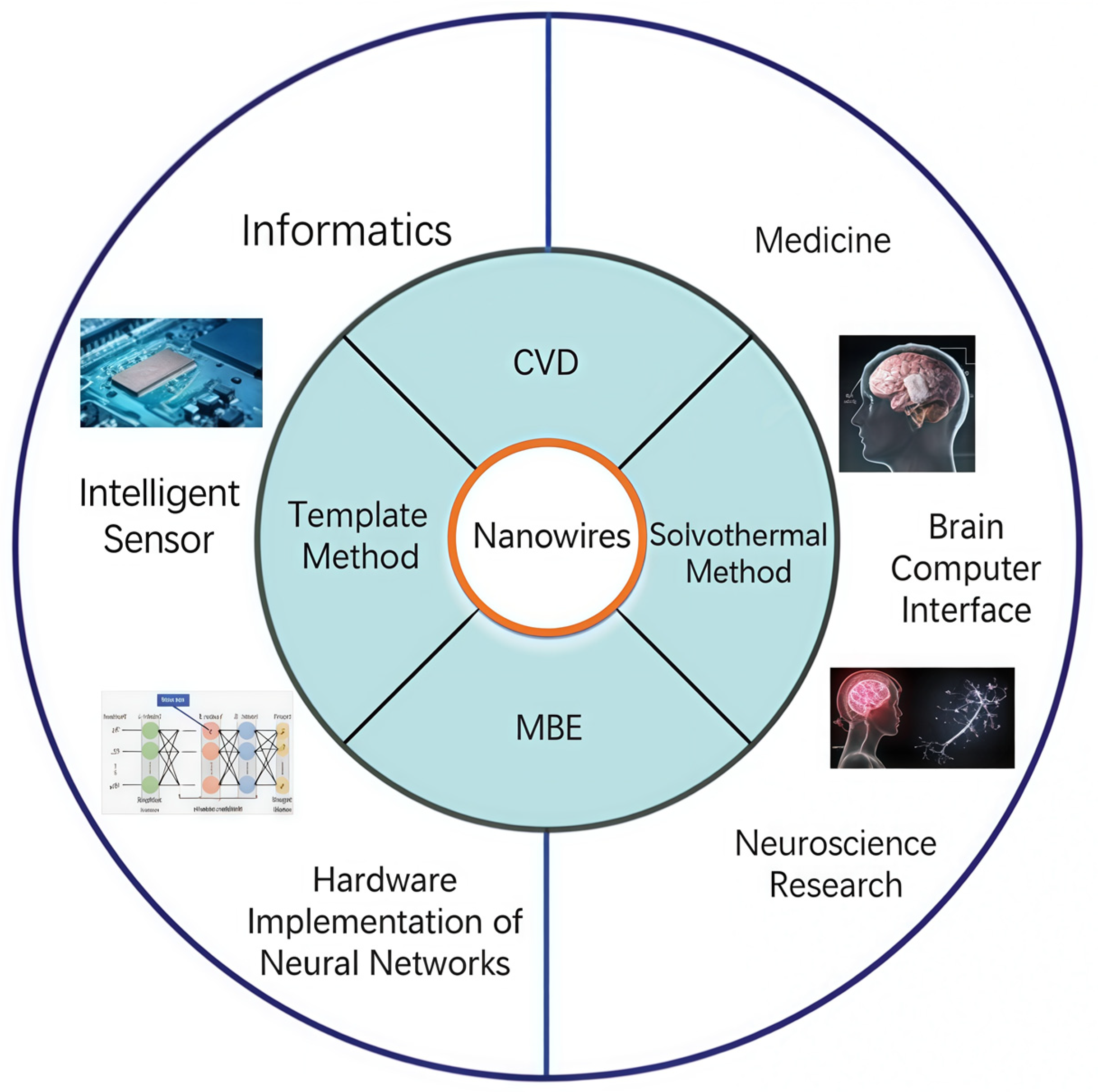

A Review of Nanowire Devices Applied in Simulating Neuromorphic Computing

Abstract

:1. Introduction

2. Nanowire Fabrication

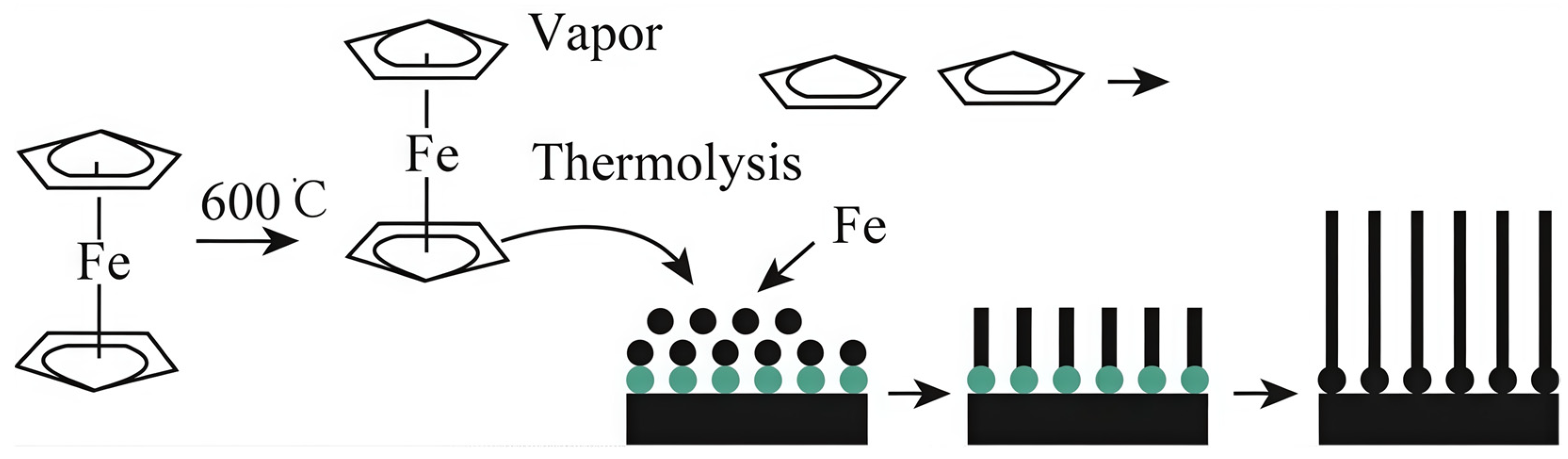

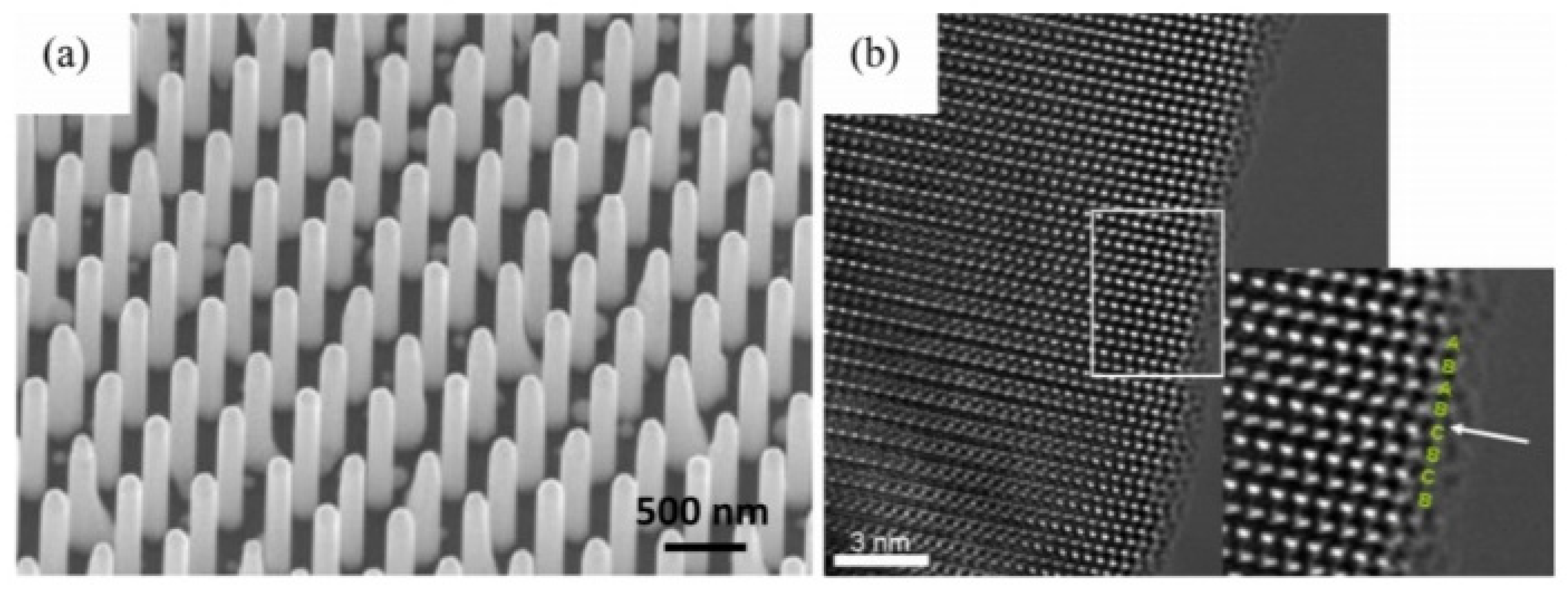

2.1. Chemical Vapor Deposition

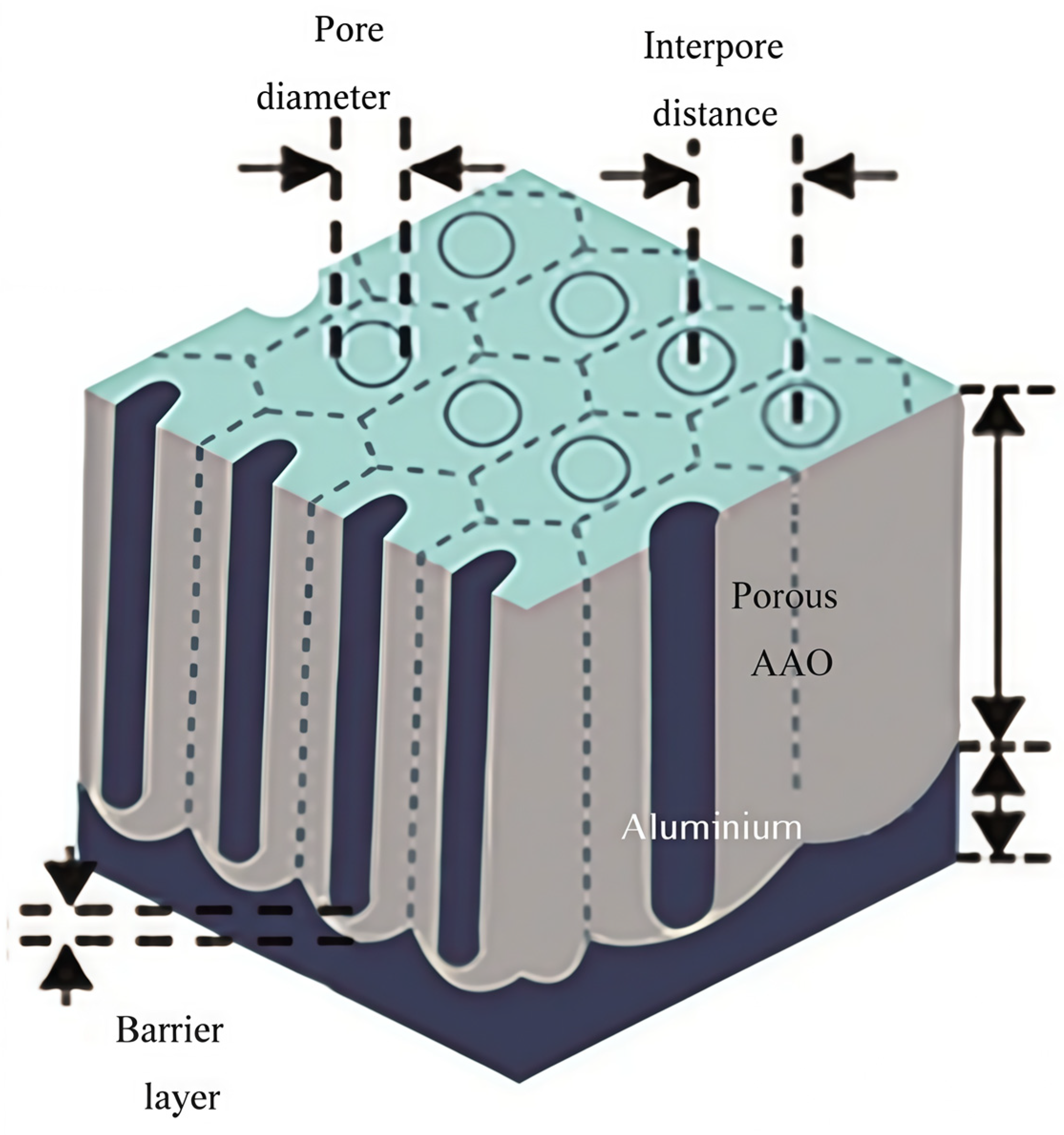

2.2. Template Method

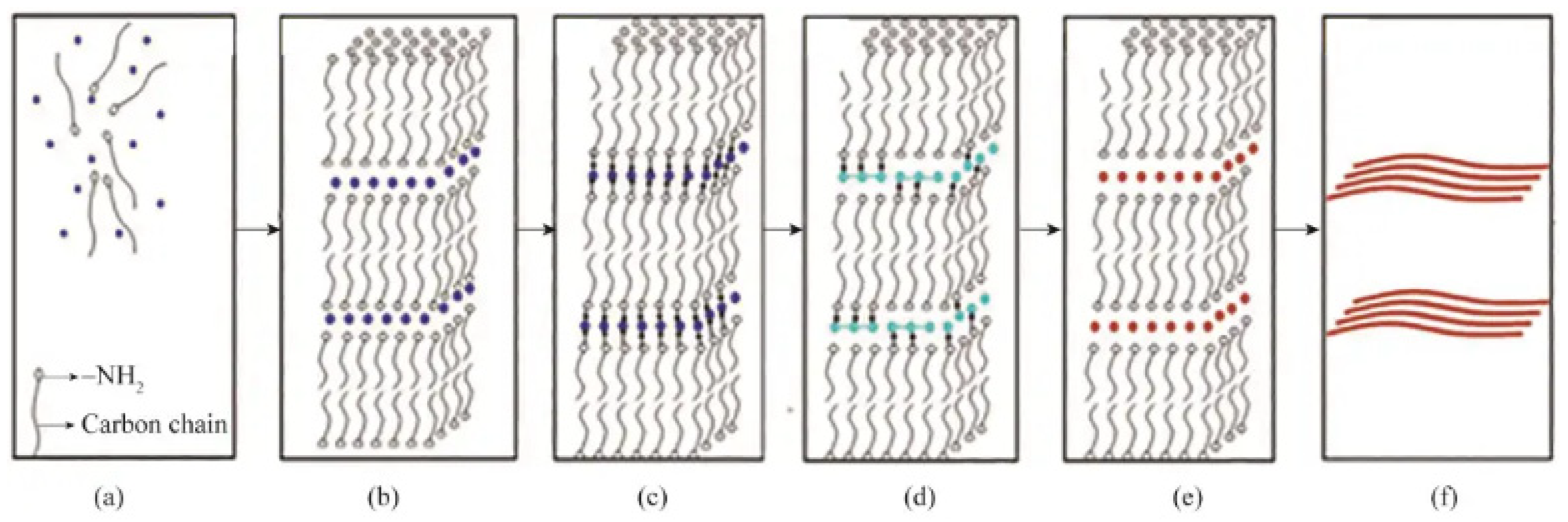

2.3. Solvothermal Method

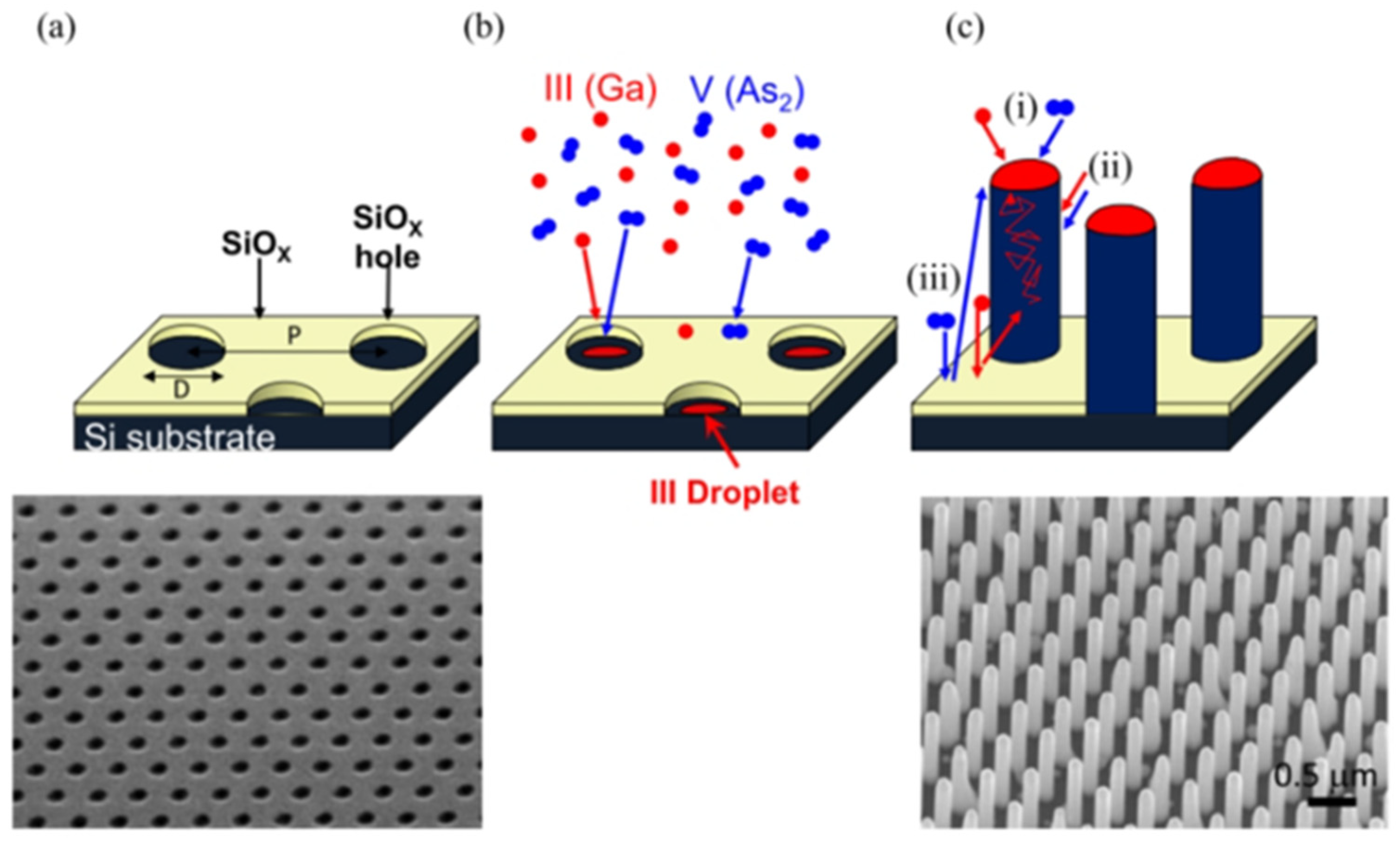

2.4. Molecular Beam Epitaxy

3. Nanowire Devices for Simulating Brain-like Computing

3.1. The Role of Nanowire Devices in Brain-like Computing

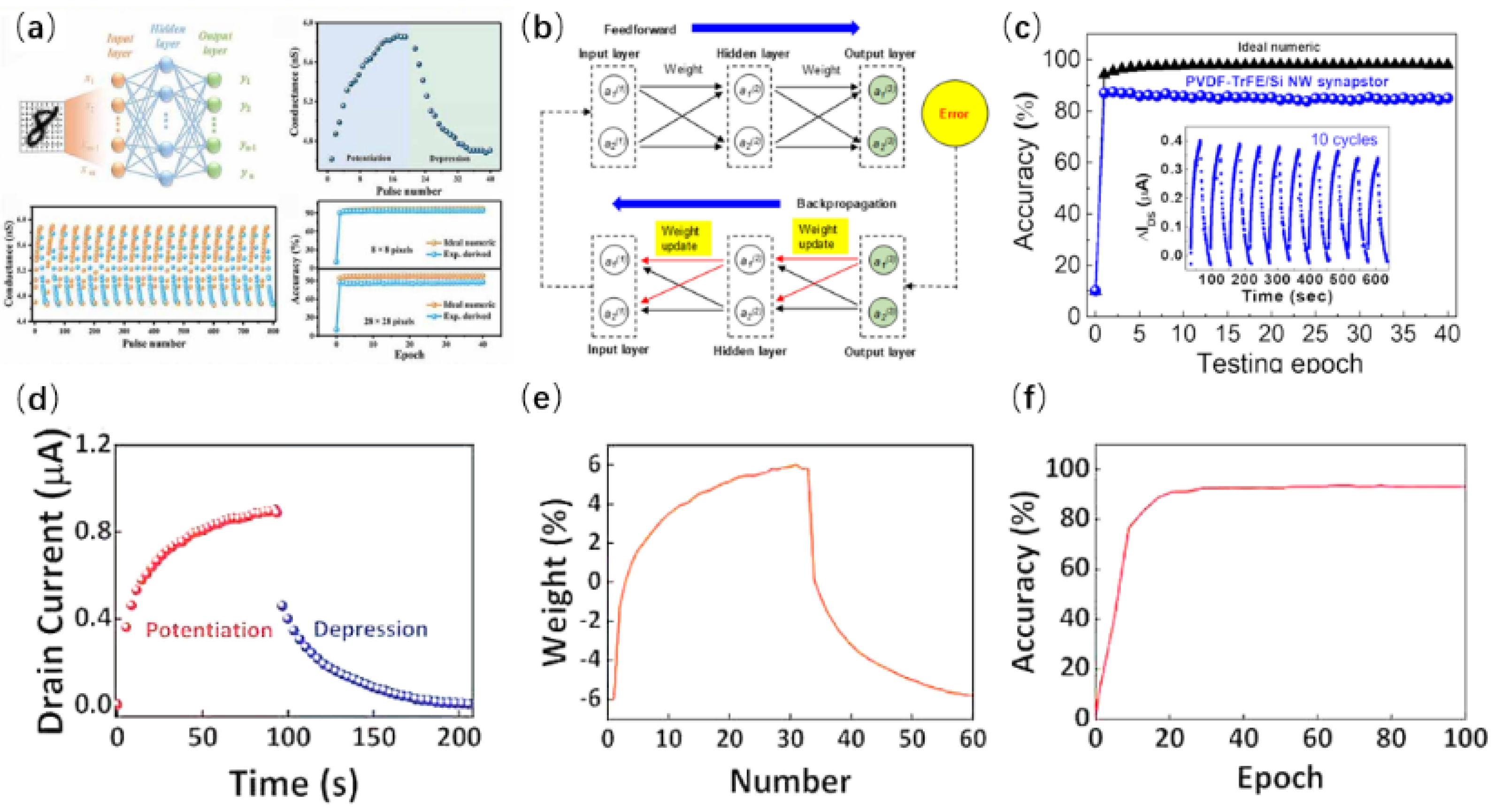

3.1.1. Simulating Synaptic Characteristics

3.1.2. Simulating Neuronal Activity

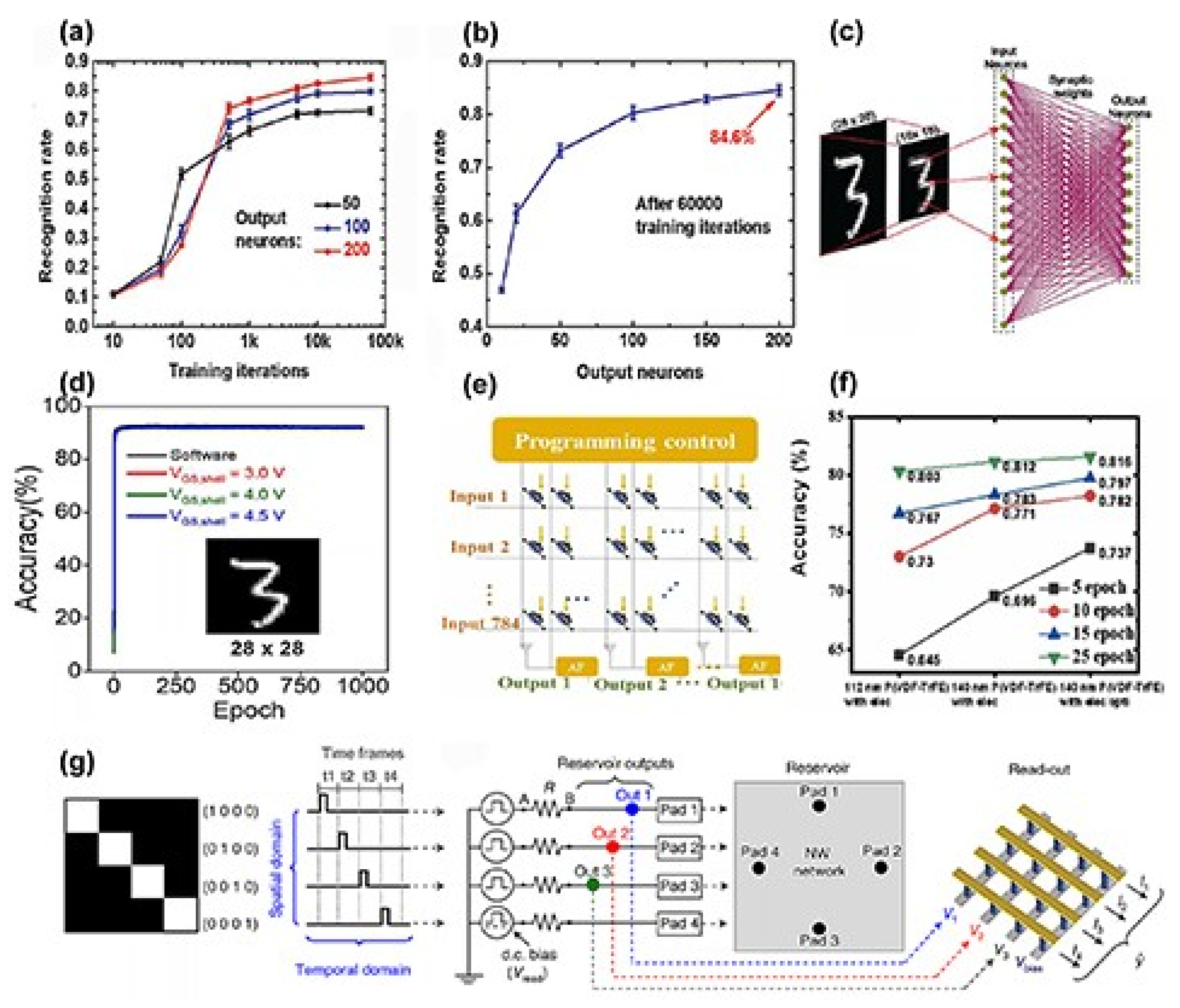

3.1.3. Nanowire Devices for Neuromorphic Computing

3.2. Nanowire Devices Simulate Brain-like Computing in Other Application Areas

3.2.1. The Application of Nanowire Devices in Brain-like Computing in the Field of Medicine

3.2.2. Application of Nanowire Devices in Informatics

4. Conclusions

Funding

Conflicts of Interest

References

- Wang, X.; Wang, R.; Shi, L.; Sun, J. Synthesis of metal/bimetal nanowires and their applications as flexible transparent electrodes. Small 2015, 11, 4737–4744. [Google Scholar] [CrossRef] [PubMed]

- Furber, S. Large-scale neuromorphic computing systems. J. Neural Eng. 2016, 13, 051001. [Google Scholar] [CrossRef] [PubMed]

- Schlatterer, K. Immune modulation by molecules of Staphylococcus aureus. Universität Tübingen: Tübingen, Germany, 2022. [Google Scholar]

- Hasler, J.; Marr, B. Finding a roadmap to achieve large neuromorphic hardware systems. Front. Neurosci. 2013, 7, 118. [Google Scholar] [CrossRef]

- Merces, L.; Ferro, L.M.M.; Nawaz, A.; Sonar, P. Advanced Neuromorphic Applications Enabled by Synaptic Ion-Gating Vertical Transistors. J Adv. Sci. 2024, 11, 2305611. [Google Scholar] [CrossRef]

- Xia, Q.; Yang, J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 2019, 18, 309–323. [Google Scholar] [CrossRef]

- Brandman, O.; Meyer, T. Feedback loops shape cellular signals in space and time. Science 2008, 322, 390–395. [Google Scholar] [CrossRef] [PubMed]

- Zhang, X.-Y.; Wang, Y.-L.; Lv, C.-L.; You, L.-X.; Li, H.; Wang, Z.; Xie, X.-M. Flux-to-voltage characteristic simulation of superconducting nanowire interference device. Chin. Phys. B 2020, 29, 098501. [Google Scholar] [CrossRef]

- Tsai, T.Y.-C.; Choi, Y.S.; Ma, W.; Pomerening, J.R.; Tang, C.; Ferrell, J., Jr. Robust, tunable biological oscillations from interlinked positive and negative feedback loops. Science 2008, 321, 126–129. [Google Scholar] [CrossRef]

- Ferrell, J.E., Jr. Feedback loops and reciprocal regulation: Recurring motifs in the systems biology of the cell cycle. Curr. Opin. Cell Biol. 2013, 25, 676–686. [Google Scholar] [CrossRef]

- Yang, R.; Huang, H.M.; Guo, X.J. Memristive synapses and neurons for bioinspired computing. Adv. Electron. Mater. 2019, 5, 1900287. [Google Scholar] [CrossRef]

- Sun, W.; Gao, B.; Chi, M.; Xia, Q.; Yang, J.J.; Qian, H.; Wu, H. Understanding memristive switching via in situ characterization and device modeling. Nat. Commun. 2019, 10, 3453. [Google Scholar] [CrossRef]

- Van De Burgt, Y.; Lubberman, E.; Fuller, E.J.; Keene, S.T.; Faria, G.C.; Agarwal, S.; Marinella, M.J.; Alec Talin, A.; Salleo, A.J.N. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 2017, 16, 414–418. [Google Scholar] [CrossRef]

- Stoliar, P.; Tranchant, J.; Corraze, B.; Janod, E.; Besland, M.P.; Tesler, F.; Rozenberg, M.; Cario, L. A leaky-integrate-and-fire neuron analog realized with a Mott insulator. Adv. Funct. Mater. 2017, 27, 1604740. [Google Scholar] [CrossRef]

- Mahowald, M.; Douglas, R.J.N. A silicon neuron. Nature 1991, 354, 515–518. [Google Scholar] [CrossRef] [PubMed]

- Indiveri, G.; Linares-Barranco, B.; Hamilton, T.; Van Schaik, A.; Etienne-Cummings, R.; Delbruck, T.; Liu, S.; Dudek, P.; Häfliger, P.; Renaud, S. Neuromorphic silicon neuron circuits Front. Neurosci 2011, 5, 1–23. [Google Scholar]

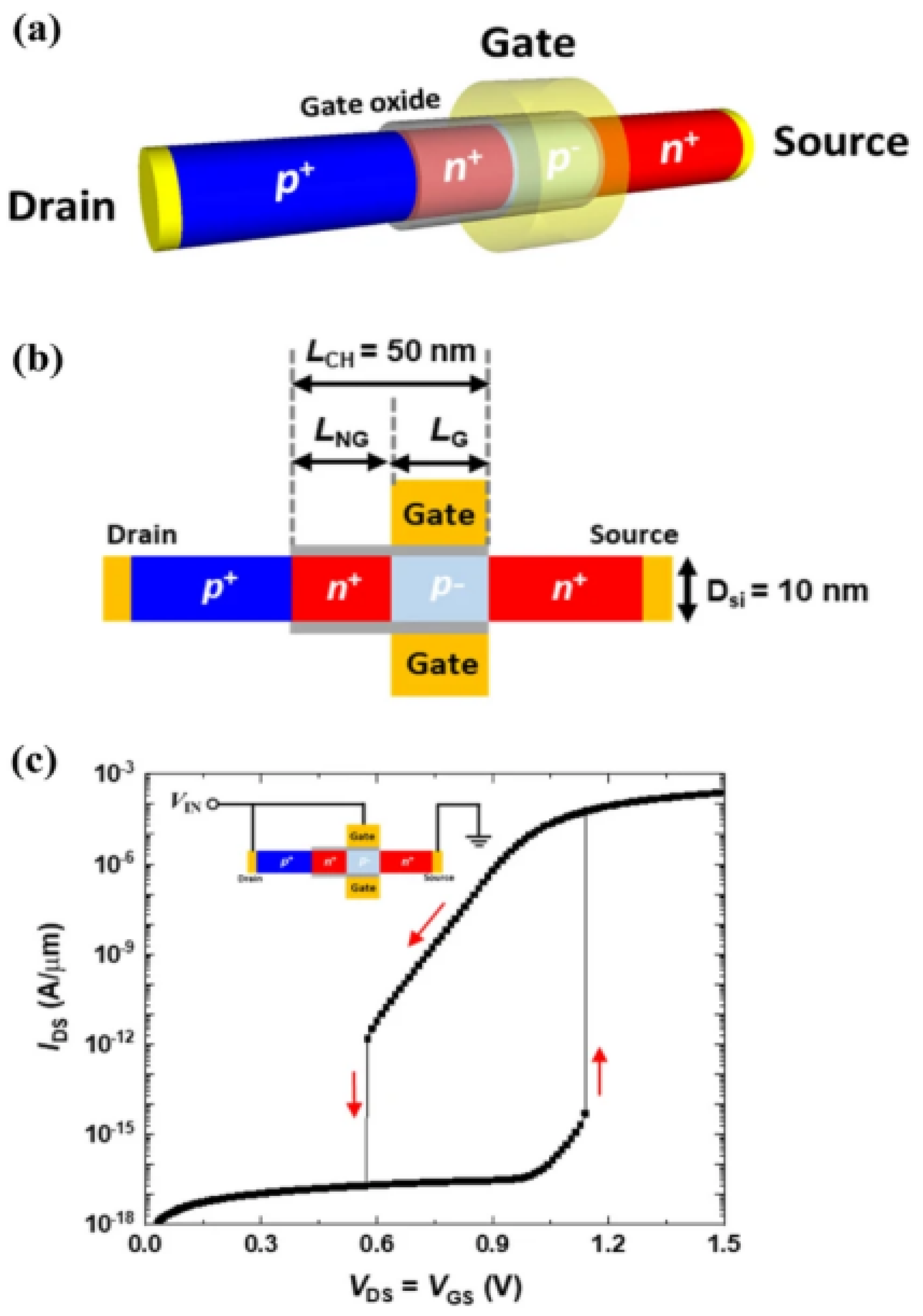

- Han, J.-K.; Seo, M.; Kim, W.-K.; Kim, M.-S.; Kim, S.-Y.; Kim, M.-S.; Yun, G.-J.; Lee, G.-B.; Yu, J.-M.; Choi, Y. Mimicry of excitatory and inhibitory artificial neuron with leaky integrate-and-fire function by a single MOSFET. IEEE Electron Device Lett. 2019, 41, 208–211. [Google Scholar] [CrossRef]

- Liu, Q.; Dai, X.; Zhang, T.; Shi, H.; Zhang, Y.; Wang, T. Preparation and applications in electronic materials of metallic nanowires. Huagong Xuebao/CIESC J. 2021, 72, 681–708. [Google Scholar]

- Zhou, L.; Zhang, R. A self-attention–based neural network for three-dimensional multivariate modeling and its skillful ENSO predictions. Sci. Adv. 2023, 9, eadf2827. [Google Scholar] [CrossRef]

- Oehler, F.; Gentile, P.; Baron, T.; Den Hertog, M.; Rouviere, J.; Ferret, P. The morphology of silicon nanowires grown in the presence of trimethylaluminium. Nanotechnology 2009, 20, 245602. [Google Scholar] [CrossRef]

- Kuncic, Z.; Nakayama, T. Neuromorphic nanowire networks: Principles, progress and future prospects for neuro-inspired information processing. Adv. Phys. X 2021, 6, 1894234. [Google Scholar] [CrossRef]

- Zhang, W.; Gao, B.; Tang, J.; Yao, P.; Yu, S.; Chang, M.-F.; Yoo, H.-J.; Qian, H.; Wu, H. Neuro-inspired computing chips. Nat. Electron. 2020, 3, 371–382. [Google Scholar] [CrossRef]

- Mehonic, A.; Sebastian, A.; Rajendran, B.; Simeone, O.; Vasilaki, E.; Kenyon, A. Memristors—From in-memory computing, deep learning acceleration, and spiking neural networks to the future of neuromorphic and bio-inspired computing. Adv. Intell. Syst. 2020, 2, 2000085. [Google Scholar] [CrossRef]

- Hochstetter, J.; Zhu, R.; Loeffler, A.; Diaz-Alvarez, A.; Nakayama, T.; Kuncic, Z. Avalanches and edge-of-chaos learning in neuromorphic nanowire networks. Nat. Commun. 2021, 12, 4008. [Google Scholar] [CrossRef] [PubMed]

- Dunham, C.S.; Lilak, S.; Hochstetter, J.; Loeffler, A.; Zhu, R.; Chase, C.; Stieg, A.Z.; Kuncic, Z.; Gimzewski, J. Nanoscale neuromorphic networks and criticality: A perspective. J. Phys. Complex. 2021, 2, 042001. [Google Scholar] [CrossRef]

- Milano, G.; Porro, S.; Valov, I.; Ricciardi, C. Nanowire Memristors: Recent Developments and Perspectives for Memristive Devices Based on Metal Oxide Nanowires (Adv. Electron. Mater. 9/2019). Adv. Electron. Mater. 2019, 5, 1970044. [Google Scholar] [CrossRef]

- Simanullang, M.; Usami, K.; Kodera, T. Growth of nanowires by high-temperature glancing angle deposition. Jpn. J. Appl. Phys. 2013, 52, 110116. [Google Scholar]

- Hu, J.; Zhang, F.; Wang, J.; Xiao, J. Synthesis of single-crystalline Fe nanowires using catalyst-assisted chemical vapor deposition. Mater. Lett. 2015, 160, 529–532. [Google Scholar] [CrossRef]

- Chan, K.T.; Kan, J.J.; Doran, C.; Ouyang, L.; Smith, D.J.; Fullerton, E. Oriented growth of single-crystal Ni nanowires onto amorphous SiO2. Nano Lett. 2010, 10, 5070–5075. [Google Scholar] [CrossRef]

- Chan, K.T.; Kan, J.J.; Doran, C.; Ouyang, L.; Smith, D.J.; Fullerton, E. Controlled growth behavior of chemical vapor deposited Ni nanostructures. Philos. Mag. 2012, 92, 2173–2186. [Google Scholar] [CrossRef]

- Ganapathi, A.; Swaminathan, P.; Neelakantan, L. Anodic aluminum oxide template assisted synthesis of copper nanowires using a galvanic displacement process for electrochemical denitrification. ACS Appl. Nano Mater. 2019, 2, 5981–5988. [Google Scholar] [CrossRef]

- Guiliani, J.; Cadena, J.; Monton, C. Template-assisted electrodeposition of Ni and Ni/Au nanowires on planar and curved substrates. Nanotechnology 2018, 29, 075301. [Google Scholar] [CrossRef]

- Wen, L.; Xu, R.; Mi, Y.; Lei, Y. Multiple nanostructures based on anodized aluminium oxide templates. Nat. Nanotechnol. 2017, 12, 244–250. [Google Scholar] [CrossRef]

- Zhang, D.; Wang, R.; Wen, M.; Weng, D.; Cui, X.; Sun, J.; Li, H.; Lu, Y. Synthesis of ultralong copper nanowires for high-performance transparent electrodes. J. Am. Chem. Soc. 2012, 134, 14283–14286. [Google Scholar] [CrossRef] [PubMed]

- Zheng, Y.; Chen, N.; Wang, C.; Zhang, X.; Liu, Z. Oleylamine-mediated hydrothermal growth of millimeter-long Cu nanowires and their electrocatalytic activity for reduction of nitrate. Nanomaterials 2018, 8, 192. [Google Scholar] [CrossRef]

- Goktas, N.I.; Wilson, P.; Ghukasyan, A.; Wagner, D.; McNamee, S.; LaPierre, R. Nanowires for energy: A review. Appl. Phys. Rev. 2018, 5, 041305. [Google Scholar] [CrossRef]

- Biermanns, A.; Breuer, S.; Trampert, A.; Davydok, A.; Geelhaar, L.; Pietsch, U. Strain accommodation in Ga-assisted GaAs nanowires grown on silicon (111). Nanotechnology 2012, 23, 305703. [Google Scholar] [CrossRef] [PubMed]

- Mohseni, P.; Maunders, C.; Botton, G.; LaPierre, R. GaP/GaAsP/GaP core–multishell nanowire heterostructures on (111) silicon. Nanotechnology 2007, 18, 445304. [Google Scholar] [CrossRef]

- Ting, Y.H.; Chen, J.Y.; Huang, C.W.; Huang, T.K.; Hsieh, C.Y.; Wu, W. Observation of resistive switching behavior in crossbar core–shell Ni/NiO nanowires memristor. Small 2018, 14, 1703153. [Google Scholar] [CrossRef]

- Wu, X.; Cui, N.; Zhang, Q.; Xiong, X.; Zhu, T.; Xu, Q. ZnO single-nanowire schottky barrier resistive switching memory assembly with dielectrophoresis. J. Electron. Mater. 2022, 51, 7190–7197. [Google Scholar] [CrossRef]

- Chen, J.-G.; Cao, G.-M.; Liu, Q.; Meng, P.; Liu, Z.; Liu, F. Two-dimensional Nb3Cl8 memristor based on desorption and adsorption of O2 molecules. Rare Met. 2022, 41, 325–332. [Google Scholar] [CrossRef]

- Merolla, P.A.; Arthur, J.V.; Alvarez-Icaza, R.; Cassidy, A.S.; Sawada, J.; Akopyan, F.; Jackson, B.L.; Imam, N.; Guo, C.; Nakamura, Y. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 2014, 345, 668–673. [Google Scholar] [CrossRef]

- Zidan, M.; Chen, A.; Indiveri, G.; Lu, W. Memristive computing devices and applications. Nat. Electron. 2018, 1, 22. [Google Scholar] [CrossRef]

- Liu, C.; Yan, X.; Song, X.; Ding, S.; Zhang, D.W.; Zhou, P. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 2018, 13, 404–410. [Google Scholar] [CrossRef]

- Manipatruni, S.; Nikonov, D.E.; Young, I. Beyond CMOS computing with spin and polarization. Nat. Phys. 2018, 14, 338–343. [Google Scholar] [CrossRef]

- Xu, Y.; Gao, S.; Li, Z.; Yang, R.; Miao, X. Adaptive Hodgkin–Huxley neuron for retina-inspired perception. Adv. Intell. Syst. 2022, 4, 2200210. [Google Scholar] [CrossRef]

- Chen, X.; Chen, B.; Zhao, P.; Roy, V.A.; Han, S.-T.; Zhou, Y. Nanowire-based synaptic devices for neuromorphic computing. Mater. Futures 2023, 2, 023501. [Google Scholar] [CrossRef]

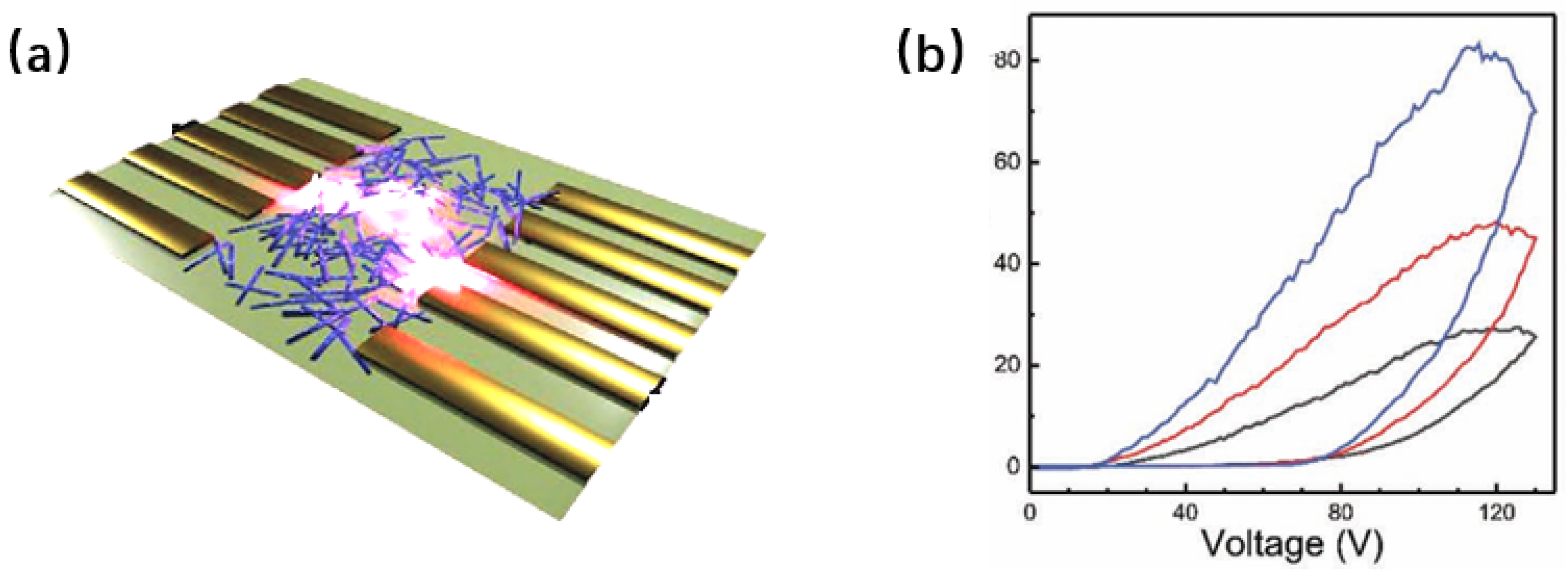

- Li, Q.; Diaz-Alvarez, A.; Iguchi, R.; Hochstetter, J.; Loeffler, A.; Zhu, R.; Shingaya, Y.; Kuncic, Z.; Uchida, K.i.; Nakayama, T. Dynamic electrical pathway tuning in neuromorphic nanowire networks. Adv. Funct. Mater. 2020, 30, 2003679. [Google Scholar] [CrossRef]

- Hosseini, M.; Frick, N.; Guilbaud, D.; Gao, M.; LaBean, T. Resistive switching of two-dimensional Ag2S nanowire networks for neuromorphic applications. J. Vac. Sci. 2022, 40, 043201. [Google Scholar] [CrossRef]

- Qin, L.; Cheng, S.; Xie, B.; Wei, X.; Jie, W. Co-existence of bipolar nonvolatile and volatile resistive switching based on WO3 nanowire for applications in neuromorphic computing and selective memory. Appl. Phys. Lett. 2022, 121, 093502. [Google Scholar] [CrossRef]

- Xu, J.; Luo, Z.; Chen, L.; Zhou, X.; Zhang, H.; Zheng, Y.; Wei, L. Recent advances in flexible memristors for advanced computing and sensing. Mater. Horiz. 2024, 11, 4015–4036. [Google Scholar] [CrossRef]

- Wan, J.; Qiu, W.; Lai, Y.; Lin, P.; Zheng, Q.; Yu, J.; Cheng, S.; Zhang, H. Efficient implementation of synaptic learning rules for neuromorphic computing based on plasma-treated ZnO nanowire memristors. J. Phys. D Appl. Phys. 2019, 53, 055303. [Google Scholar] [CrossRef]

- Yeon, H.; Lin, P.; Choi, C.; Tan, S.H.; Park, Y.; Lee, D.; Lee, J.; Xu, F.; Gao, B.; Wu, H.; et al. Alloying conducting channels for reliable neuromorphic computing. Nat. Nanotechnol. 2020, 15, 574–579. [Google Scholar] [CrossRef] [PubMed]

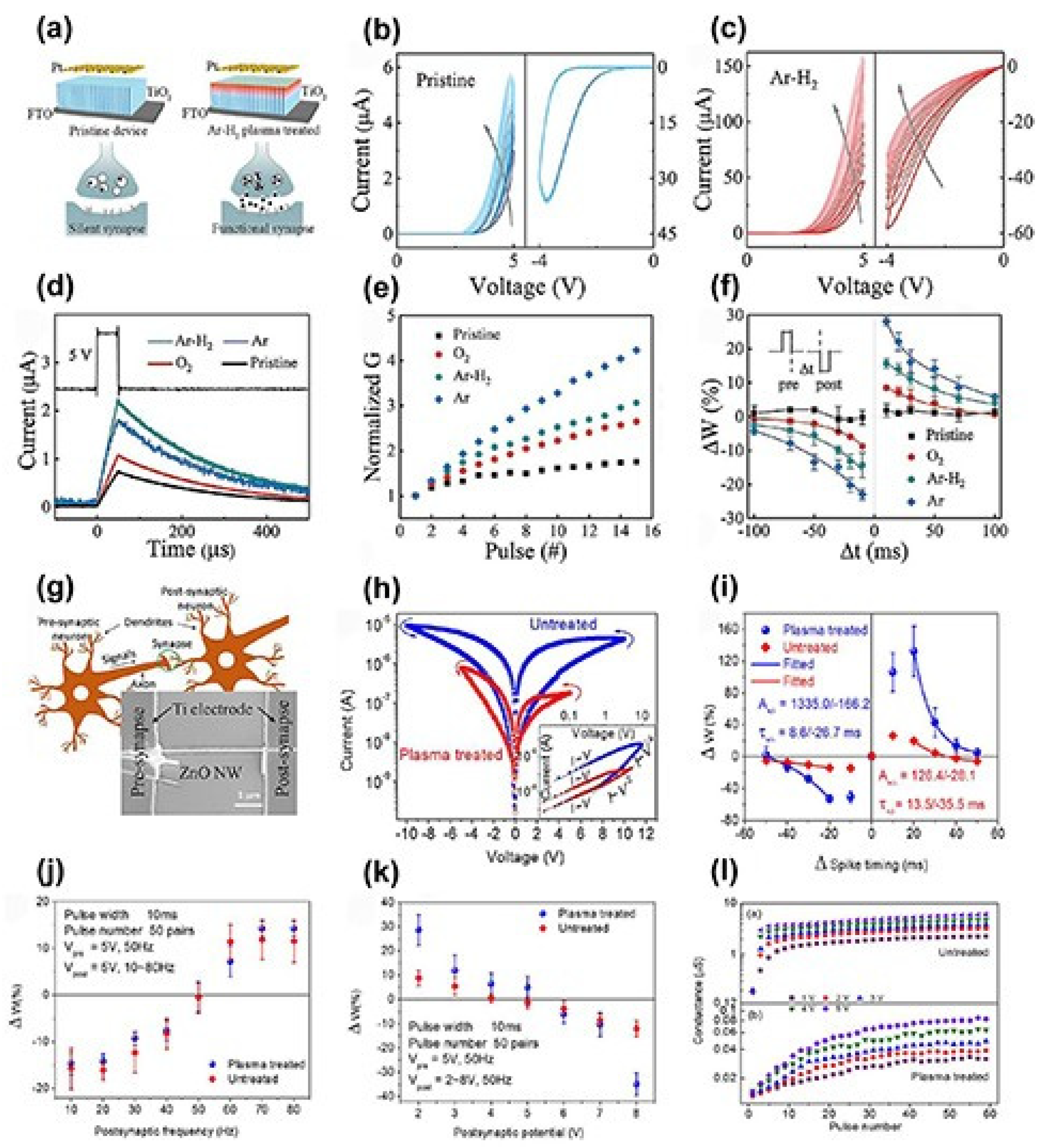

- Shan, X.; Wang, Z.; Lin, Y.; Zeng, T.; Zhao, X.; Xu, H.; Liu, Y. Silent Synapse Activation by Plasma-Induced Oxygen Vacancies in TiO2 Nanowire-Based Memristor. Adv. Electron. Mater. 2020, 6, 2000536. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, W.; Zhang, C.; Kan, H.; Yue, W.; Pang, J.; Gao, S.; Li, Y. A digital–analog integrated memristor based on a ZnO NPs/CuO NWs heterostructure for neuromorphic computing. ACS Appl. Electron. Mater. 2022, 4, 3525–3534. [Google Scholar] [CrossRef]

- He, H.-K.; Yang, R.; Huang, H.-M.; Yang, F.-F.; Wu, Y.-Z.; Shaibo, J.; Guo, X. Multi-gate memristive synapses realized with the lateral heterostructure of 2D WSe2 and WO3. Nanoscale 2020, 12, 380–387. [Google Scholar] [CrossRef]

- Van, N.H.; Lee, J.-H.; Whang, D.; Kang, D. Ultralow-power non-volatile memory cells based on P (VDF-TrFE) ferroelectric-gate CMOS silicon nanowire channel field-effect transistors. Nanoscale 2015, 7, 11660–11666. [Google Scholar]

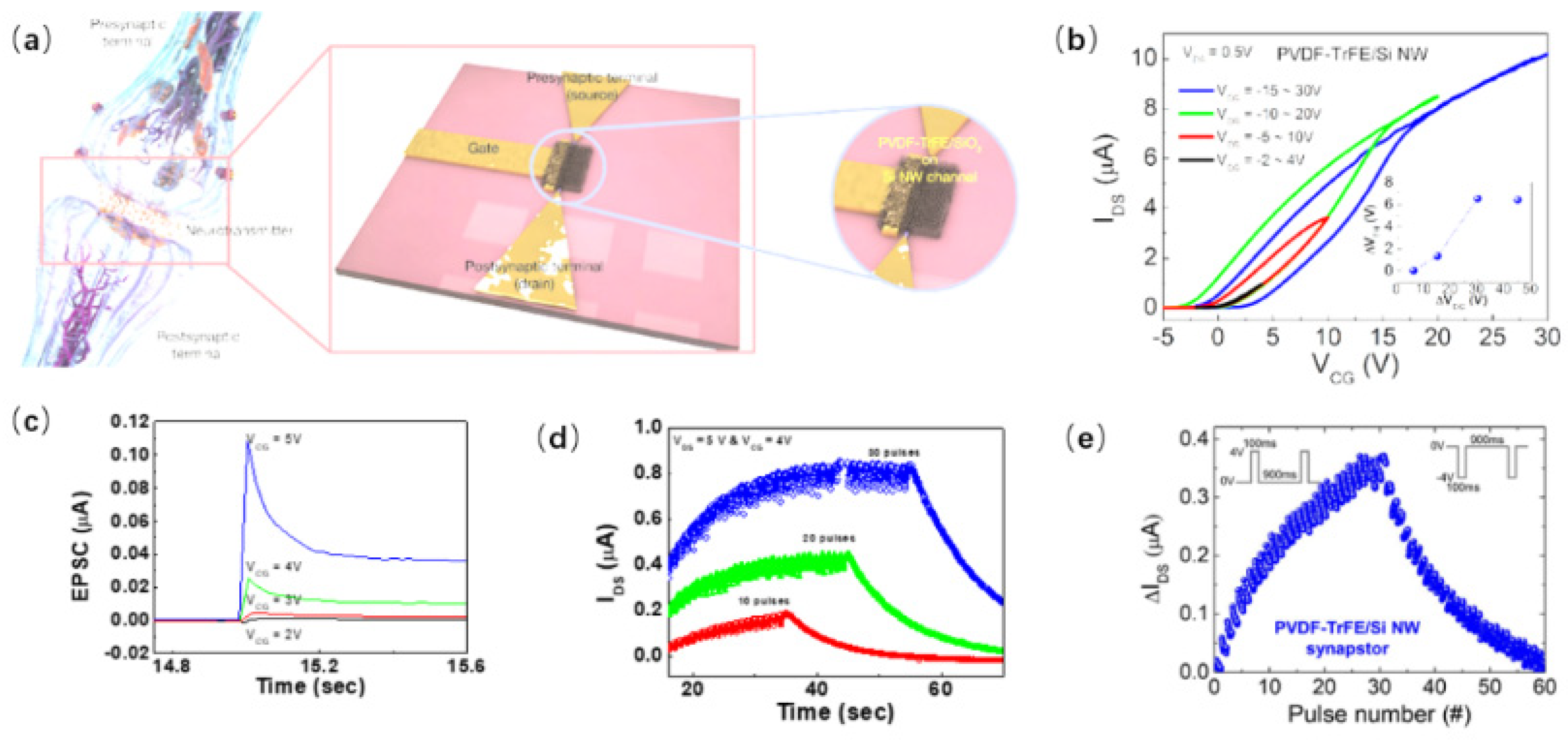

- Lee, M.; Park, W.; Son, H.; Seo, J.; Kwon, O.; Oh, S.; Hahm, M.; Kim, U.; Cho, B. Brain-inspired ferroelectric Si nanowire synaptic device. APL Mater. 2021, 9, 031103. [Google Scholar] [CrossRef]

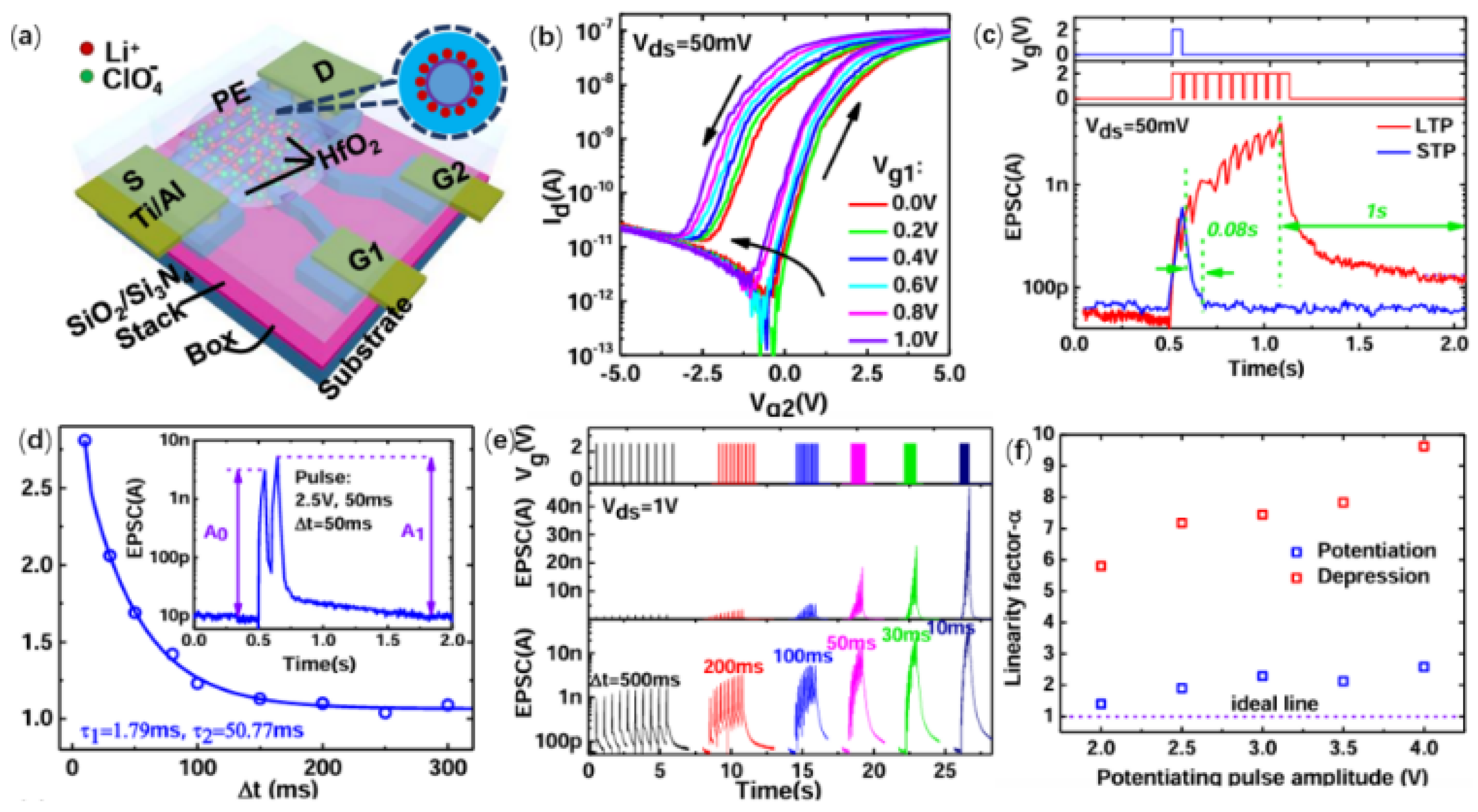

- Li, X.; Yu, B.; Wang, B.; Bao, L.; Zhang, B.; Li, H.; Yu, Z.; Zhang, T.; Yang, Y.; Huang, R.; et al. Multi-terminal ionic-gated low-power silicon nanowire synaptic transistors with dendritic functions for neuromorphic systems. Nanoscale 2020, 12, 16348–16358. [Google Scholar] [CrossRef]

- Yu, S. Neuro-inspired computing with emerging nonvolatile memorys. Proc. IEEE 2018, 106, 260–285. [Google Scholar] [CrossRef]

- Chen, P.-Y.; Peng, X.; Yu, S. NeuroSim: A circuit-level macro model for benchmarking neuro-inspired architectures in online learning. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 37, 3067–3080. [Google Scholar] [CrossRef]

- Wu, H.; Cui, Y.; Xu, J.; Yan, Z.; Xie, Z.; Hu, Y.; Zhu, S. Multifunctional half-floating-gate field-effect transistor based on MoS2–BN–graphene van der Waals heterostructures. Nano Lett. 2022, 22, 2328–2333. [Google Scholar] [CrossRef] [PubMed]

- Zhang, B.-W.; Fang, D.; Fang, X.; Zhao, H.-B.; Wang, D.-K.; Li, J.-H.; Wang, X.-H.; Wang, D. InAs/InAsSb type-II superlattice with near room-temperature long-wave emission through interface engineering. Rare Met. 2022, 41, 982–991. [Google Scholar] [CrossRef]

- Liu, M.; Shi, C.; Li, W.; Nan, P.; Fang, X.; Ge, B.; Xu, Z.; Wang, D.; Fang, D.; Wang, X.; et al. Interfacial Characteristics and Optical Properties of InAs/InAsSb Type II Superlattices for the Mid-Infrared Operation. Phys. Status Solidi–Rapid Res. Lett. 2023, 17, 2200412. [Google Scholar] [CrossRef]

- Vieira, D.H.; Nogueira, G.L.; Merces, L.; Bufon, C.C.B.; Alves, N. Electrolyte-Gated Vertical Transistor Charge Transport Enables Photo-Switching. Adv. Electron. Mater. 2024, 10, 2300562. [Google Scholar] [CrossRef]

- Baby, T.T.; Rommel, M.; von Seggern, F.; Friederich, P.; Reitz, C.; Dehm, S.; Kübel, C.; Wenzel, W.; Hahn, H.; Dasgupta, S. Sub-50 nm Channel Vertical Field-Effect Transistors using Conventional Ink-Jet Printing. Adv. Mater. 2017, 29, 1603858. [Google Scholar] [CrossRef]

- Lam, K.T.; Seol, G.; Guo, J. Operating principles of vertical transistors based on monolayer two-dimensional semiconductor heterojunctions. Appl. Phys. Lett. 2014, 105, 013112. [Google Scholar] [CrossRef]

- Liu, G.; Li, Q.; Shi, W.; Liu, Y.; Liu, K.; Yang, X.; Shao, M.; Guo, A.; Huang, X.; Zhang, F.; et al. Ultralow-power and multisensory artificial synapse based on electrolyte-gated vertical organic transistors. Adv. Funct. Mater. 2022, 32, 2200959. [Google Scholar] [CrossRef]

- Woo, S.; Kim, S.J. Neural oscillation of single silicon nanowire neuron device with no external bias voltage. Sci. Rep. 2022, 12, 3516. [Google Scholar] [CrossRef]

- Chen, J.; Zhu, Y.-Q.; Zhao, X.-C.; Wang, Z.-H.; Zhang, K.; Zhang, Z.; Sun, M.-Y.; Wang, S.; Zhang, Y.; Han, L.; et al. PZT-enabled MoS2 floating gate transistors: Overcoming boltzmann tyranny and achieving ultralow energy consumption for high-accuracy neuromorphic computing. Nano Lett. 2023, 23, 10196–10204. [Google Scholar] [CrossRef]

- Yao, C.; Wu, G.; Huang, M.; Wang, W.; Zhang, C.; Wu, J.; Liu, H.; Zheng, B.; Yi, J.; Zhu, C.; et al. Reconfigurable artificial synapse based on ambipolar floating gate memory. ACS Appl. Mater. 2023, 15, 23573–23582. [Google Scholar] [CrossRef]

- Li, C.; Chen, X.; Zhang, Z.; Wu, X.; Yu, T.; Bie, R.; Yang, D.; Yao, Y.; Wang, Z.; Sun, L. Charge-selective 2D heterointerface-driven multifunctional floating gate memory for in situ sensing-memory-computing. Nano Lett. 2024, 24, 15025–15034. [Google Scholar] [CrossRef]

- Zhang, Q.; Jin, T.; Ye, X.; Geng, D.; Chen, W.; Hu, W. Organic field effect transistor-based photonic synapses: Materials, devices, and applications. Adv. Funct. Mater. 2021, 31, 2106151. [Google Scholar] [CrossRef]

- Xie, D.; Wei, L.; Wei, Z.; He, J.; Jiang, J. Water-induced dual ultrahigh mobilities over 400 cm 2 V−1 s−1 in 2D MoS2 transistors for ultralow-voltage operation and photoelectric synapse perception. J. Mater. Chem. C 2022, 10, 5249–5256. [Google Scholar] [CrossRef]

- Wang, W.S.; Ren, Z.Y.; Shi, Z.W.; Xiao, H.; Zeng, Y.H.; Zhu, L. Flexible nanocellulose gated pseudo-diode for neuromorphic electronic applications. IEEE Electron. Device Lett. 2022, 43, 737–740. [Google Scholar] [CrossRef]

- Liu, X.; Sun, C.; Guo, Z.; Zhang, Y.; Zhang, Z.; Shang, J.; Zhong, Z.; Zhu, X.; Yu, X.; Li, R. A flexible dual-gate hetero-synaptic transistor for spatiotemporal information processing. Nanoscale Adv. 2022, 4, 2412–2419. [Google Scholar] [CrossRef]

- Wang, S.; Chen, X.; Zhao, C.; Kong, Y.; Lin, B.; Wu, Y.; Bi, Z.; Xuan, Z.; Li, T.; Li, Y.; et al. An organic electrochemical transistor for multi-modal sensing, memory and processing. Nat. Electron. 2023, 6, 281–291. [Google Scholar] [CrossRef]

- van De Burgt, Y.; Melianas, A.; Keene, S.T.; Malliaras, G.; Salleo, A. Organic electronics for neuromorphic computing. Nat. Electron. 2018, 1, 386–397. [Google Scholar] [CrossRef]

- Bi, G.-Q.; Poo, M. Synaptic modifications in cultured hippocampal neurons: Dependence on spike timing, synaptic strength, and postsynaptic cell type. J. Neurosci. 1998, 18, 10464–10472. [Google Scholar] [CrossRef]

- Wang, W.; Pedretti, G.; Milo, V.; Carboni, R.; Calderoni, A.; Ramaswamy, N.; Spinelli, A.S.; Ielmini, D. Learning of spatiotemporal patterns in a spiking neural network with resistive switching synapses. Sci. Adv. 2018, 4, eaat4752. [Google Scholar] [CrossRef]

- Fuller, E.J.; Keene, S.T.; Melianas, A.; Wang, Z.; Agarwal, S.; Li, Y.; Tuchman, Y.; James, C.D.; Marinella, M.J.; Yang, J.; et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 2019, 364, 570–574. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.; et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, H.; Burr, G.W.; Hwang, C.S.; Wang, K.L.; Xia, Q.; Yang, J. Resistive switching materials for information processing. Nat. Rev. Mater. 2020, 5, 173–195. [Google Scholar] [CrossRef]

- Yan, Y.; Chen, Q.; Wu, X.; Wang, X.; Li, E.; Ke, Y.; Liu, Y.; Chen, H.; Guo, T. High-performance organic electrochemical transistors with nanoscale channel length and their application to artificial synapse. ACS Appl. Mater. 2020, 12, 49915–49925. [Google Scholar] [CrossRef] [PubMed]

- Maria de Andrade, D.; Merces, L.; Nawaz, A.; Bof Bufon, C. Pushing On-Chip Photosensitivity Forward Using Edge-Driven Vertical Organic Phototransistors. ACS Appl. Electron. Mater. 2023, 5, 3038–3047. [Google Scholar] [CrossRef]

- Shen, C.; Gao, X.; Chen, C.; Ren, S.; Xu, J.-L.; Xia, Y.-D.; Wang, S. ZnO nanowire optoelectronic synapse for neuromorphic computing. Nanotechnology 2021, 33, 065205. [Google Scholar] [CrossRef] [PubMed]

- Song, J.; Bazant, M. Electrochemical impedance imaging via the distribution of diffusion times. Phys. Rev. Lett. 2018, 120, 116001. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Kannan, U.M.; Cho, S. Core-shell dual-gate nanowire charge-trap memory for synaptic operations for neuromorphic applications. Nanomaterials 2021, 11, 1773. [Google Scholar] [CrossRef]

- Xie, P.; Huang, Y.; Wang, W.; Meng, Y.; Lai, Z.; Wang, F.; Yip, S.; Bu, X.; Wang, W.; Li, D.; et al. Ferroelectric P (VDF-TrFE) wrapped InGaAs nanowires for ultralow-power artificial synapses. Nano Energy 2022, 91, 106654. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhao, X.; Zhang, X.; Hou, X.; Ma, X.; Tang, S.; Zhang, Y.; Xu, G.; Liu, Q.; Long, S. In-sensor reservoir computing system for latent fingerprint recognition with deep ultraviolet photo-synapses and memristor array. Nat. Commun. 2022, 13, 6590. [Google Scholar] [CrossRef]

- Milano, G.; Pedretti, G.; Montano, K.; Ricci, S.; Hashemkhani, S.; Boarino, L.; Ielmini, D.; Ricciardi, C. In materia reservoir computing with a fully memristive architecture based on self-organizing nanowire networks. Nat. Mater. 2022, 21, 195–202. [Google Scholar] [CrossRef]

- Bao, H.; Zhou, H.; Li, J.; Pei, H.; Tian, J.; Yang, L.; Ren, S.; Tong, S.; Li, Y.; He, Y.; et al. Toward memristive in-memory computing: Principles and applications. Front. Optoelectron. 2022, 15, 23. [Google Scholar] [CrossRef] [PubMed]

- Poddar, S.; Zhang, Y.; Chen, Z.; Ma, Z.; Fu, Y.; Ding, Y.; Chan, C.L.J.; Zhang, Q.; Zhang, D.; Song, Z.; et al. Image processing with a multi-level ultra-fast three dimensionally integrated perovskite nanowire array. Nanoscale Horiz. 2022, 7, 759–769. [Google Scholar] [CrossRef] [PubMed]

- Wang, P.; Li, G.; Liu, J.; Hou, Z.; Meng, C.; Guo, S.; Liu, C.; Fan, S. Tailorable capacitive tactile sensor based on stretchable and dissolvable porous silver nanowire/polyvinyl alcohol nanocomposite hydrogel for wearable human motion detection. Adv. Mater. Interfaces 2021, 8, 2100998. [Google Scholar] [CrossRef]

- Ambhorkar, P.; Wang, Z.; Ko, H.; Lee, S.; Koo, K.-i.; Kim, K.; Cho, D. Nanowire-based biosensors: From growth to applications. Micromachines 2018, 9, 679. [Google Scholar] [CrossRef] [PubMed]

- Patolsky, F.; Zheng, G.; Lieber, C. Nanowire sensors for medicine and the life sciences. Nanomedicine 2006, 1, 51–65. [Google Scholar] [CrossRef]

- Koo, K.-i.; Seo, J. A review of nanotechnology for highly sensitive photodetectors for vision sensors of insect-like robots. Sensors 2015, 27, 465–474. [Google Scholar] [CrossRef]

- Kurkina, T.; Balasubramanian, K. Towards in vitro molecular diagnostics using nanostructures. Cell. Mol. Life Sci. 2012, 69, 373–388. [Google Scholar] [CrossRef]

- Thiele, T.; Ibarlucea, B.; Akbar, T.F.; Werner, C.; Cuniberti, G. StarPEG–heparin biosensors for rapid and portable diagnostics in complex biofluids. Sensors 2022, 1, 558–565. [Google Scholar] [CrossRef]

- Zhou, W.; Dai, X.; Lieber, C. Advances in nanowire bioelectronics. Rep. Prog. Phys. 2016, 80, 016701. [Google Scholar] [CrossRef]

- Xie, C.; Liu, J.; Fu, T.-M.; Dai, X.; Zhou, W.; Lieber, C. Three-dimensional macroporous nanoelectronic networks as minimally invasive brain probes. Nat. Mater. 2015, 14, 1286–1292. [Google Scholar] [CrossRef]

- Cho, J.; Li, X.; Gu, Z.; Kurup, P. Recognition of explosive precursors using nanowire sensor array and decision tree learning. IEEE Sens. J. 2011, 12, 2384–2391. [Google Scholar] [CrossRef]

- Silver, D.; Schrittwieser, J.; Simonyan, K.; Antonoglou, I.; Huang, A.; Guez, A.; Hubert, T.; Baker, L.; Lai, M.; Bolton, A.; et al. Mastering the game of go without human knowledge. Nature 2017, 550, 354–359. [Google Scholar] [CrossRef] [PubMed]

- Amit, M.; Mishra, R.K.; Hoang, Q.; Galan, A.M.; Wang, J.; Ng, T. Point-of-use robotic sensors for simultaneous pressure detection and chemical analysis. Mater. Horiz. 2019, 6, 604–611. [Google Scholar] [CrossRef]

- Shang, Q.; Peng, W.; Song, T.; Li, Z.; Li, F.; He, Y. ZnO photoconductive synaptic devices for neuromorphic computing. Mater. Sci. Semicond. Process. 2023, 162, 107489. [Google Scholar] [CrossRef]

- Tan, H.; Ni, Z.; Peng, W.; Du, S.; Liu, X.; Zhao, S.; Li, W.; Ye, Z.; Xu, M.; Xu, Y.; et al. Broadband optoelectronic synaptic devices based on silicon nanocrystals for neuromorphic computing. Nano Energy 2018, 52, 422–430. [Google Scholar] [CrossRef]

- Qian, C.; Oh, S.; Choi, Y.; Kim, J.-H.; Sun, J.; Huang, H.; Yang, J.; Gao, Y.; Park, J.-H.; Cho, J. Solar-stimulated optoelectronic synapse based on organic heterojunction with linearly potentiated synaptic weight for neuromorphic computing. Nano Energy 2019, 66, 104095. [Google Scholar] [CrossRef]

- Kumar, N.; Patel, M.; Nguyen, T.T.; Bhatnagar, P.; Kim, J. All-oxide-based and metallic electrode-free artificial synapses for transparent neuromorphic computing. Mater. Today Chem. 2022, 23, 100681. [Google Scholar] [CrossRef]

- Bhatnagar, P.; Hong, J.; Patel, M.; Kim, J. Transparent photovoltaic skin for artificial thermoreceptor and nociceptor memory. Nano Energy 2022, 91, 106676. [Google Scholar] [CrossRef]

- Peng, W.; Pan, Z.; Li, F.; Cai, Y.; He, Y. Pyro-phototronic effect enhanced ZnO nanowire-based tri-layer heterojunction for visible light sensing and communication. Nano Energy 2020, 78, 105268. [Google Scholar] [CrossRef]

- Zheng, J.; Ji, G.; Fan, X.; Chen, J.; Li, Q.; Wang, H.; Yang, Y.; DeMella, K.C.; Raghavan, S.R.; Wang, C. High-fluorinated electrolytes for Li–S batteries. Adv. Energy Mater. 2019, 9, 1803774. [Google Scholar] [CrossRef]

- Manthiram, A.; Fu, Y.; Chung, S.-H.; Zu, C.; Su, Y. Rechargeable lithium–sulfur batteries. Chem. Rev. 2014, 114, 11751–11787. [Google Scholar] [CrossRef] [PubMed]

- Li, C.; Wang, Z.; Rao, M.; Belkin, D.; Song, W.; Jiang, H.; Yan, P.; Li, Y.; Lin, P.; Hu, M.; et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 2019, 1, 49–57. [Google Scholar] [CrossRef]

- Hochreiter, S.; Schmidhuber, J. Long short-term memory. J Neural Comput. 1997, 9, 1735–1780. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.; Kim, T.W.; Choi, H.Y.; Strukov, D.B.; Yang, J. Flexible three-dimensional artificial synapse networks with correlated learning and trainable memory capability. Nat. Commun. 2017, 8, 752. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, T.; Wang, Y.; Jin, Z.; Liu, H.; Wang, K.; Chee, T.L.; Shi, Y.; Yan, S. A Review of Nanowire Devices Applied in Simulating Neuromorphic Computing. Nanomaterials 2025, 15, 724. https://doi.org/10.3390/nano15100724

Huang T, Wang Y, Jin Z, Liu H, Wang K, Chee TL, Shi Y, Yan S. A Review of Nanowire Devices Applied in Simulating Neuromorphic Computing. Nanomaterials. 2025; 15(10):724. https://doi.org/10.3390/nano15100724

Chicago/Turabian StyleHuang, Tianci, Yuxuan Wang, Zhihan Jin, Hao Liu, Kaili Wang, Tan Leong Chee, Yi Shi, and Shancheng Yan. 2025. "A Review of Nanowire Devices Applied in Simulating Neuromorphic Computing" Nanomaterials 15, no. 10: 724. https://doi.org/10.3390/nano15100724

APA StyleHuang, T., Wang, Y., Jin, Z., Liu, H., Wang, K., Chee, T. L., Shi, Y., & Yan, S. (2025). A Review of Nanowire Devices Applied in Simulating Neuromorphic Computing. Nanomaterials, 15(10), 724. https://doi.org/10.3390/nano15100724