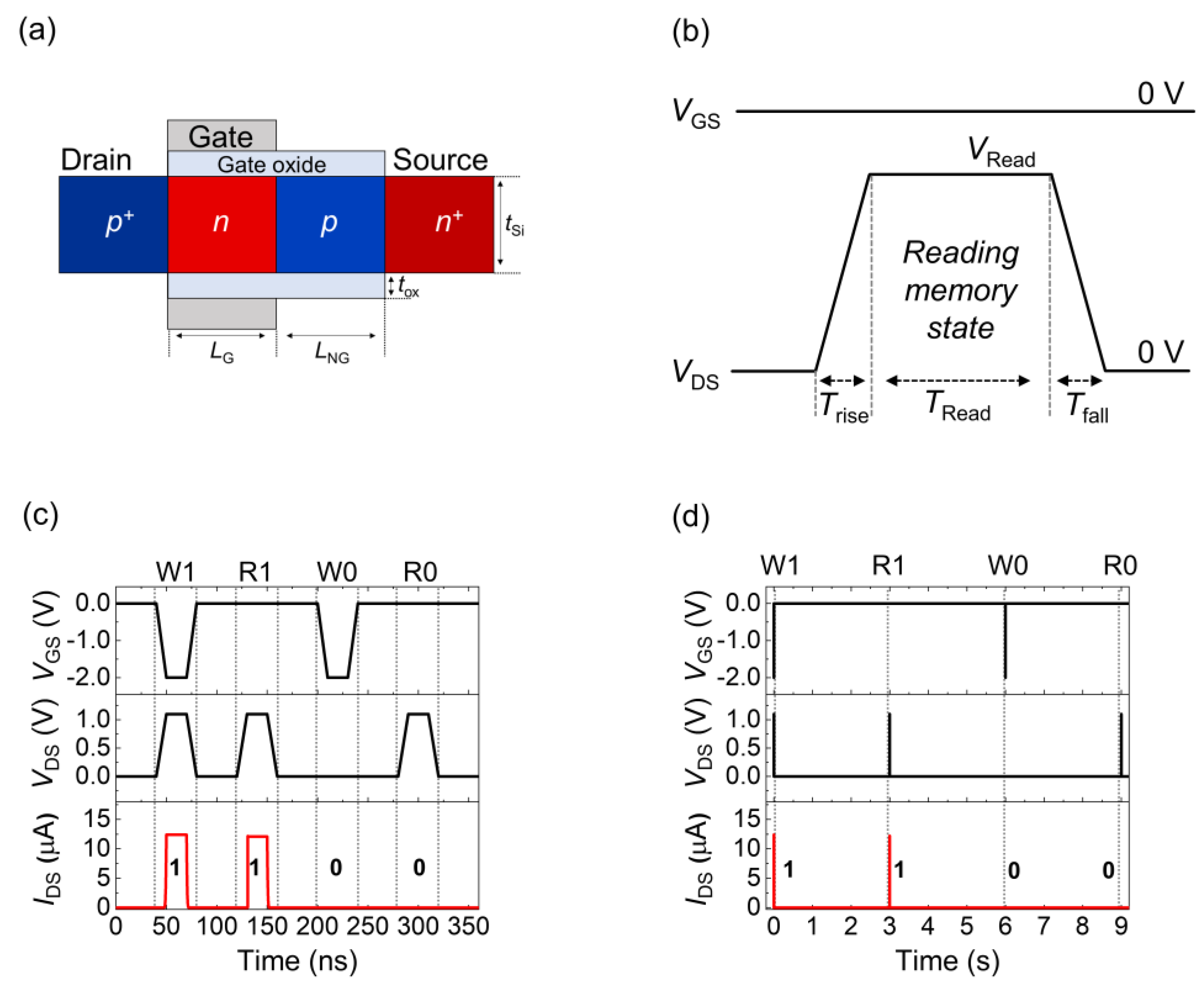

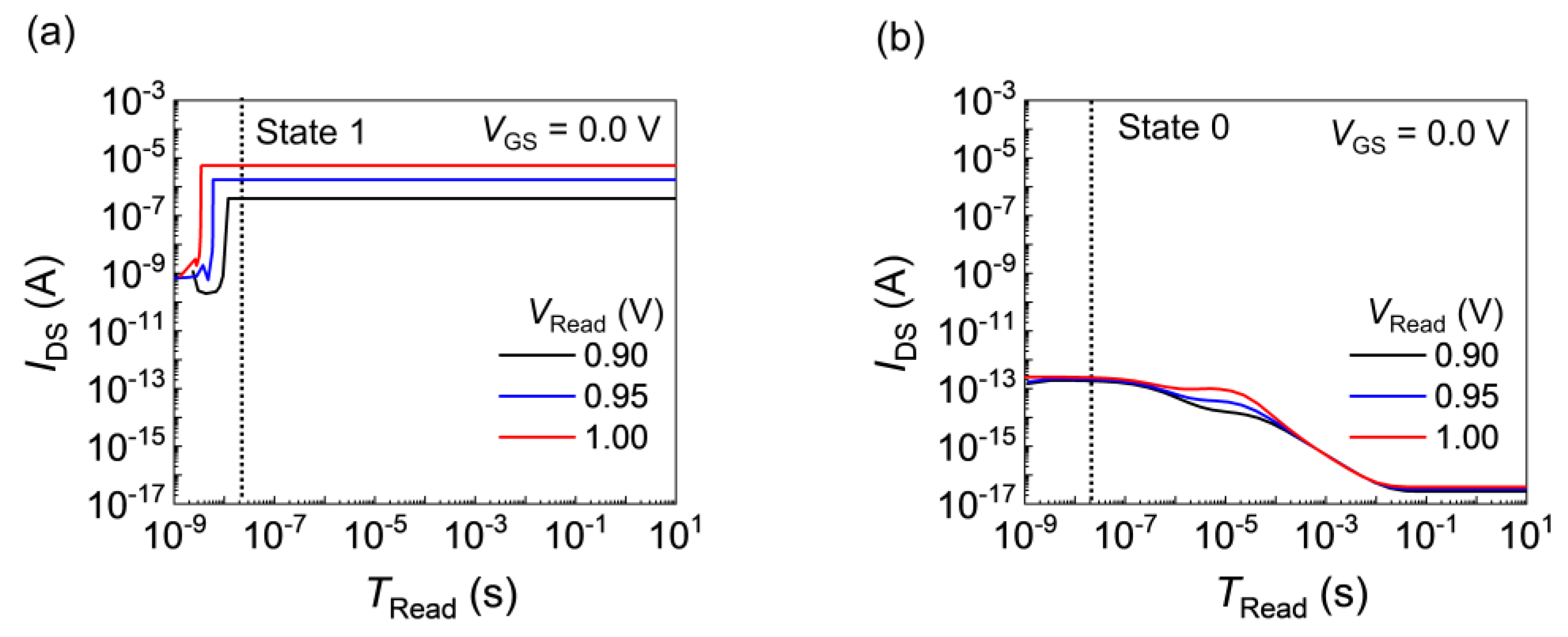

Read Operation Mechanism of Feedback Field-Effect Transistors with Quasi-Nonvolatile Memory States

Abstract

1. Introduction

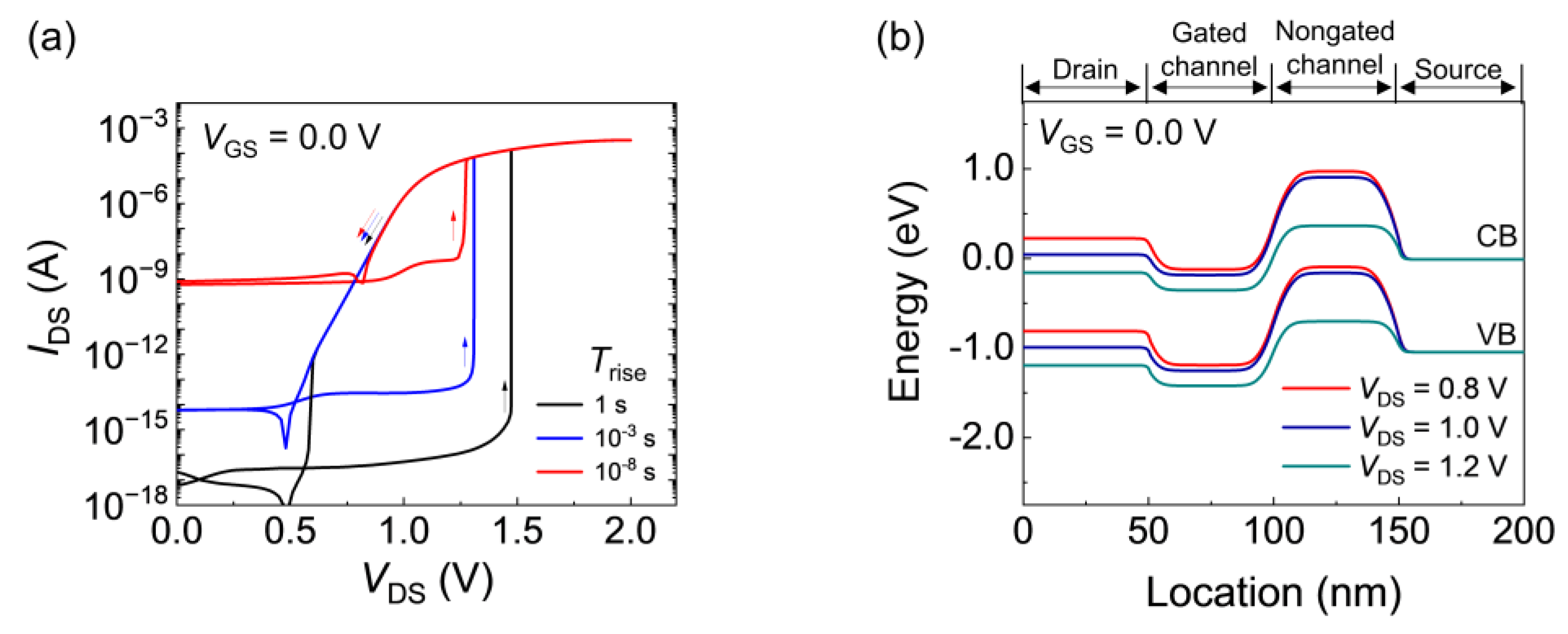

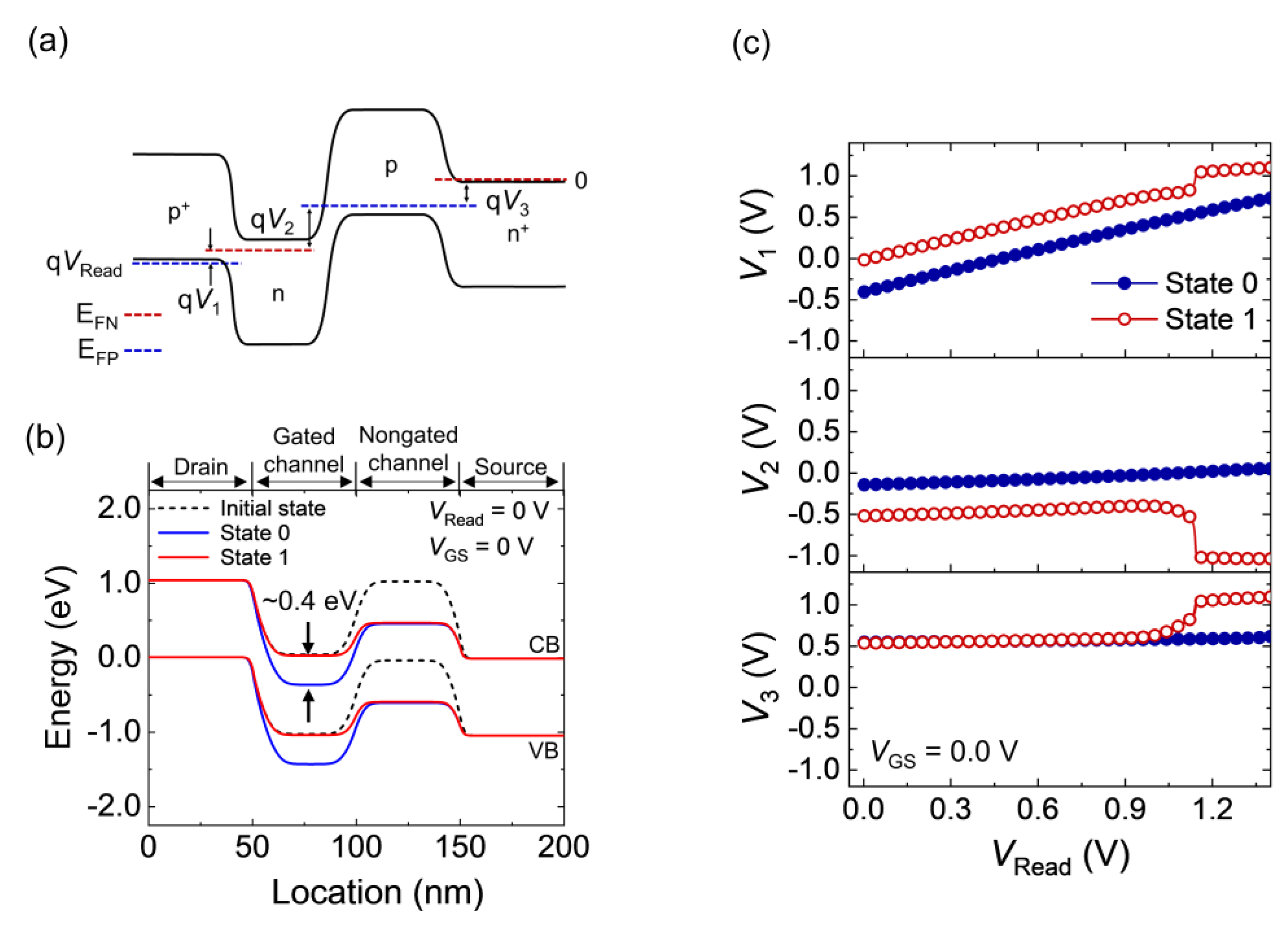

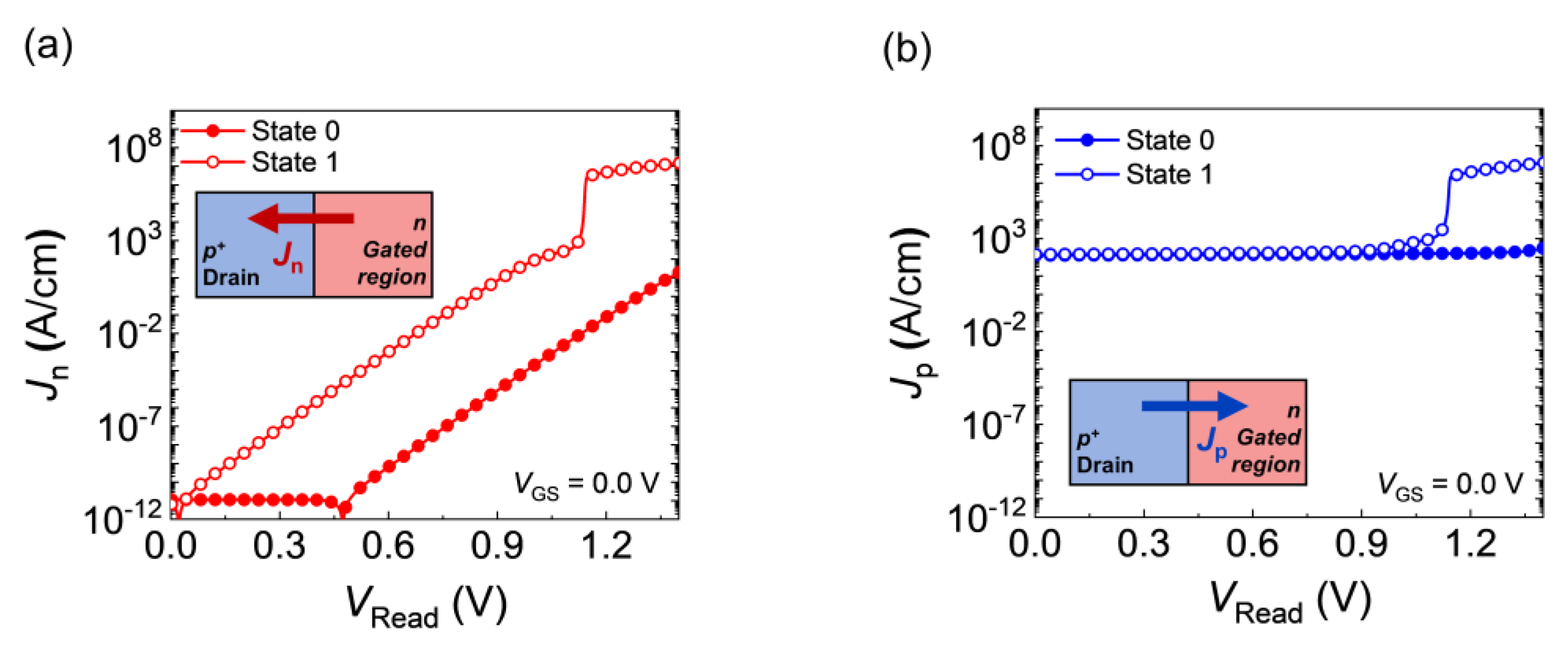

2. Results and Discussions

3. Conclusions

4. Simulation Method

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, C.; Yan, X.; Song, X.; Ding, S.; Zhang, D.W.; Zhou, P. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 2018, 13, 404–410. [Google Scholar] [CrossRef]

- Yang, K.; Liu, H.; Wang, S.; Yu, W.; Han, T. Comprehensive performance quasi-non-volatile memory compatible with large-scale preparation by chemical vapor deposition. Nanomaterials 2020, 10, 1471. [Google Scholar] [CrossRef] [PubMed]

- Lim, D.; Son, J.; Cho, K.; Kim, S. Quasi-nonvolatile silicon memory device. Adv. Mater. Technol. 2020, 5, 2000915. [Google Scholar] [CrossRef]

- Wong, H.S.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.-H. Technology scaling challenges and opportunities of memory devices. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; IEEE Publications: New York, NY, USA, 2016; Volume 2016, pp. 1.1.1–1.1.8. [Google Scholar] [CrossRef]

- Yu, S.; Chen, P. Emerging Memory Technologies: Recent Trends and Prospects. IEEE Solid State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Spessot, A.; Oh, H. 1T-1C dynamic random access memory status, challenges, and prospects. IEEE Trans. Electron. Devices 2020, 67, 1382–1393. [Google Scholar] [CrossRef]

- Park, J.M.; Hwang, Y.S.; Kim, S.-W.; Han, S.Y.; Park, J.S.; Kim, J.; Seo, J.W.; Kim, B.S.; Shin, S.H.; Cho, C.H.; et al. 20nm DRAM: A new beginning of another revolution. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 26.5.1–26.5.4. [Google Scholar] [CrossRef]

- Cao, Q.; Lü, W.; Wang, X.R.; Guan, X.; Wang, L.; Yan, S.; Wu, T.; Wang, X. Nonvolatile multistates memories for high-density data storage. ACS Appl. Mater. Interfaces 2020, 12, 42449–42471. [Google Scholar] [CrossRef] [PubMed]

- Hwang, C.S. Prospective of semiconductor memory devices: From memory system to materials. Adv. Electron. Mater. 2015, 1, 1400056. [Google Scholar] [CrossRef]

- Ielmini, D.; Wong, H.-S.P. In-memory computing with resistive switching devices. Nat. Electron. 2018, 1, 333–343. [Google Scholar] [CrossRef]

- Li, J.; Liu, L.; Chen, X.; Liu, C.; Wang, J.; Hu, W.; Zhang, D.W.; Zhou, P. Symmetric ultrafast writing and erasing speeds in quasi-nonvolatile memory via van der Waals heterostructures. Adv. Mater. 2019, 31, e1808035. [Google Scholar] [CrossRef] [PubMed]

- Zhou, Y.; Ning, J.; Shen, X.; Guo, H.; Zhang, C.; Dong, J.; Lu, W.; Feng, X.; Hao, Y. An ultrafast quasi-non-volatile semi-floating gate memory with low-power optoelectronic memory application. Adv. Electron. Mater. 2021, 7, 2100564. [Google Scholar] [CrossRef]

- Kwon, M.W.; Park, K.; Baek, M.-H.; Lee, J.; Park, B.G. A Low-Energy High-Density Capacitor-Less I&F Neuron Circuit Using Feedback FET Co-Integrated with CMOS. IEEE J. Electron Devices Soc. 2019, 7, 1080–1084. [Google Scholar] [CrossRef]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; IEEE Publications: New York, NY, USA, 2008; Volume 2008, pp. 1–4. [Google Scholar] [CrossRef]

- Lee, C.; Ko, E.; Shin, C. Steep slope silicon-on-insulator feedback field-effect transistor: Design and performance analysis. IEEE Trans. Electron. Devices 2018, 66, 286–291. [Google Scholar] [CrossRef]

- Resnati, D.; Monzio Compagnoni, C.M.; Mulaosmanovic, H.; Castellani, N.; Carnevale, G.; Fantini, P.; Ventrice, D.; Lacaita, A.L.; Spinelli, A.S.; Benvenuti, A. Modeling of dynamic operation of T-RAM cells. IEEE Trans. Electron. Devices 2015, 62, 1905–1911. [Google Scholar] [CrossRef]

- Navarro, C.; Lacord, J.; Parihar, M.S.; Adamu-Lema, F.; Duan, M.; Rodriguez, N.; Cheng, B.; El Dirani, H.; Barbe, J.-C.; Fonteneau, P.; et al. Extended analysis of the Z2-FET: Operation as capacitorless eDRAM. IEEE Trans. Electron. Devices 2017, 64, 4486–4491. [Google Scholar]

- Parihar, M.S.; Lee, K.H.; Bawedin, M.; Lacord, J.; Martinie, S.; Barbé, J.-C.; Xu, Y.; Taur, Y.; Cristoloveanu, S. Impact of carrier lifetime on Z2-FET operation. In Proceedings of the Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Athens, Greece, 3–5 April 2017; IEEE Publications: New York, NY, USA, 2017; Volume 2017, pp. 57–60. [Google Scholar] [CrossRef]

- Taur, Y.; Lacord, J.; Parihar, M.S.; Wan, J.; Martinie, S.; Lee, K.; Bawedin, M.; Barbe, J.-C.; Cristoloveanu, S. A comprehensive model on field-effect pnpn devices (Z2-FET). Solid State Electron. 2017, 134, 1–8. [Google Scholar] [CrossRef]

- Cho, J.; Lim, D.; Woo, S.; Cho, K.; Kim, S.; Lee, K. Static Random Access Memory Characteristics of Single-Gated Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 413–419. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide; Synopsys: Mountain View, CA, USA, 2018.

| Simulation Parameters | Value (Unit) |

|---|---|

| Drain/source doping concentration | 3 × 1019 (cm−3) |

| Gated/nongated channel doing concentration | 5 × 1018 (cm−3) |

| Gated channel length (LG) | 50 (nm) |

| Nongated channel length (LNG) | 50 (nm) |

| Channel thickness (tSi) | 20 (nm) |

| Gate oxide thickness (tox) | 5 (nm) |

| Work function of gate, drain, and source electrodes | 4.0 (eV) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeon, J.; Cho, K.; Kim, S. Read Operation Mechanism of Feedback Field-Effect Transistors with Quasi-Nonvolatile Memory States. Nanomaterials 2024, 14, 210. https://doi.org/10.3390/nano14020210

Jeon J, Cho K, Kim S. Read Operation Mechanism of Feedback Field-Effect Transistors with Quasi-Nonvolatile Memory States. Nanomaterials. 2024; 14(2):210. https://doi.org/10.3390/nano14020210

Chicago/Turabian StyleJeon, Juhee, Kyoungah Cho, and Sangsig Kim. 2024. "Read Operation Mechanism of Feedback Field-Effect Transistors with Quasi-Nonvolatile Memory States" Nanomaterials 14, no. 2: 210. https://doi.org/10.3390/nano14020210

APA StyleJeon, J., Cho, K., & Kim, S. (2024). Read Operation Mechanism of Feedback Field-Effect Transistors with Quasi-Nonvolatile Memory States. Nanomaterials, 14(2), 210. https://doi.org/10.3390/nano14020210