Reconfigurable Feedback Field-Effect Transistors with a Single Gate

Abstract

:1. Introduction

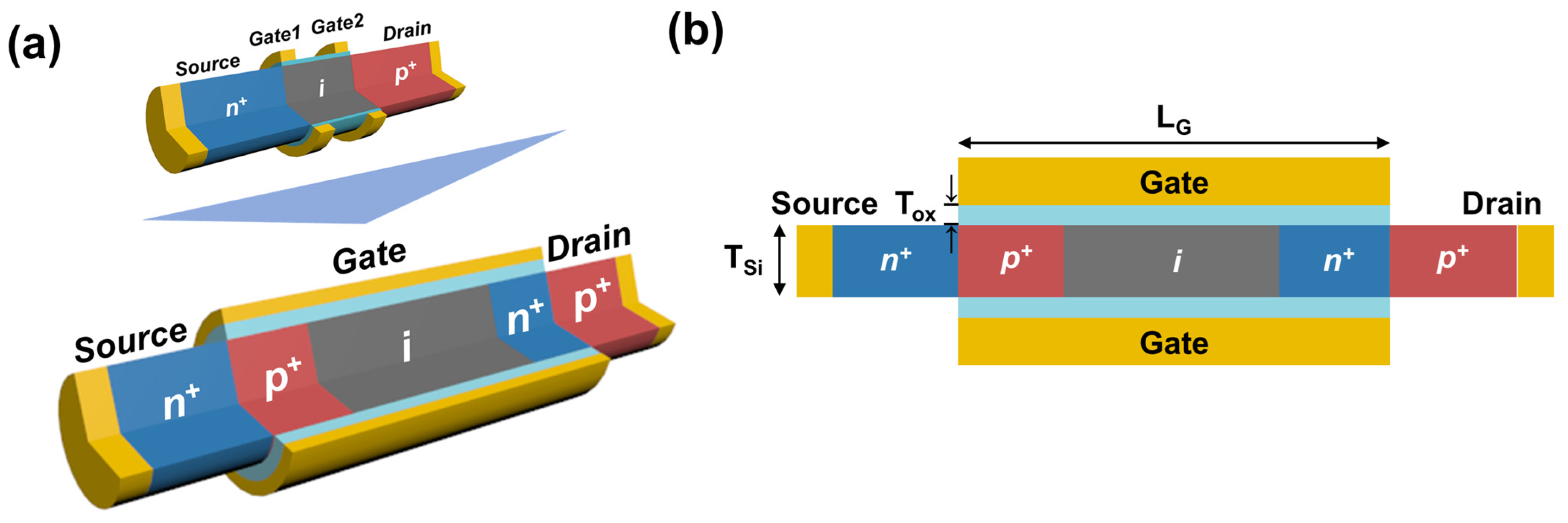

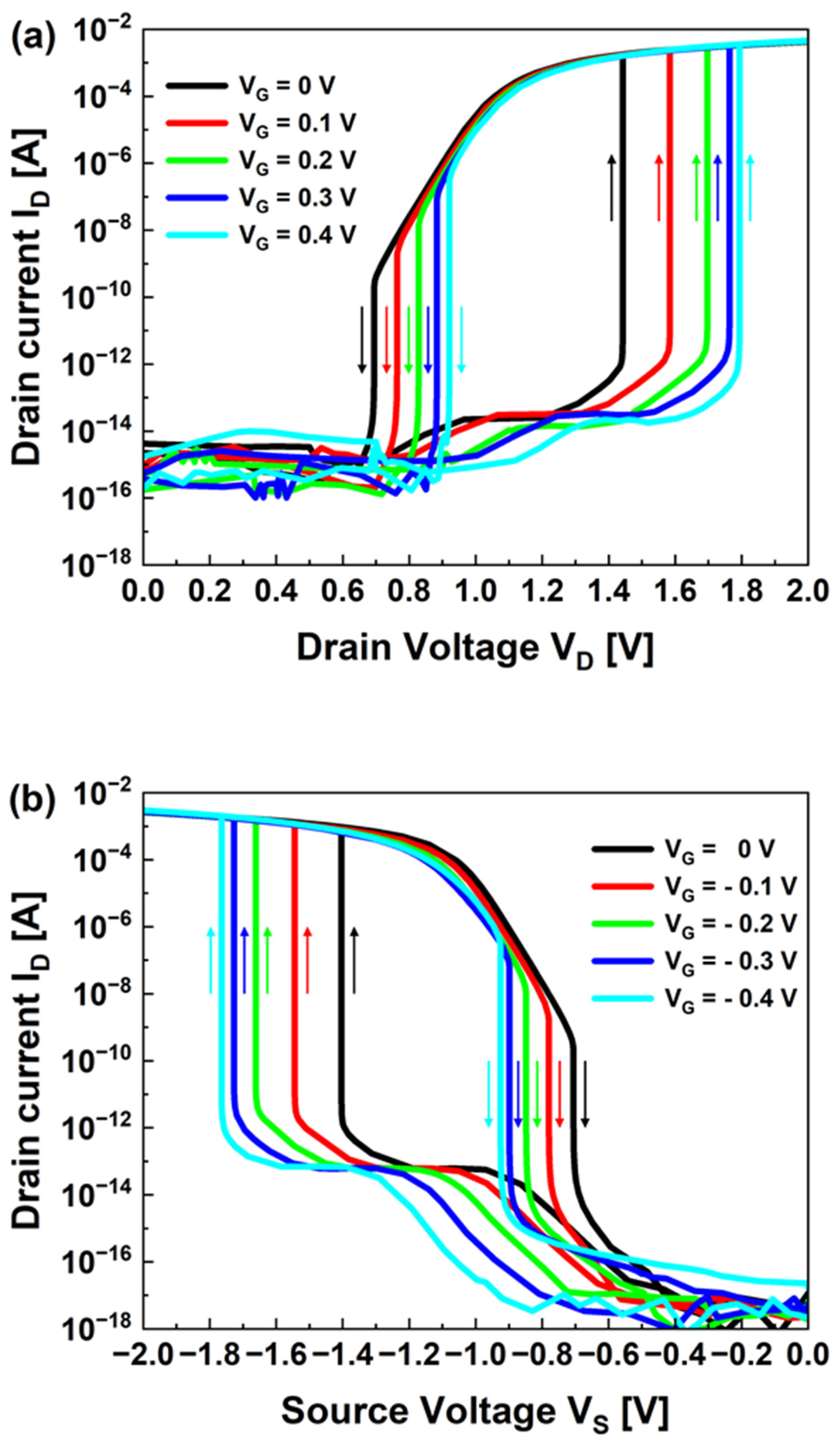

2. Device Structure and Simulation

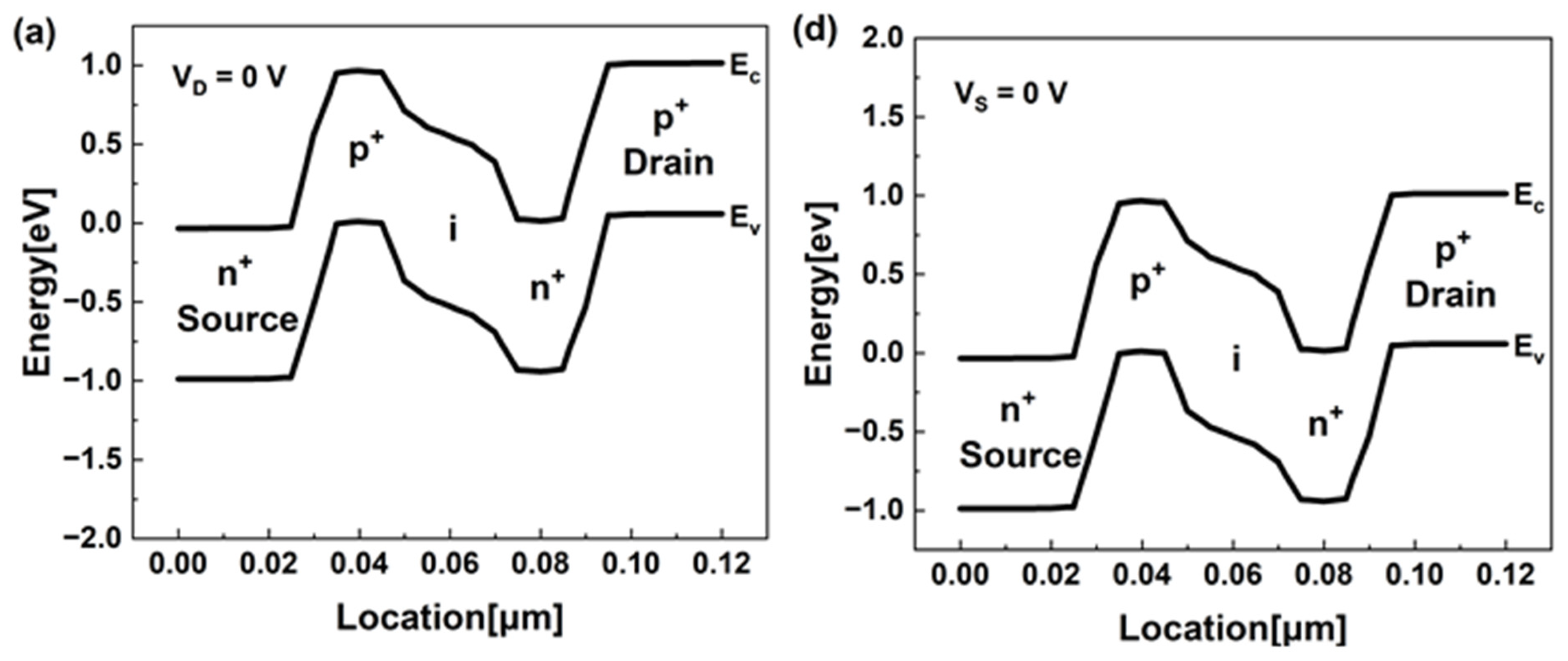

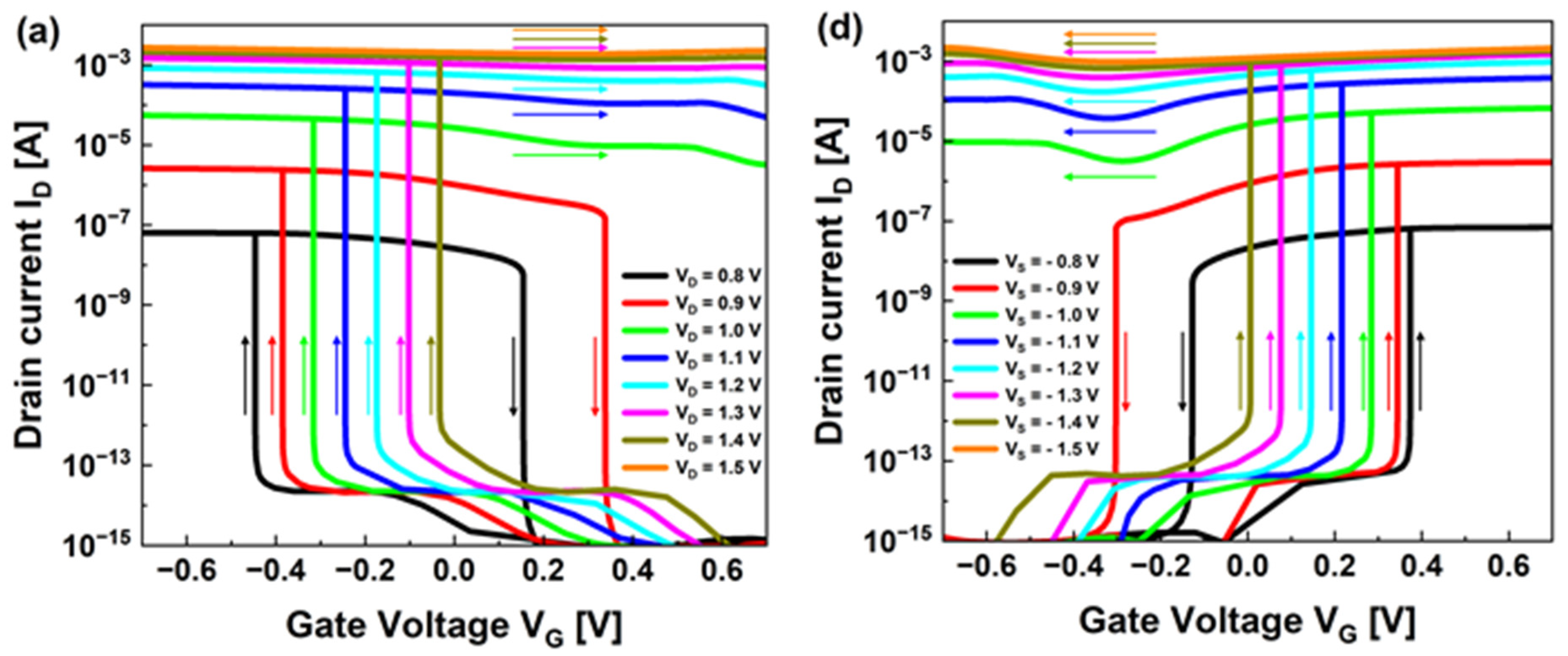

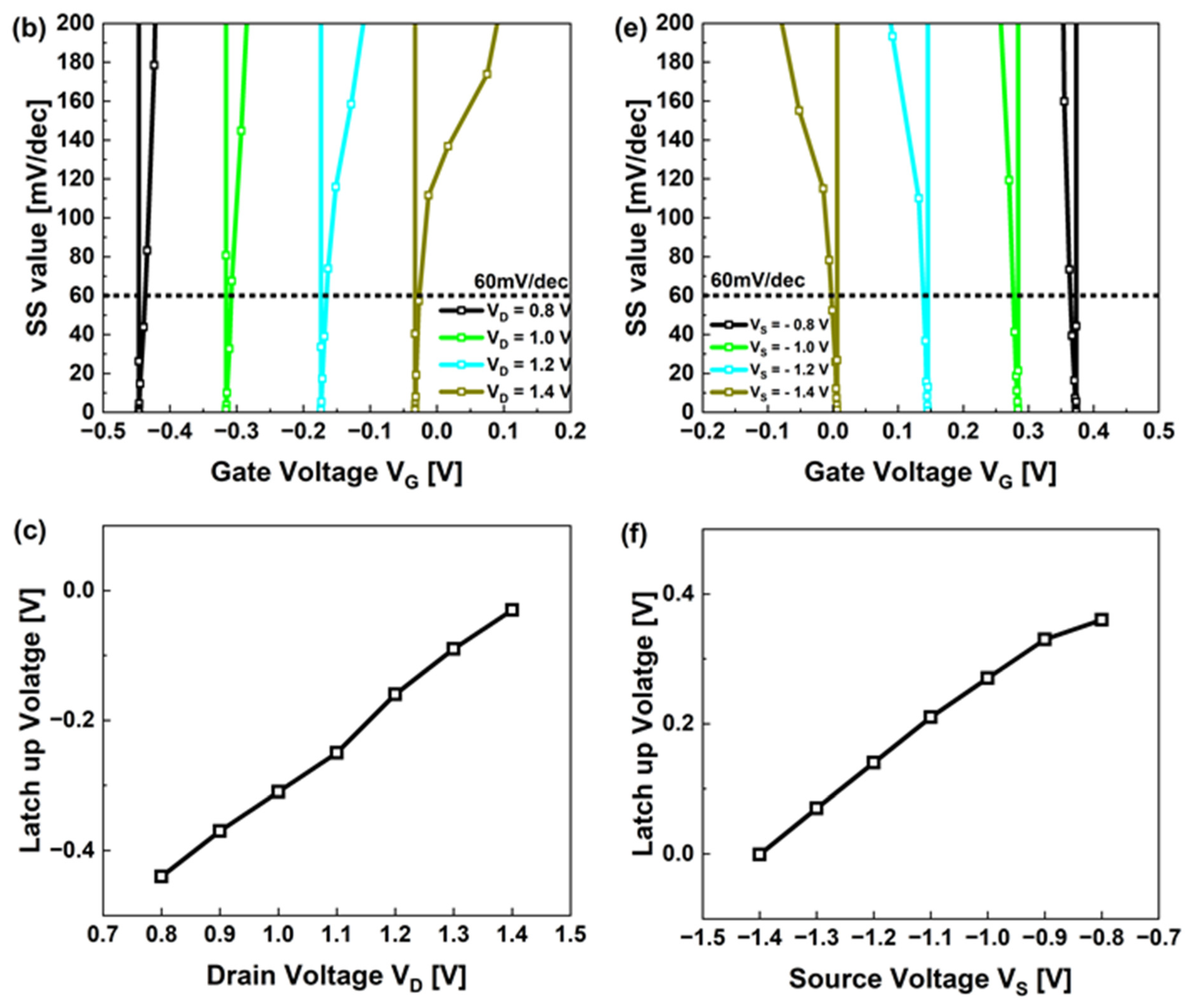

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Moore, G.E. Cramming More Components onto Integrated Circuits, Reprinted from Electronics, Volume 38, Number 8, April 19, 1965, Pp.114 Ff. IEEE Solid-State Circuits Soc. Newsl. 2006, 11, 33–35. [Google Scholar] [CrossRef]

- Khanna, V.K. (Ed.) Short-Channel Effects in MOSFETs BT—Integrated Nanoelectronics: Nanoscale CMOS, Post-CMOS and Allied Nanotechnologies; Springer: New Delhi, India, 2016; pp. 73–93. ISBN 978-81-322-3625-2. [Google Scholar]

- Lim, D.; Kim, M.; Kim, Y.; Kim, S. Memory Characteristics of Silicon Nanowire Transistors Generated by Weak Impact Ionization. Sci. Rep. 2017, 7, 12436. [Google Scholar] [CrossRef] [PubMed]

- Knoch, J.; Mantl, S.; Appenzeller, J. Impact of the Dimensionality on the Performance of Tunneling FETs: Bulk versus One-Dimensional Devices. Solid State Electron. 2007, 51, 572–578. [Google Scholar] [CrossRef]

- Datta, S.; Liu, H.; Narayanan, V. Tunnel FET Technology: A Reliability Perspective. Microelectron. Reliab. 2014, 54, 861–874. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-Gate Tunnel FET with High-k Gate Dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, S.; Park, B.-G. Double-Gate TFET with Vertical Channel Sandwiched by Lightly Doped Si. IEEE Trans. Electron Devices 2019, 66, 1656–1661. [Google Scholar] [CrossRef]

- Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. A Novel Biasing Scheme for I-MOS (Impact-Ionization MOS) Devices. IEEE Trans. Nanotechnol. 2005, 4, 322–325. [Google Scholar] [CrossRef]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. I-MOS: A Novel Semiconductor Device with a Subthreshold Slope Lower than KT/Q. In Proceedings of the Digest, International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 289–292. [Google Scholar]

- Hoeneisen, B.; Mead, C.A. Fundamental Limitations in Microelectronics—I. MOS Technology. Solid State Electron. 1972, 15, 819–829. [Google Scholar] [CrossRef]

- Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. 100-Nm n-/p-Channel I-MOS Using a Novel Self-Aligned Structure. IEEE Electron Device Lett. 2005, 26, 261–263. [Google Scholar] [CrossRef]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A Novel Transistor Exhibiting Steep Switching Behavior at Low Bias Voltages. In Proceedings of the Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Jeon, Y.; Kim, M.; Lim, D.; Kim, S. Steep Subthreshold Swing N- and p-Channel Operation of Bendable Feedback Field-Effect Transistors with P+–i–N+ Nanowires by Dual-Top-Gate Voltage Modulation. Nano Lett. 2015, 15, 4905–4913. [Google Scholar] [CrossRef]

- Lim, D.; Kim, S. Polarity Control of Carrier Injection for Nanowire Feedback Field-Effect Transistors. Nano Res. 2019, 12, 2509–2514. [Google Scholar] [CrossRef]

- Choi, S.; Son, J.; Cho, K.; Kim, S. One-Transistor Static Random-Access Memory Cell Array Comprising Single-Gated Feedback Field-Effect Transistors. Sci. Rep. 2021, 11, 17983. [Google Scholar] [CrossRef] [PubMed]

- Wan, J.; Royer, C.L.; Zaslavsky, A.; Cristoloveanu, S. A Compact Capacitor-Less High-Speed DRAM Using Field Effect-Controlled Charge Regeneration. IEEE Electron Device Lett. 2012, 33, 179–181. [Google Scholar] [CrossRef]

- Yang, Y.; Park, Y.-S.; Son, J.; Cho, K.; Kim, S. Simulation Studies on Electrical Characteristics of Silicon Nanowire Feedback Field-Effect Transistors with Interface Trap Charges. Sci. Rep. 2021, 11, 18650. [Google Scholar] [CrossRef]

- Lim, D.; Son, J.; Cho, K.; Kim, S. Quasi-Nonvolatile Silicon Memory Device. Adv. Mater. Technol. 2020, 5, 2000915. [Google Scholar] [CrossRef]

- Lim, D.; Cho, K.; Kim, S. Reconfigurable Logic-in-Memory Using Silicon Transistors. Adv. Mater. Technol. 2022, 7, 2101504. [Google Scholar] [CrossRef]

- Wan, J.; Royer, C.L.; Zaslavsky, A.; Cristoloveanu, S. A Systematic Study of the Sharp-Switching Z2-FET Device: From Mechanism to Modeling and Compact Memory Applications. Solid State Electron. 2013, 90, 2–11. [Google Scholar] [CrossRef]

- Solaro, Y.; Wan, J.; Fonteneau, P.; Fenouillet-Beranger, C.; Le Royer, C.; Zaslavsky, A.; Ferrari, P.; Cristoloveanu, S. Z2-FET: A Promising FDSOI Device for ESD Protection. Solid State Electron. 2014, 97, 23–29. [Google Scholar] [CrossRef]

- Yeung, C.W.; Padilla, A.; Liu, T.-J.K.; Hu, C. Programming Characteristics of the Steep Turn-on/off Feedback FET (FBFET). In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 176–177. [Google Scholar]

- Jeon, Y.; Kim, M.; Kim, Y.; Kim, S. Switching Characteristics of Nanowire Feedback Field-Effect Transistors with Nanocrystal Charge Spacers on Plastic Substrates. ACS Nano 2014, 8, 3781–3787. [Google Scholar] [CrossRef]

- Jeon, J.; Woo, S.; Cho, K.; Kim, S. Logic and Memory Functions of an Inverter Comprising Reconfigurable Double Gated Feedback Field Effect Transistors. Sci. Rep. 2022, 12, 12534. [Google Scholar] [CrossRef]

- Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W.M. Reconfigurable Silicon Nanowire Transistors. Nano Lett. 2012, 12, 119–124. [Google Scholar] [CrossRef] [PubMed]

- Simon, M.; Liang, B.; Fischer, D.; Knaut, M.; Tahn, A.; Mikolajick, T.; Weber, W.M. Top-Down Fabricated Reconfigurable FET with Two Symmetric and High-Current On-States. IEEE Electron Device Lett. 2020, 41, 1110–1113. [Google Scholar] [CrossRef]

- Weber, W.M.; Heinzig, A.; Trommer, J.; Martin, D.; Grube, M.; Mikolajick, T. Reconfigurable Nanowire Electronics—A Review. Solid State Electron. 2014, 102, 12–24. [Google Scholar] [CrossRef]

- Trommer, J.; Heinzig, A.; Mühle, U.; Löffler, M.; Winzer, A.; Jordan, P.M.; Beister, J.; Baldauf, T.; Geidel, M.; Adolphi, B.; et al. Enabling Energy Efficiency and Polarity Control in Germanium Nanowire Transistors by Individually Gated Nanojunctions. ACS Nano 2017, 11, 1704–1711. [Google Scholar] [CrossRef]

- Glassner, S.; Zeiner, C.; Periwal, P.; Baron, T.; Bertagnolli, E.; Lugstein, A. Multimode Silicon Nanowire Transistors. Nano Lett. 2014, 14, 6699–6703. [Google Scholar] [CrossRef] [PubMed]

- Silvaco Inc. Atlas User’s Manual; Silvaco Inc.: Santa Clara, CA, USA, 2016; p. 89. [Google Scholar]

- Singh, G.; Amin, S.I.; Anand, S.; Sarin, R.K. Design of Si0.5Ge0.5 Based Tunnel Field Effect Transistor and Its Performance Evaluation. Superlattices Microstruct. 2016, 92, 143–156. [Google Scholar] [CrossRef]

- Anam, A.; Amin, S.I.; Prasad, D.; Kumar, N.; Anand, S. Charge-Plasma-Based Inverted T-Shaped Source-Metal Dual-Line Tunneling FET with Improved Performance at 0.5 V Operation. Phys. Scr. 2023, 98, 95918. [Google Scholar] [CrossRef]

- Singh, S.; Raman, A. Gate-All-Around Charge Plasma-Based Dual Material Gate-Stack Nanowire FET for Enhanced Analog Performance. IEEE Trans. Electron Devices 2018, 65, 3026–3032. [Google Scholar] [CrossRef]

- Anand, S.; Amin, S.I.; Sarin, R.K. Analog Performance Investigation of Dual Electrode Based Doping-Less Tunnel FET. J. Comput. Electron. 2016, 15, 94–103. [Google Scholar] [CrossRef]

| Ref. | Features | Channel Size | SS min (mV/dec) | Ion | Ion/Ioff | Year | |||

|---|---|---|---|---|---|---|---|---|---|

| p | n | p | n | p | n | ||||

| [13] | Si NW, plastic substrate, dual top gate, bending compatible | L = 5 m H = 150 nm | 10 | 18 | ~10−5 | ~106 | 2015 | ||

| [14] | p+-i-n+ with two separate gates, SiNW FET | L = 4 m W = 30 nm | 1.78 | 1.36 | ~10−3 | ~105 | 2019 | ||

| [24] | p+-i-n+ with two separate gates (program gate, control gate), SINW FET | L = 200 nm W(Tsi) = 12 nm | 0.4 | ~10−6 | ~1012 | 2022 | |||

| this work | n+-p+-i-n+-p+ with single gate, SINW FET | L = 60 nm W(Tsi) = 10 nm | 8.2 × 10−8 | 5.9 × 10−8 | ~1.5 × 10−3 | ~1010 | 2023 | ||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, Y.; Lim, D. Reconfigurable Feedback Field-Effect Transistors with a Single Gate. Nanomaterials 2023, 13, 3133. https://doi.org/10.3390/nano13243133

Lee Y, Lim D. Reconfigurable Feedback Field-Effect Transistors with a Single Gate. Nanomaterials. 2023; 13(24):3133. https://doi.org/10.3390/nano13243133

Chicago/Turabian StyleLee, Yoocheon, and Doohyeok Lim. 2023. "Reconfigurable Feedback Field-Effect Transistors with a Single Gate" Nanomaterials 13, no. 24: 3133. https://doi.org/10.3390/nano13243133

APA StyleLee, Y., & Lim, D. (2023). Reconfigurable Feedback Field-Effect Transistors with a Single Gate. Nanomaterials, 13(24), 3133. https://doi.org/10.3390/nano13243133