Steep-Slope and Hysteresis-Free MoS2 Negative-Capacitance Transistors Using Single HfZrAlO Layer as Gate Dielectric

Abstract

:1. Introduction

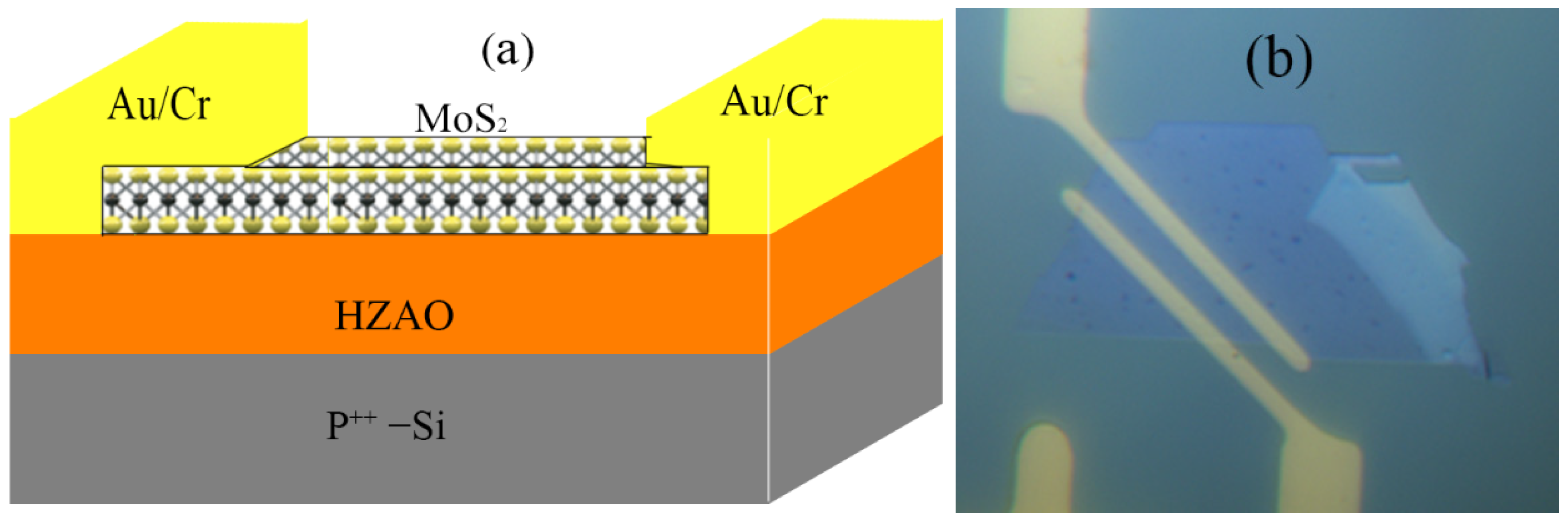

2. Experimental Method

3. Results and Discussion

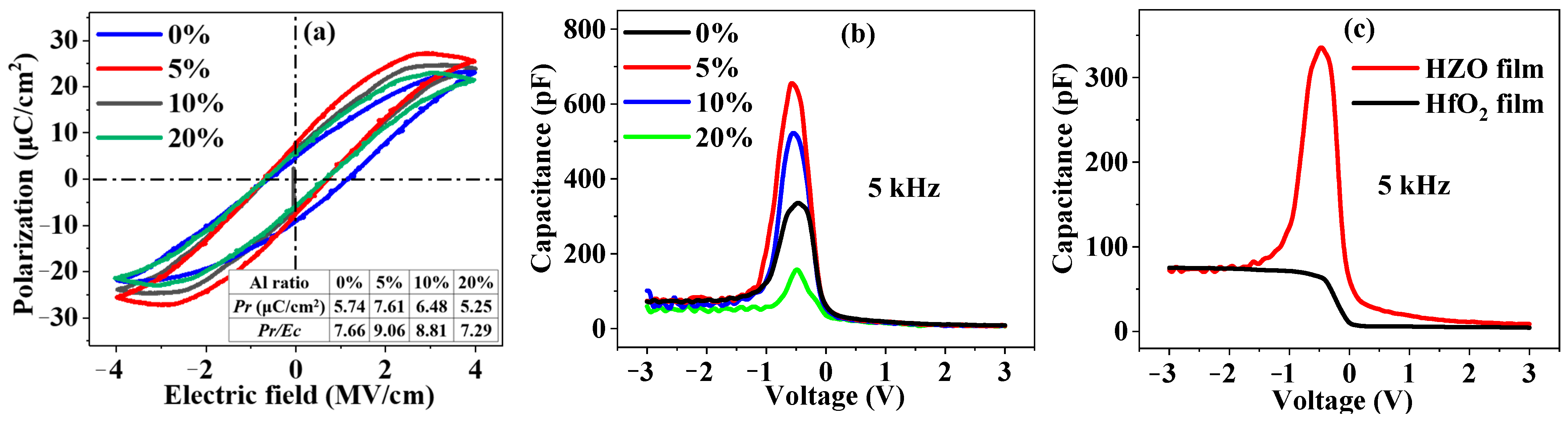

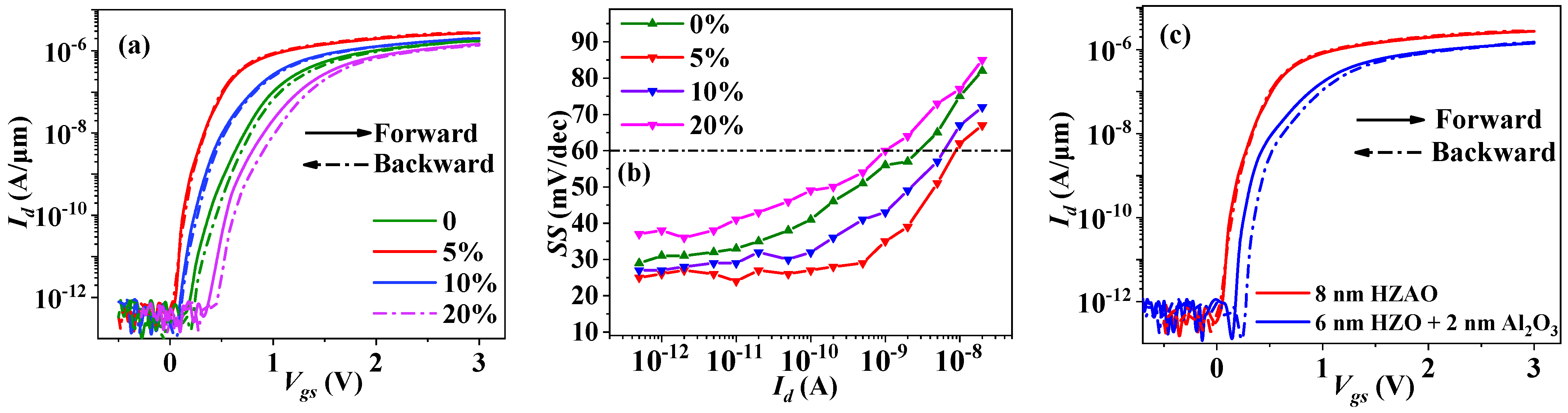

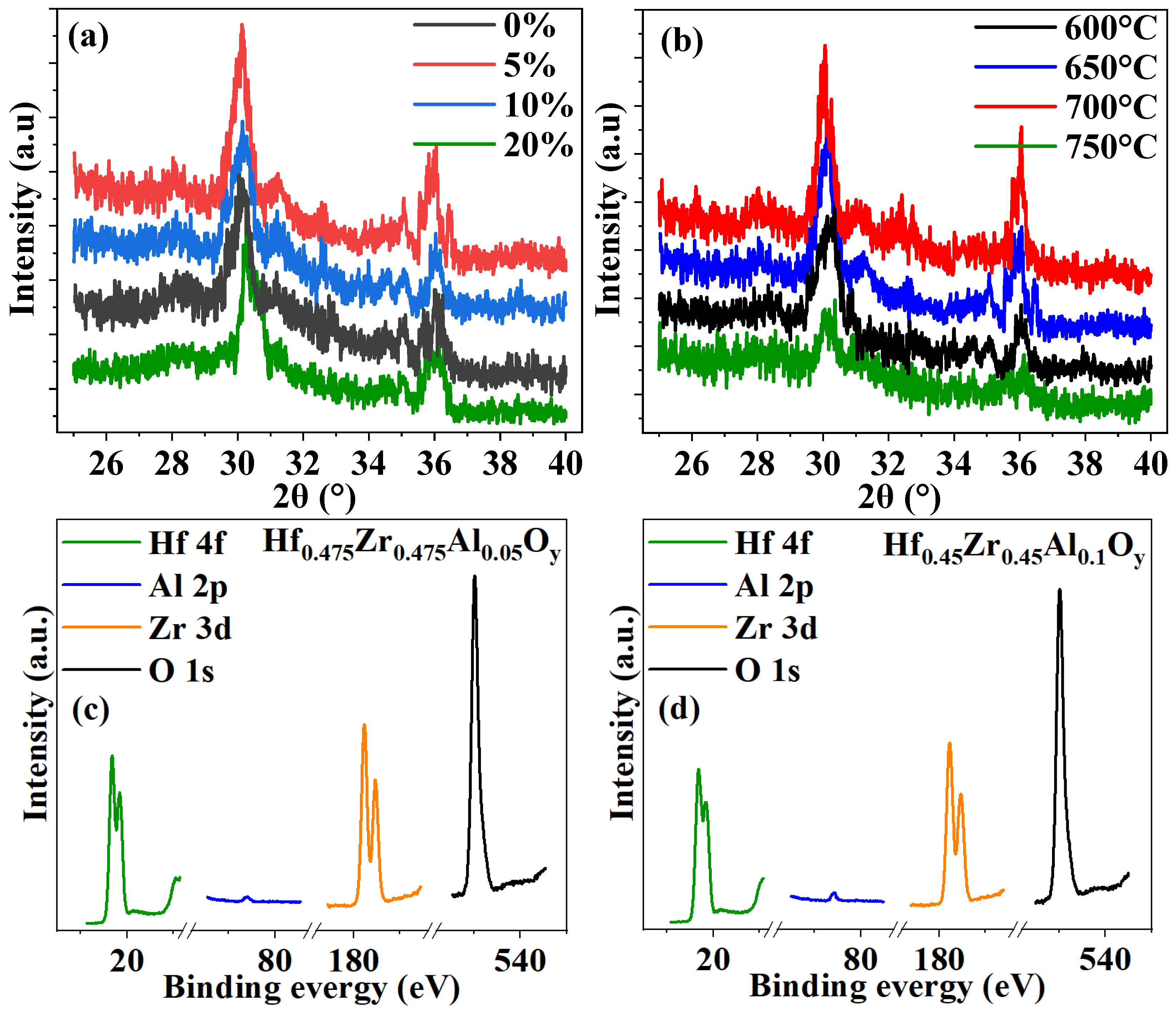

3.1. Optimization of Al Content in HZAO Thin Film

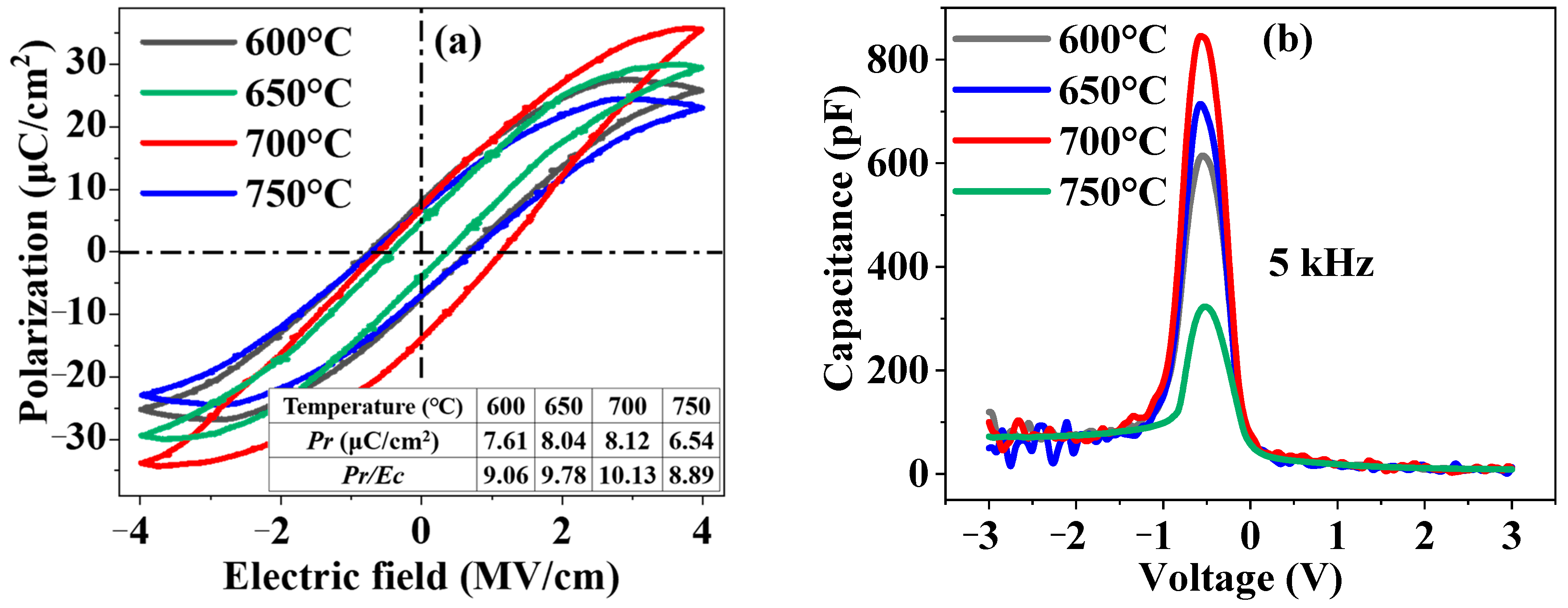

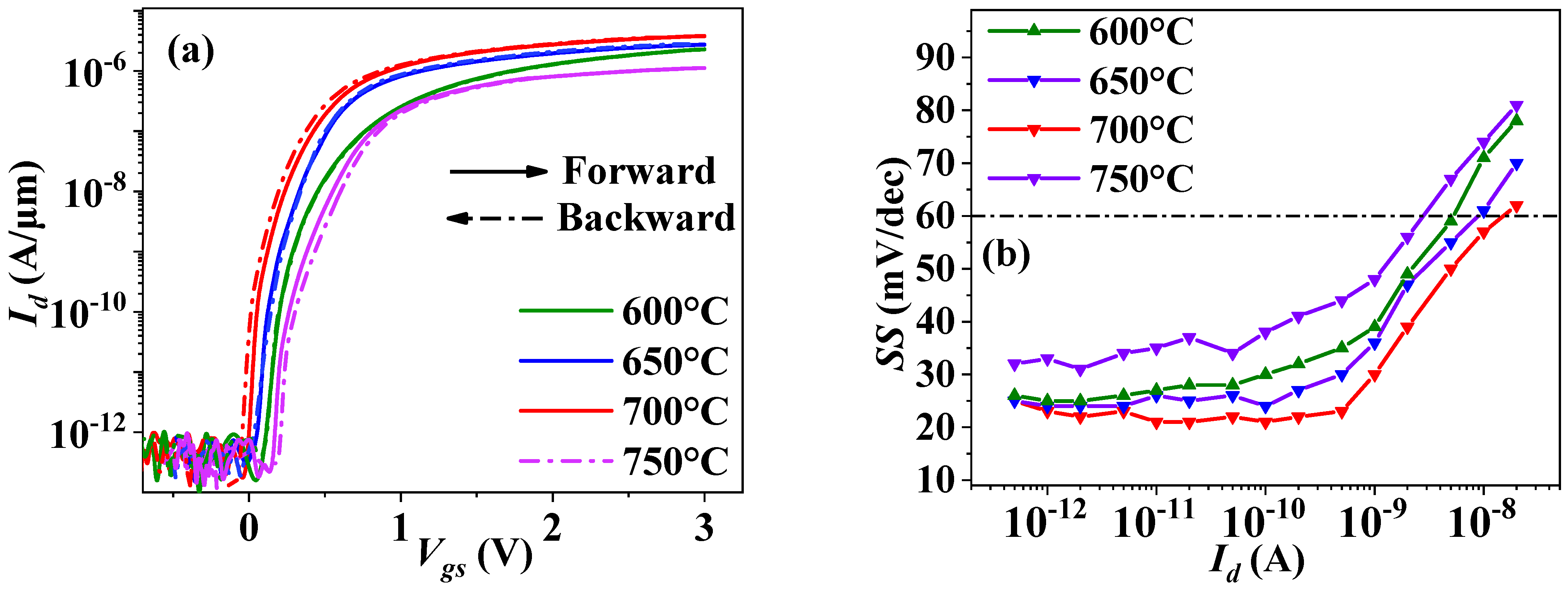

3.2. Optimization of Annealing Temperature

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. Nano Lett. 2008, 8, 405–410. [Google Scholar] [CrossRef] [PubMed]

- Krivokapic, Z.; Aziz, A.; Song, D.; Rana, U.; Galatage, R.; Banna, S. NCFET: Opportunities & challenges for advanced technology nodes. In Proceedings of the 2017 Fifth Berkeley Symposium on Energy Efficient Electronic Systems & Steep Transistors Workshop (E3S), Berkeley, CA, USA, 19–20 October 2017. [Google Scholar] [CrossRef]

- You, W.; Su, P. Design space exploration considering back-gate biasing effects for negative-capacitance transi-tion-metal-dichalcogenide (TMD) field-effect transistors. In Proceedings of the 2017 IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Toyama, Japan, 28 February–2 March 2017; pp. 136–137. [Google Scholar]

- Rusu, A.; Salvatore, G.A.; Jiménez, D.; Ionescu, A.M. Metal-Ferroelectric-Meta-Oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 16.3.1–16.3.4. [Google Scholar] [CrossRef]

- Rollo, T.; Esseni, D. Energy Minimization and Kirchhoff’s Laws in Negative Capacitance Ferroelectric Capacitors and MOSFETs. IEEE Electron Device Lett. 2017, 38, 814–817. [Google Scholar] [CrossRef]

- Zang, X.; Zhou, Q.; Chang, J.; Liu, Y.; Lin, L. Graphene and carbon nanotube (CNT) in MEMS/NEMS applications. Microelectron. Eng. 2015, 132, 192–206. [Google Scholar] [CrossRef]

- Abele, N.; Fritschi, R.; Boucart, K.; Casset, F.; Ancey, P.; Ionescu, A. Suspended-gate MOSFET: Bringing new MEMS functionality into solid-state MOS transistor. In Proceedings of the IEDM 2015, IEEE International Electron Devices Meeting, Washington, DC, USA, 5 December 2005; pp. 479–481. [Google Scholar] [CrossRef]

- Villalon, A.; Le Carval, G.; Martinie, S.; Le Royer, C.; Jaud, M.-A.; Cristoloveanu, S. Further Insights in TFET Operation. IEEE Trans. Electron Devices 2014, 61, 2893–2898. [Google Scholar] [CrossRef]

- Revelant, A.; Villalon, A.; Wu, Y.; Zaslavsky, A.; Le Royer, C.; Iwai, H.; Cristoloveanu, S. Electron-Hole Bilayer TFET: Experiments and Comments. IEEE Trans. Electron Devices 2014, 61, 2674–2681. [Google Scholar] [CrossRef]

- Ilatikhameneh, H.; Tan, Y.; Novakovic, B.; Klimeck, G.; Rahman, R.; Appenzeller, J. Tunnel Field-Effect Transistors in 2-D Transition Metal Dichalcogenide Materials. IEEE J. Explor. Solid-State Comput. Devices Circuits 2015, 1, 12–18. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef]

- Yadav, A.K.; Nguyen, K.X.; Hong, Z.; García-Fernández, P.; Aguado-Puente, P.; Nelson, C.T.; Das, S.; Prasad, B.; Kwon, D.; Cheema, S.; et al. Spatially resolved steady-state negative capacitance. Nature 2019, 565, 468–471. [Google Scholar] [CrossRef] [Green Version]

- Chen, K.-T.; Lo, C.; Chen, P.-G.; Liao, M.-H.; Li, K.-S.; Chang, S.-T.; Lee, M.-H.; Gu, S.-S.; Wang, Z.-Y.; Liao, C.-Y.; et al. Ferroelectric HfZrOx FETs on SOI Substrate with Reverse-DIBL (Drain-Induced Barrier Lowering) and NDR (Negative Differential Resistance). IEEE J. Electron Devices Soc. 2018, 6, 900–904. [Google Scholar] [CrossRef]

- McGuire, F.A.; Lin, Y.-C.; Price, K.; Rayner, G.B.; Khandelwal, S.; Salahuddin, S.; Franklin, A.D. Sustained Sub-60 mV/decade Switching via the Negative Capacitance Effect in MoS2 Transistors. Nano Lett. 2017, 17, 4801–4806. [Google Scholar] [CrossRef]

- Müller, J.; Schröder, U.; Böscke, T.S.; Müller, I.; Bottger, U.; Wilde, L.; Sundqvist, J.; Lemberger, M.; Kucher, P.; Mikolajick, T.; et al. Ferroelectricity in yttrium-doped hafnium oxide. J. Appl. Phys. 2011, 110, 114113. [Google Scholar] [CrossRef] [Green Version]

- Mueller, S.; Mueller, J.; Singh, A.; Riedel, S.; Sundqvist, J.; Schroeder, U.; Mikolajick, T. Incipient Ferroelectricity in Al-Doped HfO2 Thin Films. Adv. Funct. Mater. 2012, 22, 2412–2417. [Google Scholar] [CrossRef]

- Böscke, T.S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 2011, 99, 102903. [Google Scholar] [CrossRef]

- Boscke, T.S.; Muller, J.; Brauhaus, D.; Schroder, U.; Bottger, U. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011. [Google Scholar] [CrossRef]

- Müller, J.; Böscke, T.S.; Schröder, U.; Mueller, S.; Bräuhaus, D.; Böttger, U.; Frey, L.; Mikolajick, T. Ferroelectricity in Simple Binary ZrO2 and HfO2. Nano Lett. 2012, 12, 4318–4323. [Google Scholar] [CrossRef] [PubMed]

- Lee, M.H.; Wei, Y.-T.; Chu, K.-Y.; Huang, J.-J.; Chen, C.-W.; Cheng, C.-C.; Chen, M.-J.; Lee, H.-Y.; Chen, Y.-S.; Lee, L.-H.; et al. Steep Slope and Near Non-Hysteresis of FETs With Antiferroelectric-Like HfZrO for Low-Power Electronics. IEEE Electron Device Lett. 2015, 36, 294–296. [Google Scholar] [CrossRef]

- Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar] [CrossRef]

- Peng, Y.; Liu, Y.; Han, G.; Zhang, J.; Hao, Y. Germanium Negative Capacitance Field Effect Transistors: Impacts of Zr Composition in Hf1−xZrxO2. Nanoscale Res. Lett. 2019, 14, 125. [Google Scholar] [CrossRef]

- Riedel, S.; Polakowski, P.; Müller, J. A thermally robust and thickness independent ferroelectric phase in laminated hafnium zirconium oxide. AIP Adv. 2016, 6, 095123. [Google Scholar] [CrossRef] [Green Version]

- Kang, J.; Liu, W.; Banerjee, K. High-performance MoS2 transistors with low-resistance molybdenum contacts. Appl. Phys. Lett. 2014, 104, 093106. [Google Scholar] [CrossRef] [Green Version]

- Sibhatu, A.K.; Teshome, T.; Akin-Ojo, O.; Yimam, A.; Asres, G.A. DFT investigation of the electronic and optical properties of hexagonal MX2/ZrXO (M = W, Mo and X = S, Se) van der Waals heterostructures for photovoltaic solar cell application. RSC Adv. 2022, 12, 30838–30845. [Google Scholar] [CrossRef]

- Guo, Y.; Liu, D.; Robertson, J. 3D Behavior of Schottky Barriers of 2D Transition-Metal Dichalcogenides. ACS Appl. Mater. Interfaces 2015, 7, 25709–25715. [Google Scholar] [CrossRef] [Green Version]

- Szczęśniak, D.; Hoehn, R.D.; Kais, S. Canonical Schottky barrier heights of transition metal dichalcogenide monolayers in contact with a metal. Phys. Rev. B 2018, 97, 195315. [Google Scholar] [CrossRef] [Green Version]

- Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Electrical characterization of back-gated bi-layer MoS2 field-effect transistors and the effect of ambient on their performances. Appl. Phys. Lett. 2012, 100, 123104. [Google Scholar] [CrossRef]

- Khan, A.I.; Yeung, C.W.; Hu, C.; Salahuddin, S. Ferroelectric Negative Capacitance MOSFET: Capacitance Tuning & An-tiferroelectric Operation. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011. [Google Scholar] [CrossRef]

- Li, T.; Wan, B.; Du, G.; Zhang, B.; Zeng, Z. Electrical performance of multilayer MoS2 transistors on high-κAl2O3coated Si substrates. AIP Adv. 2015, 5, 057102. [Google Scholar] [CrossRef]

- Li, J.; Zhou, J.; Han, G.; Liu, Y.; Peng, Y.; Zhang, J.; Sun, Q.-Q.; Zhang, D.W.; Hao, Y. Negative Capacitance Ge PFETs for Performance Improvement: Impact of Thickness of HfZrOx. IEEE Trans. Electron Devices 2018, 65, 1217–1222. [Google Scholar] [CrossRef]

- Zhou, J.; Zhou, Y.; Hao, Y.; Peng, Y.; Han, G.; Li, Q.; Liu, Y.; Zhang, J.; Liao, M.; Sun, Q.-Q.; et al. Hysteresis Reduction in Negative Capacitance Ge PFETs Enabled by Modulating Ferroelectric Properties in HfZrOx. IEEE J. Electron Devices Soc. 2017, 6, 41–48. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 2017, 5, 015014. [Google Scholar] [CrossRef] [Green Version]

- Alam, N.K.; Kaczer, B.; Ragnarsson, L.-A.; Popovici, M.; Rzepa, G.; Horiguchi, N.; Heyns, M.; Van Houdt, J. On the Characterization and Separation of Trapping and Ferroelectric Behavior in HfZrO FET. IEEE J. Electron Devices Soc. 2019, 7, 855–862. [Google Scholar] [CrossRef]

- Lee, M.H.; Wei, Y.-T.; Liu, C.; Huang, J.-J.; Tang, M.; Chueh, Y.-L.; Chu, K.-Y.; Chen, M.-J.; Lee, H.-Y.; Chen, Y.-S.; et al. Ferroelectricity of HfZrO2 in Energy Landscape with Surface Potential Gain for Low-Power Steep-Slope Transistors. IEEE J. Electron Devices Soc. 2015, 3, 377–381. [Google Scholar] [CrossRef]

- Zhang, X.; Chen, L.; Sun, Q.-Q.; Wang, L.-H.; Zhou, P.; Lu, H.-L.; Wang, P.-F.; Ding, S.-J.; Zhang, D.W. Inductive crystallization effect of atomic-layer-deposited Hf0.5Zr0.5O2 films for ferroelectric application. Nanoscale Res. Lett. 2015, 10, 25. [Google Scholar] [CrossRef] [Green Version]

- Park, M.H.; Kim, H.J.; Kim, Y.J.; Lee, W.; Moon, T.; Hwang, C.S. Evolution of phases and ferroelectric properties of thin Hf0.5Zr0.5O2 films according to the thickness and annealing temperature. Appl. Phys. Lett. 2013, 102, 242905. [Google Scholar] [CrossRef]

| Sample | Hf0.4Zr0.4Al0.2Oy | Hf0.45Zr0.45Al0.1Oy | Hf0.475Zr0.475Al0.05Oy | Hf0.5Zr0.5Oy |

|---|---|---|---|---|

| Ioff (pA/μm) | 0.3~1 | 0.3~1 | 0.3~1 | 0.3~1 |

| Ion (μA/μm) | 1.1~1.2 | 1.9~2.2 | 2.5~2.8 | 1.5~1.7 |

| Mobility (cm2/Vs) | 35.8~38.4 | 35.6~38.5 | 36.2~38.7 | 35.5~37.8 |

| SS (mV/dec) | 35.0~45.1 | 24.4~26.9 | 22.3~25.6 | 28.8~40.6 |

| Hysteresis (mV) | 30~50 | 15~20 | 5~10 | 20~30 |

| VTH (V) | 0.55~0.60 | 0.15~0.20 | 0.10~0.15 | 0.40~0.45 |

| Gate Stack | 8 nm HZAO | 6 nm HZO +2 nm Al2O3 |

|---|---|---|

| Ioff (pA/μm) | 0.3~1 | 0.3~1 |

| Ion (μA/μm) | 2.5~2.8 | 1.4~1.6 |

| Mobility (cm2/Vs) | 36.2~38.7 | 35.8~37.5 |

| SS (mV/dec) | 22.3~25.6 | 33.5~41.4 |

| Hysteresis (mV) | 5~10 | 40~50 |

| VTH (V) | 0.10~0.15 | 0.25~0.30 |

| T (°C) | 600 | 650 | 700 | 750 |

|---|---|---|---|---|

| Ioff (pA/μm) | 0.3~1 | 0.3~1 | 0.3~1 | 0.3~1 |

| Ion (μA/μm) | 2.5~2.8 | 2.4~2.6 | 2.5~2.8 | 1.5~1.7 |

| Mobility (cm2/Vs) | 36.2~38.7 | 36.6~38.3 | 36.4~38.7 | 35.2~37.4 |

| SS (mV/dec) | 22.3~25.6 | 22.3~25.6 | 20.4~23.1 | 30.3~40.7 |

| Hysteresis (mV) | 5~10 | 0 | −5~−10 | 40~50 |

| VTH (V) | 0.10~0.15 | 0.05~0.10 | 0~0.05 | 0.20~0.25 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tao, X.; Liu, L.; Xu, J. Steep-Slope and Hysteresis-Free MoS2 Negative-Capacitance Transistors Using Single HfZrAlO Layer as Gate Dielectric. Nanomaterials 2022, 12, 4352. https://doi.org/10.3390/nano12244352

Tao X, Liu L, Xu J. Steep-Slope and Hysteresis-Free MoS2 Negative-Capacitance Transistors Using Single HfZrAlO Layer as Gate Dielectric. Nanomaterials. 2022; 12(24):4352. https://doi.org/10.3390/nano12244352

Chicago/Turabian StyleTao, Xinge, Lu Liu, and Jingping Xu. 2022. "Steep-Slope and Hysteresis-Free MoS2 Negative-Capacitance Transistors Using Single HfZrAlO Layer as Gate Dielectric" Nanomaterials 12, no. 24: 4352. https://doi.org/10.3390/nano12244352

APA StyleTao, X., Liu, L., & Xu, J. (2022). Steep-Slope and Hysteresis-Free MoS2 Negative-Capacitance Transistors Using Single HfZrAlO Layer as Gate Dielectric. Nanomaterials, 12(24), 4352. https://doi.org/10.3390/nano12244352