Novel Modeling Approach to Analyze Threshold Voltage Variability in Short Gate-Length (15–22 nm) Nanowire FETs with Various Channel Diameters

Abstract

:1. Introduction

2. Device Structure and Modeling Methods

2.1. Structure and Possible Vth Variation Sources of SNWFETs

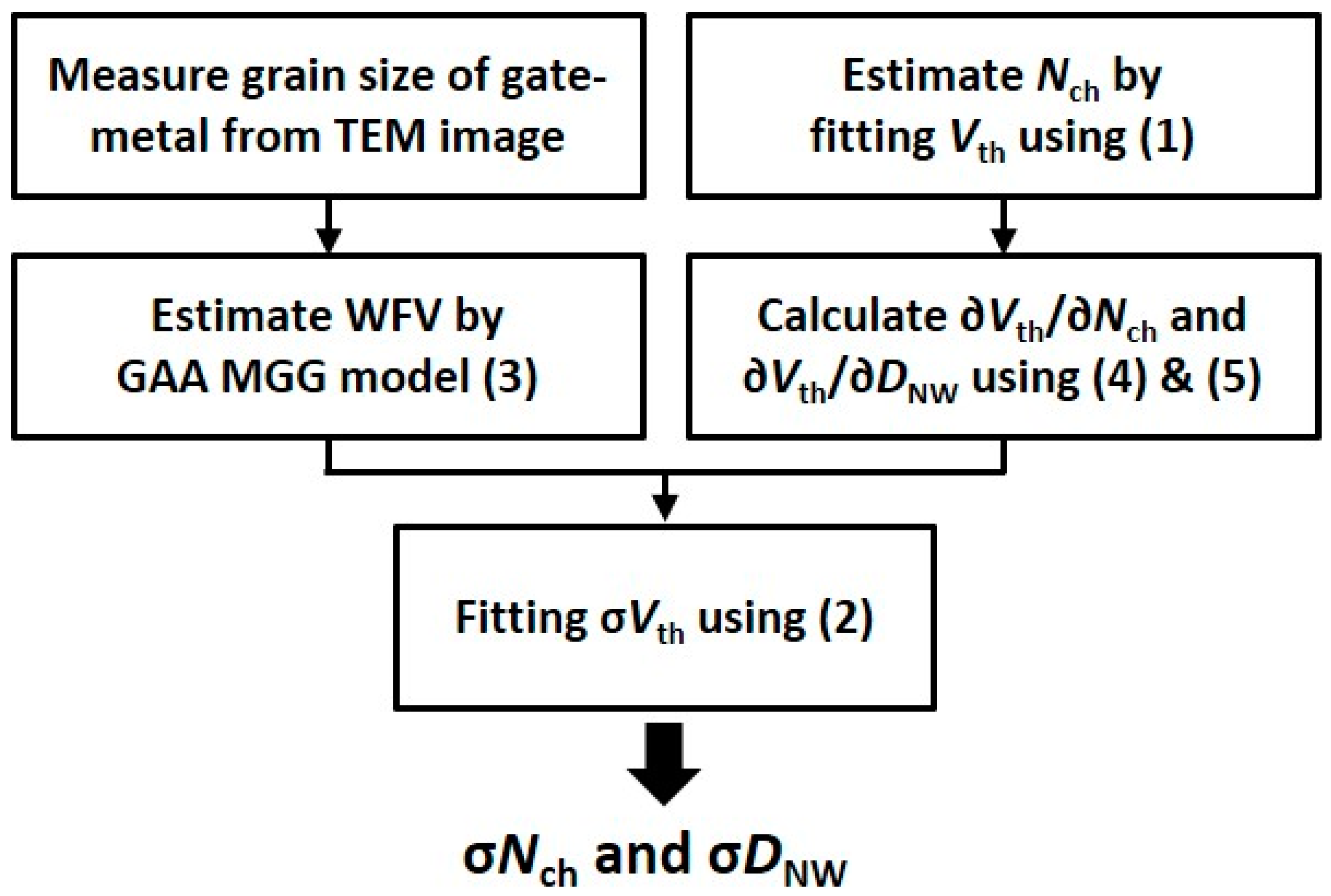

2.2. Proposed σVth Model of SNWFETs

3. Results and Discussion

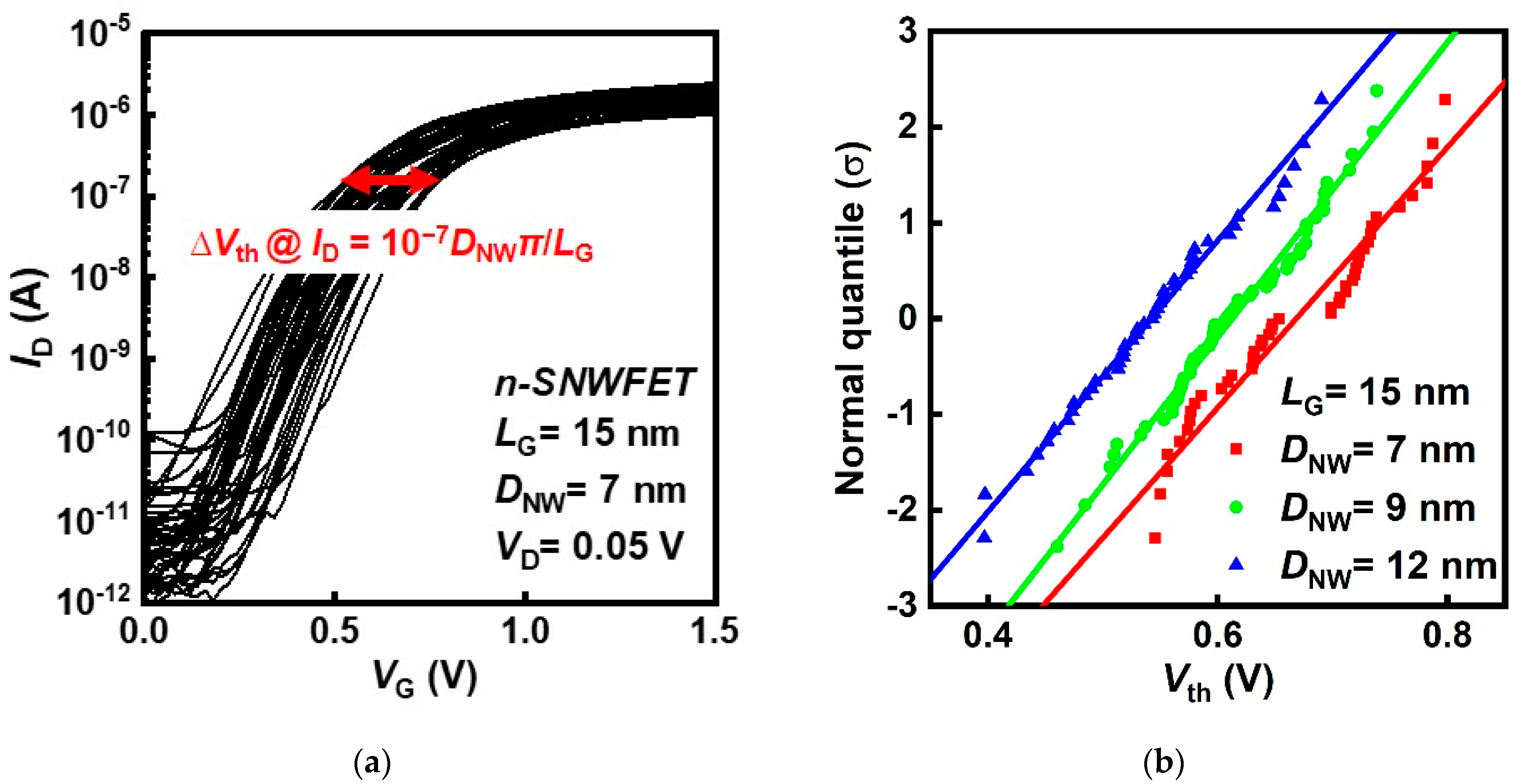

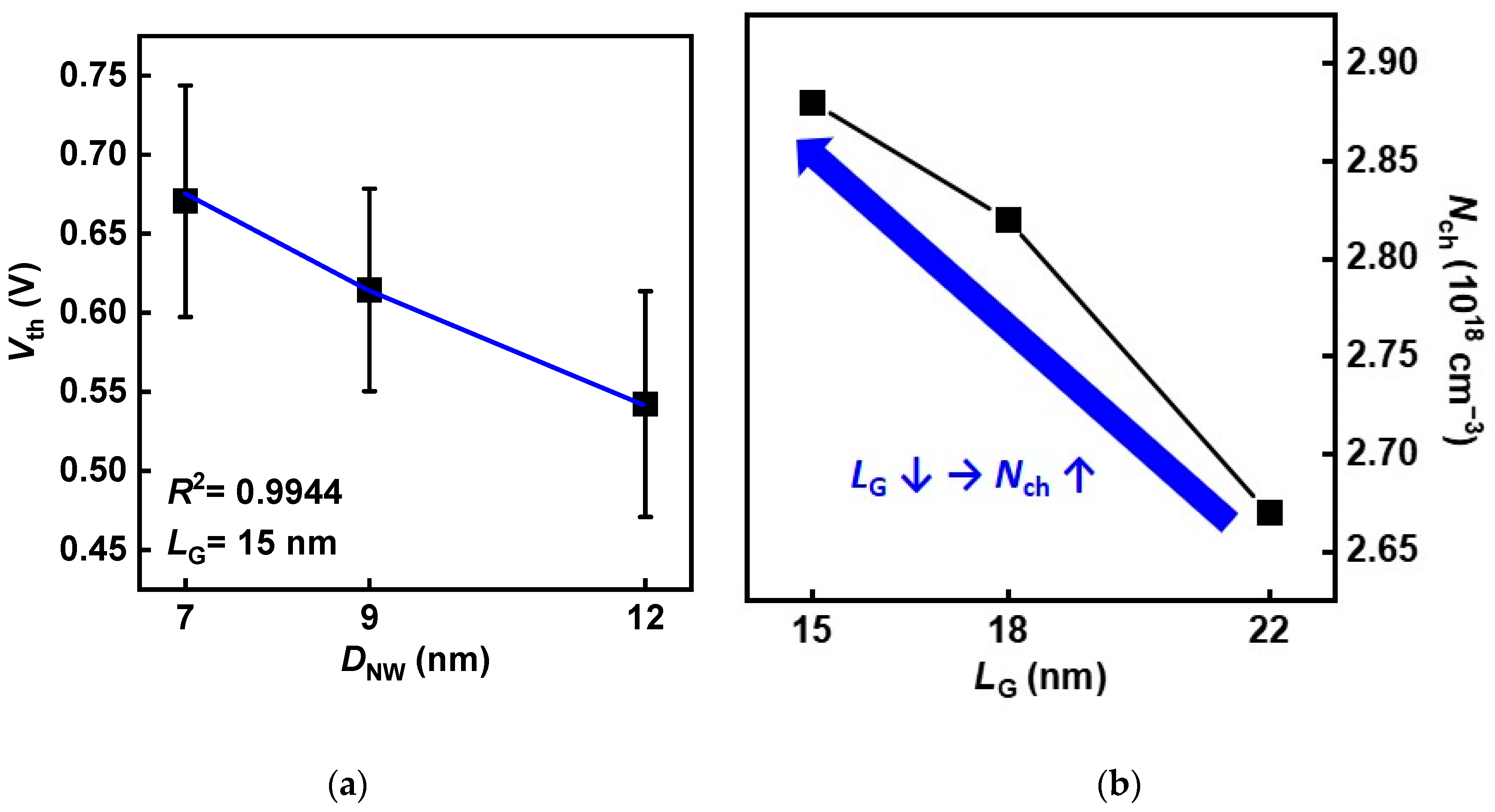

3.1. Vth Modeling Results of SNWFETs

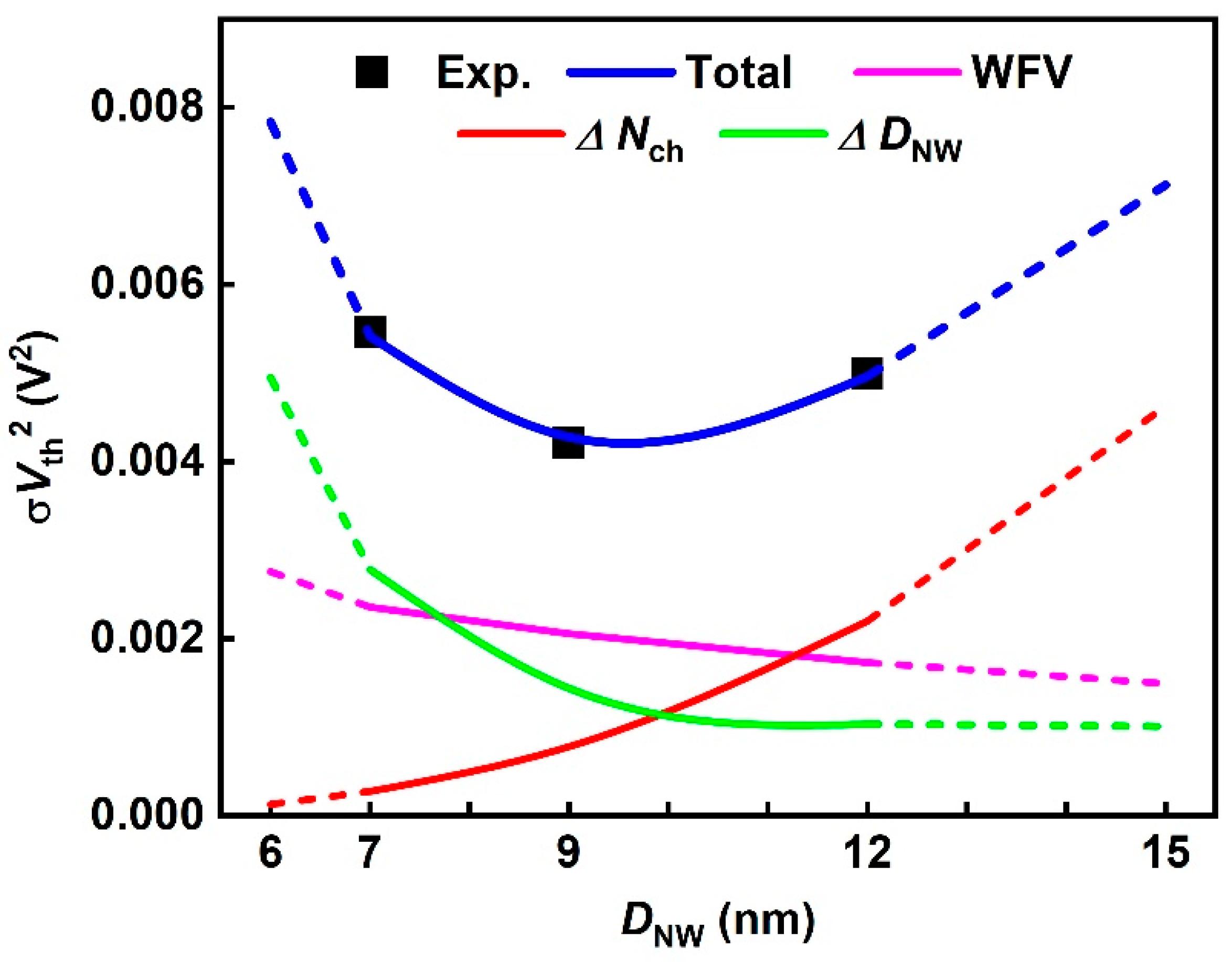

3.2. Vth Standard Deviation Modeling Results of SNWFETs

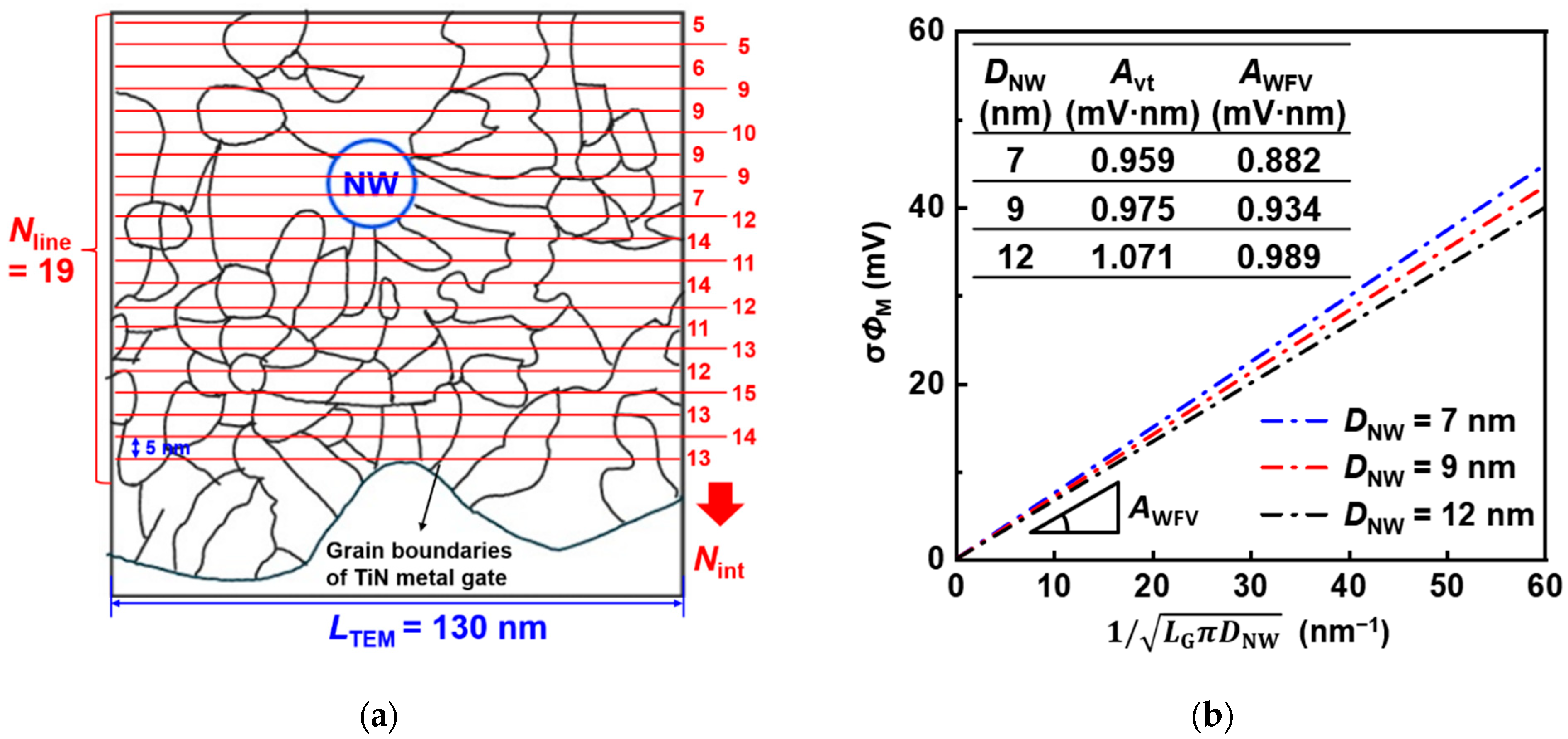

3.2.1. Extraction of Gsize and WFV of SNWFETs

3.2.2. The Contribution of Variation Sources to σVth for Each DNW

3.2.3. The Tendency of σNch and σDNW as LG Changes

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bardon, M.G.; Sherazi, Y.; Schuddinck, P.; Jang, D.; Yakimets, D.; Debacker, P.; Baert, R.; Mertens, H.; Badaroglu, M.; Mocuta, A.; et al. Extreme scaling enabled by 5 tracks cells: Holistic design-device co-optimization for FinFETs and lateral nanowires. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 28.2.1–28.2.4. [Google Scholar] [CrossRef]

- Li, J.; Li, Y.; Zhou, N.; Xiong, W.; Wang, G.; Zhang, Q.; Du, A.; Gao, J.; Kong, Z.; Lin, H.; et al. Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors. Nanomaterials 2020, 10, 793. [Google Scholar] [CrossRef] [PubMed]

- Cheng, X.; Li, Y.; Zhao, F.; Chen, A.; Liu, H.; Li, C.; Zhang, Q.; Yin, H.; Luo, J.; Wang, W. 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process. Nanomaterials 2022, 12, 889. [Google Scholar] [CrossRef] [PubMed]

- Pelgrom, M.J.M.; Duinmaijer, A.C.J.; Welbers, A.P.G. Matching properties of MOS transistors. J. Solid-State Circuits 1989, 24, 1433–1439. [Google Scholar] [CrossRef]

- Suk, S.D.; Yeoh, Y.Y.; Li, M.; Yeo, K.H.; Kim, S.H.; Kim, D.W.; Park, D.; Lee, W.-S. TSNWFET for SRAM cell application: Performance variation and process dependency. In Proceedings of the IEEE Symposium on VLSI Technology (VLSI), Honolulu, HI, USA, 18–20 June 2008; pp. 38–39. [Google Scholar] [CrossRef]

- Seoane, N.; Fernandez, J.G.; Kalna, K.; Comesaña, E.; García-Loureiro, A. Simulations of statistical variability in n-type FinFET, nanowire, and nanosheet FETs. IEEE Electron Device Lett. 2021, 42, 1416–1419. [Google Scholar] [CrossRef]

- Espiñeira, G.; Nagy, D.; Indalecio, G.; García-Loureiro, A.J.; Kalna, K.; Seoane, N. Impact of gate edge roughness variability on FinFET and gate-all-around nanowire FET. IEEE Electron Device Lett. 2019, 40, 510–513. [Google Scholar] [CrossRef] [Green Version]

- Spinelli, A.S.; Compagnoni, C.M.; Lacaita, A.L. Variability effects in nanowire and macaroni MOSFETs—Part I: Random dopant fluctuations. IEEE Trans. Electron Devices 2020, 67, 1485–1491. [Google Scholar] [CrossRef]

- Yoon, J.S.; Rim, T.; Kim, J.; Kim, K.; Baek, C.K.; Jeong, Y.H. Statistical variability study of random dopant fluctuation on gate-all-around inversion-mode silicon nanowire field-effect transistors. Appl. Phys. Lett. 2015, 106, 103507. [Google Scholar] [CrossRef] [Green Version]

- Bansal, A.K.; Gupta, C.; Gupta, A.; Singh, R.; Hook, T.B.; Dixit, A. 3-D LER and RDF matching performance of nanowire FETs in inversion, accumulation, and junctionless modes. IEEE Trans. Electron Devices 2018, 65, 1246–1252. [Google Scholar] [CrossRef]

- Li, Y.; Chang, H.T.; Lai, C.N.; Chao, P.J.; Chen, C.Y. Process variation effect, metal-gate work-function fluctuation and random dopant fluctuation of 10-nm gate-all-around silicon nanowire MOSFET devices. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 34.4.1–34.4.4. [Google Scholar]

- Paul, A.; Bryant, A.; Hook, T.B.; Yeh, C.C.; Kamineni, V.; Johnson, J.B.; Tripathi, N.; Yamashita, T.; Tsutsui, G.; Basker, V.; et al. Comprehensive study of effective current variability and MOSFET parameter correlations in 14nm multi-fin SOI FINFETs. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 13.5.1–13.5.4. [Google Scholar] [CrossRef]

- Sugii, N.; Tsuchiya, R.; Ishigaki, T.; Morita, Y.; Yoshimoto, H.; Torii, K.; Kimura, S.I. Comprehensive study on Vth variability in silicon on thin BOX (SOTB) CMOS with small random-dopant fluctuation: Finding a way to further reduce variation. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Hook, T.B.; Vinet, M.; Murphy, R.; Ponoth, S.; Grenouillet, L. Transistor matching and silicon thickness variation in ETSOI technology. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 5.7.1–5.7.4. [Google Scholar] [CrossRef]

- Wang, R.; Zhuge, J.; Huang, R.; Yu, T.; Zou, J.; Kim, D.W.; Park, D.; Wang, Y. Investigation on variability in metal-gate Si nanowire MOSFETs: Analysis of variation sources and experimental characterization. IEEE Trans. Electron Devices 2011, 58, 2317–2325. [Google Scholar] [CrossRef]

- Endo, K.; O’uchi, S.I.; Ishikawa, Y.; Liu, Y.; Matsukawa, T.; Sakamoto, K.; Tsukada, J.; Yamauchi, H.; Masahara, M. Variability Analysis of TiN Metal-Gate FinFETs. IEEE Electron Device Lett. 2010, 31, 546–548. [Google Scholar] [CrossRef]

- Bhoir, M.S.; Chiarella, T.; Ragnarsson, L.Å.; Mitard, J.; Horiguchi, N.; Mohapatra, N.R. Variability sources in nanoscale bulk FinFETs and TiTaN-a promising low variability WFM for 7/5 nm CMOS nodes. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 36.2.1–36.2.4. [Google Scholar]

- Lee, S.; Yoon, J.S.; Jeong, J.; Lee, J.; Baek, R.H. Observation of mobility and velocity behaviors in ultra-scaled LG = 15 nm silicon nanowire field-effect transistors with different channel diameters. Solid-State Electron. 2020, 164, 107740. [Google Scholar] [CrossRef]

- Li, M.; Yeo, K.H.; Suk, S.D.; Yeoh, Y.Y.; Kim, D.W.; Chung, T.Y.; Oh, K.S.; Lee, W.S. Sub-10 nm gate-all-around CMOS nanowire transistors on bulk Si substrate. In Proceedings of the IEEE Symposium on VLSI Technology (VLSI), Kyoto, Japan, 15–17 June 2009; pp. 94–95. [Google Scholar]

- Kim, D.W.; Yeo, K.; Suk, S.D.; Li, M.; Yeoh, Y.Y.; Sohn, D.K.; Chung, C. Fabrication and electrical characteristics of self-aligned (SA) gate-all-around (GAA) Si nanowire MOSFETs (SNWFET). In Proceedings of the IEEE International Conference on Integrated Circuit Design and Technology, Grenoble, France, 2–4 June 2010; pp. 63–66. [Google Scholar] [CrossRef]

- Akbari-Saatlu, M.; Procek, M.; Mattsson, C.; Thungström, G.; Nilsson, H.-E.; Xiong, W.; Xu, B.; Li, Y.; Radamson, H.H. Silicon Nanowires for Gas Sensing: A Review. Nanomaterials 2020, 10, 2215. [Google Scholar] [CrossRef] [PubMed]

- Nam, H.; Lee, Y.; Park, J.D.; Shin, C. Study of Work-Function Variation in High-k Metal-Gate Gate-All-Around Nanowire MOSFET. IEEE Trans. Electron Devices 2016, 63, 3338–3341. [Google Scholar] [CrossRef]

- Yoon, J.S.; Lee, S.; Yun, H.; Baek, R.H. Digital/Analog performance optimization of vertical nanowire FETs using machine learning. IEEE Access 2021, 9, 29071–29077. [Google Scholar] [CrossRef]

- Kuhn, K.J.; Giles, M.D.; Becher, D.; Kolar, P.; Kornfeld, A.; Kotlyar, R.; Ma, S.T.; Maheshwari, A.; Mudanai, S. Process technology variation. IEEE Trans. Electron Devices 2011, 58, 2197–2208. [Google Scholar] [CrossRef]

- Trevisoli, R.D.; Doria, R.T.; Pavanello, M.A. Analytical model for the threshold voltage in junctionless nanowire transistors of different geometries. ECS Trans. 2011, 39, 147–154. [Google Scholar] [CrossRef]

- Trevisoli, R.D.; Doria, R.T.; de Souza, M.; Pavanello, M.A. Threshold voltage in junctionless nanowire transistors. Semicond. Sci. Technol. 2011, 26, 105009. [Google Scholar] [CrossRef]

- Matsukawa, T.; Liu, Y.; O’uchi, S.I.; Endo, K.; Tsukada, J.; Yamauchi, H.; Ishikawa, Y.; Ota, H.; Migita, S.; Morita, Y.; et al. Comprehensive analysis of Ion variation in metal gate FinFETs for 20 nm and beyond. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 23.5.1–23.5.4. [Google Scholar] [CrossRef]

- Rawat, A.; Sharan, N.; Jang, D.; Chiarella, T.; Bufler, F.M.; Catthoor, F.; Parvais, B.; Ganguly, U. Experimental validation of process-induced variability aware SPICE simulation platform for sub-20 nm FinFET technologies. IEEE Trans. Electron Devices 2021, 68, 976–980. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.; Yoon, J.-S.; Lee, J.; Jeong, J.; Yun, H.; Lim, J.; Lee, S.; Baek, R.-H. Novel Modeling Approach to Analyze Threshold Voltage Variability in Short Gate-Length (15–22 nm) Nanowire FETs with Various Channel Diameters. Nanomaterials 2022, 12, 1721. https://doi.org/10.3390/nano12101721

Lee S, Yoon J-S, Lee J, Jeong J, Yun H, Lim J, Lee S, Baek R-H. Novel Modeling Approach to Analyze Threshold Voltage Variability in Short Gate-Length (15–22 nm) Nanowire FETs with Various Channel Diameters. Nanomaterials. 2022; 12(10):1721. https://doi.org/10.3390/nano12101721

Chicago/Turabian StyleLee, Seunghwan, Jun-Sik Yoon, Junjong Lee, Jinsu Jeong, Hyeok Yun, Jaewan Lim, Sanguk Lee, and Rock-Hyun Baek. 2022. "Novel Modeling Approach to Analyze Threshold Voltage Variability in Short Gate-Length (15–22 nm) Nanowire FETs with Various Channel Diameters" Nanomaterials 12, no. 10: 1721. https://doi.org/10.3390/nano12101721

APA StyleLee, S., Yoon, J.-S., Lee, J., Jeong, J., Yun, H., Lim, J., Lee, S., & Baek, R.-H. (2022). Novel Modeling Approach to Analyze Threshold Voltage Variability in Short Gate-Length (15–22 nm) Nanowire FETs with Various Channel Diameters. Nanomaterials, 12(10), 1721. https://doi.org/10.3390/nano12101721