Electrical Interconnection and Bonding by Nano-Locking

Abstract

1. Introduction

2. Experiments

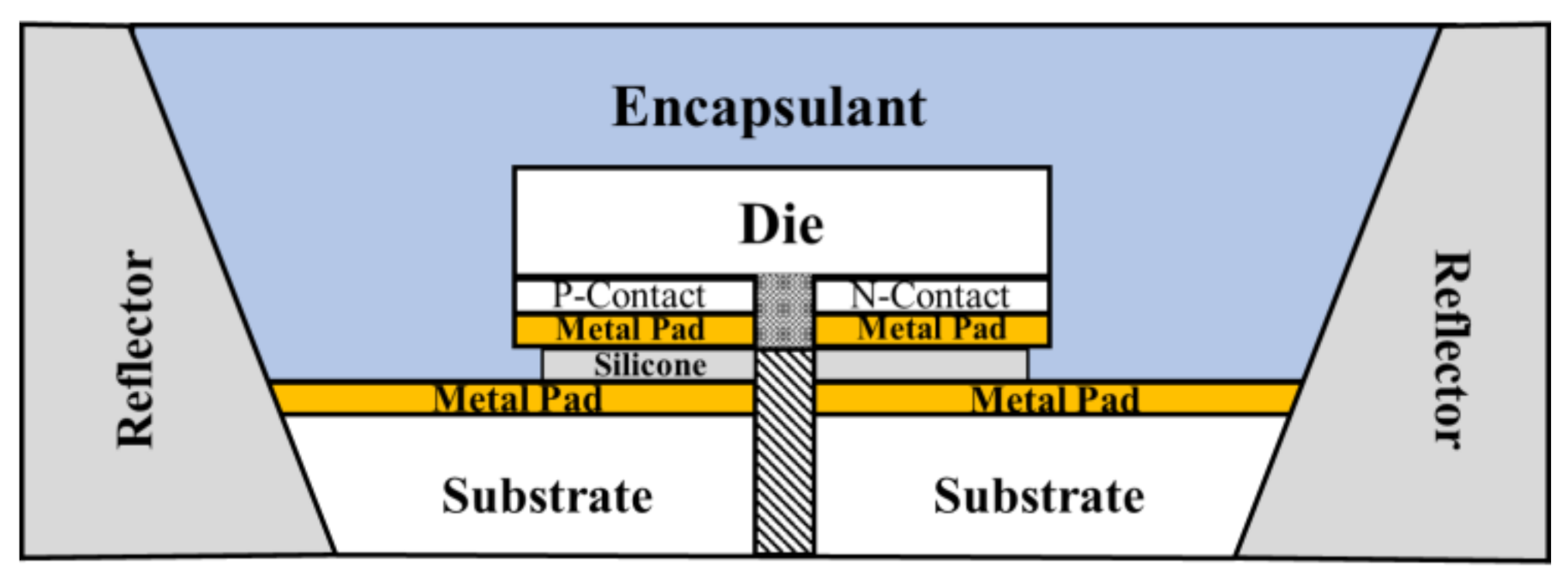

2.1. Fabrication of Packaged Devices

2.2. Devices Performance Evaluation

3. Results and Discussion

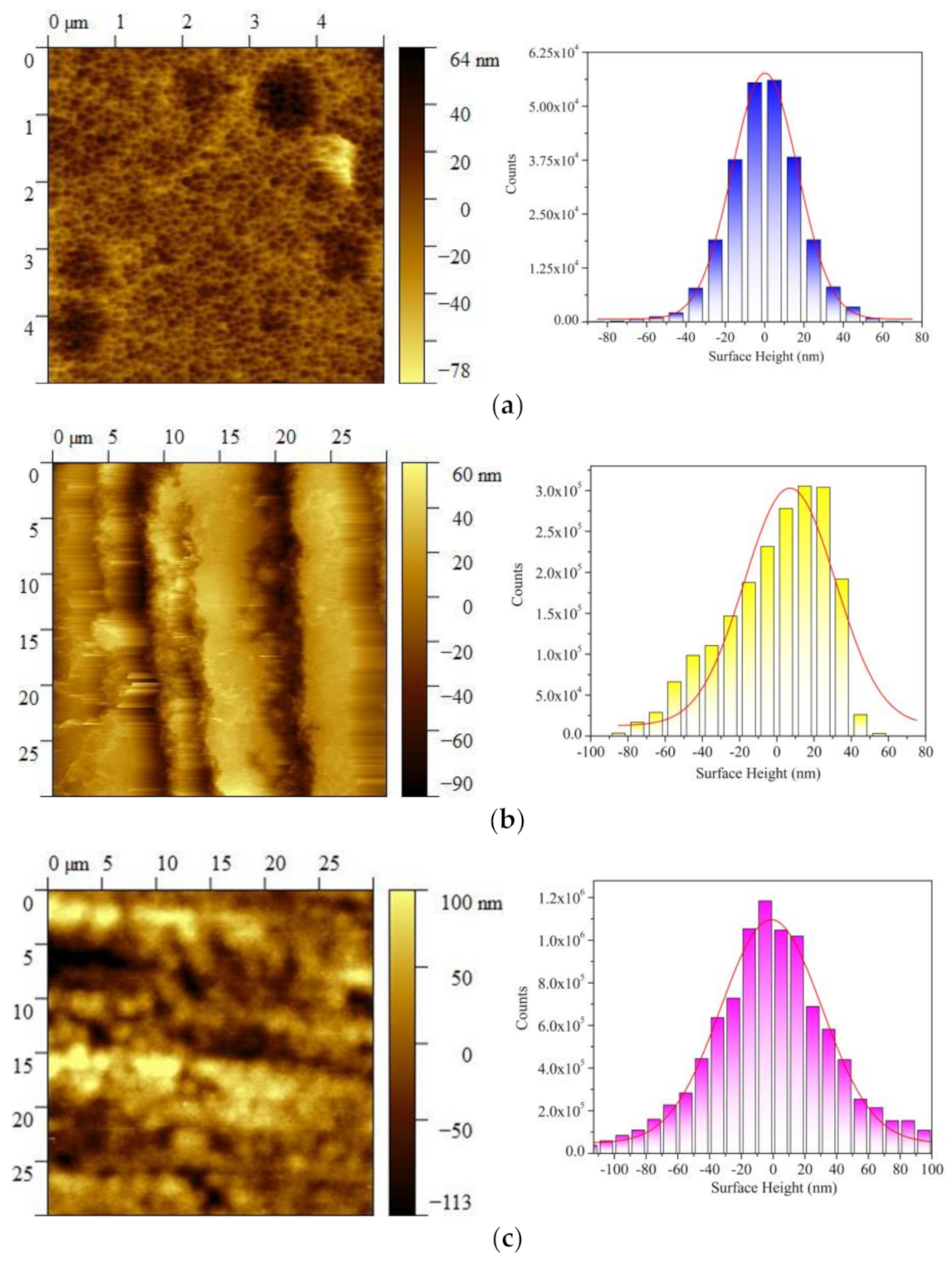

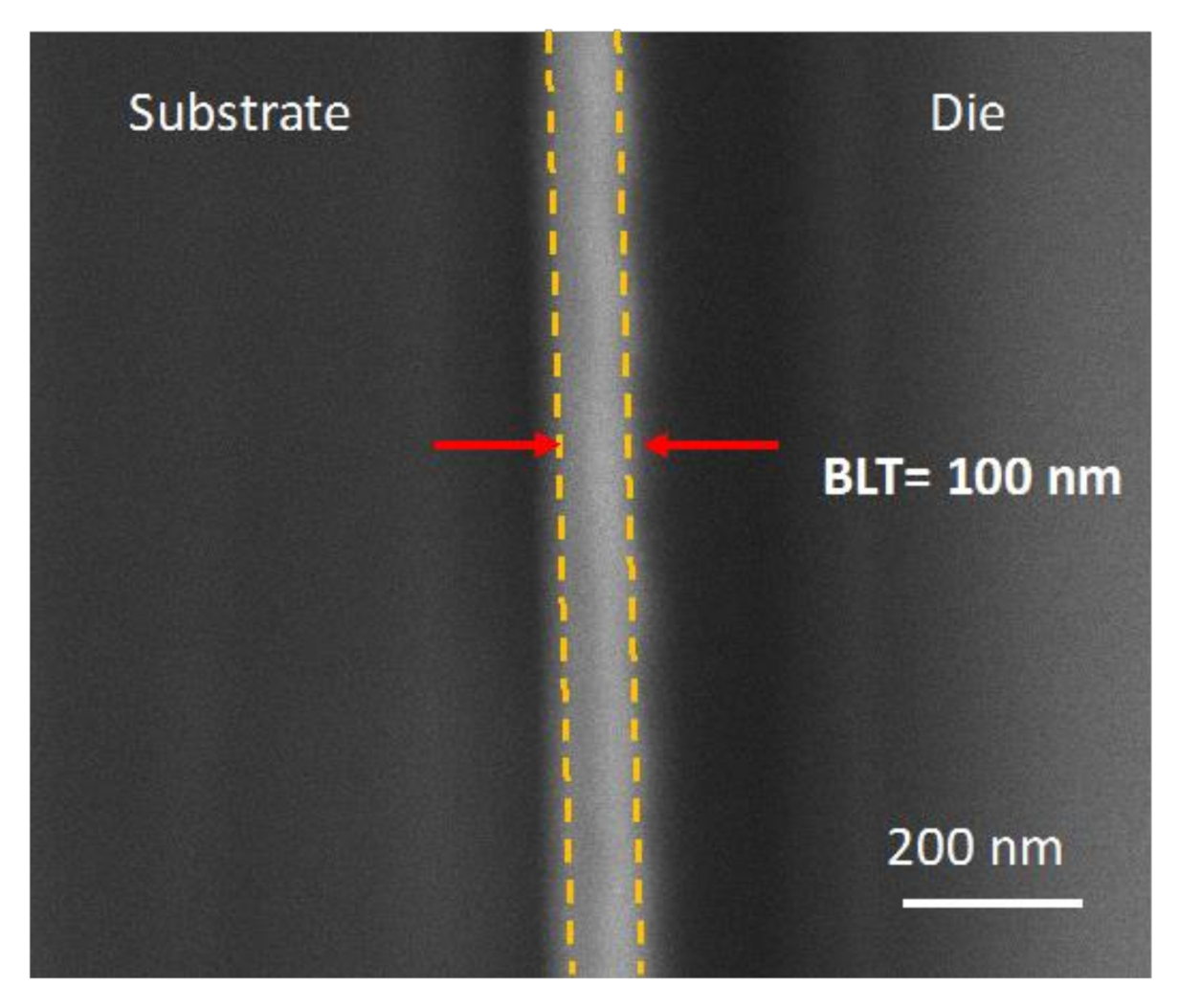

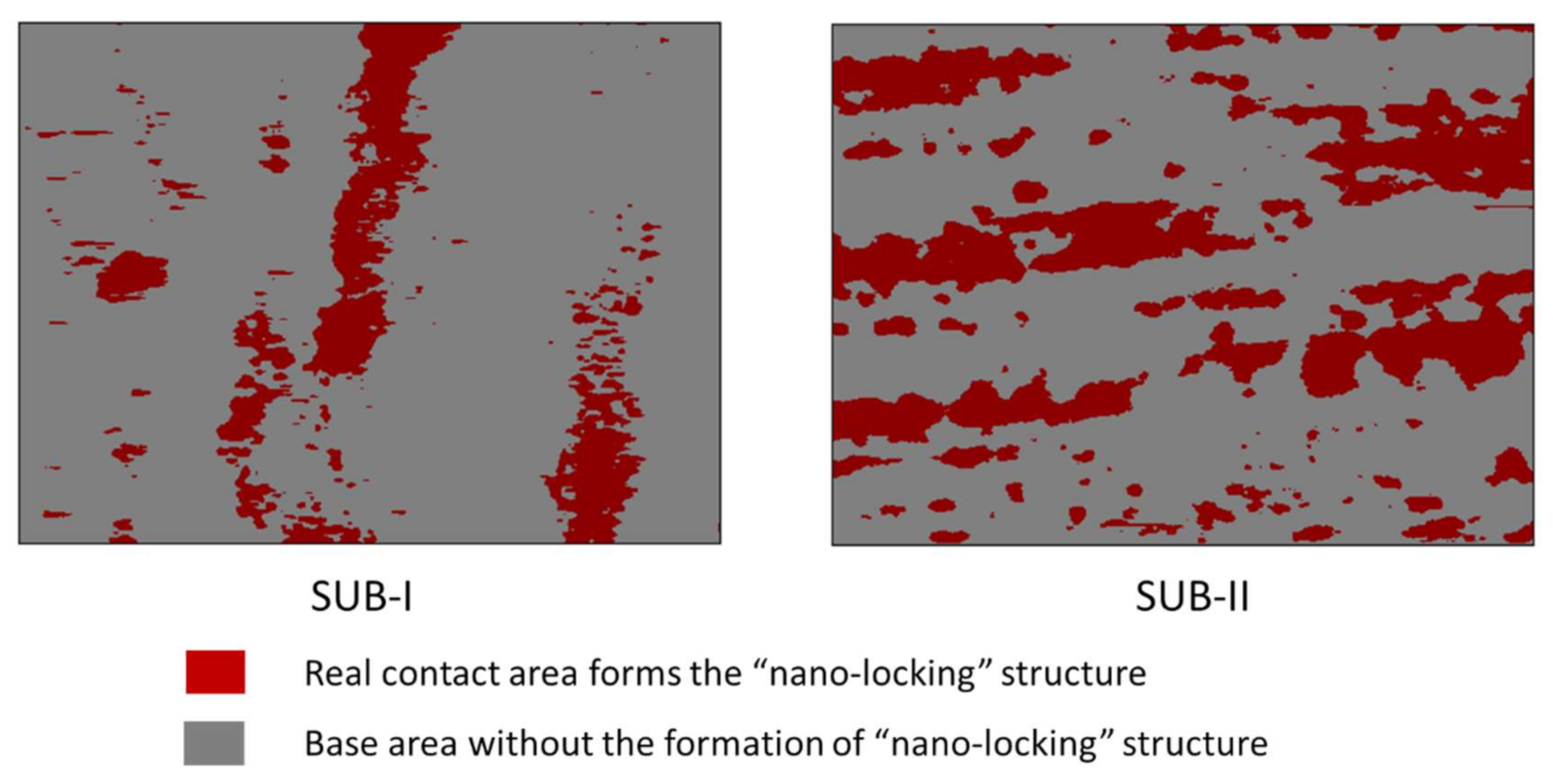

3.1. Surface Morphology Study

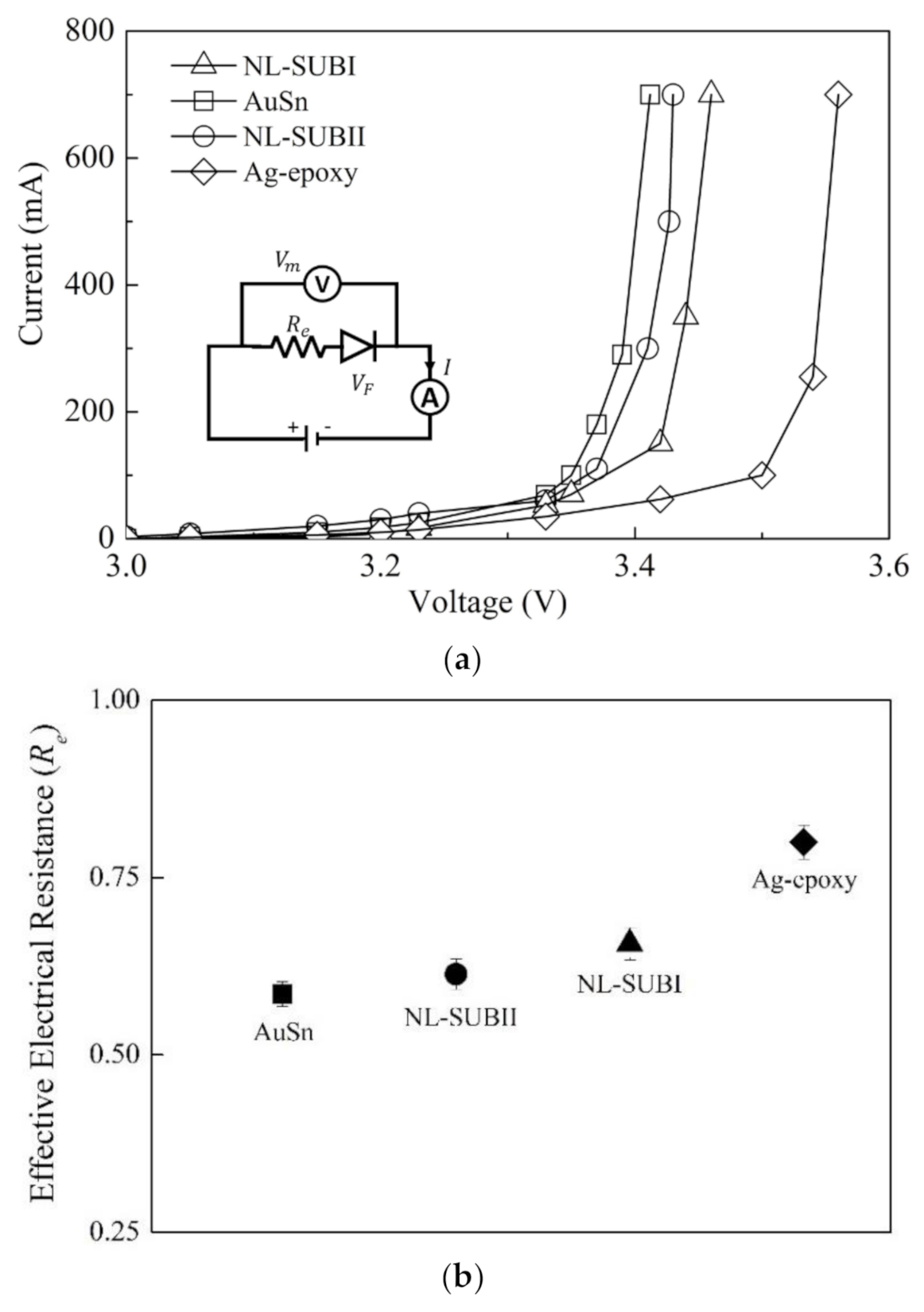

3.2. Devices Performance: Electrical

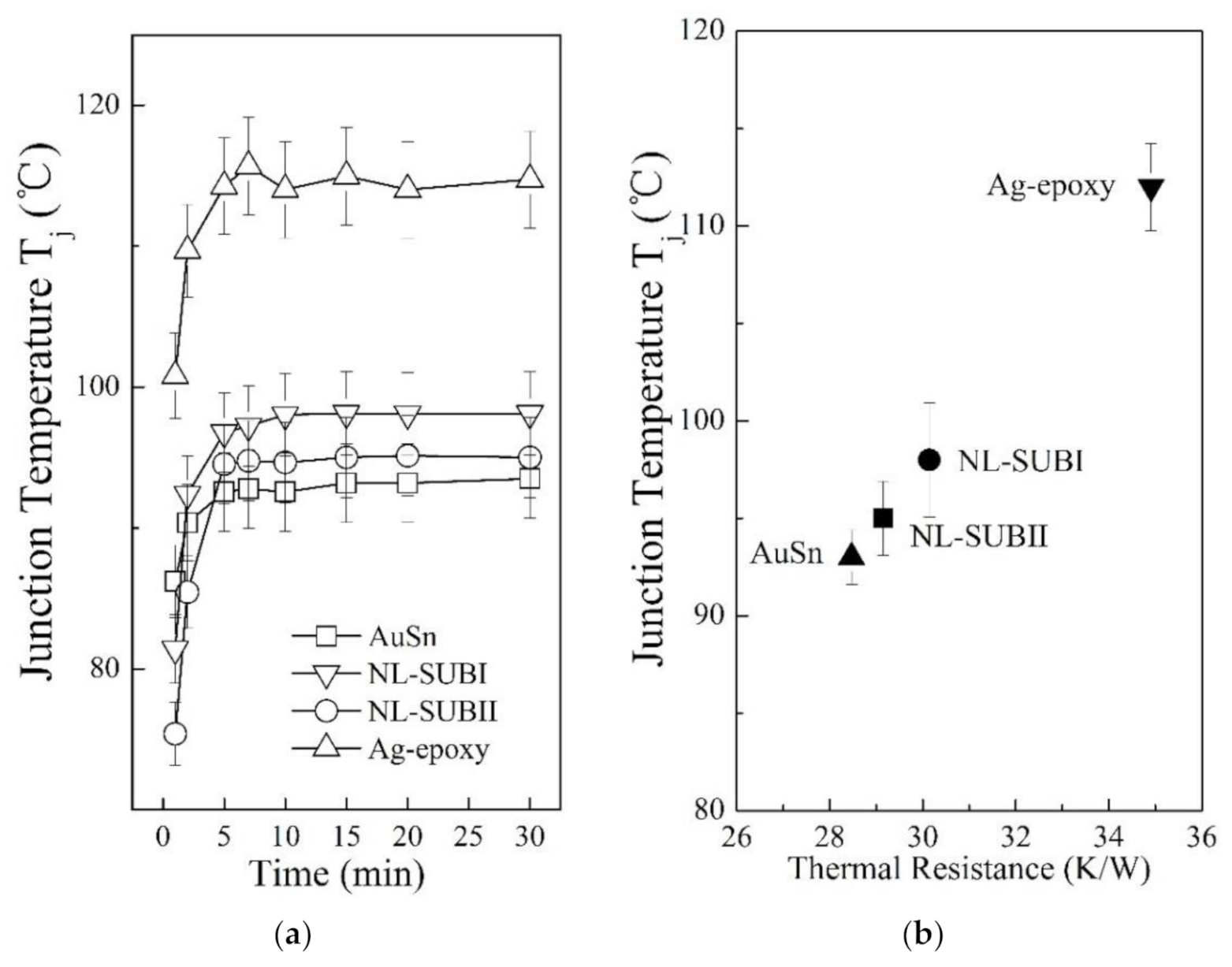

3.3. Device Performance: Thermal

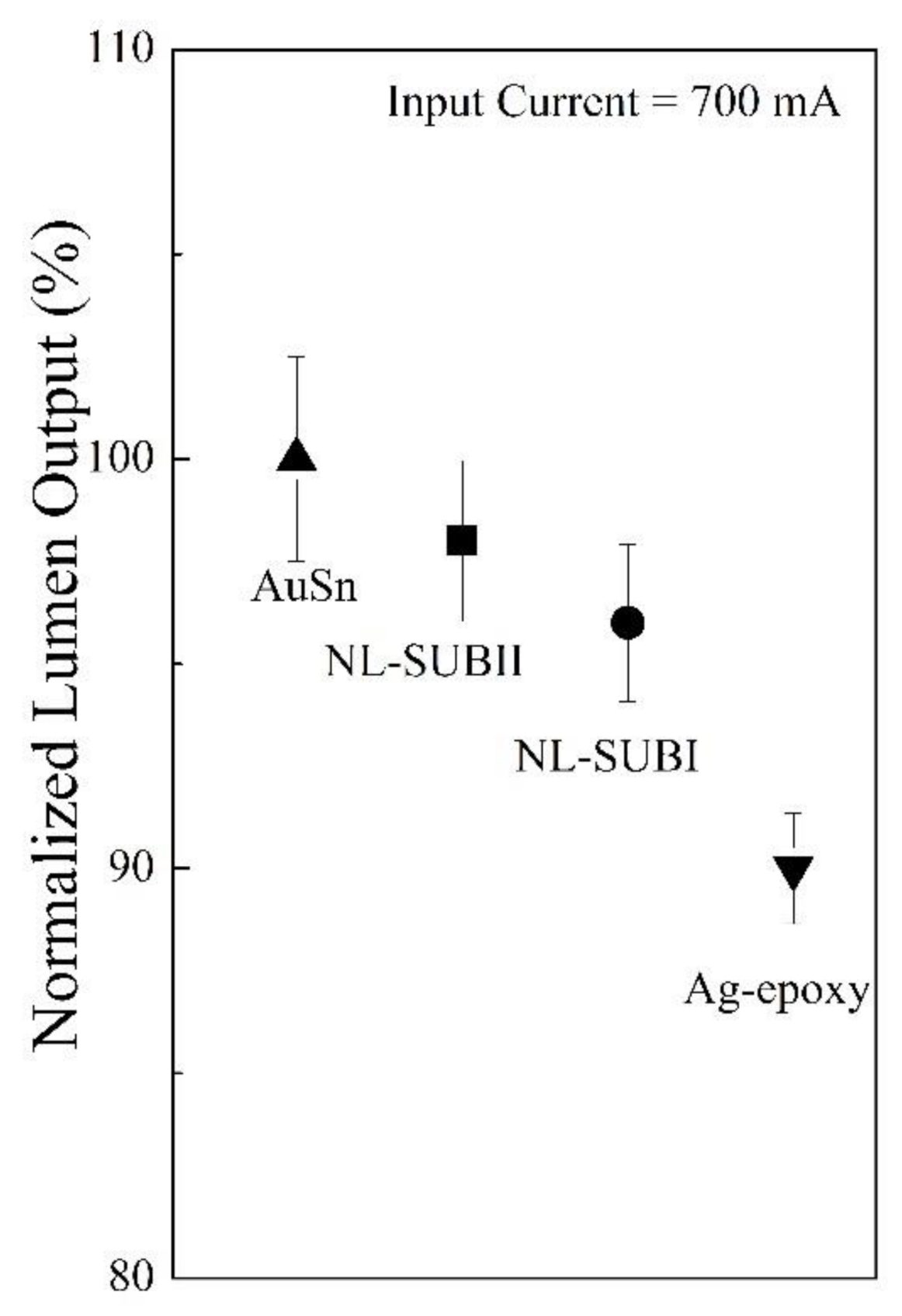

3.4. Devices Performance Evaluation: Optical

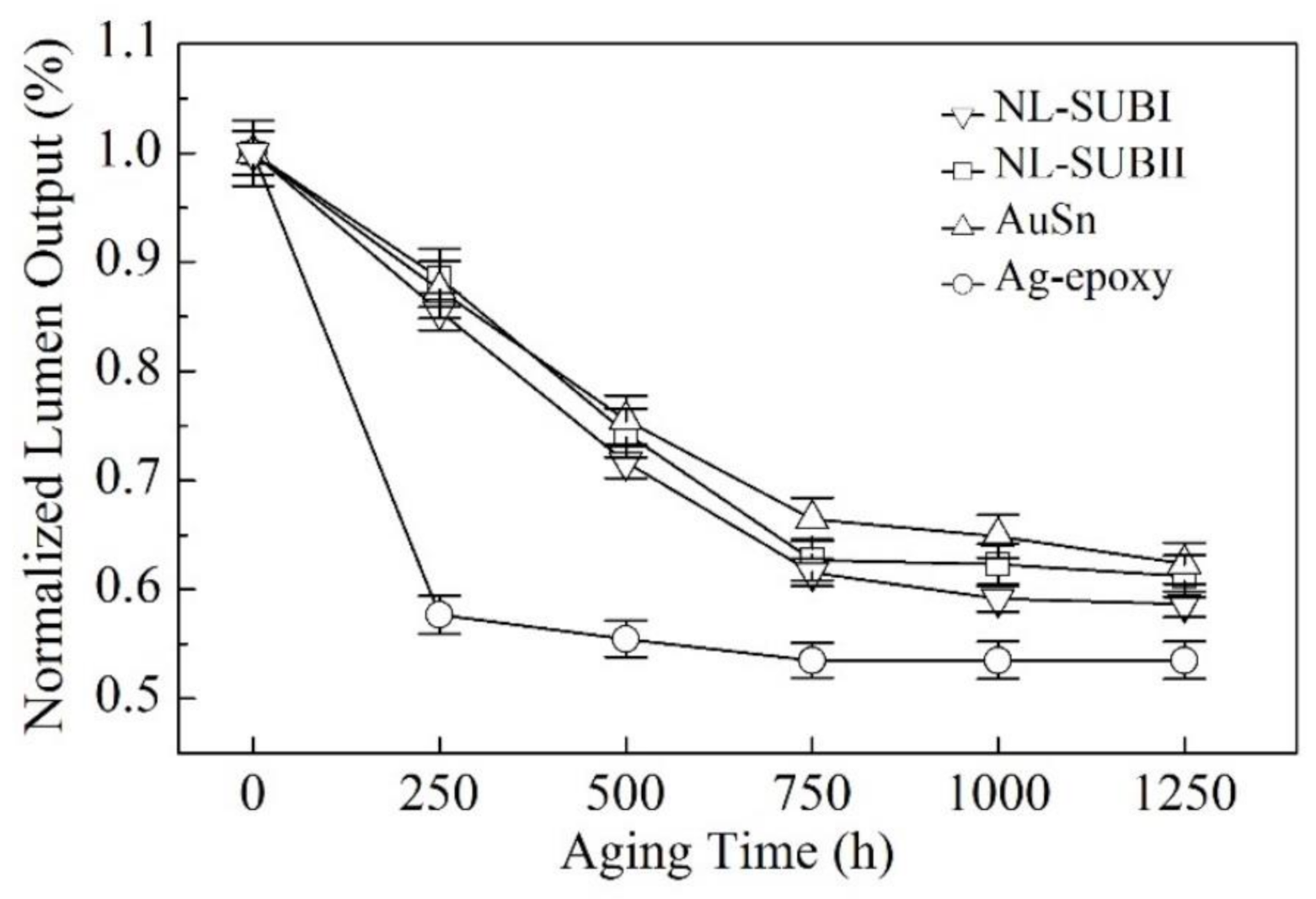

3.5. Devices Performance: Long-Term Reliability

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lau, J.H. 3D Integration; Springer Science and Business Media LLC: Berlin/Heidelberg, Germany, 2018; pp. 231–268. [Google Scholar]

- Rao, Y.; Lu, D.; Wong, C.P. A study of impact performance of conductive adhesives. Int. J. Adhes. Adhes. 2004, 24, 449–453. [Google Scholar] [CrossRef]

- Suzuki, T.; Takeshi, T.; Yusuke, Y.; Toshiaki, M.; Yuki, K.; Dai, I.; Masato, N.; Hideo, N.; Kazuhiko, K. Effect of Loading Type on Fatigue Lifetime of Sintered-Silver Die Attach. IEEE Trans. Device Mater. Reliab. 2018, 18, 350–358. [Google Scholar] [CrossRef]

- Heterogeneous Integration Roadmap. IEEE 2019 Edition. Available online: https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html (accessed on 21 February 2019).

- Shigetou, A.; Itoh, T.; Matsuo, M.; Hayasaka, N.; Okura, K.; Suga, T. Bumpless interconnect through ultrafine Cu electrodes by means of sur-face-activated bonding (SAB) method. IEEE Trans. Adv. Packag. 2006, 29, 218–226. [Google Scholar] [CrossRef]

- Datta, M. Manufacturing processes for fabrication of flip-chip micro-bumps used in microelectronic packaging: An overview. J. Micromanuf. 2019, 3, 69–83. [Google Scholar] [CrossRef]

- Lau, J.H.; Li, M.; Qingqian, M.L.; Chen, T.; Xu, I.; Yong, Q.X.; Cheng, Z.; Fan, N.; Kuah, E.; Li, Z.; et al. Fan-Out Wafer-Level Packaging for Heterogeneous Integration. IEEE Trans. Components Packag. Manuf. Technol. 2018, 8, 1544–1560. [Google Scholar] [CrossRef]

- Sheikhi, R.; Huo, Y.; Shi, F.G.; Lee, C.C. Low Temperature VECSEL-to-Diamond Heterogeneous Integration with Ag-In Spinodal Nanostructured Layer. Scr. Mater. 2021, 194, 113628. [Google Scholar] [CrossRef]

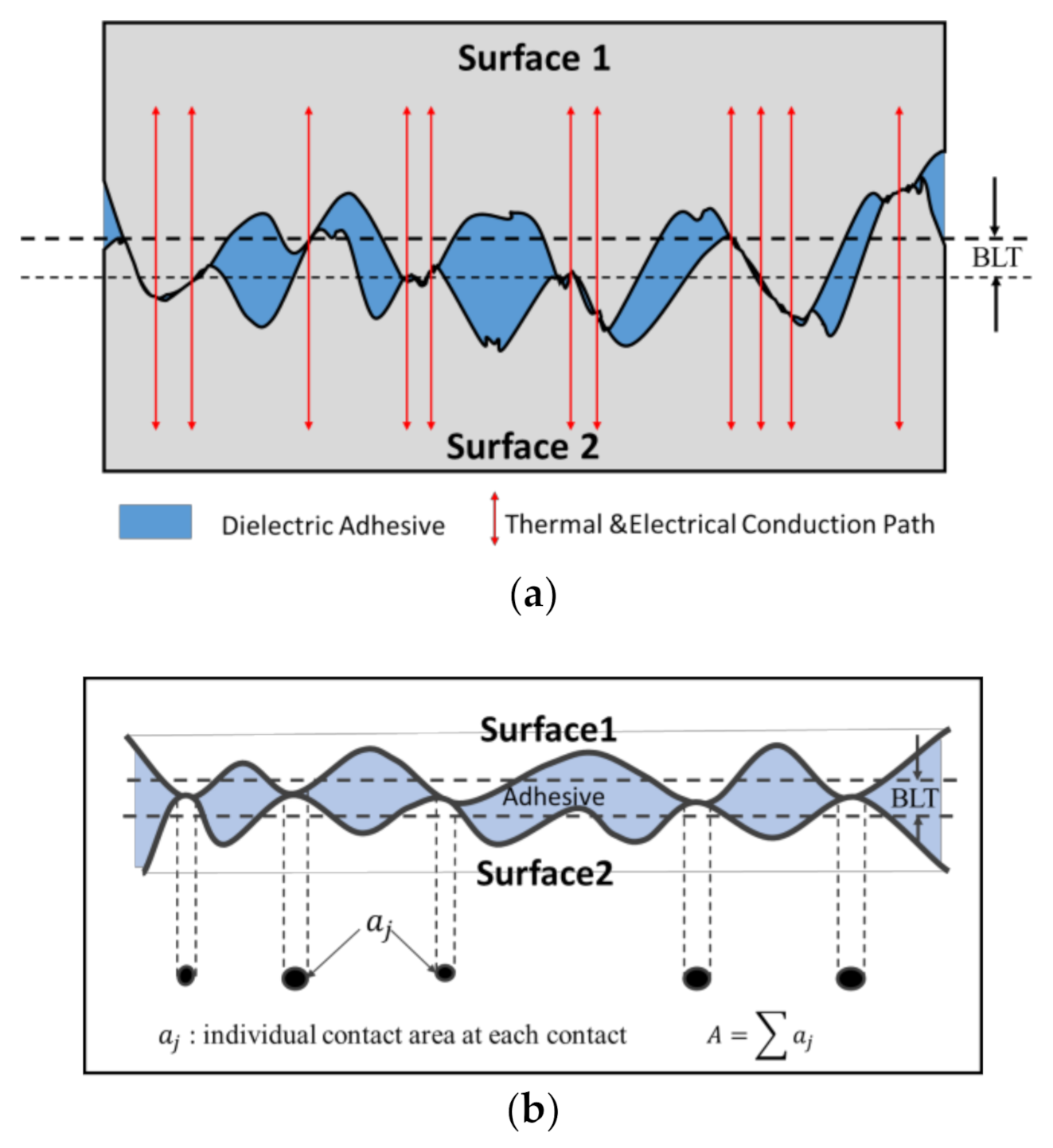

- Bhushan, B. Contact mechanics of rough surfaces in tribology: Multiple asperity contact. Tribol. Lett. 1998, 4, 1–35. [Google Scholar] [CrossRef]

- Lin, S.; Xu, L.; Xu, C.; Chen, X.; Wang, A.C.; Zhang, B.; Lin, P.; Yang, Y.; Zhao, H.; Wang, Z.L. Electron Transfer in Nanoscale Contact Electrification: Effect of Temperature in the Metal–Dielectric Case. Adv. Mater. 2019, 31, e1808197. [Google Scholar] [CrossRef] [PubMed]

- Komvopoulos, K. A Multiscale Theoretical Analysis of the Mechanical, Thermal, and Electrical Characteristics of Rough Contact Interfaces Demonstrating Fractal Behavior. Front. Mech. Eng. 2020, 6, 36. [Google Scholar] [CrossRef]

- Li, Y.; Wong, C. Recent advances of conductive adhesives as a lead-free alternative in electronic packaging: Materials, processing, reliability and applications. Mater. Sci. Eng. R Rep. 2006, 51, 1–35. [Google Scholar] [CrossRef]

- Shahil, K.M.F.; Balandin, A.A. Graphene–Multilayer Graphene Nanocomposites as Highly Efficient Thermal Interface Materials. Nano Lett. 2012, 12, 861–867. [Google Scholar] [CrossRef] [PubMed]

- Yan, B.; You, J.P.; Tran, N.T.; He, Y.; Shi, F. Influence of Die Attach Layer on Thermal Performance of High Power Light Emitting Diodes. IEEE Trans. Components Packag. Technol. 2009, 33, 722–727. [Google Scholar] [CrossRef]

- Chen, L.; Tran, H.; Batra, R.; Kim, C.; Ramprasad, R. Machine learning models for the lattice thermal conductivity prediction of inorganic materials. Comput. Mater. Sci. 2019, 170, 109155. [Google Scholar] [CrossRef]

- Jordan, M.I.; Mitchell, T.M. Machine learning: Trends, perspectives, and prospects. Science 2015, 349, 255–260. [Google Scholar] [CrossRef] [PubMed]

- Mo, Y.; Turner, K.T.; Szlufarska, I. Friction laws at the nanoscale. Nat. Cell Biol. 2009, 457, 1116–1119. [Google Scholar] [CrossRef] [PubMed]

- Ye, Z.; Moon, H.; Lee, M.H.; Martini, A. Size and load dependence of nanoscale electric contact resistance. Tribol. Int. 2014, 71, 109–113. [Google Scholar] [CrossRef]

- Lüpke, F.; Eschbach, M.; Heider, T.; Lanius, M.; Schüffelgen, P.; Rosenbach, D.; Driesch, N.V.D.; Cherepanov, V.; Mussler, G.; Plucinski, L.; et al. Electrical resistance of individual defects at a topological insulator surface. Nat. Commun. 2017, 8, 15704. [Google Scholar] [CrossRef] [PubMed]

- Tang, Z.; Shi, F.G. Effects of preexisting voids on electromigration failure of flip chip solder bumps. Microelectron. J. 2001, 32, 605–613. [Google Scholar] [CrossRef]

| Bonding Material | Volume Resistivity | Bond-Line Thickness (BLT) |

|---|---|---|

| Ag-epoxy (85% by weight) | 8 Ωm | 25 ± 2 μm |

| AuSn (80% Gold, 20% Tin) | 1.64 Ωm | 20 ± 2 μm |

| Semiconductor Die | Substrate | SUB-I | SUB-II | |

|---|---|---|---|---|

| Heights (nm) | Frequency Percent | Heights (nm) | Frequency Percent | Frequency Percent |

| 0–10 | 0.2242 | 90–100 | 0 | 0.0113 |

| 10–20 | 0.1529 | 80–90 | 0 | 0.0160 |

| 20–30 | 0.0761 | 70–80 | 0 | 0.0160 |

| 30–40 | 0.0324 | 60–70 | 0 | 0.0222 |

| 40–50 | 0.0138 | 50–60 | 0.0016 | 0.0264 |

| 50–60 | 0.0035 | 40–50 | 0.0131 | 0.0456 |

| 60–70 | 0.0004 | 30–40 | 0.096 | 0.0604 |

| −10–0 | 0.2248 | 100–110 | 0 | 0.0071 |

| Total | 0.11 | 0.21 | ||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Guo, J.; Shih, Y.-C.; Shi, F.G. Electrical Interconnection and Bonding by Nano-Locking. Nanomaterials 2021, 11, 1589. https://doi.org/10.3390/nano11061589

Guo J, Shih Y-C, Shi FG. Electrical Interconnection and Bonding by Nano-Locking. Nanomaterials. 2021; 11(6):1589. https://doi.org/10.3390/nano11061589

Chicago/Turabian StyleGuo, Jielin, Yu-Chou Shih, and Frank G. Shi. 2021. "Electrical Interconnection and Bonding by Nano-Locking" Nanomaterials 11, no. 6: 1589. https://doi.org/10.3390/nano11061589

APA StyleGuo, J., Shih, Y.-C., & Shi, F. G. (2021). Electrical Interconnection and Bonding by Nano-Locking. Nanomaterials, 11(6), 1589. https://doi.org/10.3390/nano11061589