Comprehensive Performance Quasi-Non-Volatile Memory Compatible with Large-Scale Preparation by Chemical Vapor Deposition

Abstract

1. Introduction

2. Experiment Method

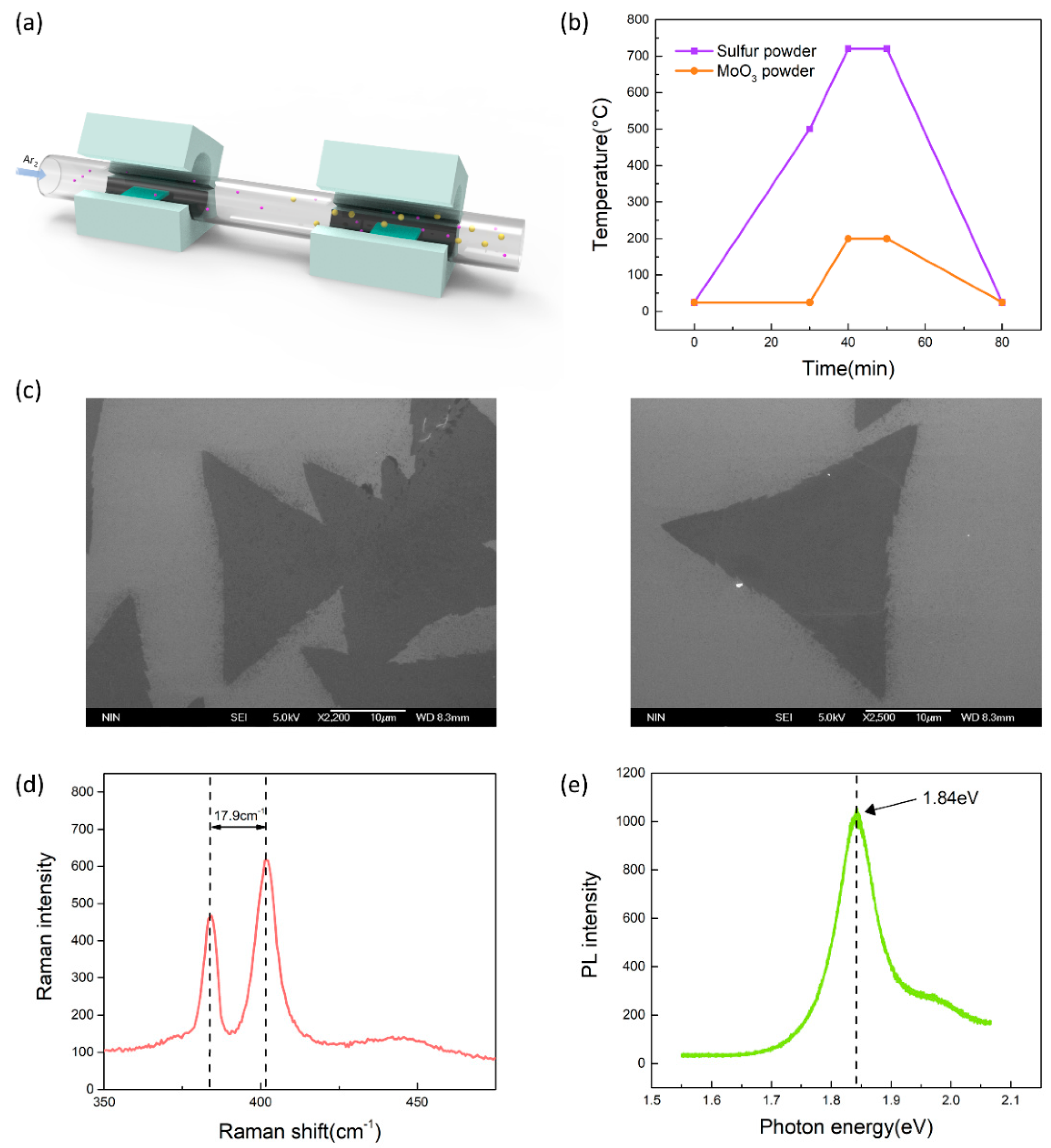

2.1. The Growth of MoS2 by APCVD and Materials Characterization

2.2. Device Fabrication and Electronic Characterization

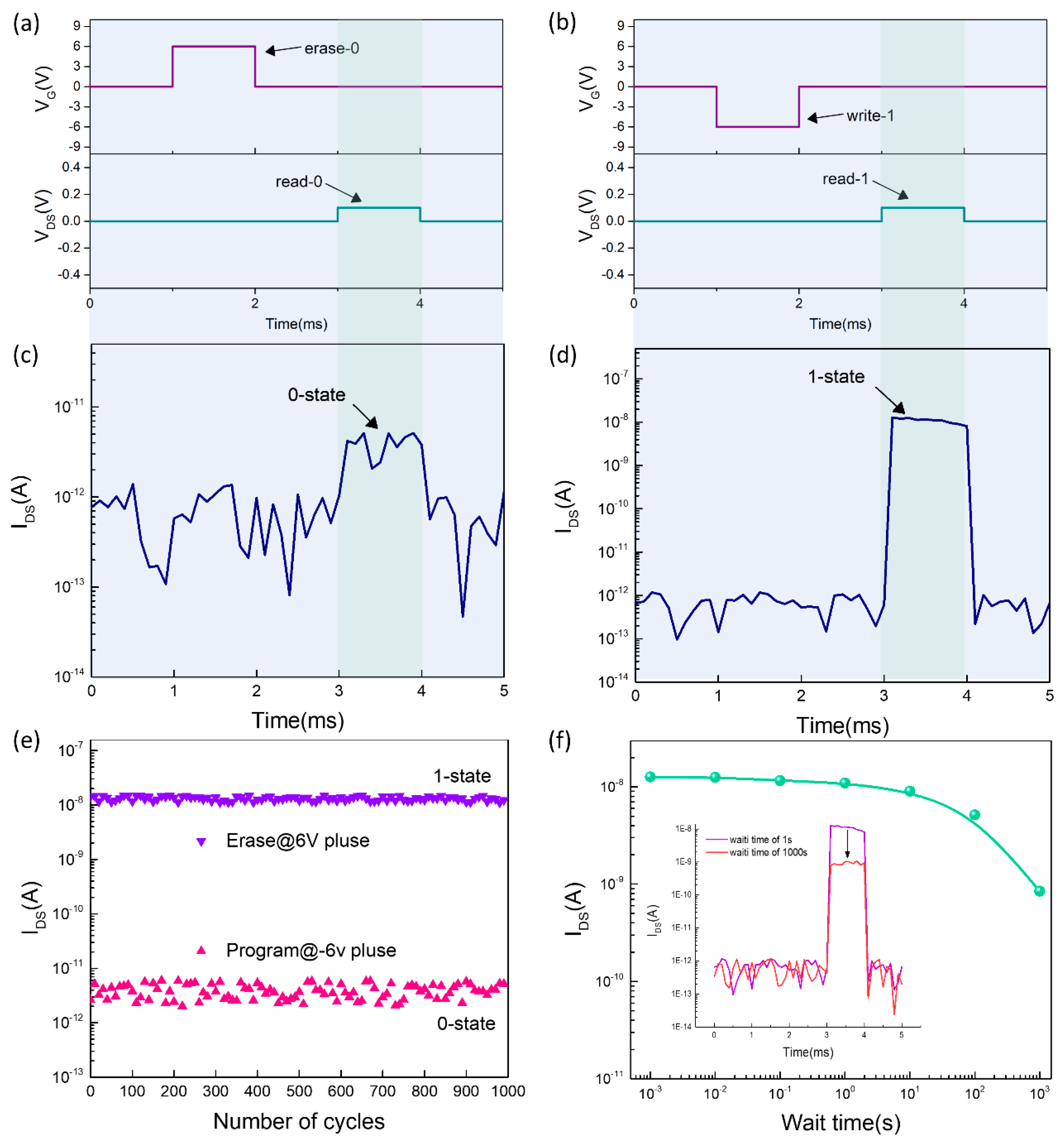

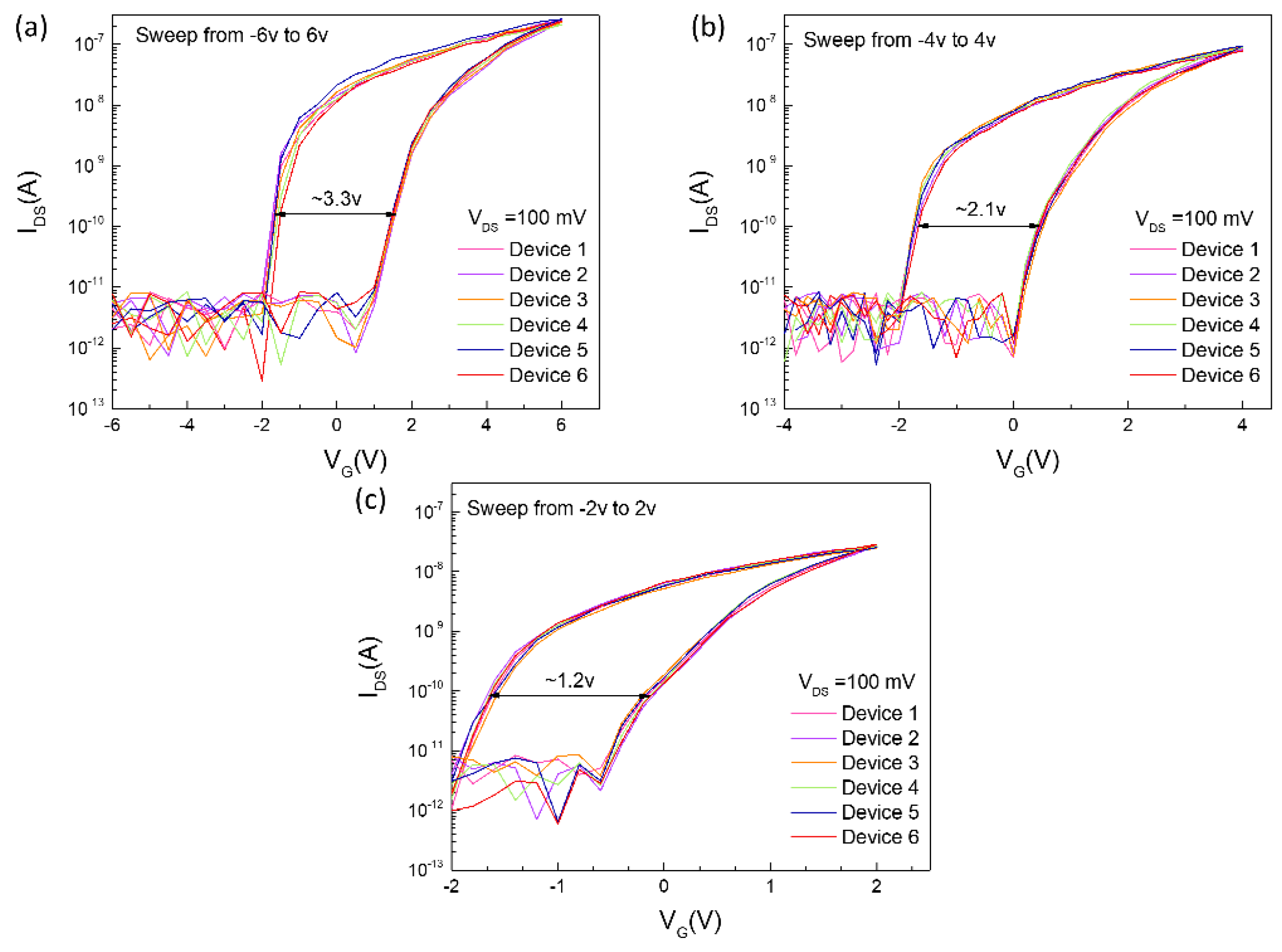

3. Results and Discussion

4. Mechanism Analysis

5. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- International Technology Roadmap for Semiconductors 2.0 (ITRS, 2015). Available online: https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/ (accessed on 8 June 2020).

- Britnell, L.; Gorbachev, R.V.; Jalil, R.; Belle, B.D.; Schedin, F.; Katsnelson, M.I.; Eaves, L.; Morozov, S.V.; Mayorov, A.S.; Peres, N.M.R.; et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 2012, 12, 1707–1710. [Google Scholar] [CrossRef]

- Liu, L.; Han, H.; Xu, L.; Zhou, J.; Zhao, C.; Ding, S.; Shi, H.; Xiao, M.; Ding, L.; Jin, C.; et al. Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics. Science 2020, 368, 850–856. [Google Scholar] [CrossRef] [PubMed]

- Li, S.; Tian, M.; Gu, C.; Wang, R.; Wang, M.; Xiong, X.; Li, X.; Huang, R.; Wu, Y. BEOL Compatible 15-nm Channel Length Ultrathin Indium-Tin-Oxide Transistors with Ion = 970 μA/μm and On/off Ratio Near 1011 at Vds = 0.5 V. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Lembke, D.; Bertolazzi, S.; Kis, A. Single-layer MoS2 electronics. Acc. Chem. Res. 2015, 48, 100–110. [Google Scholar] [CrossRef] [PubMed]

- He, Q.; He, Q.; Zeng, Z.; Yin, Z.; Li, H.; Wu, S.; Huang, X.; Zhang, H. Fabrication of flexible MoS2 thin-film transistor arrays for practical gas-sensing applications. Small 2012, 8, 2994–2999. [Google Scholar] [CrossRef]

- Britnell, L.; Ribeiro, R.M.; Eckmann, A.; Jalil, R.; Belle, B.D.; Mishchenko, A.; Kim, Y.-J.; Gorbachev, R.V.; Georgiou, T.; Morozov, S.V.; et al. Strong Light-Matter Interactions in Heterostructures of Atomically Thin Films. Science 2013, 340, 1311–1314. [Google Scholar] [CrossRef]

- Yu, W.J.; Liu, Y.; Zhou, H.; Yin, A.; Li, Z.; Huang, Y.; Duan, X. Highly efficient gate-tunable photocurrent generation in vertical heterostructures of layered materials. Nat. Nanotechnol. 2013, 8, 952–958. [Google Scholar] [CrossRef] [PubMed]

- Shi, Y.; Liang, X.; Yuan, B.; Chen, V.; Li, H.; Hui, F.; Yu, Z.; Yuan, F.; Pop, E.; Wong, H.-S.P.; et al. Electronic synapses made of layered two-dimensional materials. Nat. Electron. 2018, 1, 458–465. [Google Scholar] [CrossRef]

- Wang, M.; Cai, S.; Pan, C.; Wang, C.; Lian, X.; Zhuo, Y.; Xu, K.; Cao, T.; Pan, X.; Wang, B.; et al. Robust memristors based on layered two-dimensional materials. Nat. Electron. 2018, 1, 130–136. [Google Scholar] [CrossRef]

- Sangwan, V.K.; Lee, H.; Bergeron, H.; Balla, I.; Beck, M.E.; Chen, K.-S.; Hersam, M.C. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature 2018, 554, 500–504. [Google Scholar] [CrossRef]

- Smithe, K.K.H.; Suryavanshi, S.V.; Munoz Rojo, M.; Tedjarati, A.D.; Pop, E. Low Variability in Synthetic Monolayer MoS2 Devices. ACS Nano 2017, 11, 8456–8463. [Google Scholar] [CrossRef]

- Li, W.; Zhou, J.; Cai, S.; Yu, Z.; Zhang, J.; Fang, N.; Li, T.; Wu, Y.; Chen, T.; Xie, X.; et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2019, 2, 563–571. [Google Scholar] [CrossRef]

- Si, M.; Su, C.-J.; Jiang, C.; Conrad, N.J.; Zhou, H.; Maize, K.D.; Qiu, G.; Wu, C.-T.; Shakouri, A.; Alam, M.A.; et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 2018, 13, 24–28. [Google Scholar] [CrossRef]

- Wachter, S.; Polyushkin, D.K.; Bethge, O.; Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 2017, 8, 14948. [Google Scholar] [CrossRef] [PubMed]

- Yu, W.J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 2013, 12, 246–252. [Google Scholar] [CrossRef] [PubMed]

- Choi, M.S.; Lee, G.H.; Yu, Y.-J.; Lee, D.-Y. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 2013, 4, 1624. [Google Scholar] [CrossRef] [PubMed]

- Roy, K.; Padmanabhan, M.; Goswami, S.; Sai, T.P.; Ramalingam, G.; Raghavan, S. Graphene-MoS2 hybrid structures for multifunctional photoresponsive memory devices. Nat. Nanotechnol. 2013, 8, 826–830. [Google Scholar] [CrossRef] [PubMed]

- Kappera, R.; Voiry, D.; Yalcin, S.E.; Branch, B.; Gupta, G.; Mohite, A.D.; Chhowalla, M. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 2014, 13, 1128–1134. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive devices for computing. Nat. Nanotechnol. 2013, 8, 13–24. [Google Scholar] [CrossRef]

- JEDEC Solid State Technology Association Standard JESD79-2b 65 (2005). Available online: http://cs.ecs.baylor.edu/~maurer/CSI5338/JESD79-2B.pdf (accessed on 8 June 2020).

- Bertolazzi, S.; Krasnozhon, D.; Kis, A. Nonvolatile Memory Cells Based on MoS2/Graphene Heterostructures. ACS Nano 2013, 7, 3246–3252. [Google Scholar] [CrossRef]

- Liu, C.; Yan, X.; Song, X.; Ding, S.; Zhang, D.W.; Zhou, P. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 2018, 13, 404–410. [Google Scholar] [CrossRef]

- Zade, D.; Sato, S.; Kakushima, K.; Srivastava, A.; Ahmet, P.; Tsutsui, K.; Nishiyama, A.; Sugii, N.; Natori, K.; Hattori, T.; et al. Effects of La2O3 incorporation in HfO2 gated nMOSFETs on low-frequency noise. Microelectron. Reliab. 2011, 51, 746–750. [Google Scholar] [CrossRef]

- Umezawa, N.; Shiraishi, K.; Sugino, S.; Tachibana, A.; Ohmori, K.; Kakushima, K.; Iwai, H.; Chikyow, T.; Ohno, T.; Nara, Y.; et al. Suppression of oxygen vacancy formation in Hf-based high-k dielectrics by lanthanum incorporation. Appl. Phys. Lett. 2007, 91. [Google Scholar] [CrossRef]

- Nan, H.; Wang, Z.; Wang, W.; Liang, Z.; Lu, Y.; Chen, Q.; He, D.; Tan, P.; Miao, F.; Wang, X.; et al. Strong Photoluminescence Enhancement of MoS2 through Defect Engineering and Oxygen Bonding. ACS Nano 2014, 8, 5738–5745. [Google Scholar] [CrossRef] [PubMed]

- Zhang, E.; Wang, W.; Zhang, C.; Jin, Y.; Zhu, G.; Sun, Q.; Zhang, D.W.; Zhou, P.; Xiu, F. Tunable Charge-Trap Memory Based on Few-Layer MoS2. ACS Nano 2015, 9, 612–619. [Google Scholar] [CrossRef] [PubMed]

- Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 2015, 106. [Google Scholar] [CrossRef]

- Li, J.; Liu, L.; Chen, X.; Liu, C.; Wang, J.; Hu, W.; Zhang, D.W.; Zhou, P. Symmetric Ultrafast Writing and Erasing Speeds in Quasi-Nonvolatile Memory via van der Waals Heterostructures. Adv. Mater. 2019, 31, e1808035. [Google Scholar] [CrossRef]

- Wang, J.; Zou, X.; Xiao, X.; Xu, L.; Wang, C.; Jiang, C.; Ho, J.C.; Wang, T.; Li, J.; Liao, L. Floating gate memory-based monolayer MoS2 transistor with metal nanocrystals embedded in the gate dielectrics. Small 2015, 11, 208–213. [Google Scholar] [CrossRef] [PubMed]

- Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 2017, 5. [Google Scholar] [CrossRef]

- Urban, F.; Giubileo, F.; Grillo, A.; Iemmo, L.; Luongo, G.; Passacantando, M.; Foller, T.; Madauß, L.; Pollmann, E.; Geller, M.P.; et al. Gas dependent hysteresis in MoS2 field effect transistors. 2D Mater. 2016, 6. [Google Scholar] [CrossRef]

- Illarionov, Y.Y.; Smithe, K.K.H.; Waltl, M.; Knobloch, T.; Pop, E.; Grasser, T. Improved Hysteresis and Reliability of MoS2 Transistors With High-Quality CVD Growth and Al2O3 Encapsulation. IEEE Electron. Device Lett. 2017, 38, 1763–1766. [Google Scholar] [CrossRef]

| Ref. | Materials | Program/Erase Ratio | Program/Erase Voltage | Write Speed | Date Retention Time | Process Complexity | Large-Scale Preparation |

|---|---|---|---|---|---|---|---|

| Our result | MoS2/LaAlO3 | ~1 × 103 | ±6 v | 1 ms | 1000 s | I | √ |

| [22] | HfO2/Graphene/HfO2/MoS2 | ~1 × 103 | ±18 v | 100 ms | 10 year | II | × |

| [23] | HfS2/MoS2/BN/WSe2 | ~1 × 102 | ±5 v | 15 ns | 10 s | IV | × |

| [27] | Al2O3/HfO2/Al2O3/MoS2 | <1 × 103 | ±26 v | 200 ms | - | II | × |

| [29] | MoS2/BN/WSe2 | ~1 × 102 | ±5 v | 40 ns | 14 s | III | × |

| [30] | HfO2/Metal/HfO2/MoS2 | ~1 × 105 | ±15 v | 100 ms | 10 year | II | × |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, K.; Liu, H.; Wang, S.; Yu, W.; Han, T. Comprehensive Performance Quasi-Non-Volatile Memory Compatible with Large-Scale Preparation by Chemical Vapor Deposition. Nanomaterials 2020, 10, 1471. https://doi.org/10.3390/nano10081471

Yang K, Liu H, Wang S, Yu W, Han T. Comprehensive Performance Quasi-Non-Volatile Memory Compatible with Large-Scale Preparation by Chemical Vapor Deposition. Nanomaterials. 2020; 10(8):1471. https://doi.org/10.3390/nano10081471

Chicago/Turabian StyleYang, Kun, Hongxia Liu, Shulong Wang, Wenlong Yu, and Tao Han. 2020. "Comprehensive Performance Quasi-Non-Volatile Memory Compatible with Large-Scale Preparation by Chemical Vapor Deposition" Nanomaterials 10, no. 8: 1471. https://doi.org/10.3390/nano10081471

APA StyleYang, K., Liu, H., Wang, S., Yu, W., & Han, T. (2020). Comprehensive Performance Quasi-Non-Volatile Memory Compatible with Large-Scale Preparation by Chemical Vapor Deposition. Nanomaterials, 10(8), 1471. https://doi.org/10.3390/nano10081471