Co-Design of the Control and Power Stages of a Boost-Based Rectifier with Power Factor Correction Depending on Performance Criteria

Abstract

:1. Introduction

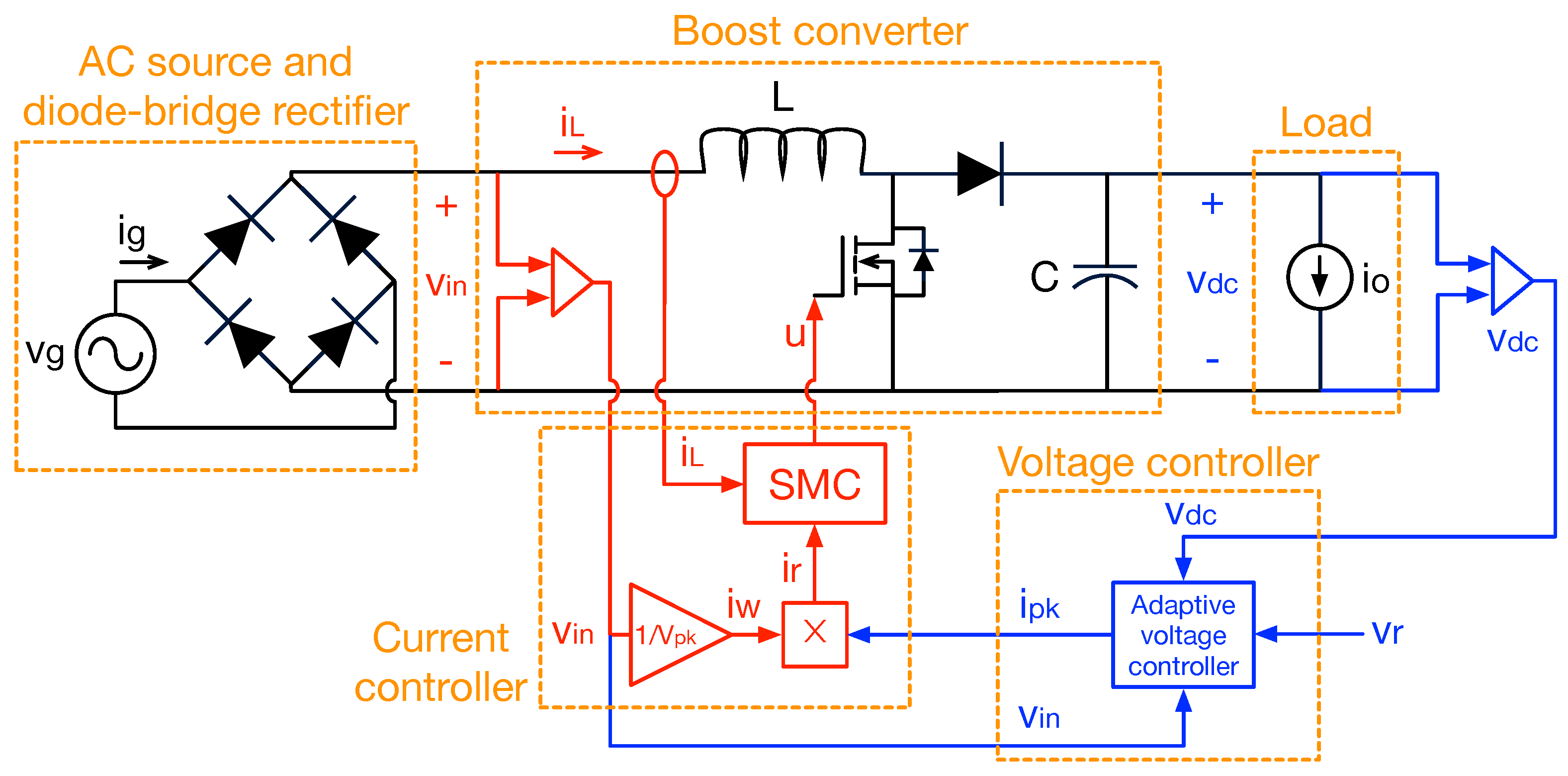

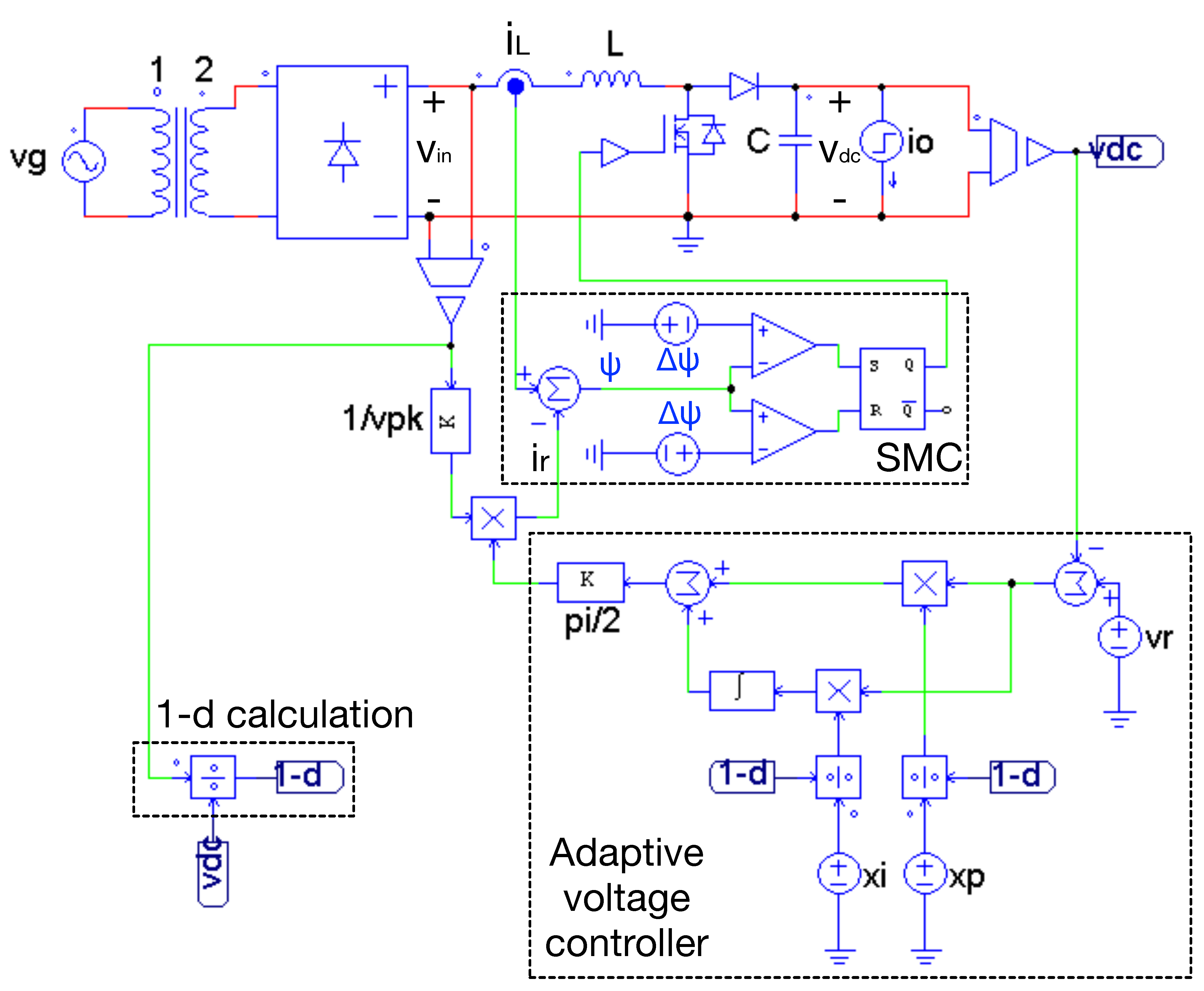

2. Materials and Methods

2.1. Circuital and Mathematical Models

2.2. Current Controller

2.2.1. Transversality Condition

2.2.2. Reachability Conditions

- When the system () is operating under the surface (), the derivative of the switching function must be positive to reach the surface:

- When the system () is operating above the surface (), the derivative of the switching function must be negative to reach the surface:

2.2.3. Equivalent Control Condition

2.2.4. Practical Implementation

2.2.5. SMC Circuit

2.3. Design of the Inductor to Guarantee Global Stability

2.4. Voltage Controller and Capacitor Design

2.4.1. Equivalent Model of the Current and Voltage Loops

2.4.2. Adaptive Controller Design

- The reference for the averaged DC voltage is constant.

- The load current is the main perturbation for the average DC voltage. This design is performed for the worst-case scenario, which corresponds to a step change in the load current as given in (43), where is the step size.

- The maximum deviation allowed for the average DC voltage is .

- The maximum settling time (2% criterion) for recovering the average DC voltage is .

- The waveform of the average DC voltage must have a damping ratio .

2.4.3. Capacitor Design to Ensure the Average Voltage Deviation

2.5. Low-Frequency Ripple in the DC Voltage

2.6. Design Procedure and Application Example

2.6.1. Design of the Inductor and Hysteresis Band

- Left zone: a zone where Equation (35) is fulfilled, thus the system is stable, but the switching frequency is higher than 300 kHz.

- Right zone: a zone where Equation (23) ensures 300 kHz, but the system is unstable.

- Bottom zone: a zone where the system is unstable and > 300 kHz.

- Top zone: a zone where both global stability and and 300 kHz are ensured.

2.6.2. Design of the Capacitor and Controller Parameters

2.6.3. Summary of the Design Process

3. Results

4. Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- De Castro Pereira, D.; Da Silva, M.R.; Silva, E.M.; Tofoli, F.L. Comprehensive review of high power factor AC-DC boost converters for PFC applications. Int. J. Electron. 2015, 102, 1361–1381. [Google Scholar] [CrossRef]

- Ortiz-Castrillón, J.R.; Mejía-Ruíz, G.E.; Muñoz-Galeano, N.; López-Lezama, J.M.; Saldarriaga-Zuluaga, S.D. PFC Single-Phase AC/DC Boost Converters: Bridge, Semi-Bridgeless, and Bridgeless Topologies. Appl. Sci. 2021, 11, 7651. [Google Scholar] [CrossRef]

- IEC 61000-3-2:2018; Electromagnetic Compatibility (EMC)—Part 3-2: Limits—Limits for Harmonic Current Emissions (Equipment Input CURRENT ≤16 A Per Phase). IEC: Geneva, Switzerland, 2018.

- IEEE. IEEE 519-2014—IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems; IEEE: Piscataway, NJ, USA, 2014. [Google Scholar]

- Memon, A.H.; Ali, R.; Memon, Z.A. Discontinuous conduction mode Buck converter with high efficiency. 3C Tecnol. 2021, 10, 35–51. [Google Scholar] [CrossRef]

- González-Castaño, C.; Restrepo, C.; Sanz, F.; Chub, A.; Giral, R. DC Voltage Sensorless Predictive Control of a High-Efficiency PFC Single-Phase Rectifier Based on the Versatile Buck-Boost Converter. Sensors 2021, 21, 5107. [Google Scholar] [CrossRef]

- Kamalapathi, K.; Priyadarshi, N.; Padmanaban, S.; Holm-Nielsen, J.B.; Azam, F.; Umayal, C.; Ramachandaramurthy, V.K. A Hybrid Moth-Flame Fuzzy Logic Controller Based Integrated Cuk Converter Fed Brushless DC Motor for Power Factor Correction. Electronics 2018, 7, 288. [Google Scholar] [CrossRef] [Green Version]

- Umamaheswari, M.G.; Uma, G.; Vijayalakshmi, K.M. Design and implementation of reduced-order sliding mode controller for higher-order power factor correction converters. IET Power Electron. 2011, 4, 984–992. [Google Scholar] [CrossRef]

- Yang, J.W.; Do, H.L. Efficient Single-Switch Boost-Dual-Input Flyback PFC Converter With Reduced Switching Loss. IEEE Trans. Ind. Electron. 2015, 62, 7460–7468. [Google Scholar] [CrossRef]

- Garcia-Sanchez, J.R.; Hernandez-Marquez, E.; Ramirez-Morales, J.; Marciano-Melchor, M.; Marcelino-Aranda, M.; Taud, H.; Silva-Ortigoza, R. A Robust Differential Flatness-Based Tracking Control for the ‘MIMO DC/DC Boost Converter-Inverter-DC Motor’ System: Experimental Results. IEEE Access 2019, 7, 84497–84505. [Google Scholar] [CrossRef]

- Montoya, O.D.; Serra, F.M.; Gil-González, W.; Asensio, E.M.; Bosso, J.E. An IDA-PBC Design with Integral Action for Output Voltage Regulation in an Interleaved Boost Converter for DC Microgrid Applications. Actuators 2022, 11, 5. [Google Scholar] [CrossRef]

- Hoyos Velasco, C.I.; Hoyos Velasco, F.E.; Candelo-Becerra, J.E. Nonlinear dynamics and performance analysis of a buck converter with hysteresis control. Computation 2021, 9, 112. [Google Scholar] [CrossRef]

- Trujillo, S.C.; Candelo-Becerra, J.E.; Hoyos, F.E. Performance of the boost converter controlled with ZAD to regulate dc signals. Computation 2021, 9, 96. [Google Scholar] [CrossRef]

- Wang, Y.; Yang, Y.; Chen, Y.; Pan, T.C.; Guo, C.; Xia, A. Adaptive total sliding mode control for the current of power factor correction circuit. IEICE Electron. Express 2018, 15, 1–12. [Google Scholar] [CrossRef] [Green Version]

- Pandey, A.; Kothari, D.P.; Singh, B. Sliding mode control of PFC converter. IETE J. Res. 2005, 51, 371–377. [Google Scholar] [CrossRef]

- Kessal, A.; Lazhar, R.; Gaubert, J.P.; Mohammed, M. Analysis and design of an isolated single-phase power factor corrector with a fast regulation. Electr. Power Syst. Res. 2011, 81, 1825–1831. [Google Scholar] [CrossRef]

- Genc, N.; Iskender, I. DSP-based current sharing of average current controlled two-cell interleaved boost power factor correction converter. IET Power Electron. 2011, 4, 1015–1022. [Google Scholar] [CrossRef]

- Bosque-Moncusi, J.M.; Valderrama-Blavi, H.; Flores-Bahamonde, F.; Vidal-Idiarte, E.; Martínez-Salamero, L. Using low-cost microcontrollers to implement variable hysteresis-width comparators for switching power converters. IET Power Electron. 2018, 11, 787–795. [Google Scholar] [CrossRef]

- Chiang, H.C.; Lin, F.J.; Chang, J.K.; Chen, K.F.; Chen, Y.L.; Liu, K.C. Control method for improving the response of single-phase continuous conduction mode boost power factor correction converter. IET Power Electron. 2016, 9, 1792–1800. [Google Scholar] [CrossRef]

- Marcos-Pastor, A.; Vidal-Idiarte, E.; Cid-Pastor, A.; Martinez-Salamero, L. Interleaved Digital Power Factor Correction Based on the Sliding-Mode Approach. IEEE Trans. Power Electron. 2016, 31, 4641–4653. [Google Scholar] [CrossRef]

- Wu, S.T.; Chen, F.Y.; Chien, M.C.; Wang, J.M.; Su, Y.Y. A Hybrid Control Scheme with Fast Transient and Low Harmonic for Boost PFC Converter. Electronics 2021, 10, 1848. [Google Scholar] [CrossRef]

- Kessal, A.; Rahmani, L. Ga-optimized parameters of sliding-mode controller based on both output voltage and input current with an application in the PFC of AC/DC converters. IEEE Trans. Power Electron. 2014, 29, 3159–3165. [Google Scholar] [CrossRef]

- Zhou, Y.; Wang, B.L. PWM-quasi-sliding mode control for APFC converters. Electr. Eng. 2010, 92, 43–48. [Google Scholar] [CrossRef]

- Karabacak, M.; Poyraz, G. Robust adaptive control of pulse-width modulated rectifiers based on adaptive super-twisting sliding-mode and state feedback controllers. Electr. Power Compon. Syst. 2015, 43, 1289–1296. [Google Scholar] [CrossRef]

- Mohanty, P.R.; Panda, A.K. Fixed-Frequency Sliding-Mode Control Scheme Based on Current Control Manifold for Improved Dynamic Performance of Boost PFC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 576–586. [Google Scholar] [CrossRef]

- Kayisli, K.; Tuncer, S.; Poyraz, M. A Novel Power Factor Correction System Based on Sliding Mode Fuzzy Control. Electr. Power Compon. Syst. 2017, 45, 430–441. [Google Scholar] [CrossRef]

- Seleme, S.I.; Rosa, A.H.; Morais, L.M.; Donoso-Garcia, P.F.; Cortizo, P.C. Evaluation of adaptive passivity-based controller for power factor correction using a boost converter. IET Control. Theory Appl. 2012, 6, 2168–2178. [Google Scholar] [CrossRef]

- Karami, Z.; Shafiee, Q.; Khayat, Y.; Yaribeygi, M.; Dragicevic, T.; Bevrani, H. Decentralized Model Predictive Control of DC Microgrids with Constant Power Load. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 451–460. [Google Scholar] [CrossRef]

- Rasoolzadeh, A.; Salmasi, F.R. Reduced-order dynamic model for droop-controlled inverter/converter-based low-voltage hybrid AC/DC microgrids - part 2: DC sub-microgrid and power exchange. IET Smart Grid 2018, 1, 134–142. [Google Scholar] [CrossRef]

- Chatrenour, N.; Razmi, H.; Doagou-Mojarrad, H. Improved double integral sliding mode MPPT controller based parameter estimation for a stand-alone photovoltaic system. Energy Convers. Manag. 2017, 139, 97–109. [Google Scholar] [CrossRef]

- Taheri, B.; Sedaghat, M.; Bagherpour, M.A.; Farhadi, P. A New Controller for DC-DC Converters Based on Sliding Mode Control Techniques. J. Control. Autom. Electr. Syst. 2019, 30, 63–74. [Google Scholar] [CrossRef]

- Sira-Ramirez, H. Sliding Motions in Bilinear Switched Networks. IEEE Trans. Circuits Syst. 1987, 34, 919–933. [Google Scholar] [CrossRef]

- Sira-Ramirez, H. Nonlinear variable structure systems in sliding mode: The general case. IEEE Trans. Autom. Control. 1989, 34, 1186–1188. [Google Scholar] [CrossRef]

- Villegas Ceballos, J.P.; Serna-Garcés, S.I.; González Montoya, D.; Ramos-Paja, C.A.; Bastidas-Rodríguez, J.D. Charger/discharger DC/DC converter with interleaved configuration for DC-bus regulation and battery protection. Energy Sci. Eng. 2019, 8, 530–543. [Google Scholar] [CrossRef] [Green Version]

- Henao-Bravo, E.E.; Saavedra-Montes, A.J.; Ramos-Paja, C.A.; Bastidas-Rodriguez, J.D.; Gonzalez Montoya, D. Charging/discharging system based on zeta/sepic converter and a sliding mode controller for dc bus voltage regulation. IET Power Electron. 2020, 13, 1515–1527. [Google Scholar] [CrossRef]

- Umamaheswari, M.G.; Uma, G.; Vijayalakshmi, K.M. Analysis and design of reduced-order sliding-mode controller for three-phase power factor correction using Cuk rectifiers. IET Power Electron. 2013, 6, 935–945. [Google Scholar] [CrossRef]

- Gonzalez Montoya, D.; Ramos-Paja, C.; Giral, R. Improved design of sliding mode controllers based on the requirements of MPPT techniques. IEEE Trans. Power Electron. 2016, 31, 235–247. [Google Scholar] [CrossRef] [Green Version]

- Intersil. HA-2557 130 MHz, Four Quadrant, Current Output Analog Multiplier. 2002. Available online: https://www.alldatasheet.com/datasheet-pdf/pdf/122864/INTERSIL/HA-2557.html (accessed on 30 March 2022).

- Fairchild Semiconductor. RC4200 Analog Multiplier. 2001. Available online: https://www.alldatasheet.com/datasheet-pdf/pdf/54398/FAIRCHILD/RC4200.html (accessed on 30 March 2022).

- Analog Devices. AD533 Low Cost IC Multiplier, Divider, Squarer, Square Rooter. 2022. Available online: https://www.analog.com/en/products/ad533.html (accessed on 30 March 2022).

- Alsmadi, Y.M.; Utkin, V.; Haj-ahmed, M.A.; Xu, L. Sliding mode control of power converters: DC/DC converters. Int. J. Control. 2018, 91, 2472–2493. [Google Scholar] [CrossRef]

| Perturbation | Main Cause | Main Effect |

|---|---|---|

| Change in | Connection/disconnection of loads | Reduction/increment in |

| Change in | Sag/swell in grid voltage | Reduction/increment in |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 84.85 V | 220 V | ||

| 60 Hz | 300 kHz | ||

| 1 A | 2 A | ||

| −10 V | 4 V | ||

| 0.707 | 100 ms |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramos-Paja, C.A.; Saavedra-Montes, A.J.; Bastidas-Rodriguez, J.D. Co-Design of the Control and Power Stages of a Boost-Based Rectifier with Power Factor Correction Depending on Performance Criteria. Computation 2022, 10, 61. https://doi.org/10.3390/computation10040061

Ramos-Paja CA, Saavedra-Montes AJ, Bastidas-Rodriguez JD. Co-Design of the Control and Power Stages of a Boost-Based Rectifier with Power Factor Correction Depending on Performance Criteria. Computation. 2022; 10(4):61. https://doi.org/10.3390/computation10040061

Chicago/Turabian StyleRamos-Paja, Carlos Andres, Andres Julian Saavedra-Montes, and Juan David Bastidas-Rodriguez. 2022. "Co-Design of the Control and Power Stages of a Boost-Based Rectifier with Power Factor Correction Depending on Performance Criteria" Computation 10, no. 4: 61. https://doi.org/10.3390/computation10040061

APA StyleRamos-Paja, C. A., Saavedra-Montes, A. J., & Bastidas-Rodriguez, J. D. (2022). Co-Design of the Control and Power Stages of a Boost-Based Rectifier with Power Factor Correction Depending on Performance Criteria. Computation, 10(4), 61. https://doi.org/10.3390/computation10040061