Four-Switch Three-Phase PMSM Converter with Output Voltage Balance and DC-Link Voltage Offset Suppression

Abstract

:1. Introduction

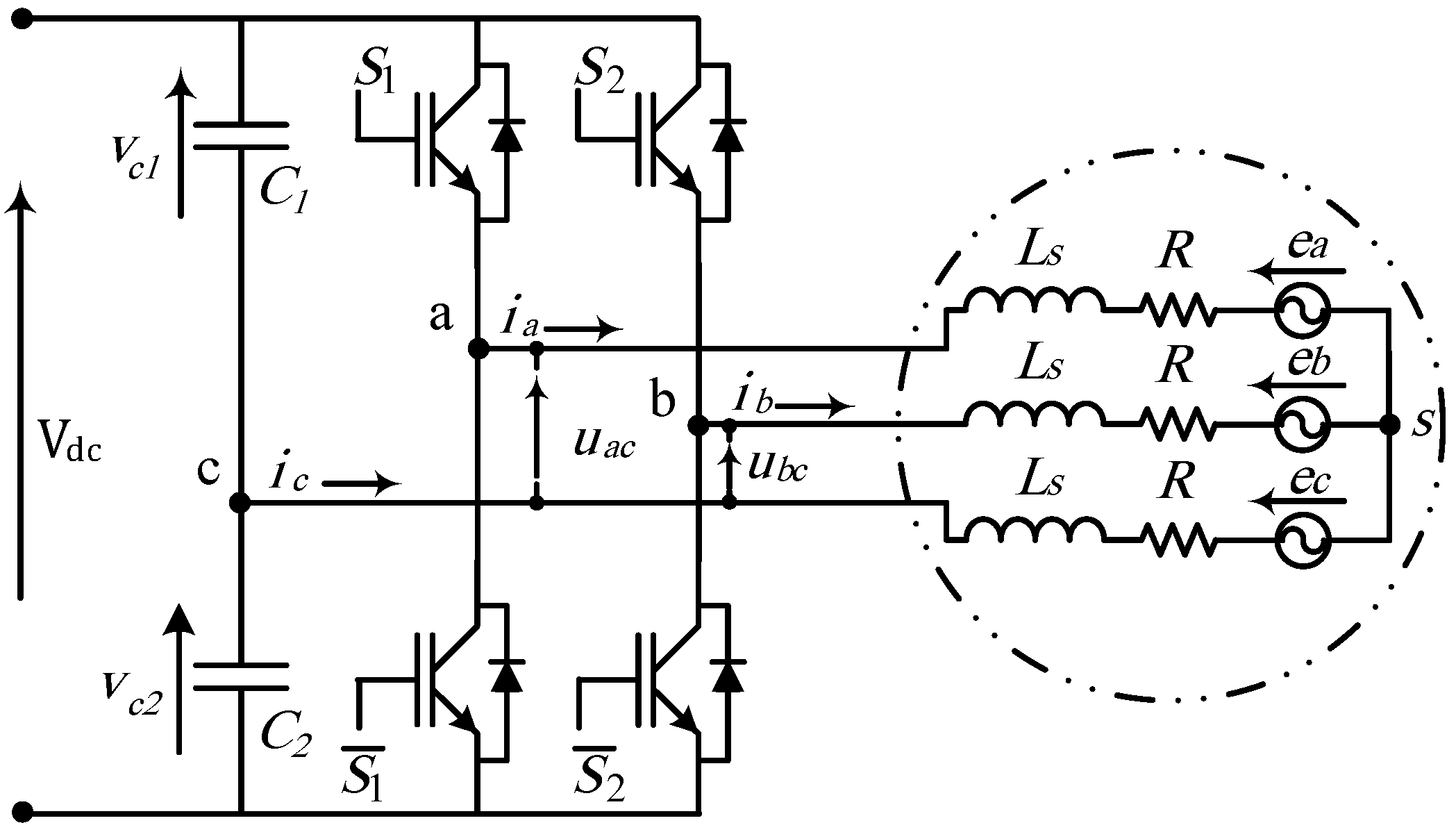

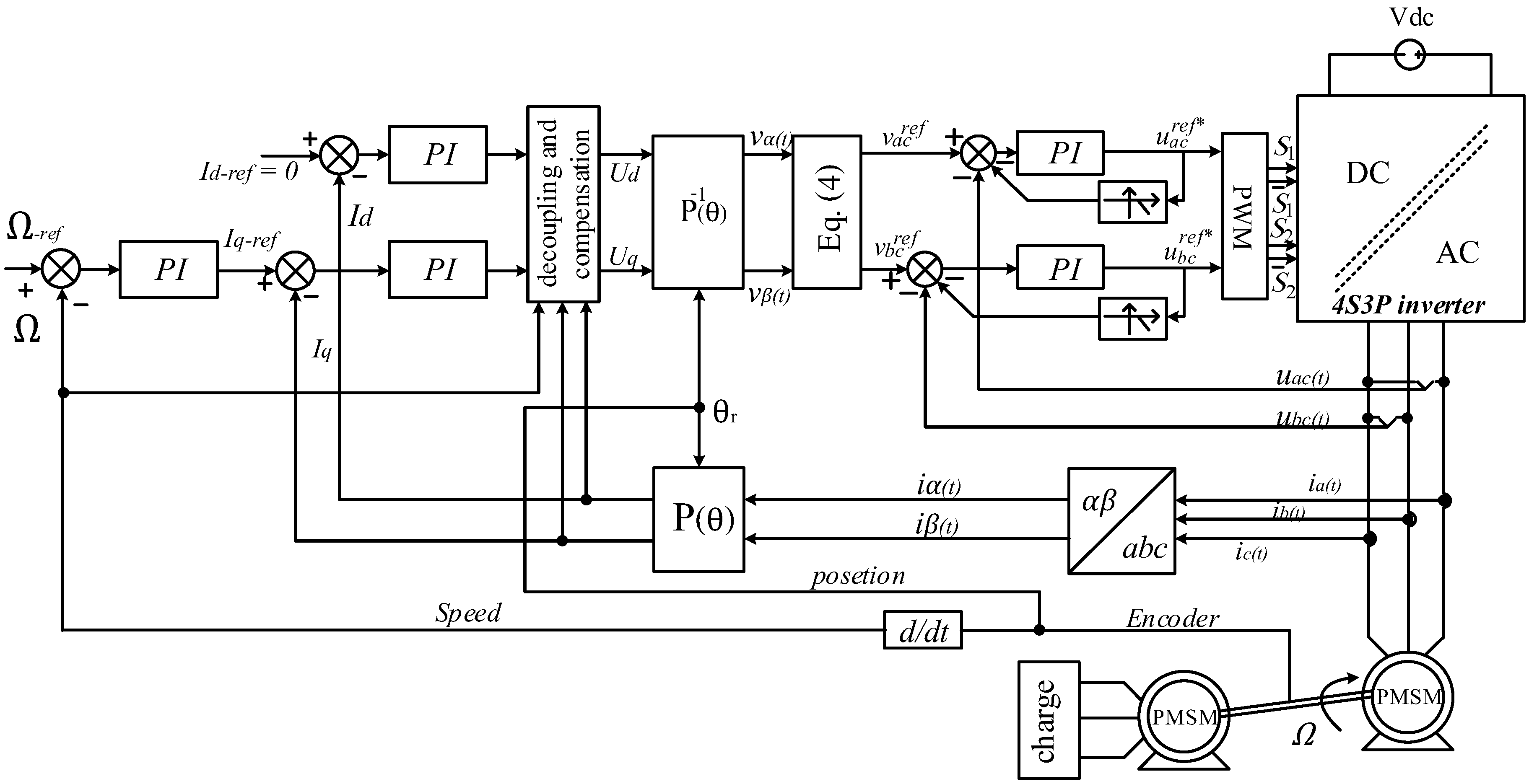

2. Four-Switch Three-Phase Inverter for PMSM Drives

2.1. 4S3P Inverter Configuration and Operation

2.2. PMSM Modelling and Current Ripple Determination

3. Four-Switch Three-Phase Inverter Voltage Balance

4. Simulation and Experimental Results

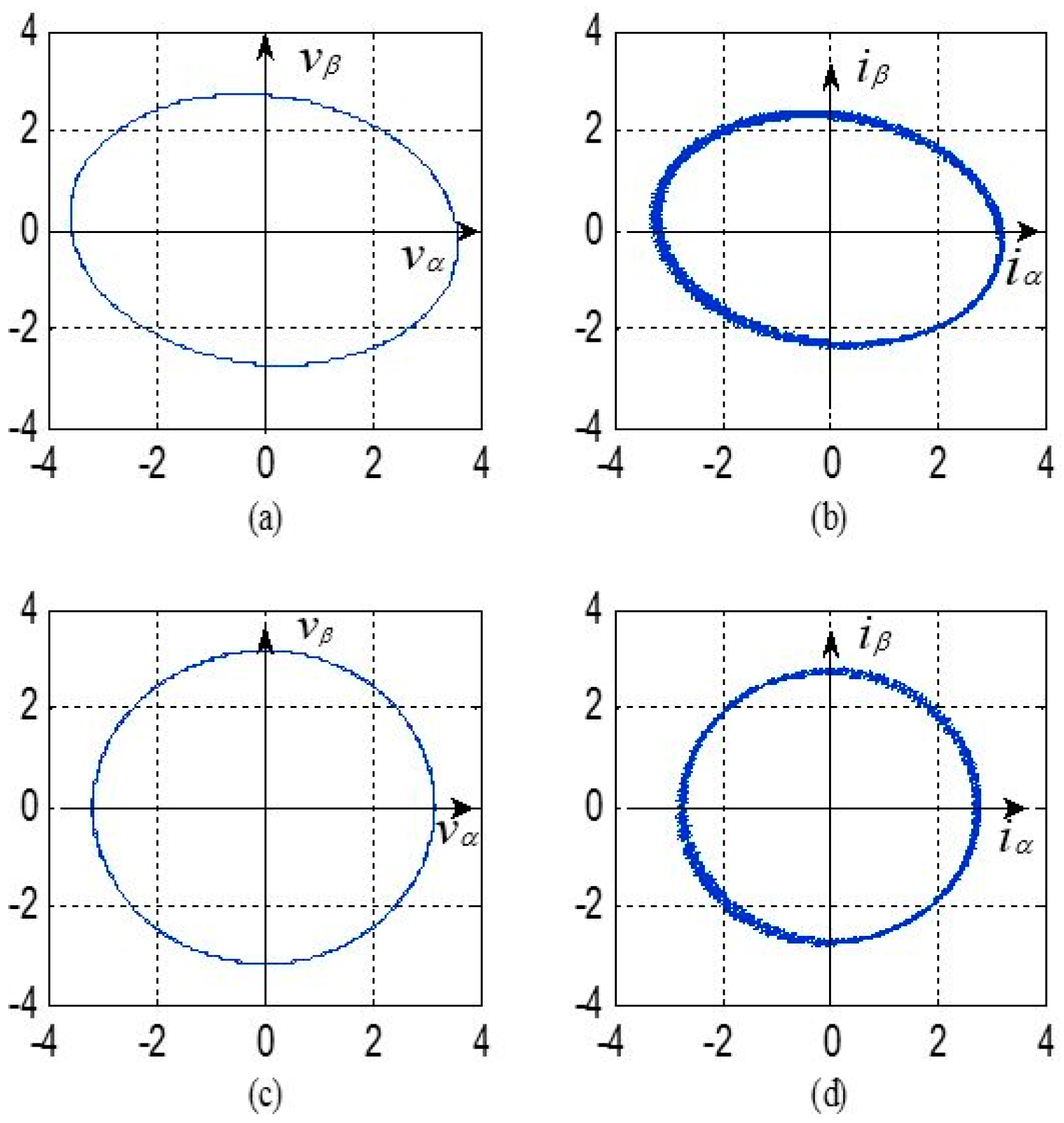

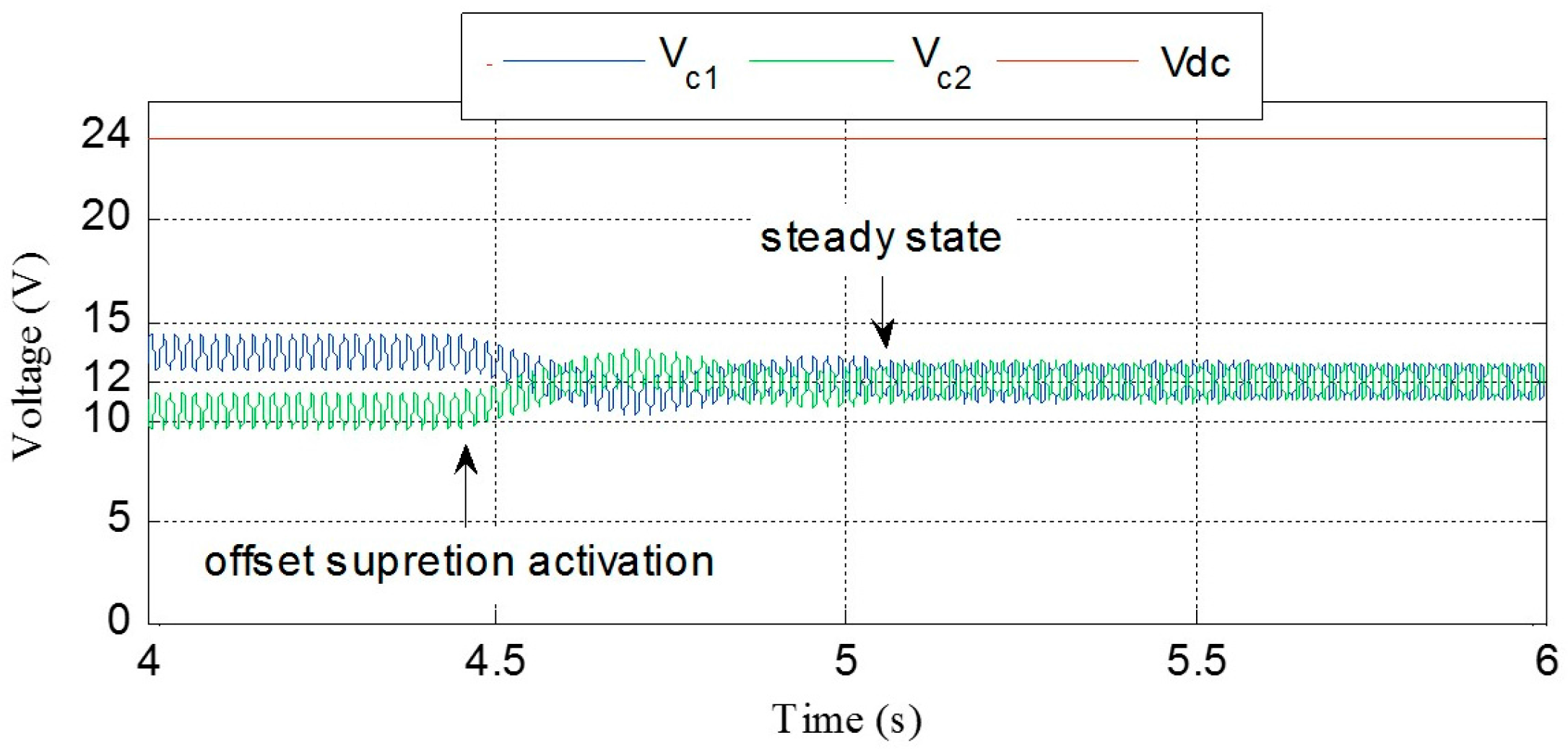

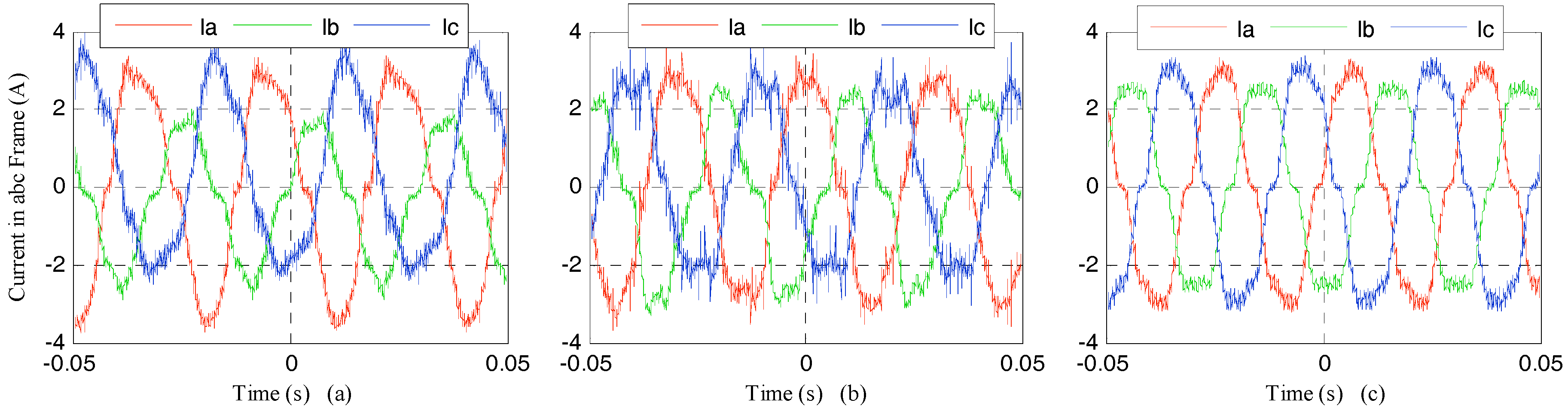

4.1. Simulation Studies

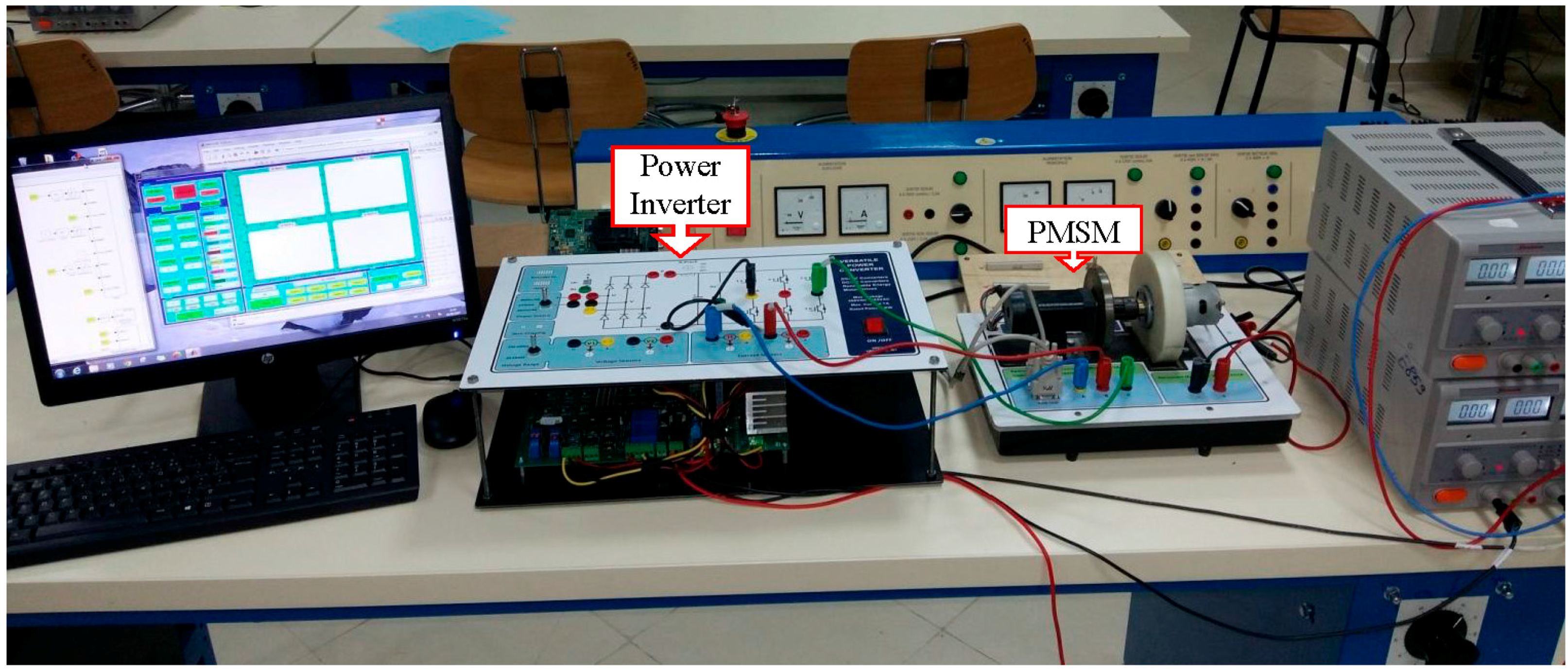

4.2. Experimental Evaluation

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Van der Broeck, H.W.; Van Wyk, J.D. A Comparative Investigation of a Three-Phase Induction Machine Drive with a Component Minimized Voltage-Fed Inverter under Different Control Options. IEEE Trans. Ind. Appl. 1984, 20, 309–320. [Google Scholar] [CrossRef]

- Lee, D.-M.; Park, J.-B.; Toliyat, H.A. A Simple Current Ripple Reduction Method for B4 Inverters. J. Electr. Eng. Technol. 2013, 8, 1062–1069. [Google Scholar] [CrossRef]

- Pan, L.; Wang, B.; Su, G.; Cheng, B.; Peng, G. A Novel Space Vector modulation Scheme and Direct Torque Control for Four-switch BLDCM Using Flux Observer. J. Electr. Eng. Technol. 2015, 10, 251–260. [Google Scholar] [CrossRef]

- Lin, C.-T.; Hung, C.-W.; Liu, C.-W. Position sensorless control for four-switch three-phase brushless DC motor drives. IEEE Trans. Power Electron. 2008, 23, 438–444. [Google Scholar] [CrossRef]

- Trinh, Q.-N.; Lee, H.-H. Low Cost and High Performance UPQC with Four-Switch Three-Phase Inverters. J. Electr. Eng. Technol. 2015, 10, 1015–1024. [Google Scholar] [CrossRef]

- Welchko, B.A.; Lipo, T.A.; Jahns, T.M.; Schulz, S.E. Fault tolerant three-phase AC motor drive topologies: A comparison of features, cost, and limitations. IEEE Trans. Power Electron. 2004, 19, 1108–1116. [Google Scholar] [CrossRef]

- Errabelli, R.R.; Mutschler, P. Fault-Tolerant Voltage Source Inverter for Permanent Magnet Drives. IEEE Trans. Power Electron. 2012, 27, 500–508. [Google Scholar] [CrossRef]

- Freire, N.M.A.; Marques Cardoso, A.J. A Fault-Tolerant Direct Controlled PMSG Drive for Wind Energy Conversion Systems. IEEE Trans. Power Electron. 2014, 61, 821–834. [Google Scholar] [CrossRef]

- Lin, C.K.; Yu, J.T.; Lai, Y.S.; Yu, H.C.; Peng, C.I. Two-vector-based modeless predictive current control for four-switch inverter-fed synchronous reluctance motors emulating the six-switch inverter operation. Electron. Lett. 2016, 52, 1244–1246. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H.-H.; Nguyen, H.M. Adaptive Carrier-based PWM for a Four-Switch Three-Phase Inverter under DC-link Voltage Ripple Conditions. J. Electr. Eng. Technol. 2010, 5, 290–298. [Google Scholar] [CrossRef]

- Kim, J.; Hong, J.; Nam, K. A Current Distortion Compensation Scheme for Four-Switch Inverters. IEEE Trans. Power Electron. 2009, 24, 1032–1040. [Google Scholar]

- Blaabjerg, F.; Neacsu, D.O.; Pedersen, J.K. Adaptive SVM to compensate DC-Link voltage ripple for four-switch three-phase voltage-source inverters. IEEE Trans. Power Electron. 1999, 14, 743–752. [Google Scholar] [CrossRef]

- Fadil, H.; Driss, Y.; Aite Driss, Y.; Elafyani, M.L.; Abd Rahim, N. Sliding-Mode Speed Control of PMSM with Fuzzy-Logic Chattering Minimization—Design and Implementation. Information 2015, 6, 432–442. [Google Scholar]

- Fadil, H.; Yousfi, D.; Driss, Y.A.; Nasrudin, A.R. Synchronization Techniques benchmarking of grid fault modes in single-phase Systems. In Proceedings of the Renewable and Sustainable Energy Conference, Ouarzazat, Morocco, 17–19 October 2014.

- Pillay, P.; Krishnan, R. Modeling of Permanent Magnet Motor Drives. IEEE Trans. Ind. Electron. 1988, 35, 537–541. [Google Scholar] [CrossRef]

- Dasgupta, S.; Mohan, S.N.; Sahoo, S.K.; Panda, S.K. Application of four-switch-based three-phase grid-connected inverter to connect renewable energy source to a generalized unbalanced microgrid system. IEEE Trans. Ind. Electron. 2013, 60, 1204–1215. [Google Scholar] [CrossRef]

- Zeng, Z.; Zheng, W.; Zhao, R. Performance Analysis of the Zero-Voltage Vector Distribution in Three-Phase Four-Switch Converter Using a Space Vector Approach. IEEE Trans. Power Electron. 2017, 9, 1732–1740. [Google Scholar] [CrossRef]

- Hu, Y.; Gan, C.; Cao, W.; Li, W. Central-Tapped Node Linked Modular Fault Tolerance Topology for SRM Based EV/HEV Applications. IEEE Trans. Power Electron. 2016, 31, 1541–1554. [Google Scholar] [CrossRef]

- Zeng, Z.Y.; Zheng, W.Y.; Zhao, R.X.; Zhu, C.; Yuan, Q.W. Modelling modulation and control of the three-phase four-switch PWM rectifier under balanced voltage. IEEE Trans. Power Electron. 2016, 31, 4892–4905. [Google Scholar]

- Wang, W.; Luo, A.; Xu, X.Y.; Fang, L.; Thuyen, C.M.; Li, Z. Space vector pulse-width modulation algorithm and DC-side voltage control strategy of three-phase four-switch active power filters. IET Power Electron. 2013, 6, 125–135. [Google Scholar] [CrossRef]

- Wang, R.; Zhao, J.; Liu, Y. A comprehensive investigation of four-switch three-phase voltage source inverter based on double Fourier integral analysis. IEEE Trans. Power Electron. 2011, 26, 2774–2787. [Google Scholar] [CrossRef]

| Components | Values | Components | Values |

|---|---|---|---|

| DC-voltage | 24 V | DC-link upper capacitor C1 | 4400 µF |

| PWM frequency | FPWM = 12 kHz | DC-link lower capacitor C2 | 4400 µF |

| Sampling | Fs = 10 kHz | Inverter rated power | 1 kW |

| Components | Values | Components | Values |

|---|---|---|---|

| Rated power | p = 80 W | Pole pairs | 4 |

| Rated speed | 4000 rpm | Viscous friction | fr = 0.04·10−3 Kg·m2 |

| Resistance and inductance | R = 0.43 Ω, L = 1.35 mH | Rotation inertia | J = 0.5·10−3 Nm/rad |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hicham, F.; Yousfi, D.; Mohamed Larbi, E.; Youness, A.D. Four-Switch Three-Phase PMSM Converter with Output Voltage Balance and DC-Link Voltage Offset Suppression. Information 2017, 8, 11. https://doi.org/10.3390/info8010011

Hicham F, Yousfi D, Mohamed Larbi E, Youness AD. Four-Switch Three-Phase PMSM Converter with Output Voltage Balance and DC-Link Voltage Offset Suppression. Information. 2017; 8(1):11. https://doi.org/10.3390/info8010011

Chicago/Turabian StyleHicham, Fadil, Driss Yousfi, Elhafyani Mohamed Larbi, and Aite Driss Youness. 2017. "Four-Switch Three-Phase PMSM Converter with Output Voltage Balance and DC-Link Voltage Offset Suppression" Information 8, no. 1: 11. https://doi.org/10.3390/info8010011

APA StyleHicham, F., Yousfi, D., Mohamed Larbi, E., & Youness, A. D. (2017). Four-Switch Three-Phase PMSM Converter with Output Voltage Balance and DC-Link Voltage Offset Suppression. Information, 8(1), 11. https://doi.org/10.3390/info8010011