Modeling a Dual-Mode Controller Design for a Quasi-Resonant Flyback Converter

Abstract

:1. Introduction

- (1).

- A quadratic prediction strategy for SPAACE to increase prediction accuracy.

- (2).

- A dead-zone band supplemental strategy for SPAACE to improve set point tracking.

- (3).

- An approach to implement SPAACE in unbalanced systems.

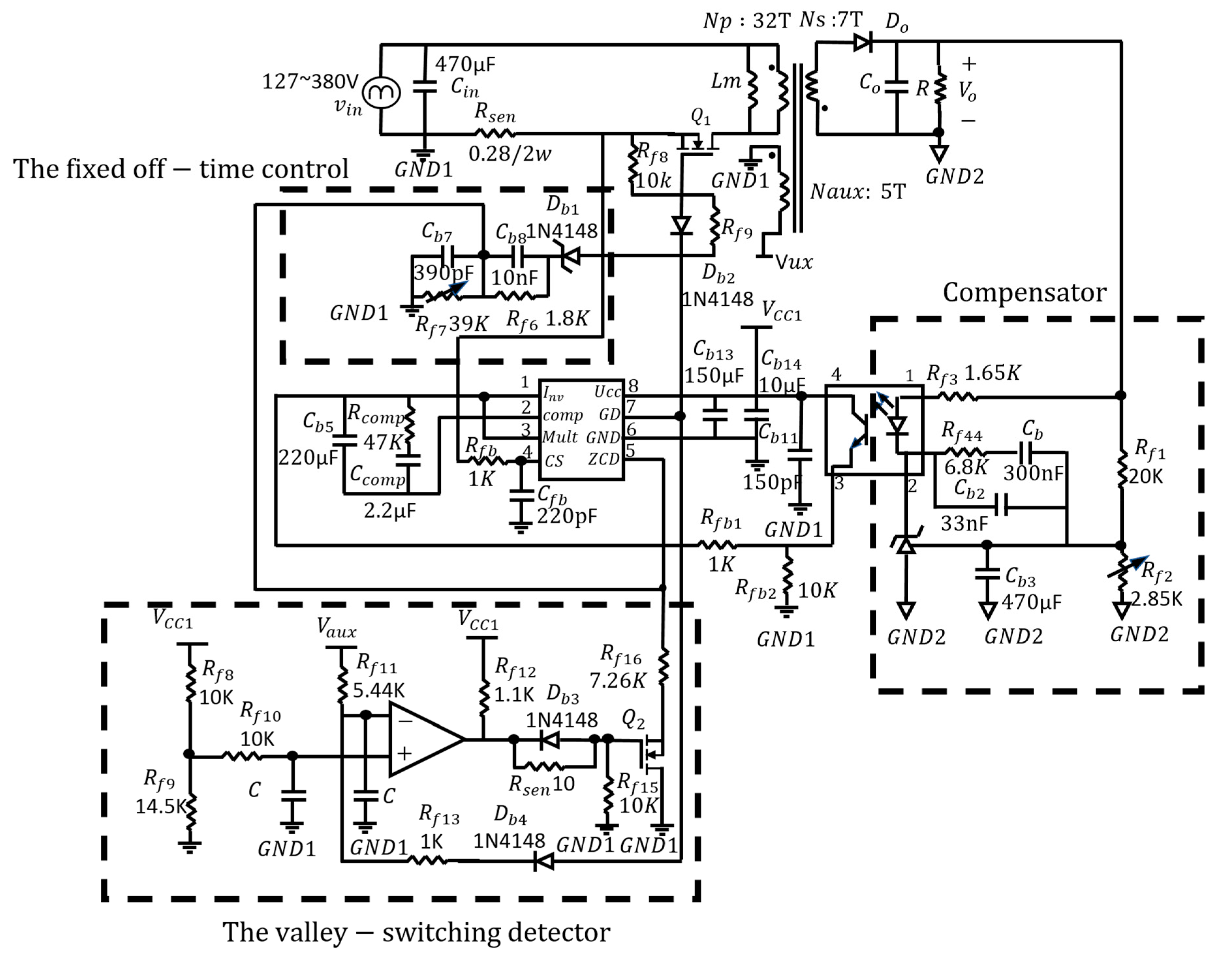

2. QRF Converter with Dual-Mode Control

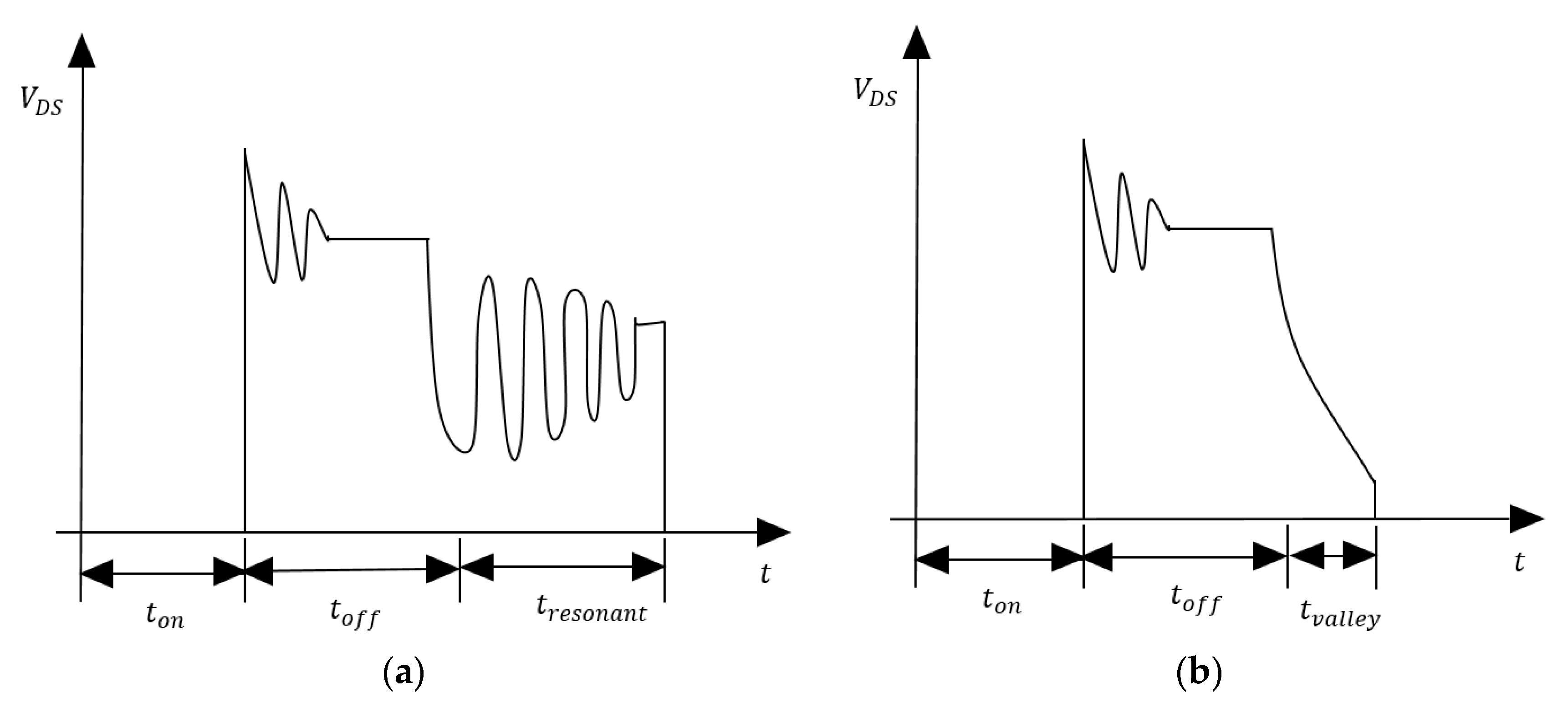

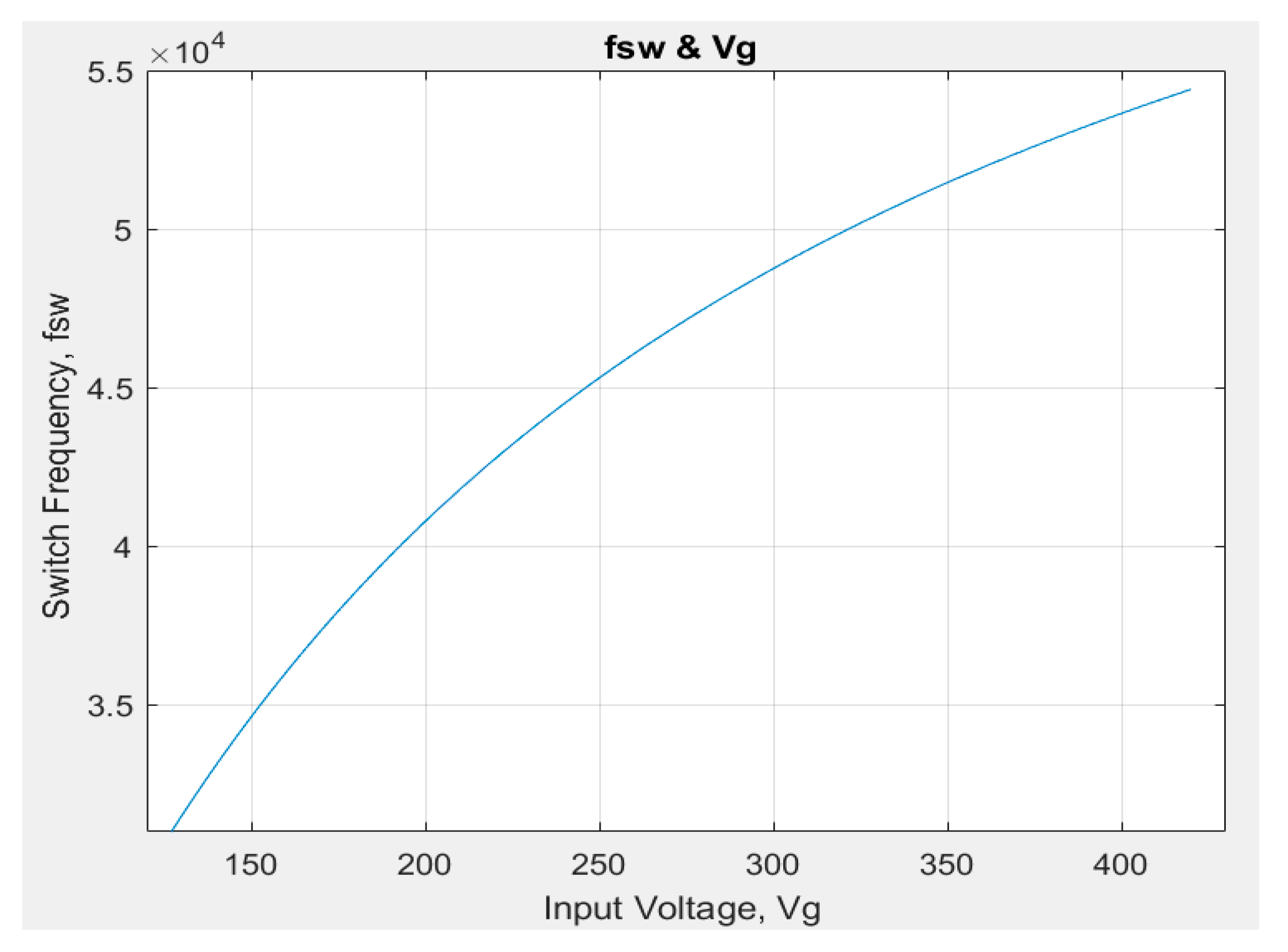

2.1. Single-Switch Flyback Converter

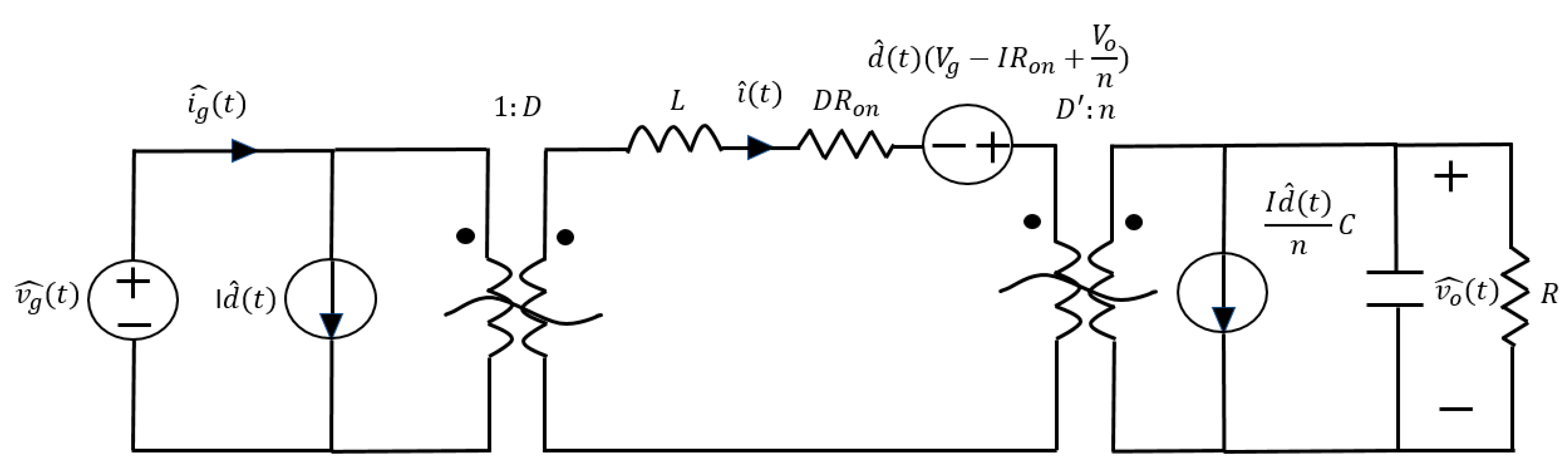

2.2. Small-Signal AC Model

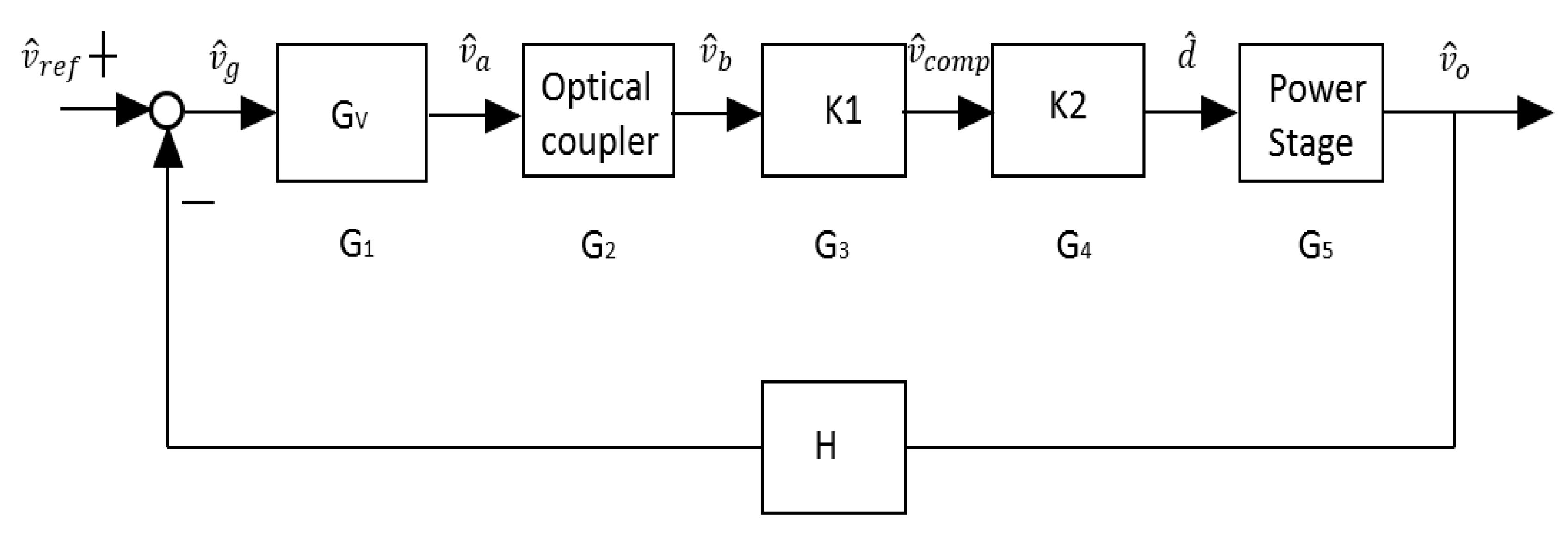

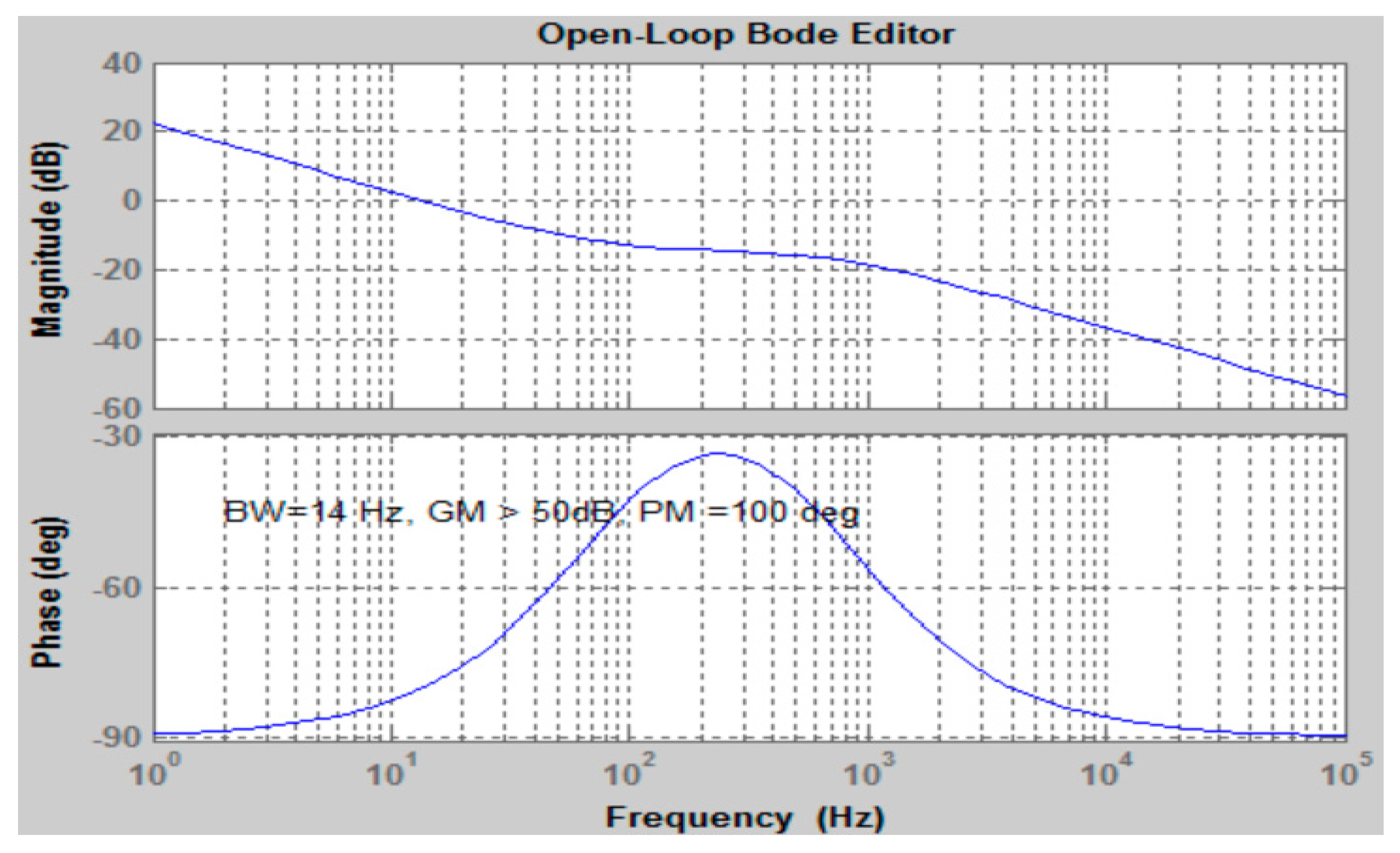

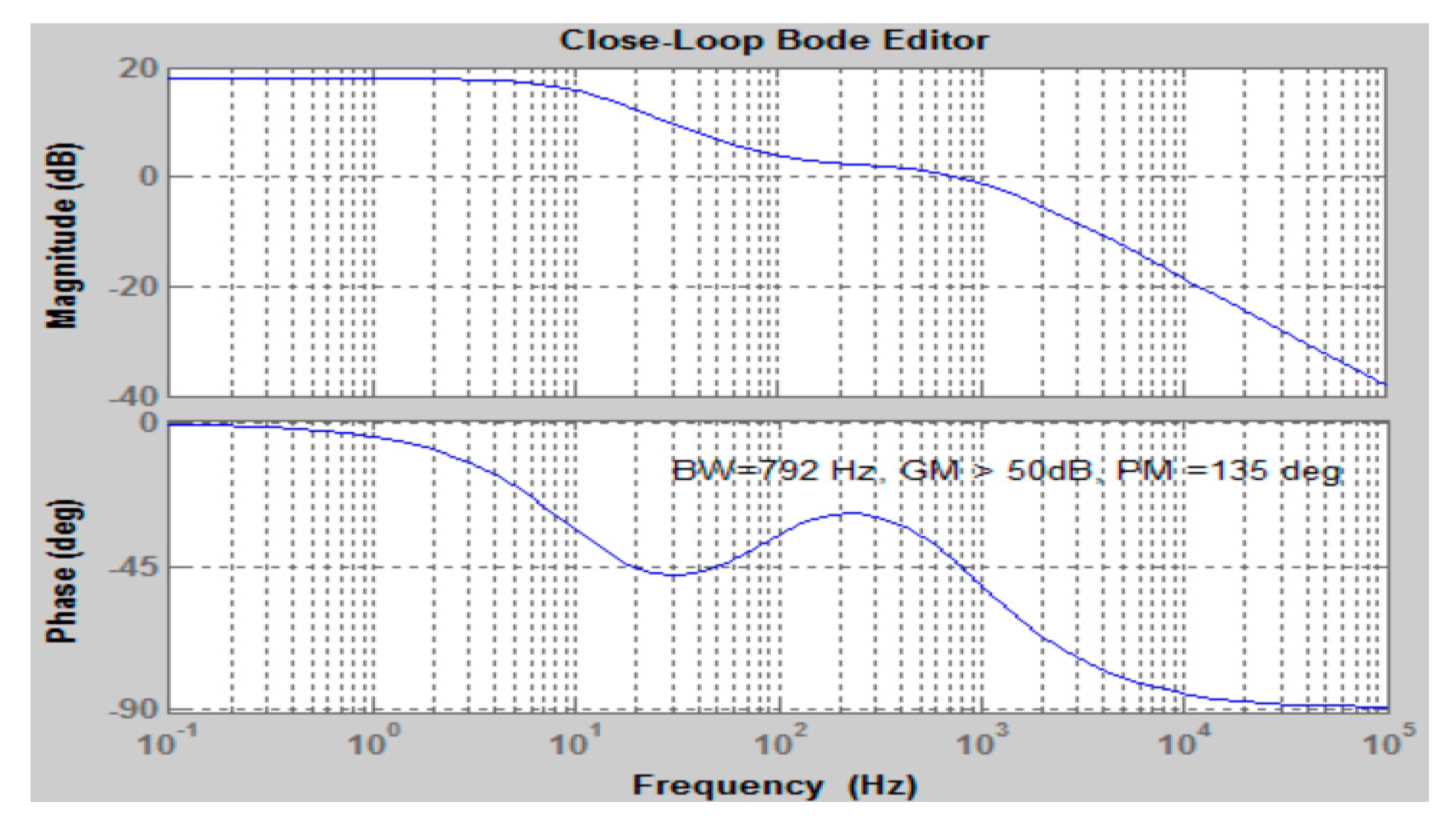

3. Controller Design

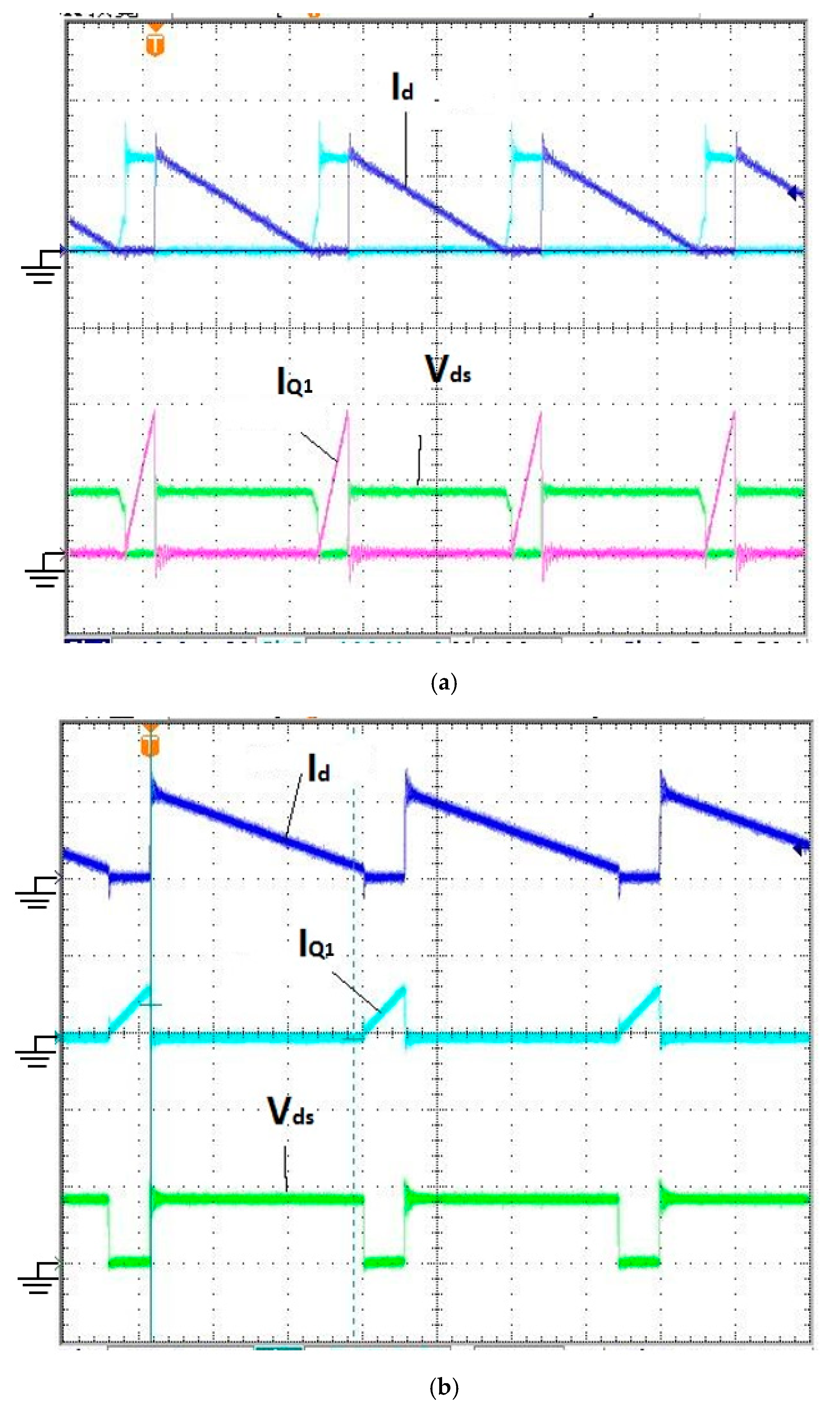

4. Circuit Simulations and Experimental Verifications

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Liu, K.H.; Qruganti, R.; Lee, F.C. Quasi-resonant converters—Topologies and characteristics. IEEE Trans. Power Electron. 1987, 2, 62–71. [Google Scholar] [CrossRef]

- Lee, F.C. High-Frequency Quasi-Resonant Converter Topologies. Proc. IEEE 1988, 76, 377–390. [Google Scholar] [CrossRef]

- Vorperian, V. Quasi-Square-wave Converters: Topologies and Analysis. IEEE Trans. Power Electron. 1998, 3, 183–191. [Google Scholar] [CrossRef]

- PWM Current-Mode Controller for Free Running Quasi-Resonant Operation, On Semiconductor NCP1207 Datasheet; Rev. 11; On Semiconductor: Denver, CO, USA, December 2011.

- Lo, Y.-K.; Lin, J.-Y.; Wang, C.-F.; Lin, C.-Y. Analysis and Design of a Dual-Model Flyback Converter. In Proceedings of the 2010 IEEE International Conference on Sustainable Energy Technologies (ICSET), Kandy, Sri Lanka, 6–9 December 2010; pp. 1–5. [Google Scholar]

- Yeh, C.A.; Lai, Y.S. Novel hybrid control technique with constant on/off time control for DC/DC converter to reduce the switching losses. In Proceedings of the 2009 International Conference on IEEE Power Electronics and Drives Systems Conference, Taipei, Taiwan, 2–5 November 2009; pp. 848–853. [Google Scholar]

- Watson, R.; Hua, G.C.; Lee, F.C. Characterization of an active clamp flyback topology for power factor correction applications. IEEE Trans. Power Electron. 1996, 11, 191–198. [Google Scholar] [CrossRef]

- Papanikolaou, N.P.; Tatakis, E.C. Active voltage clamp in flyback converters operating in CCM mode under wide load variation. IEEE Trans. Ind. Electron. 2004, 51, 632–640. [Google Scholar] [CrossRef]

- Ridley, R.B. A new continuous-time mode for current-mode control with a constant frequency, constant on-time, and constant off-time, in CCM and DCM. In Proceedings of the 21st Annual IEEE Conference on Power Electronics Specialists, San Antonio, TX, USA, 11–14 June 1990; pp. 382–389. [Google Scholar]

- Watson, R.; Lee, F.C.; Hua, G.C. Utilization of an active-clamp circuit to achieve soft switching in flyback converters. IEEE Trans. Power Electron. 1996, 11, 162–169. [Google Scholar] [CrossRef]

- Arouodi, A.E.; Mandal, K.; Giaouris, D.; Banerjee, S. Self-compensation of DC-DC converters under peak current mode control. Electron. Lett. 2017, 53, 345–347. [Google Scholar] [CrossRef]

- Kim, E.; Chung, B.; Jang, S.; Choi, M.; Key, M. A study of novel Flyback converter with very low power consumption at the standby operating mode. In Proceedings of the 2010 Twenty-Fifth Annual IEEE, Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1833–1837. [Google Scholar]

- Alou, P.; Garcia, O.; Cobos, J.A.; Uceda, J.; Rason, M. Flyback with active clamp: A suitable topology for low power and very wide input voltage range applications. In Proceedings of the APEC Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No. 02CH37335), Dallas, TX, USA, 10–14 March 2002; Volume 1, pp. 242–248. [Google Scholar]

- Chen, B.Y.; Lai, Y.S. Novel dual mode operation of phase-shifted full bridge converter to improve efficiency under light load condition. In Proceedings of the IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 1367–1374. [Google Scholar]

- Jang, Y.; Jovanovic, M.M. Light-load efficiency optimization method. IEEE Trans. Power Electron. 2010, 25, 67–74. [Google Scholar] [CrossRef]

- Ayachit, A.; Reatti, A.; Kazimierczuk, M.K. Magnetising Inductance of Multiple-Output Flyback DC-DC Converter for Discontinuous-Conduction Mode. IET Power Electron. 2016, 10, 451–461. [Google Scholar] [CrossRef]

- Saliva, A. Design Guide for Off-Line Fixed Frequency DCM Flyback Converter, Infineon Technologies North America, Design Note DN 2013-01. Available online: https://www.infineon.com (accessed on 15 August 2017).

- Panov, Y.; Jovaovic, M. Small-Signal Analysis and Control Design of Isolated Power Supplies with Optocoupler Feedback. IEEE Trans. Power Electron. 2005, 20, 823–832. [Google Scholar] [CrossRef]

- Karvelis, G.A.; Manias, S.N. Analysis and Design of Flyback Zero-Current Switched (ZCS) Quasi-Resonant AC/DC Converter. Proc. IEEE Electr. Power Appl. 1997, 144, 401–408. [Google Scholar] [CrossRef]

- ST Microelectronics. Solution for Designing a 400W Fixed Off-Time Controlled PFC Pre-Regulator with the L6562A. Application Note AN2782. Available online: https://www.st.com (accessed on 15 August 2017).

- Kit Sum, K. Switch Mode Power Conversion; Marcel Dekker: New York, NY, USA, 1984. [Google Scholar]

- Ghaffarzadeh, H.; Stone, C.; Mehrizi-Sani, A. Predictive Set Point Modulation to Mitigate Transients in Lightly Damped Balanced and Unbalanced Systems. IEEE Trans. Power Electron. 2017, 32, 1041–1049. [Google Scholar]

- Adragna, C.; Gattavari, G. Fly-Back Converters with the L6561 PFC Controller; STMicroelectronics: Geneva, Switzerland, 2003. [Google Scholar]

- Erickson, R.W.; Maksimović, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic Publishers: Norwell, MA, USA, 2001. [Google Scholar]

| Symbol | Value | Symbol | Value |

|---|---|---|---|

| Vin | 127~380 Vdc | Lm | 170 |

| Vo | 19V dc | Co | 2000 |

| Po(max) | 100 W | Dmax | 0.4 |

| Io(max) | 5.26 A | fsw(min) | 40 kHz |

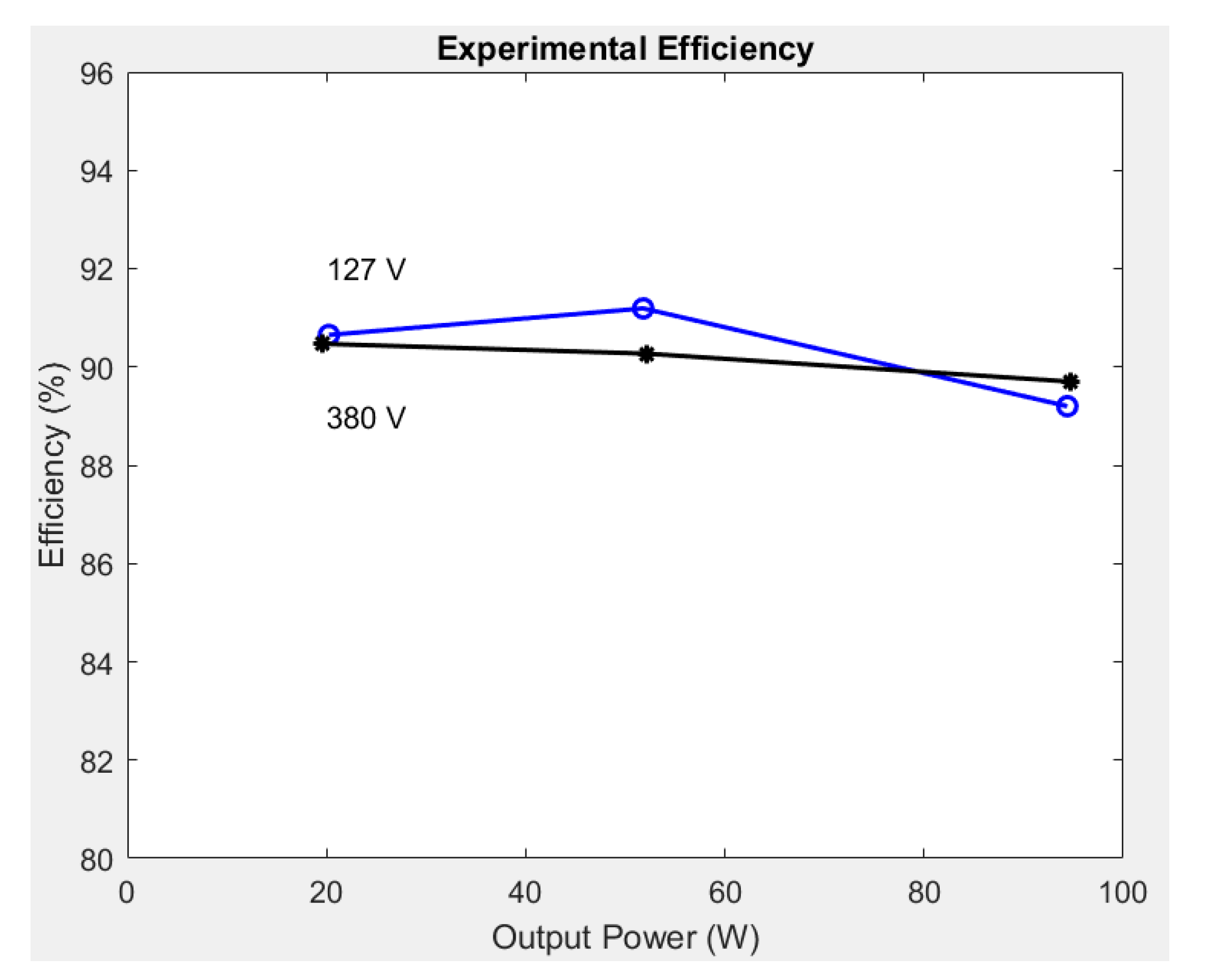

| Control Mode | Vin (V) | Iin (A) | Pin (W) | Vo (V) | Io (A) | Po (W) | η (%) |

|---|---|---|---|---|---|---|---|

| QR Control | 127 | 0.842 | 106.68 | 18.73 | 5 | 93.65 | 87.70 |

| QR Control | 380 | 0.281 | 106.95 | 18.81 | 5 | 94.05 | 87.90 |

| DM Control | 127 | 0.833 | 105.41 | 18.85 | 5 | 94.25 | 89.20 |

| DM Control | 380 | 0.277 | 105.26 | 18.90 | 5 | 94.50 | 89.70 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chuang, C.-C.; Hua, C.-C.; Huang, C.-Y.; Jhou, L.-K. Modeling a Dual-Mode Controller Design for a Quasi-Resonant Flyback Converter. Appl. Sci. 2019, 9, 1860. https://doi.org/10.3390/app9091860

Chuang C-C, Hua C-C, Huang C-Y, Jhou L-K. Modeling a Dual-Mode Controller Design for a Quasi-Resonant Flyback Converter. Applied Sciences. 2019; 9(9):1860. https://doi.org/10.3390/app9091860

Chicago/Turabian StyleChuang, Ching-Chun, Chih-Chiang Hua, Chong-Yu Huang, and Li-Kai Jhou. 2019. "Modeling a Dual-Mode Controller Design for a Quasi-Resonant Flyback Converter" Applied Sciences 9, no. 9: 1860. https://doi.org/10.3390/app9091860

APA StyleChuang, C.-C., Hua, C.-C., Huang, C.-Y., & Jhou, L.-K. (2019). Modeling a Dual-Mode Controller Design for a Quasi-Resonant Flyback Converter. Applied Sciences, 9(9), 1860. https://doi.org/10.3390/app9091860