Classic Discrete Control Technique and 3D-SVPWM Applied to a Dual Unified Power Quality Conditioner

Abstract

:1. Introduction

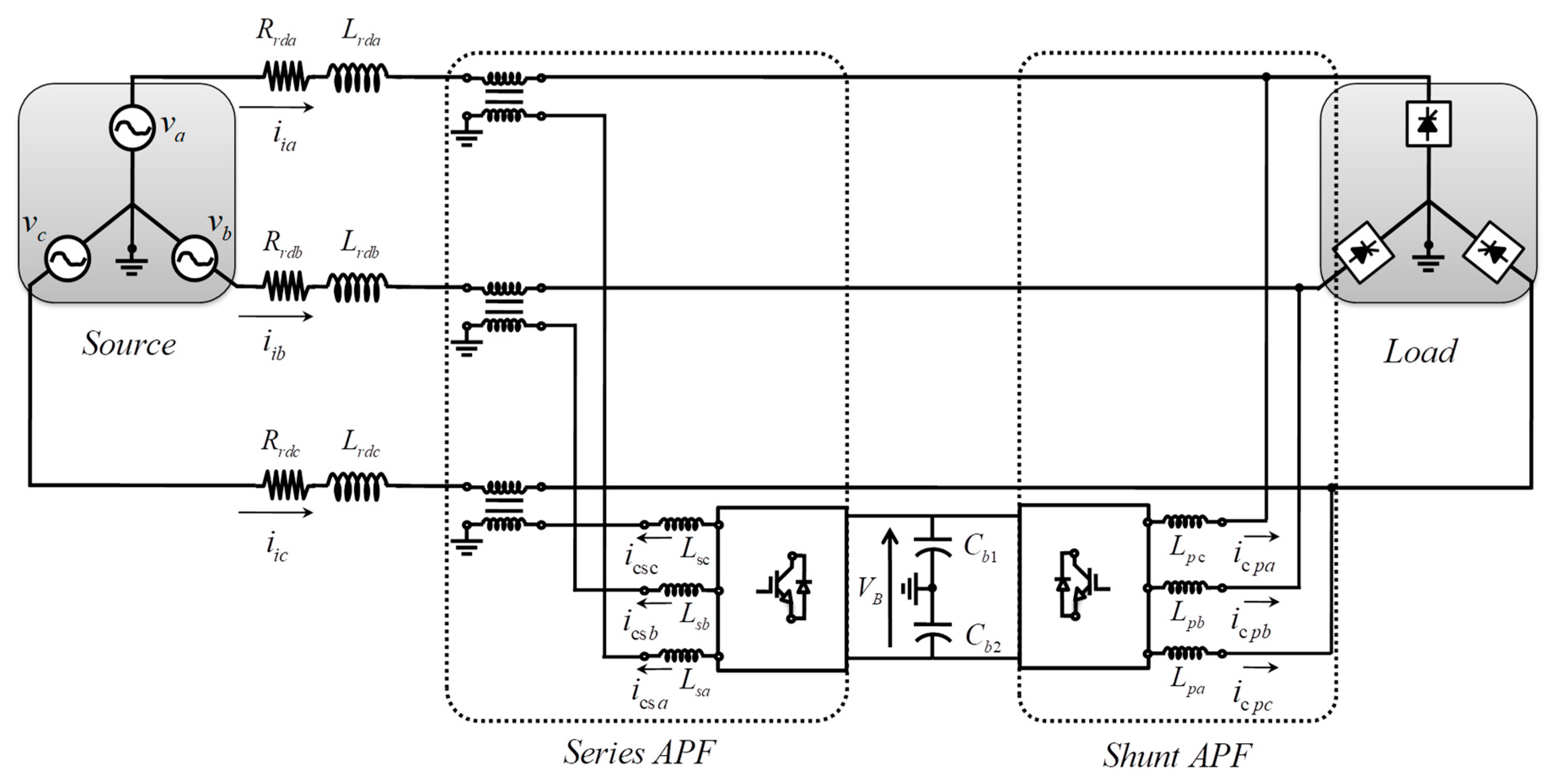

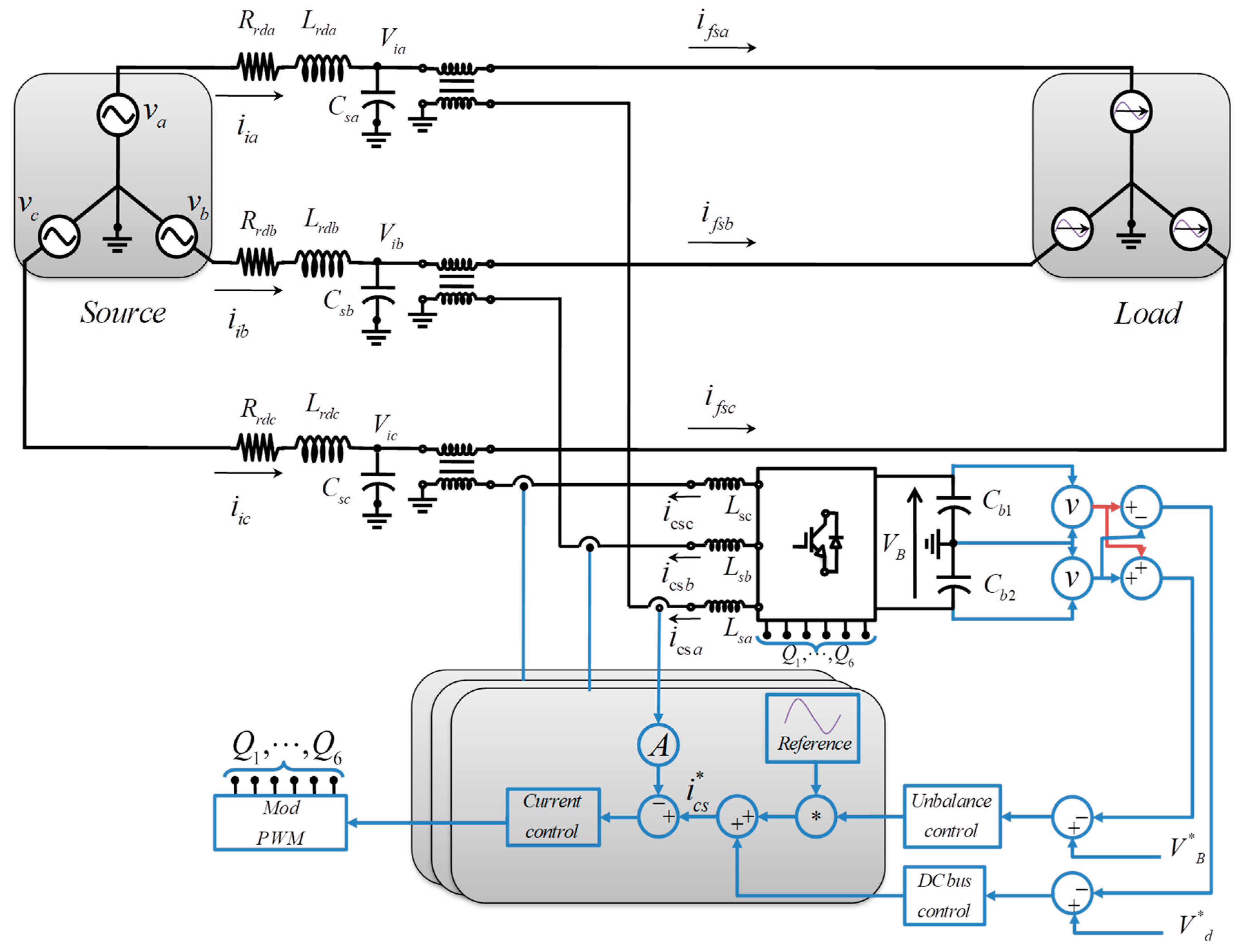

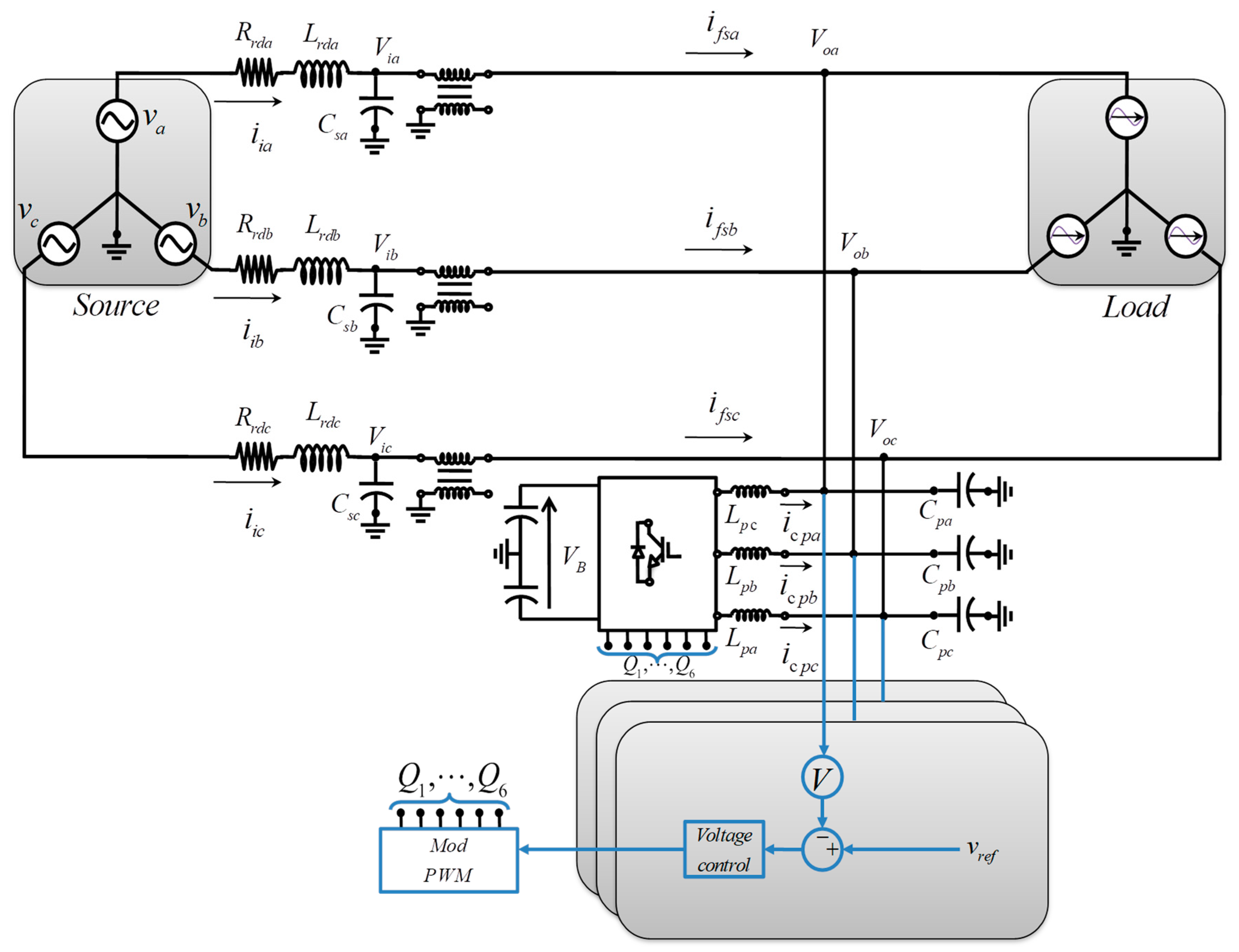

2. UPQC in Dual Topology

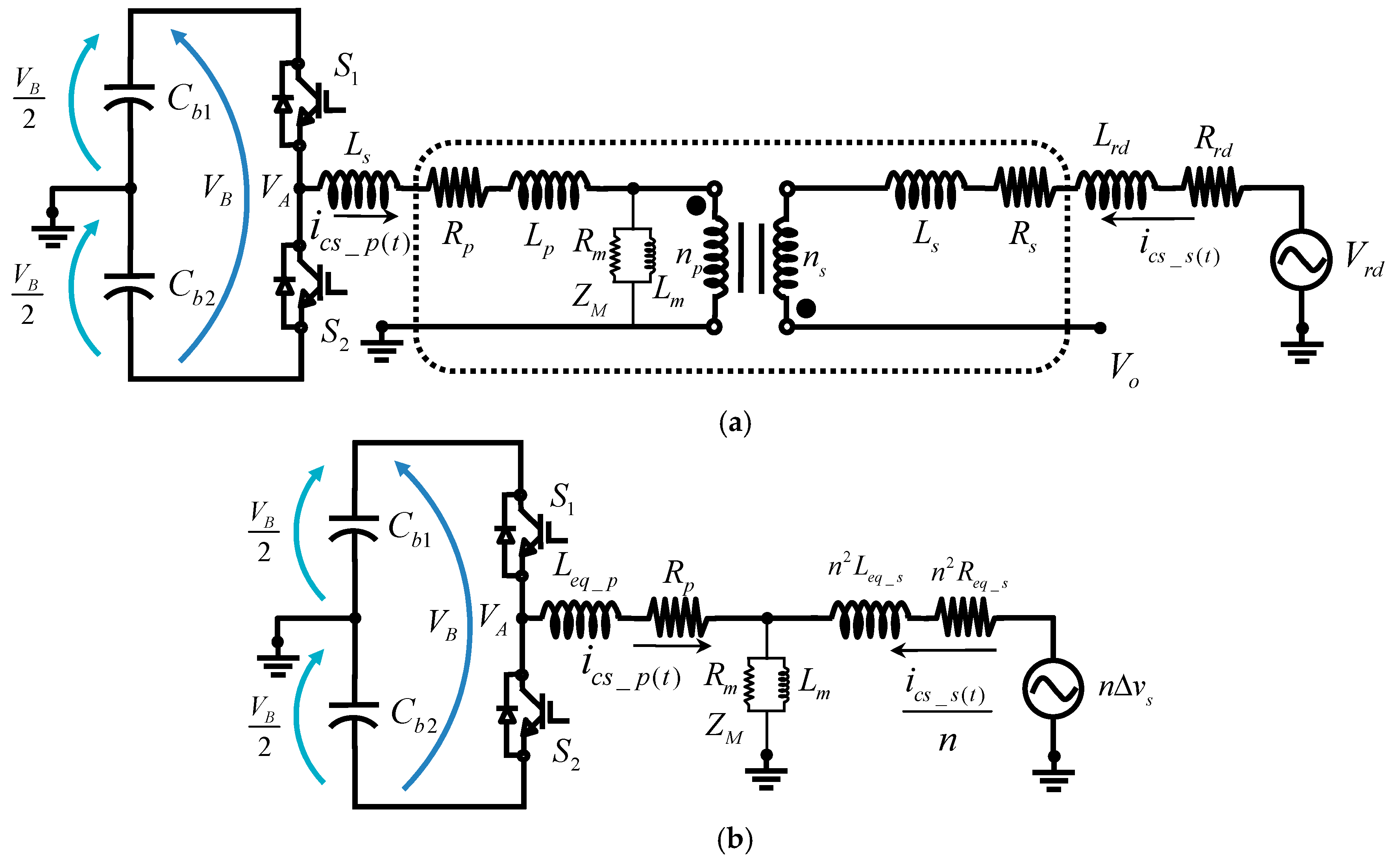

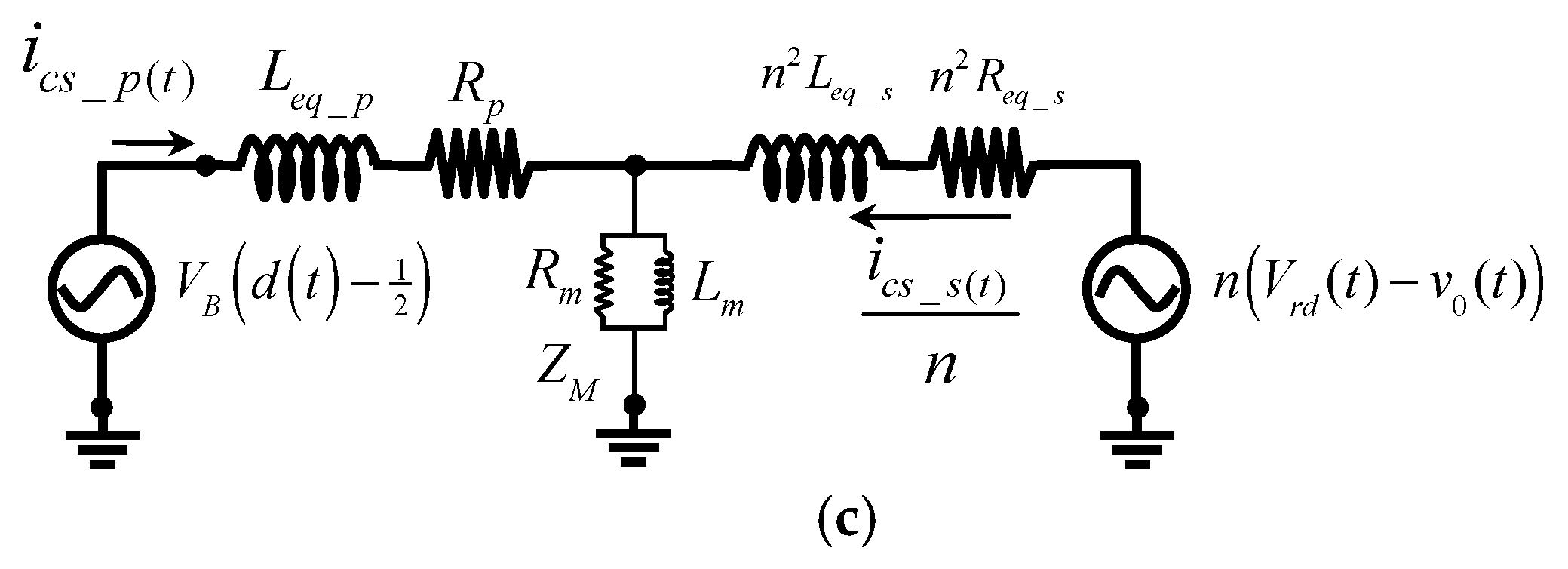

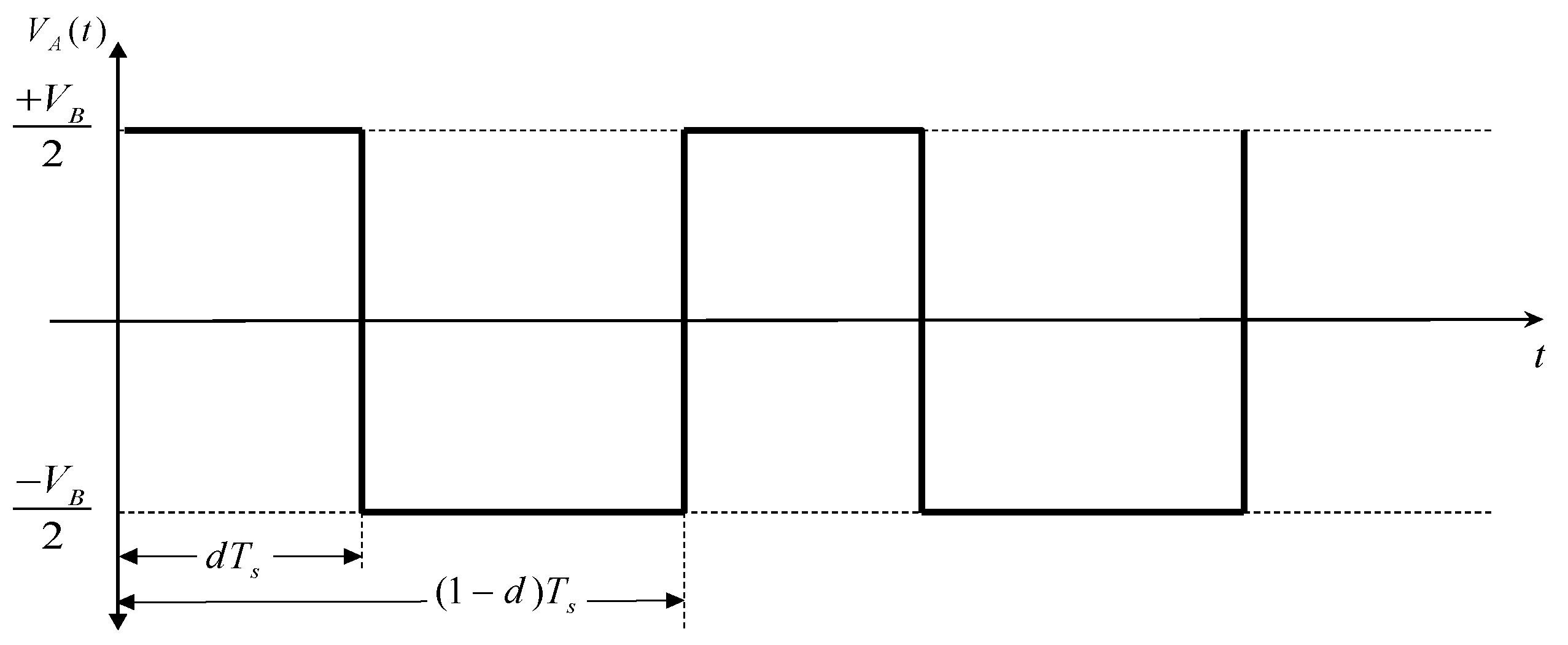

2.1. Series Active Power Filter (Series APF)

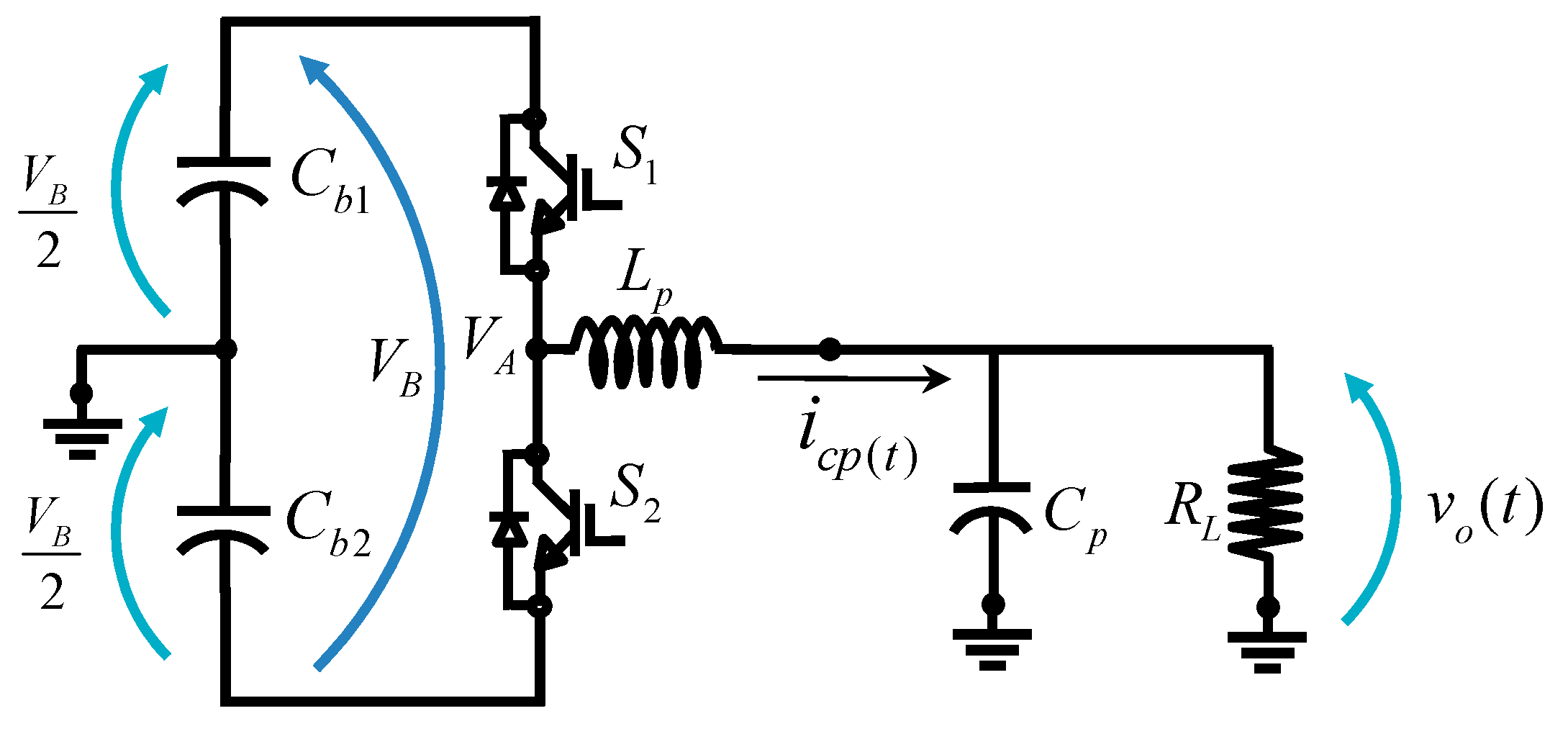

2.2. Shunt Active Power Filter (Shunt APF)

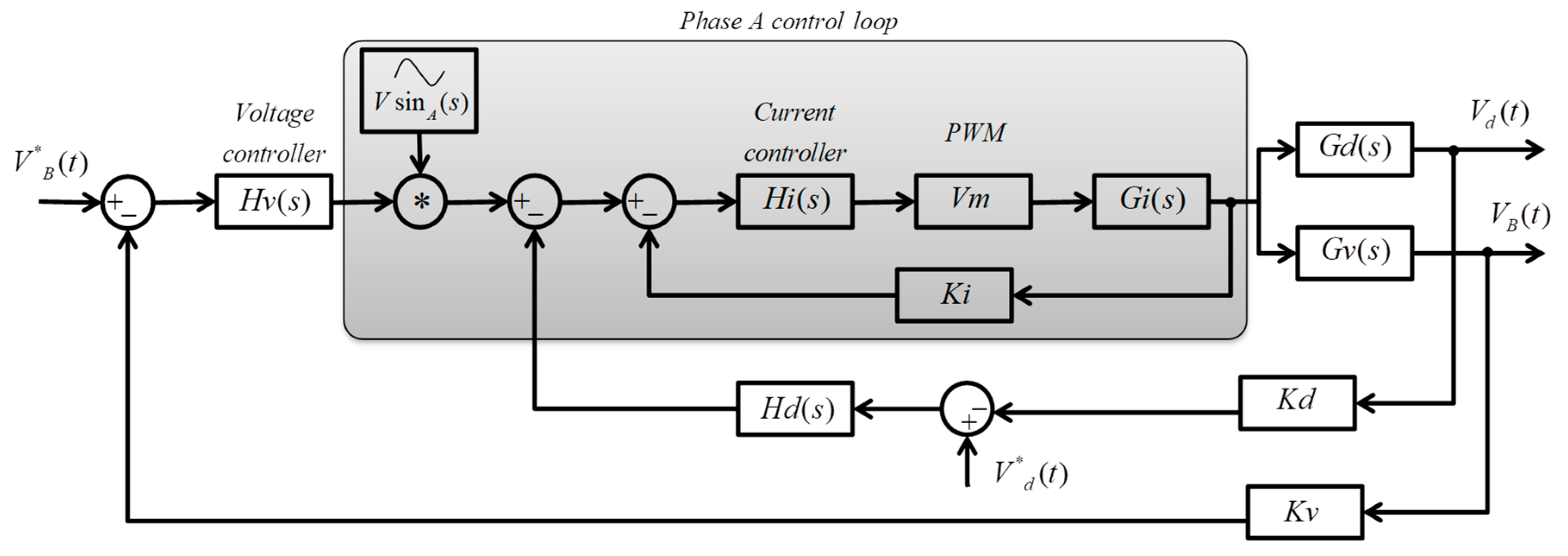

3. Design of Controllers

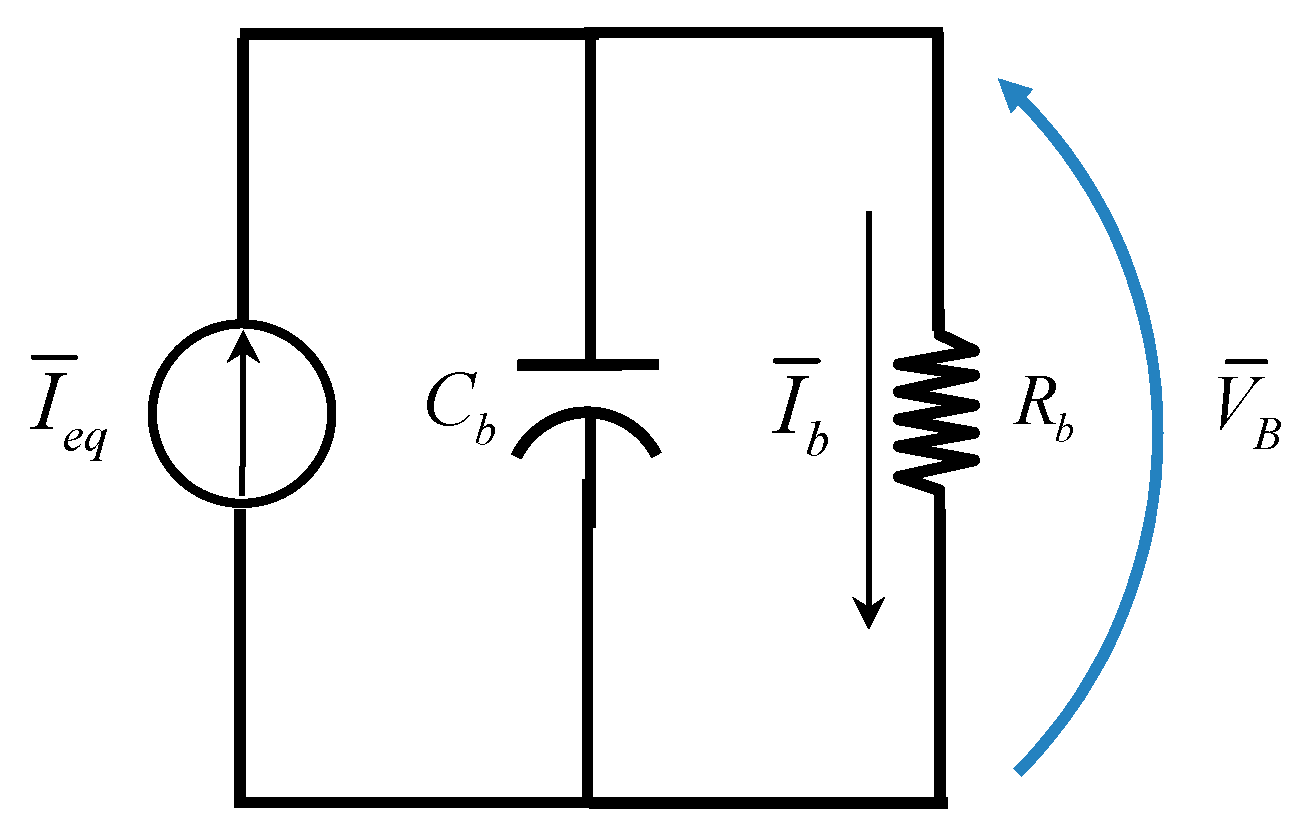

3.1. Current, DC bus, and DC bus Unbalance Controllers

3.2. Voltage Controller

3.3. Three Dimensional Space Vector Pulse Width Modulation (3D-SVPWM)

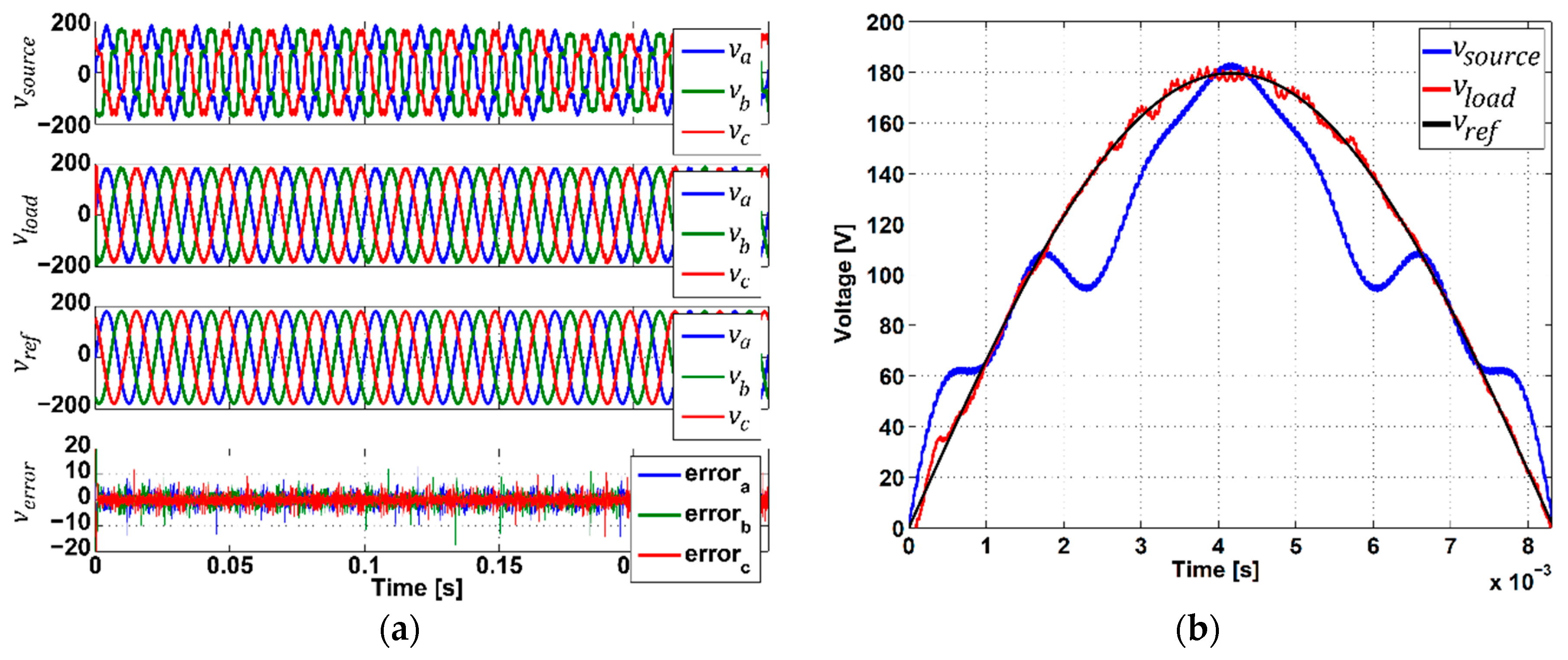

4. Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Gyugyi, L. Unified power-flow control concept for flexible AC transmission systems. IEE Proc. C Gener. Transm. Distrib. 1992, 139, 323–331. [Google Scholar] [CrossRef]

- Hingoranl, N.G.; Gyugyi, L.; El-Hawary, M.E. Understanding FACTS: Concepts and Technology of Flexible AC Transmission Systems; Wiley-IEEE Press: Hoboken, NJ, USA, 1999; ISBN 9780470546802. [Google Scholar]

- Ghosh, A.; Ledwich, G. Power Quality Enhancement Using Custom Power Devices; Springer: New York, NY, USA, 2002; ISBN 9781461354185. [Google Scholar]

- Hingorani, N.G. Introducing custom power. IEEE Spectr. 1995, 32, 41–48. [Google Scholar] [CrossRef]

- Khadkikar, V. Enhancing Electric Power Quality Using UPQC: A Comprehensive Overview. IEEE Trans. Power Electron. 2012, 27, 2284–2297. [Google Scholar] [CrossRef]

- Mokhtarpour, A.; Shayanfar, H.; Bathaee, S.M.T. Reference Generation of Custom Power Devices (CPs). In An Update on Power Quality; IntechOpen: London, UK, 2013. [Google Scholar]

- Taher, S.A.; Afsari, S.A. Optimal location and sizing of UPQC in distribution networks using differential evolution algorithm. Math. Probl. Eng. 2012, 2012. [Google Scholar] [CrossRef]

- Dharmalingam, R.; Dash, S.S.; Senthilnathan, K.; Mayilvaganan, A.B.; Chinnamuthu, S. Power quality improvement by unified power quality conditioner based on CSC topology using synchronous reference frame theory. Sci. World J. 2014, 2014, 391975. [Google Scholar] [CrossRef] [PubMed]

- Mishra, P.; Kumar Pradhan, A.; Bajpai, P. Voltage control of PV inverter connected to unbalanced distribution system. Renew. Power Gener. IET 2019, 13, 1587–1594. [Google Scholar] [CrossRef]

- Hossain, E.; Rida Tür, M.; Padmanaban, S.; Ay, S.; Khan, I. Analysis and Mitigation of Power Quality Issues in Distributed Generation Systems Using Custom Power Devices. IEEE Access 2018, 6, 16816–16833. [Google Scholar] [CrossRef]

- Lakshmi, S.; Ganguly, S. An On-line Operational Optimization Approach for Open Unified Power Quality Conditioner for Energy Loss Minimization of Distribution Networks. IEEE Trans. Power Syst. 2019, 34, 4784–4795. [Google Scholar] [CrossRef]

- Cheung, V.S.P.; Yeung, R.S.C.; Chung, H.S.H.; Lo, A.W.L.; Wu, W.M. A Transformer-Less Unified Power Quality Conditioner with Fast Dynamic Control. IEEE Trans. Power Electron. 2018, 33, 3926–3937. [Google Scholar] [CrossRef]

- Kassai, M.; Poleczky, L.; Al-Hyari, L.; Kajtar, L.; Nyers, J. Investigation of the Energy Recovery Potentials in Ventilation Systems in Different Climates. Facta Univ. Ser. Mech. Eng. 2018, 16, 203–217. [Google Scholar] [CrossRef]

- Han, Y.; Xu, L. A survey of the Smart Grid Technologies: background, motivation and practical applications. Prezglad Elektrotechniczky 2011, 87, 47–57. [Google Scholar]

- Kassai, M.; Ge, G.; Simonson, C.J. Dehumidification performance investigation of run-around membrane energy exchanger system. Therm. Sci. 2016, 20, 1927–1938. [Google Scholar] [CrossRef]

- Garcés Gomez, Y.A.; Toro García, N.; Hoyos, F.E. New Application’s Approach to Unified Power Quality Conditioners for Mitigation of Surge Voltages. J. Electr. Comput. Eng. 2016, 2016. [Google Scholar] [CrossRef]

- Monteiro, L.; Exposto, B.; Pinto, G.; Monteiro, V.; Aredes, M.; João, L. Afonso Experimental Evaluation of a Control System Based on a Dual-DSP Architecture for a Unified Power Quality Conditioner. Energies 2019, 12, 1964. [Google Scholar] [CrossRef]

- Vigneysh, T.; Kumarappan, N. Grid Interconnection of Renewable Energy Sources Using Unified Power Quality Conditioner: A Fuzzy Logic-Based Approach. J. Circuits, Syst. Comput. 2019, 28, 1959135. [Google Scholar] [CrossRef]

- Aredes, M.; Fernandes, R.M. A unified power quality conditioner with voltage SAG/SWELL compensation capability. In Proceedings of the IEEE 2009 Brazilian Power Electronics Conference, Bonito-Mato Grosso do Sul, Brazil, 27 September–1 October 2009; pp. 218–224. [Google Scholar]

- França, B.W.; Aredes, M. Comparisons between the UPQC and its dual topology (iUPQC) in dynamic response and steady-state. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, Australia, 7–10 November 2011; IEEE: Piscataway, NJ, USA, 2012; pp. 1232–1237. [Google Scholar]

- Millnitz dos Santos, R.J.; Mezaroba, M.; da Cunha, J.C. A Dual Unified Power Quality Conditioner Using a Simplified Control Technique. In Proceedings of the IEEE XI Brazilian Power Electronics Conference, Praiamar, Brazil, 11–15 September 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 486–493. [Google Scholar]

- Wang, J.; Wu, H.; Sun, K.; Zhang, L. A High Efficiency Quasi-Single-Stage Unified Power Quality Conditioner Integrating Distributed Generation. In Proceedings of the 2019 IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi’an, China, 3–6 June 2019; IEEE: Piscataway, NJ, USA, 2019. [Google Scholar]

- Oliveira da Silva, S.A.; Garcia Campanhol, L.B.; de Souza, V. Dynamic Performance Evaluation of a dual UPQC Operating Under Power Quality Disturbances. In Proceedings of the PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 5–7 June 2018; IEEE: Piscataway, NJ, USA, 2018. [Google Scholar]

- Modesto, R.A.; Oliveira da Silva, S.A.; de Oliveira Júnior, A.A. Power quality improvement using a dual unified power quality conditioner/uninterruptible power supply in three-phase four-wire systems. IET Power Electron. 2015, 8, 1595–1605. [Google Scholar] [CrossRef]

- Transformerless Series Active Power Filter to Compensate Voltage Disturbances—IEEE Conference Publication. Available online: https://ieeexplore.ieee.org/document/6020368 (accessed on 7 November 2019).

- Banaei, M.R.; Hosseini, S.H. Mitigation of Current Harmonic Using Adaptive Neural Network with Active Power Line Conditioner. In Proceedings of the 2006 CES/IEEE 5th International Power Electronics and Motion Control Conference, Shanghai, China, 14–16 August 2006; IEEE: Piscataway, NJ, USA, 2009; pp. 1–5. [Google Scholar]

- Ming, Z.; Jian-Ru, W.; Zhi-Qiang, W.; Jian, C. Control Method for Power Quality Compensation Based on Levenberg-Marquardt Optimized BP Neural Networks. In Proceedings of the 2006 CES/IEEE 5th International Power Electronics and Motion Control Conference, Shanghai, China, 14–16 August 2006; IEEE: Piscataway, NJ, USA, 2009; pp. 1–4. [Google Scholar]

- Forghani, M.; Afsharnia, S. Online Wavelet Transform-Based Control Strategy for UPQC Control System. IEEE Trans. Power Deliv. 2007, 22, 481–491. [Google Scholar] [CrossRef]

- Karthikeyan, N.; Mishra, M.K.; Kalyan Kumar, B. Complex wavelet based control strategy for UPQC. In Proceedings of the 2010 Joint International Conference on Power Electronics, Drives and Energy Systems & 2010 Power India, New Delhi, India, 20–23 December 2010; IEEE: Piscataway, NJ, USA, 2011; pp. 1–6. [Google Scholar]

- Kesler, M.; Ozdemir, E. A novel control method for unified power quality conditioner (UPQC) under non-ideal mains voltage and unbalanced load conditions. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 Febrary 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 374–379. [Google Scholar]

- Lee, W.C.; Lee, D.M.; Lee, T.K. New Control Scheme for a Unified Power-Quality Compensator-Q With Minimum Active Power Injection. IEEE Trans. Power Deliv. 2010, 25, 1068–1076. [Google Scholar] [CrossRef]

- Hoyos Velasco, F.E.; Toro-García, N.; Garcés Gómez, Y.A. Adaptive Control for Buck Power Converter Using Fixed Point Inducting Control and Zero Average Dynamics Strategies. Int. J. Bifurc. Chaos 2015, 25, 1550049. [Google Scholar] [CrossRef]

- Mohan, N. Power Electronics: A First Course; Wiley: Hoboken, NJ, USA, 2011. [Google Scholar]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics: Converters, Applications and Design, 3rd ed.; John Wiley & Sons: New York, NY, USA, 2002. [Google Scholar]

- Orts, S.; Sales, F.G.; Chilet, S.S.; Alcaniz, M.; Masot, R.; Abellan, A. New active compensator based on ieee std. 1459. IEEE Lat. Am. Trans. 2006, 4, 38–46. [Google Scholar] [CrossRef]

| Name | Parameter | Value |

|---|---|---|

| Inductance of the series APF | 650 μH | |

| Switching frequency | 20 kHz | |

| DC link voltage | 400 V | |

| PWM voltage gain | 0.091 V | |

| Power grid resistance | 0.04 Ω | |

| Power grid inductance | 107 μH | |

| Power grid capacitance | 1 μF | |

| Shunt inductance | 1.2 mH | |

| Shunt and series resistance | 0.44 Ω | |

| Magnetizing resistance of the transformer | 104 Ω | |

| Magnetizing inductance of the transformer | 104 H | |

| Secondary equivalent resistance | 0.48 Ω | |

| DC bus total capacitance | 3 mF | |

| Secondary equivalent inductance | 757 μH | |

| Primary equivalent inductance | 1.85 mH |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Garces-Gomez, Y.A.; Hoyos, F.E.; Candelo-Becerra, J.E. Classic Discrete Control Technique and 3D-SVPWM Applied to a Dual Unified Power Quality Conditioner. Appl. Sci. 2019, 9, 5087. https://doi.org/10.3390/app9235087

Garces-Gomez YA, Hoyos FE, Candelo-Becerra JE. Classic Discrete Control Technique and 3D-SVPWM Applied to a Dual Unified Power Quality Conditioner. Applied Sciences. 2019; 9(23):5087. https://doi.org/10.3390/app9235087

Chicago/Turabian StyleGarces-Gomez, Y. A., Fredy E. Hoyos, and John E. Candelo-Becerra. 2019. "Classic Discrete Control Technique and 3D-SVPWM Applied to a Dual Unified Power Quality Conditioner" Applied Sciences 9, no. 23: 5087. https://doi.org/10.3390/app9235087

APA StyleGarces-Gomez, Y. A., Hoyos, F. E., & Candelo-Becerra, J. E. (2019). Classic Discrete Control Technique and 3D-SVPWM Applied to a Dual Unified Power Quality Conditioner. Applied Sciences, 9(23), 5087. https://doi.org/10.3390/app9235087