4.1. LMSED Algorithm Simulation

4.1.1. Feasibility Verification and Convergence Speed Analysis

In order to verify the proposed scheme’s feasibility, simulation experiments were performed first. The LMSED algorithm was verified using the MATLAB software platform.

In the simulation, the frequency of the input angle is

Hz and the sample frequency is 250 Hz. The simulation model used to generate simulation data is based on Equation (21):

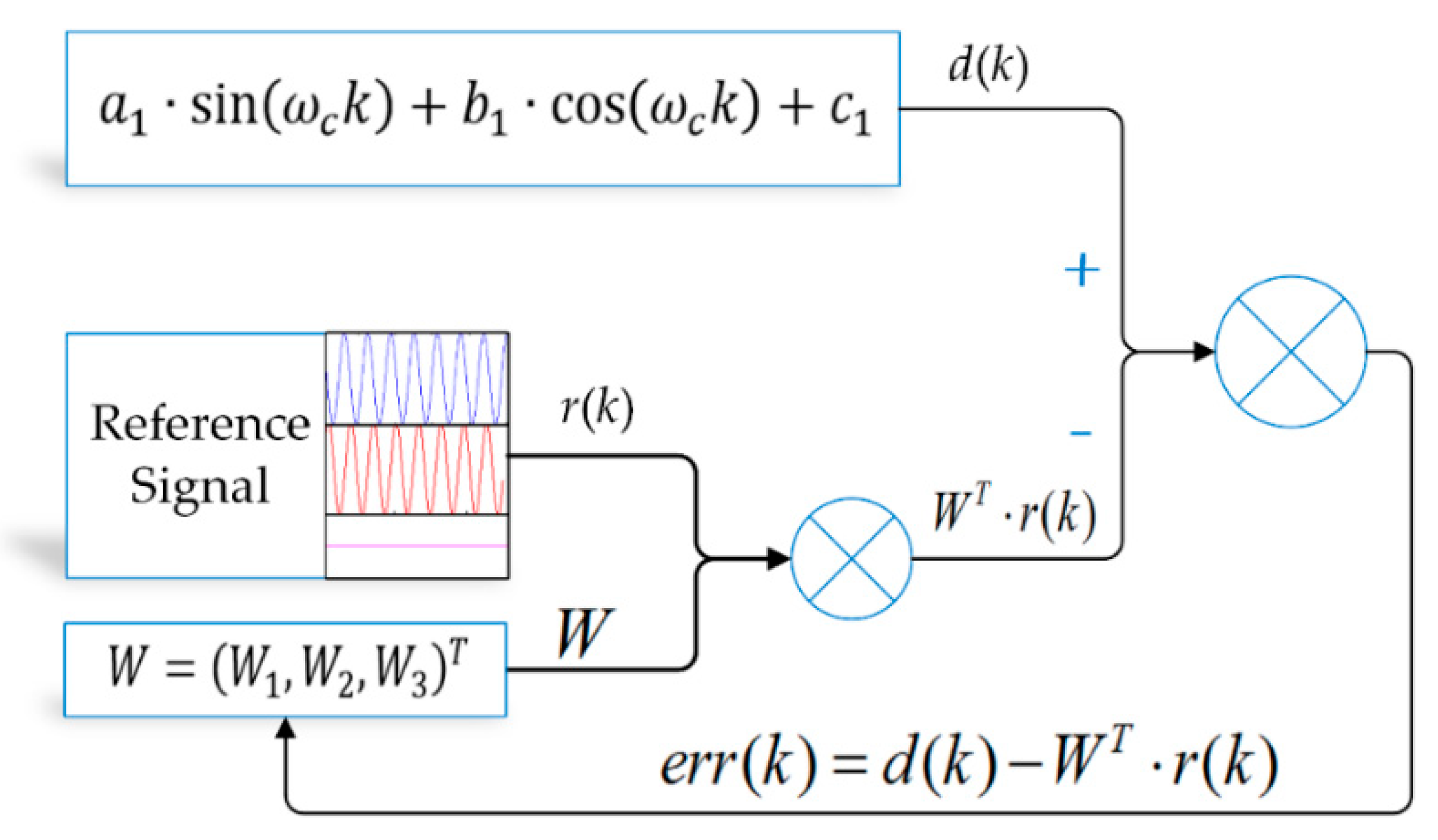

Figure 6 shows the waveform of the simulation signal and the Lissajous figure.

For the LMSED algorithm, the step factor of signal

is set to

and that of signal

is set to

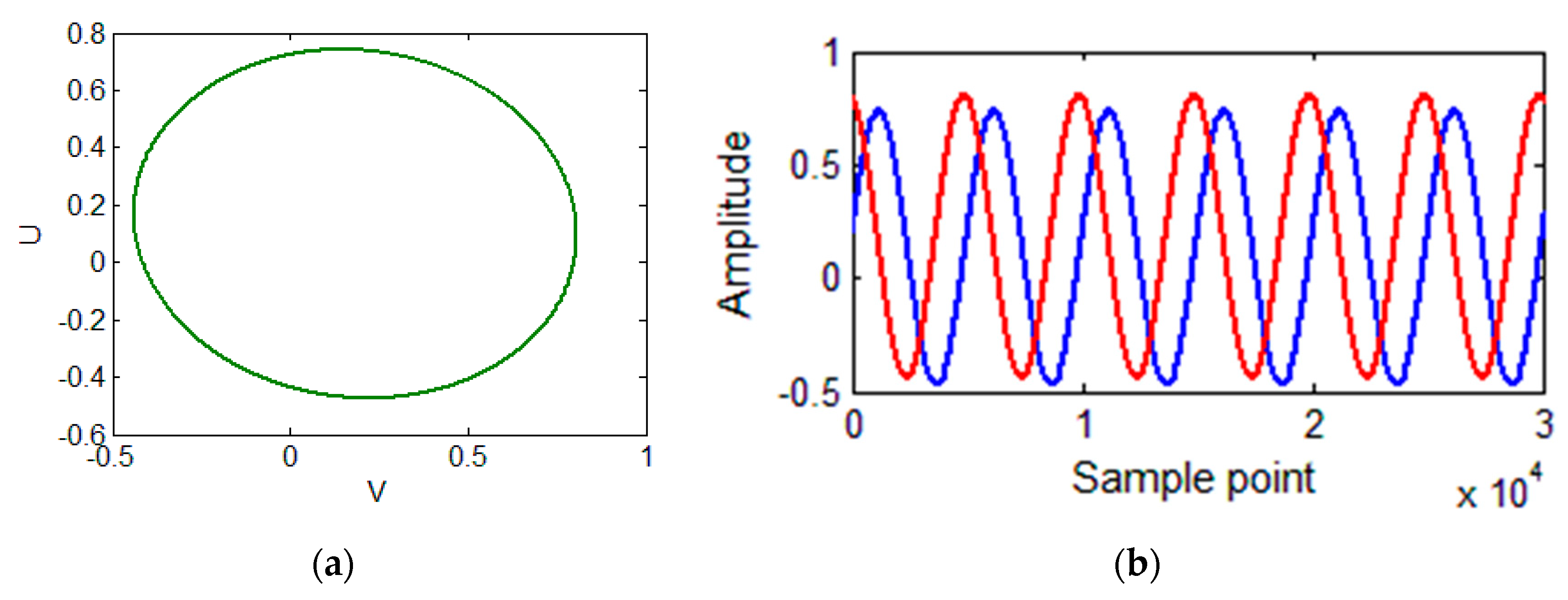

. For the demodulation process, the curve of the parameters, the error curve, and the calibrated signals are shown in

Figure 7.

Parameter demodulation results are summarized in

Table 1.

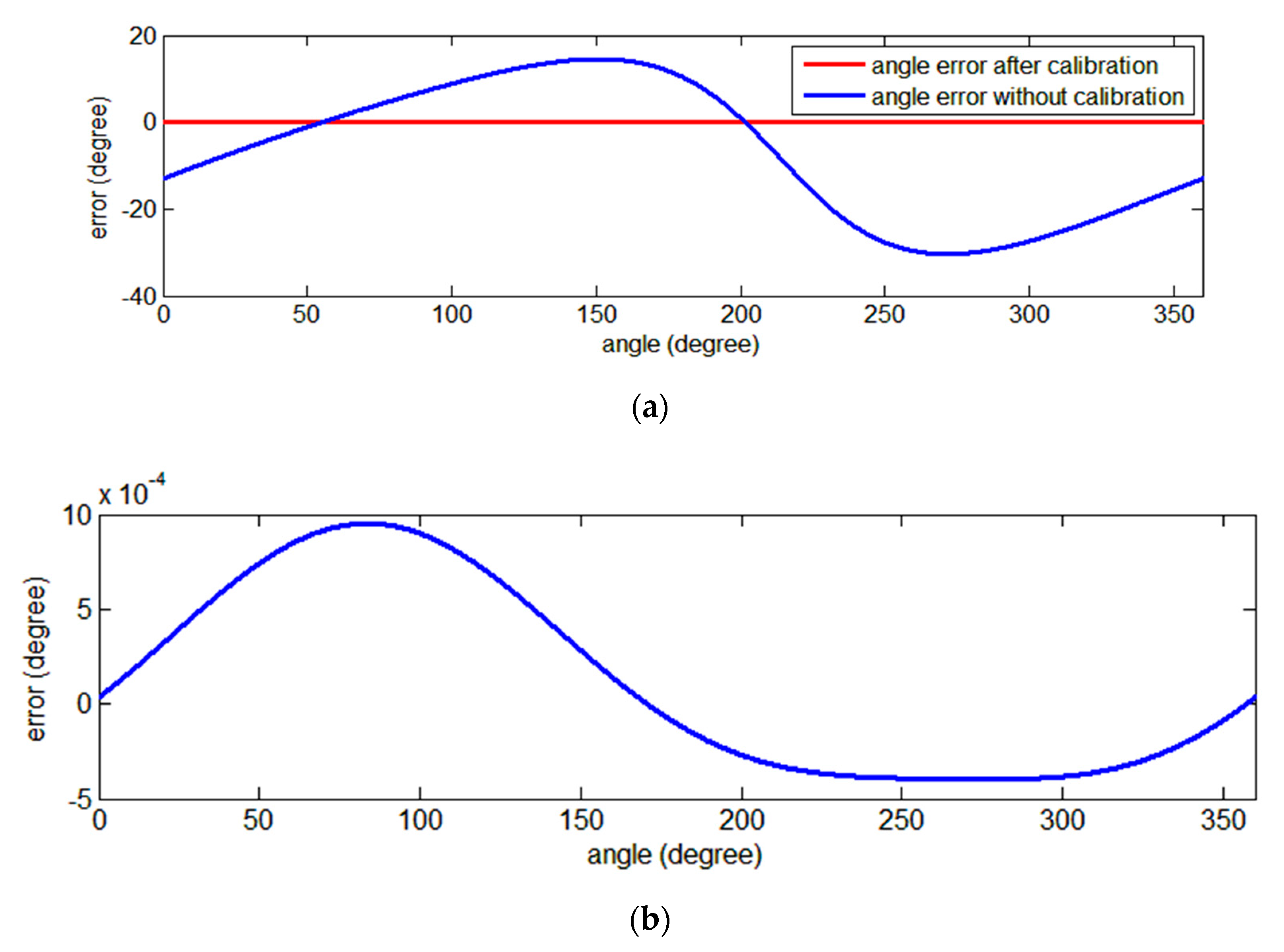

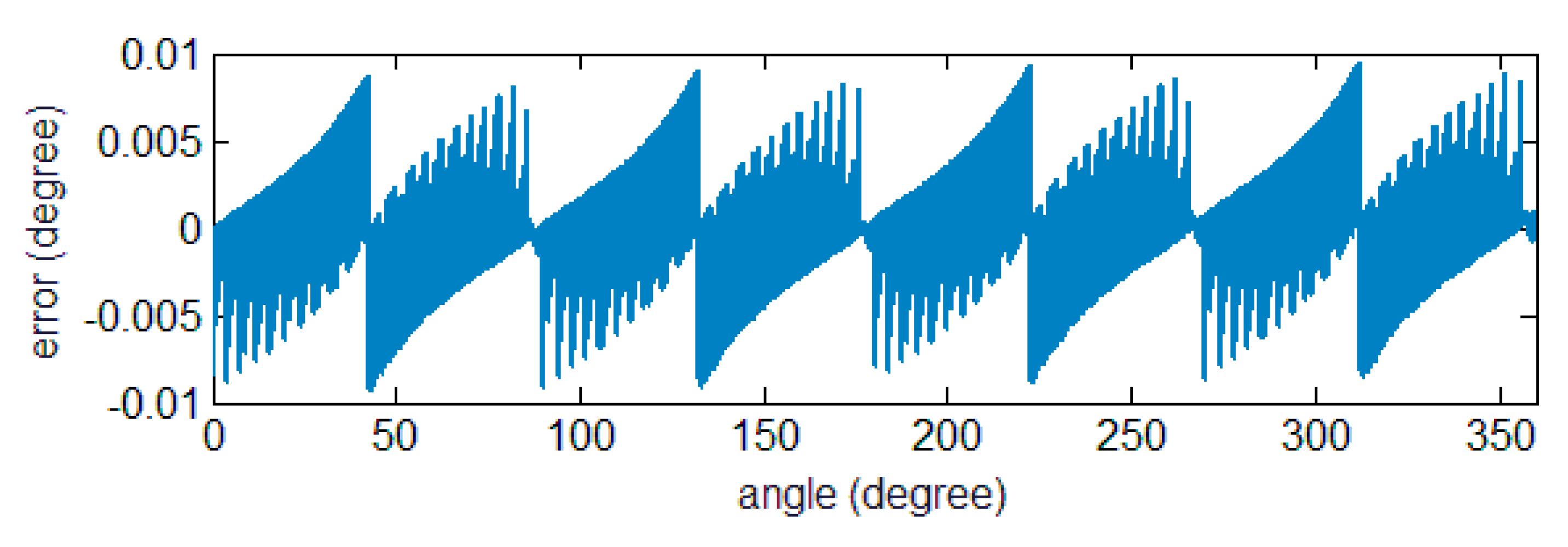

Additionally, the angular calculation errors with and without calibration are shown in

Figure 8.

The maximum value of the angular error without and with parameter calibration is 30.38° and 9.52 °, respectively. The error reduces to % after calibration. The results show that the proposed algorithm can accurately calculate the signal component amplitude and also verify the accuracy of the angle calculation module.

When the parameter demodulation values are stable within

of the preset values, the steady-state of convergence is reached. Thus, the time when all parameters satisfy this requirement for the first time is defined as the convergence time. In the simulation results, the convergence time is approximately 195.70 s. Based on the iterative formula of the parameters, it can be inferred that sampling frequency, angular frequency, and step factor all have an influence on convergence speed and accuracy. This effect cannot be characterized by a simple function. To control a single variable, more simulation experiments are performed and better optimization parameters and faster convergence speed are obtained. Results are summarized in

Table 2. This process is an attempt to continuously change parameters near the initial value. In the experiment, we tried the frequency parameter from 0 to 1000 Hz, and the step factor ranged from

to 1.

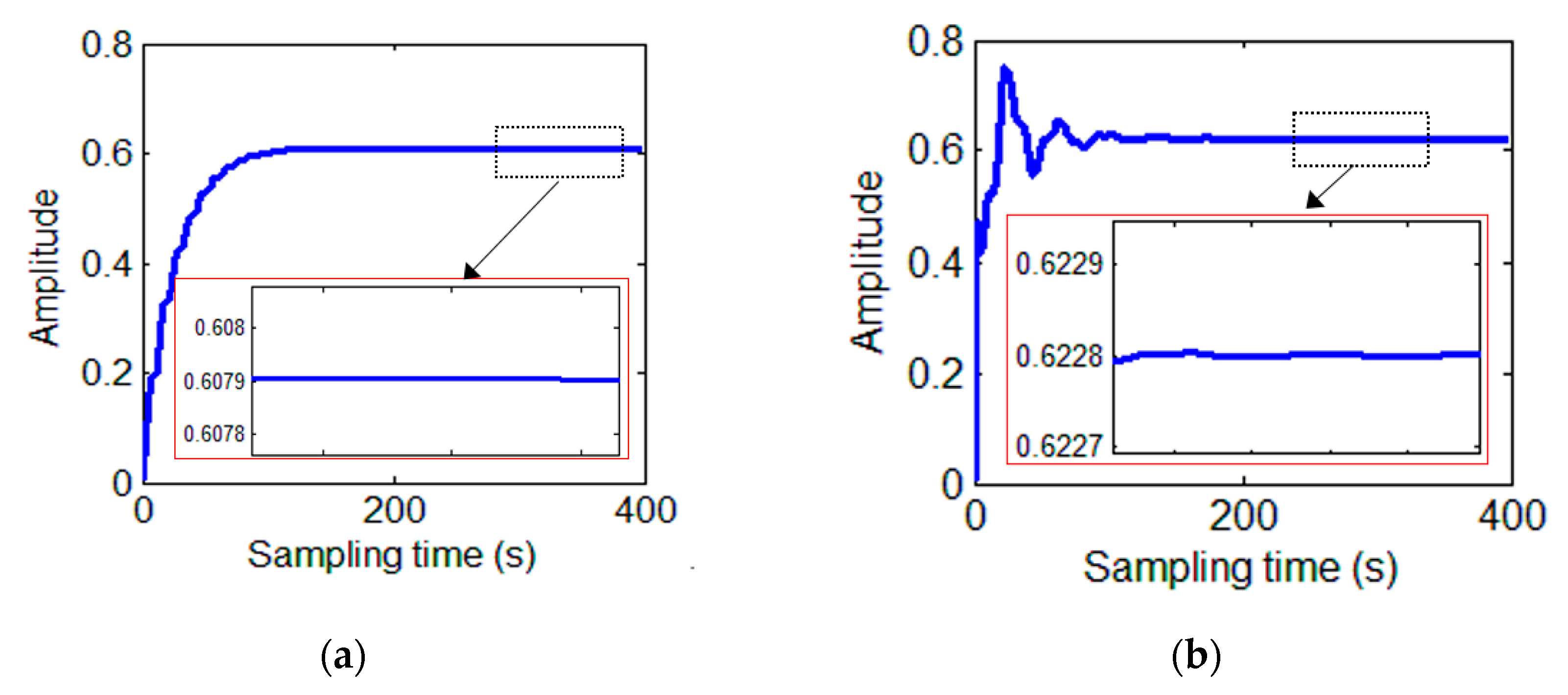

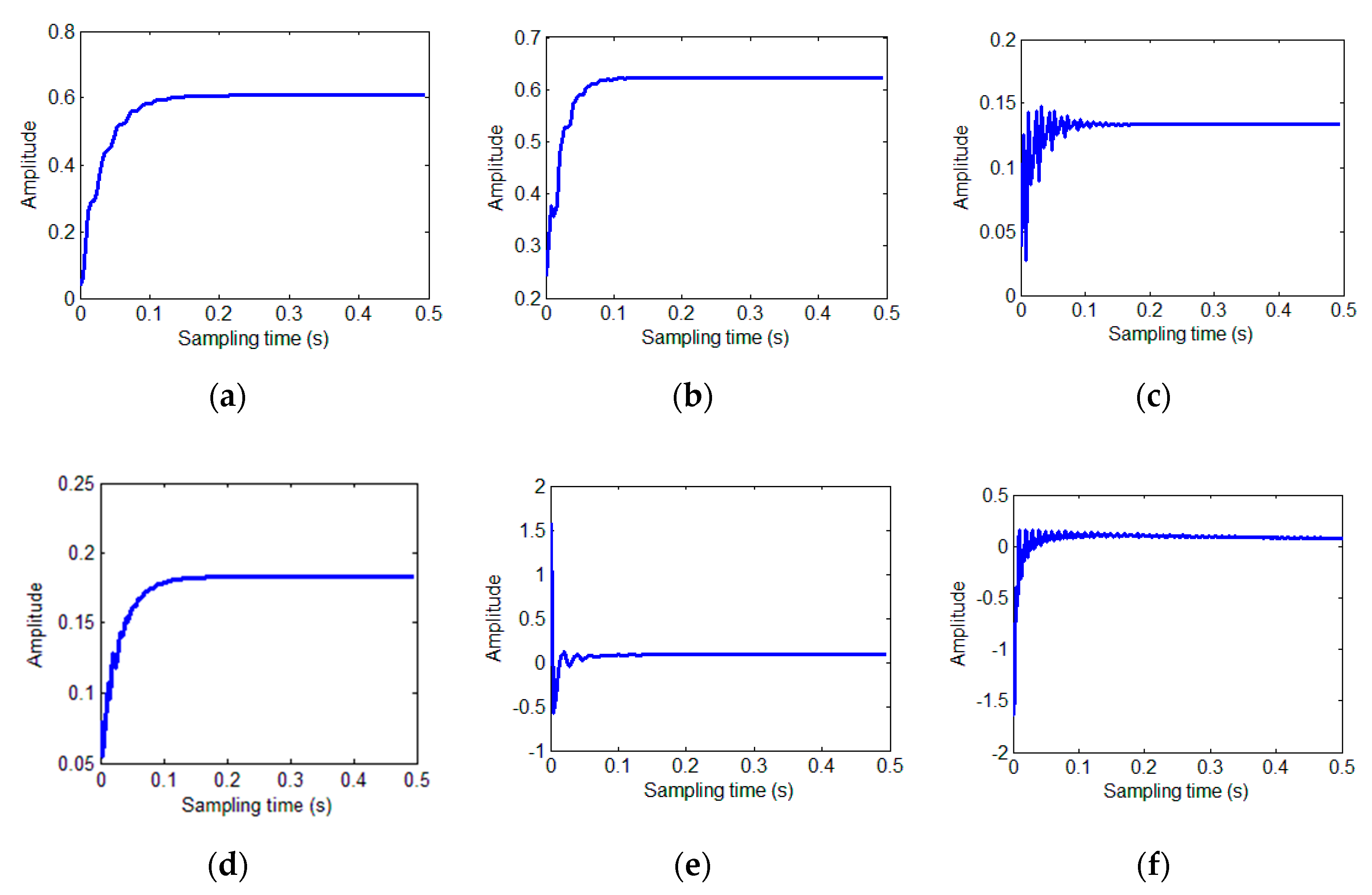

The influence of the step factor is also tested. For a sampling and angular frequency of 250 Hz and 100 Hz, respectively, a faster convergence speed is obtained by changing the step factor. When the step factor is set to

and

, the convergence time is 0.16 s and the parameters converge to the preset values. The convergence process is shown in

Figure 9.

According to the simulation results, the step factor has a greater impact on convergence speed, as properly increasing the step factor speeds up convergence. However, an excessive step factor may cause the parameters to change drastically, causing the entire convergence process to exhibit oscillating changes and prolong convergence time.

Figure 7 and

Figure 9 are the convergence processes of the demodulation parameters after determining the design parameters. They correspond to different design parameters. Better design parameters can be chosen by controlling a single variable. Since the demodulation method is essentially an iterative algorithm, the relationship between the convergence speed and the design parameters does not have an explicit expression, and can only be qualitatively evaluated. Therefore, the SoC is designed to support software-based configuration of parameters.

4.1.2. Analysis of the Effect of Influencing Factors on Demodulation and Calibration Results

In the section above, the ideal signal model is used and the exact parameter values are obtained, and the error after calibration is almost zero. This section describes the effect of the influencing factors on the calibration effect, including noise and the non-constant rotational speed.

For noise analysis, Gaussian noise with a mean of 0 and a variance of 1 is added to the two signals. The maximum value of the absolute value of the noise is defined as the noise peak, and the influence of the noise peak on the parameter solution and the angle calibration is analyzed.

The simulation signal is described in Equation (21). The input angle and sample frequency is 0.05 and 250 Hz. The range of noise peaks is chosen to be

times the amplitude of the simulated signal.

is defined as the noise scale factor. The results when simulation time is 400 s are summarized in

Table 3.

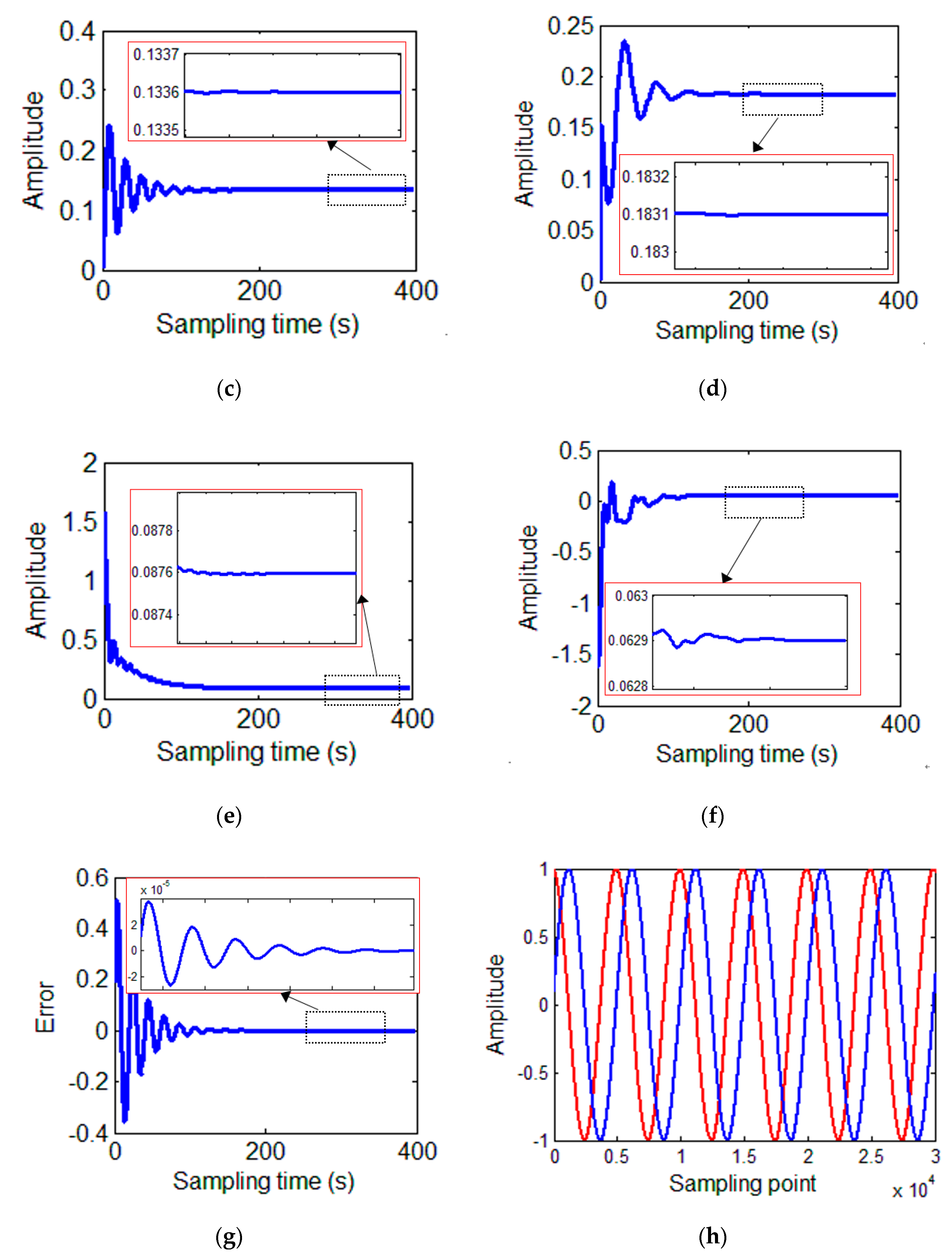

The preset values of

,

,

,

,

,

are 0.6079, 0.6228, 0.1336, 0.1831, 0.0629, 0.0876, respectively. When four decimal places are reserved, the solution result is the same as the set value. For further analysis, the angular position error results with and without calibration are summarized in

Table 4, with different noise peak values.

From the simulation results, the existence of noise has little effect on the parameter demodulation, which is related to the characteristics of the demodulation algorithm looking for the average error. The proposed solution does not eliminate signal noise, so the presence of noise affects the accuracy of the calculation of the angle.

For non-constant rotational speed analysis, speed disturbance with a mean of 0 and a variance of 1 is added to the two signals. The simulation signals have expressions described in Equation (22). The range of noise peaks is chosen to be

times the value of the simulated frequency.

is defined as the scale factor. The simulation results are summarized in

Table 5 and

Table 6.

From the simulation results, the disturbance of speed has a great influence on the parameter demodulation. Taking

as an example, it can be concluded from Equation (23) that the fluctuation of velocity is equivalent to adding an error component to both the amplitude and the DC offset. When the sampling time is large enough, the amplitude component will have a large change, and the excessive change will invalidate the algorithm.

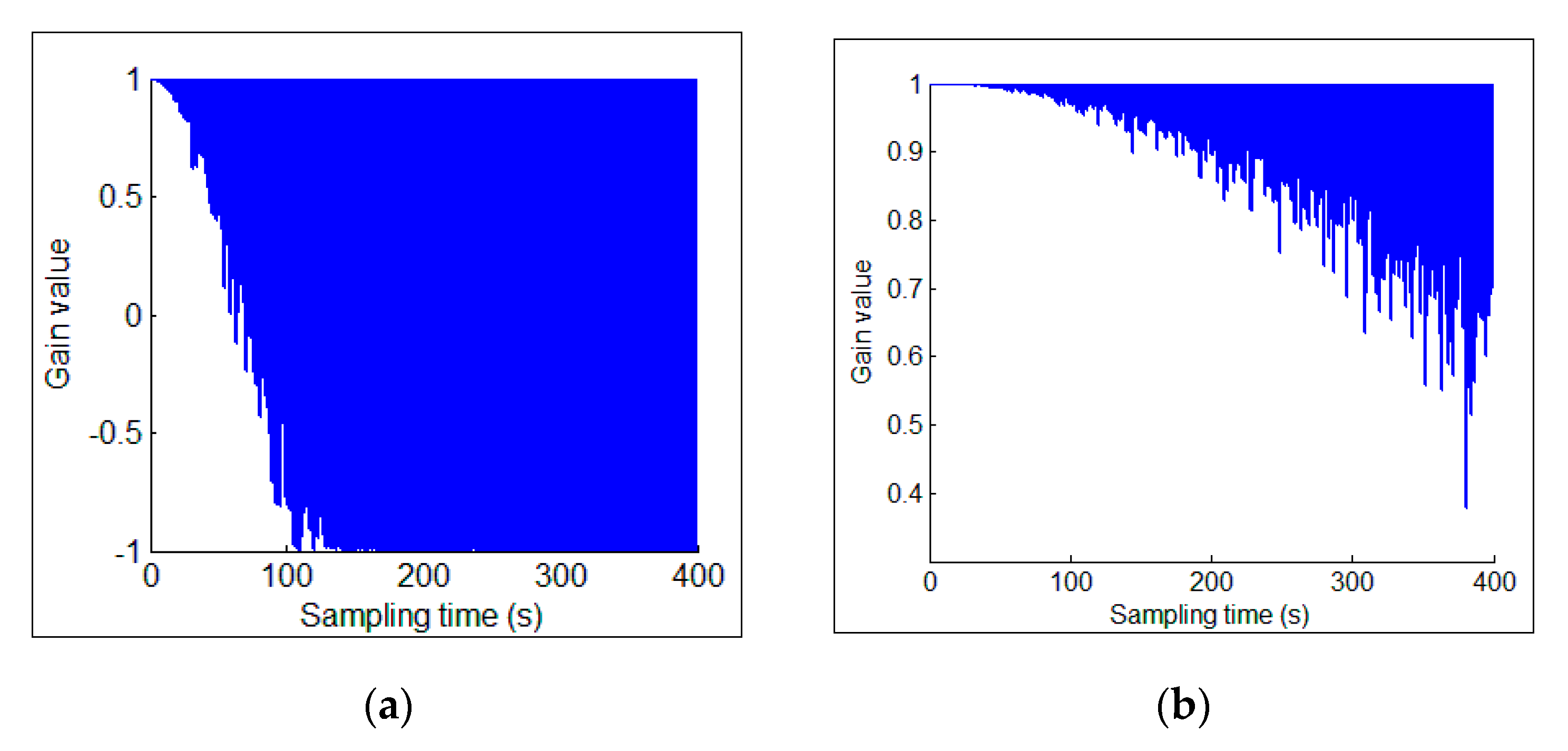

The amplitude gain caused by the speed disturbance is

. When the scale factor

is −1, −2, −3, −4, the gain curve is shown in

Figure 10.

When the speed fluctuation is large (), the demodulation curve will diverge; when the simulation time is long, the influence of the speed fluctuation on the amplitude becomes obvious, and the parameter demodulation curve diverges as well.

According to the analysis results, since the noise does not change the parameter values, the parameter demodulation process is not sensitive to noise; while the speed disturbance adds error components to the parameters, so the accuracy of the parameter demodulation is affected, and even the algorithm fails.

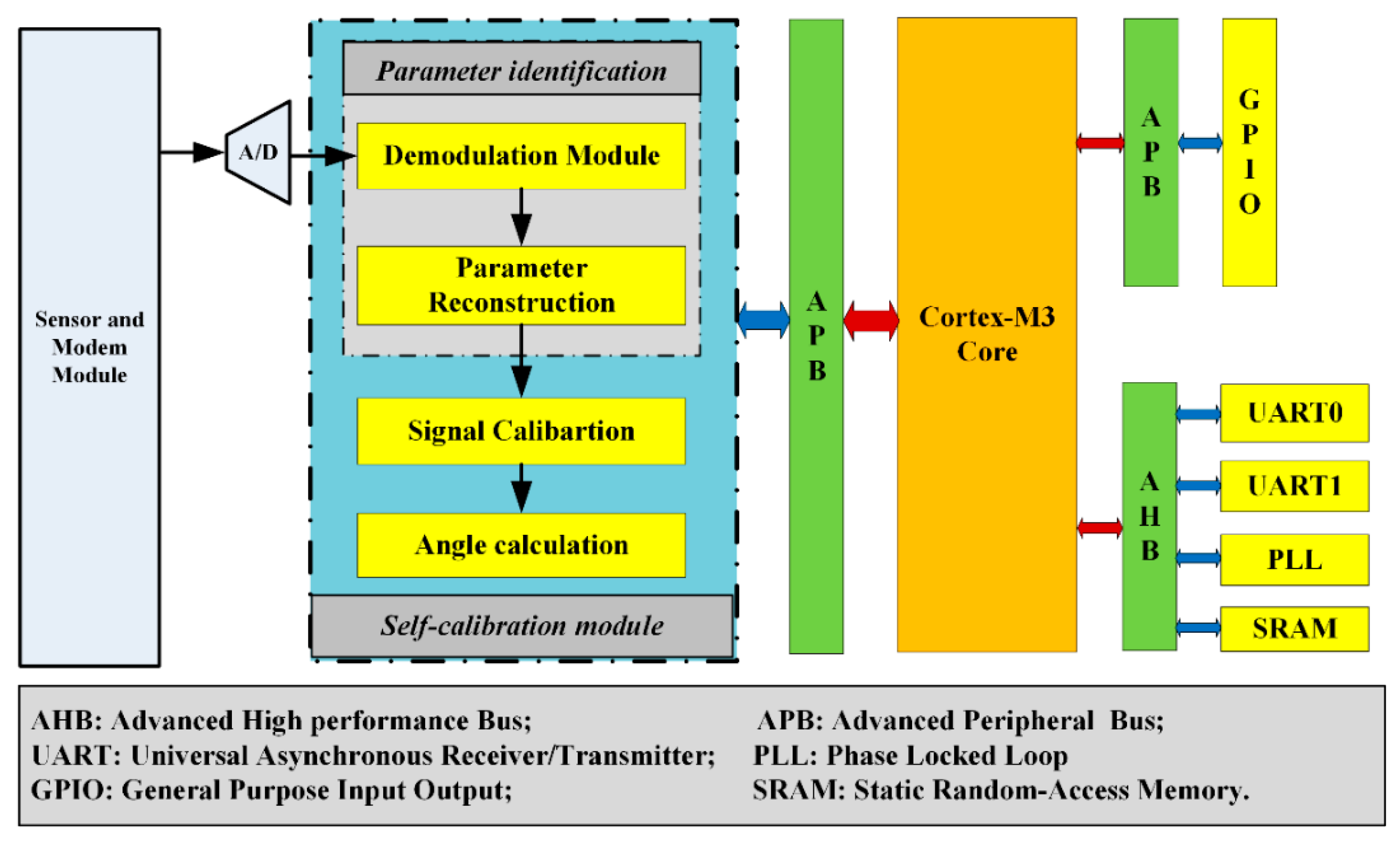

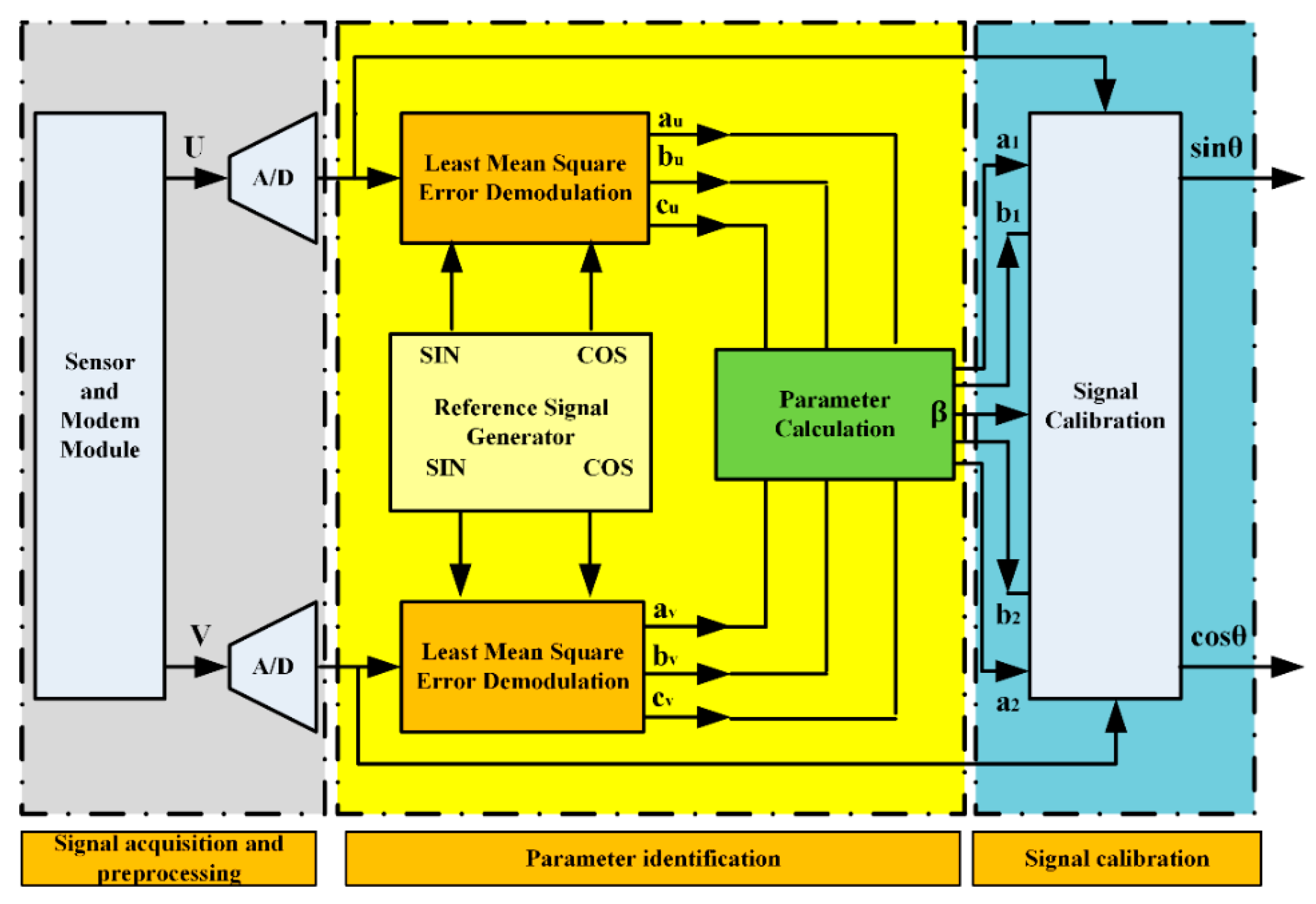

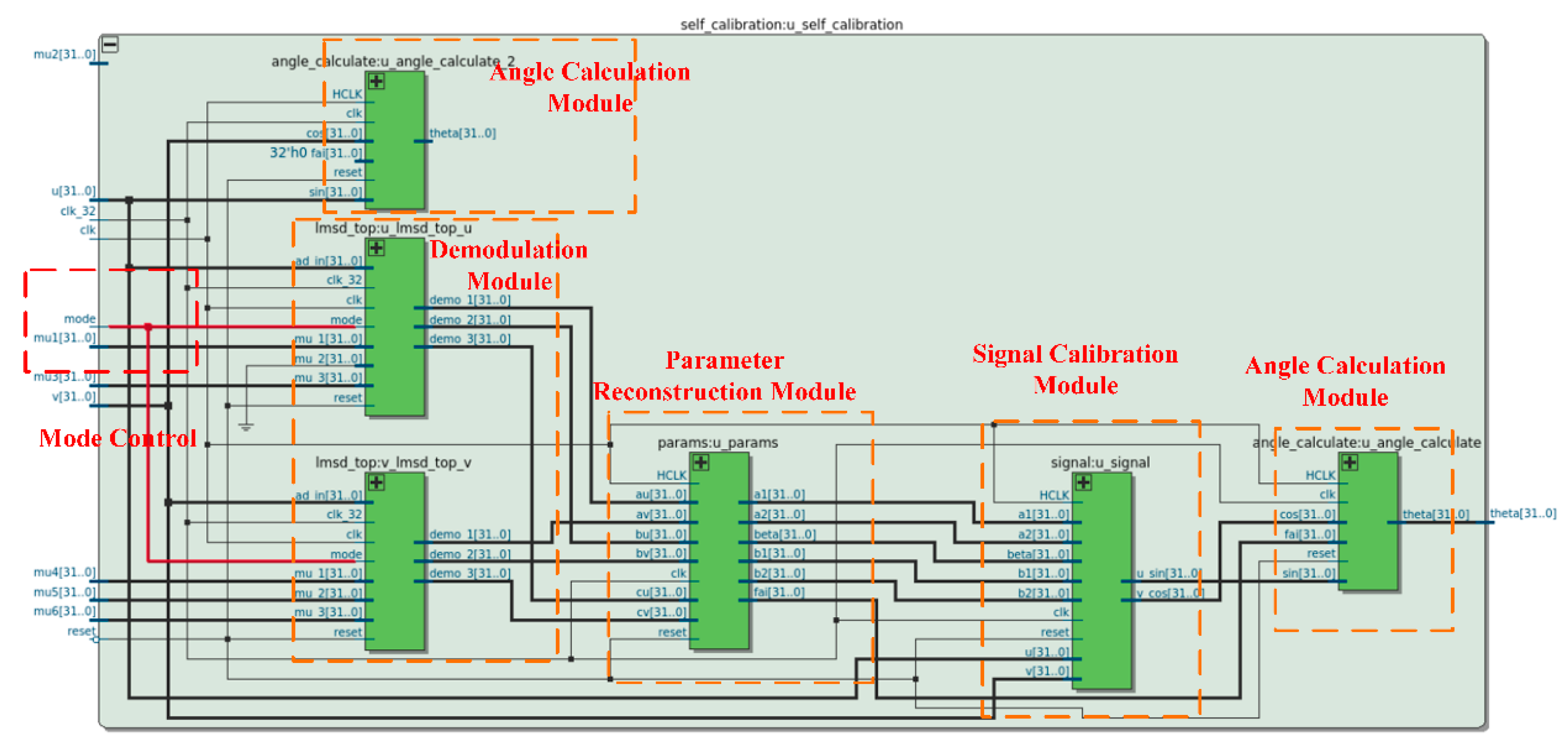

4.2. RTL Simulation of the Self-Calibration Coprocessor

According to the overall scheme design, the architecture of

Figure 2 is described using the Verilog hardware description language [

27]. The purpose of the RTL simulation is to study the error ratio that the algorithm can reduce errors involving quantization and rounding errors of fixed-point calculation modules (multiplication, root number, and arctangent operations). The RTL view of the coprocessor after synthesis with Altera Quartus II [

28] is shown in

Figure 11.

The resource overhead results obtained from Quartus synthesis tool and power estimation results from Quartus PowerPlay Power Analyzer Tool are summarized in

Table 7.

For a sampling frequency of 250 Hz and an angular frequency of 0.05 Hz, the step factor of signal

is set to

and the step factor of signal

is set to

. The data is quantized using a 32-bit signed fixed-point number with a simulation time set to 400 s. Simulation results are shown in

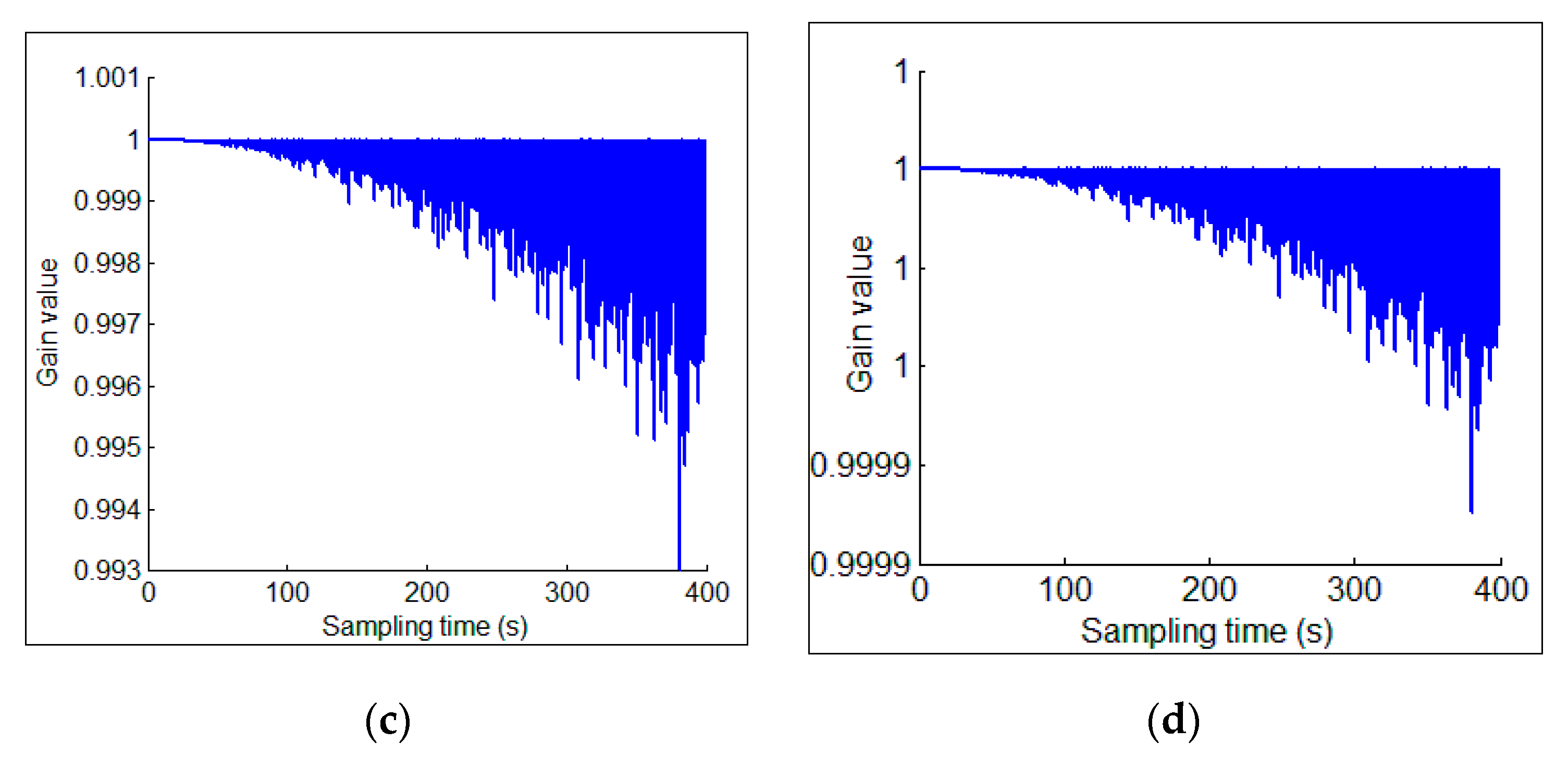

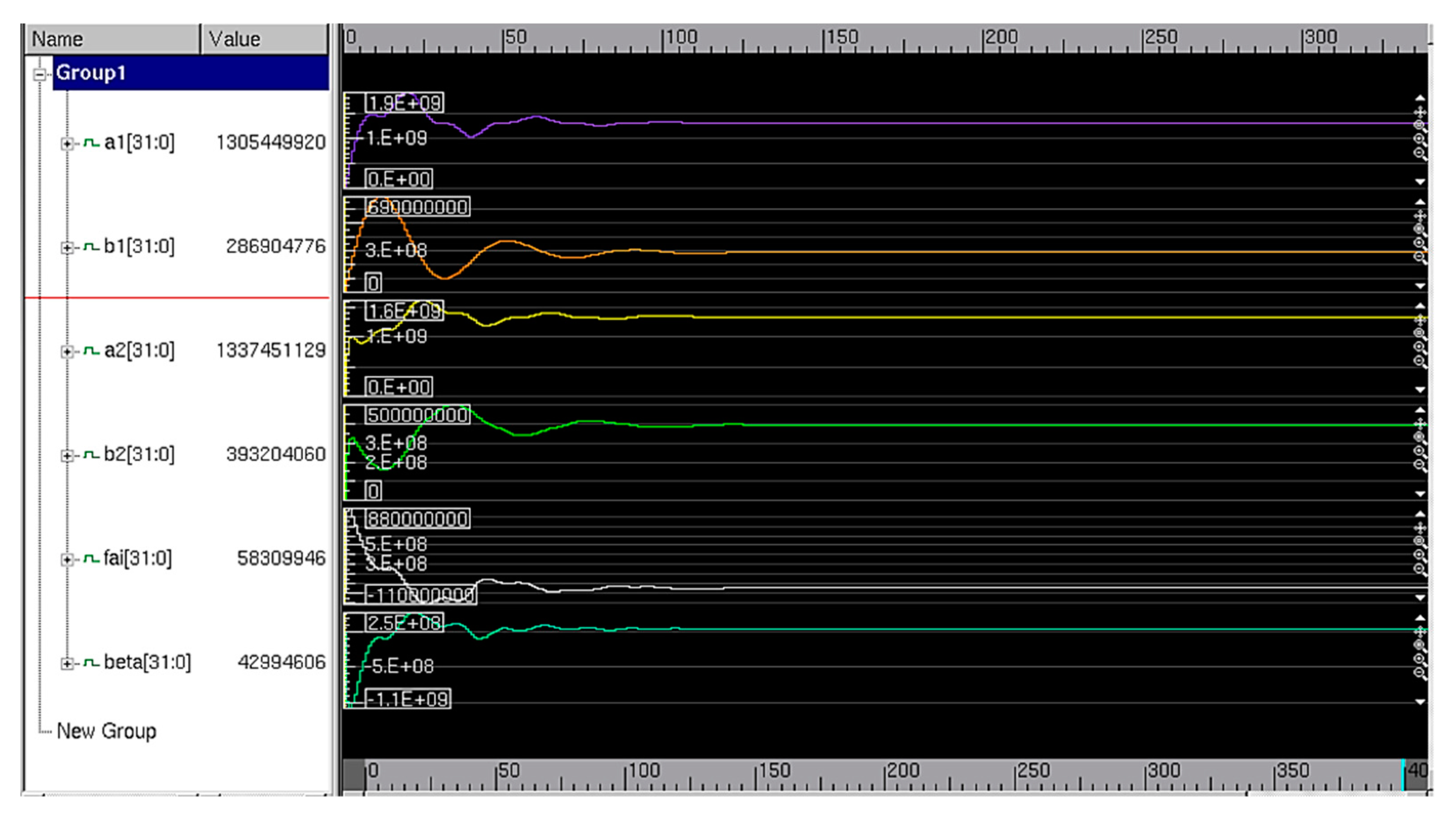

Figure 12.

Specific parameter identification results are shown in

Table 8.

The identification values of the amplitude and DC offset are obtained after dividing the identified machine value by . The identification values of the phase shift are obtained after multiplying the identified machine value by .

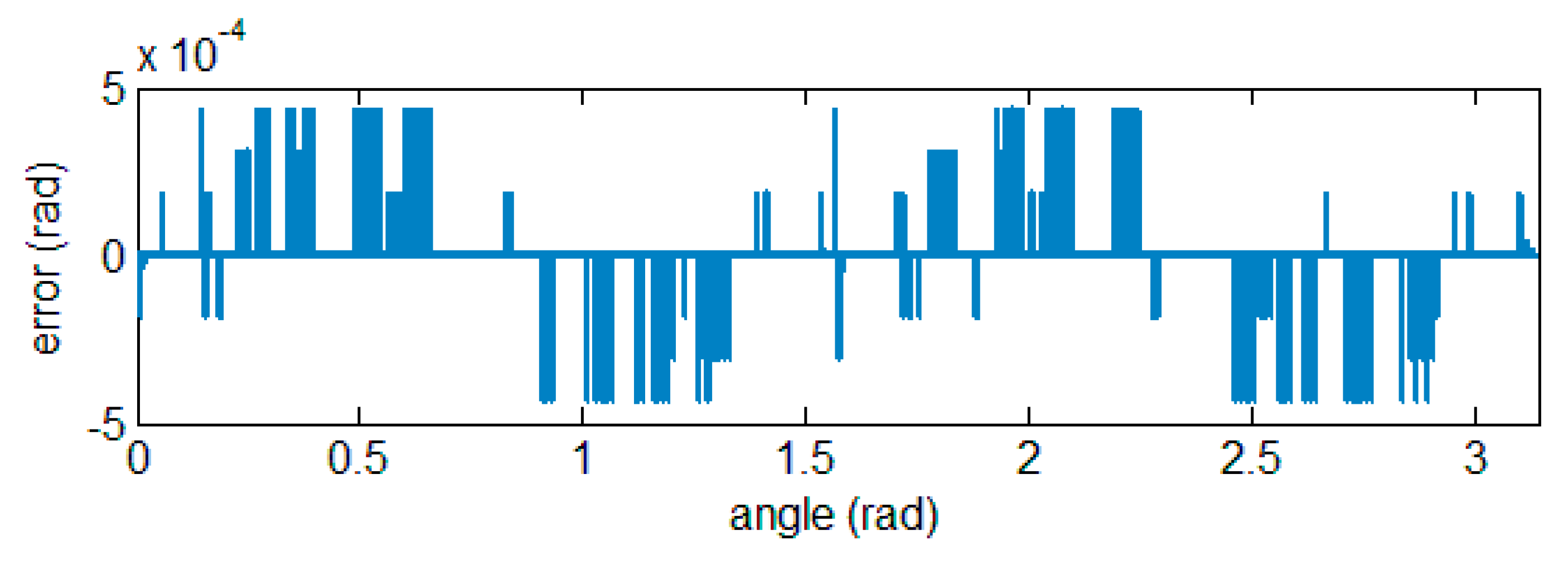

Figure 13 shows the error curve of the angle output by the coprocessor, while the error without calibration is shown in

Figure 8a.

The maximum value of the absolute angular error after calibration was 9.50 × 10−3°, while the value without calibration was 30.38°, the error reduces to 0.03% of the non-calibration value.

Table 8 shows that the angle-related estimates are not as accurate as the amplitude and DC bias estimates. The angle is calculated by the arctangent module and the calculation error of the arctangent operation is shown in

Figure 14. The error is

orders of magnitude when the operands are sine and cosine functions of magnitude 1.

The accuracy loss in the signal calibration and arctangent modules is one factor that causes the circuit simulation results to be inferior to the MATLAB simulation results. This is mainly related to the multiplication calculation’s rounding error, especially in the arctangent module where 30 multiplication operations are iteratively performed. The circuit optimization of these two parts will be the focus of future work. The results show that the accuracy loss of the calculation modules limits the further improvement of the calibration accuracy. The optimization of these modules is a means for further improved accuracy.

4.3. Experiment Based on FPGA and a CAPS

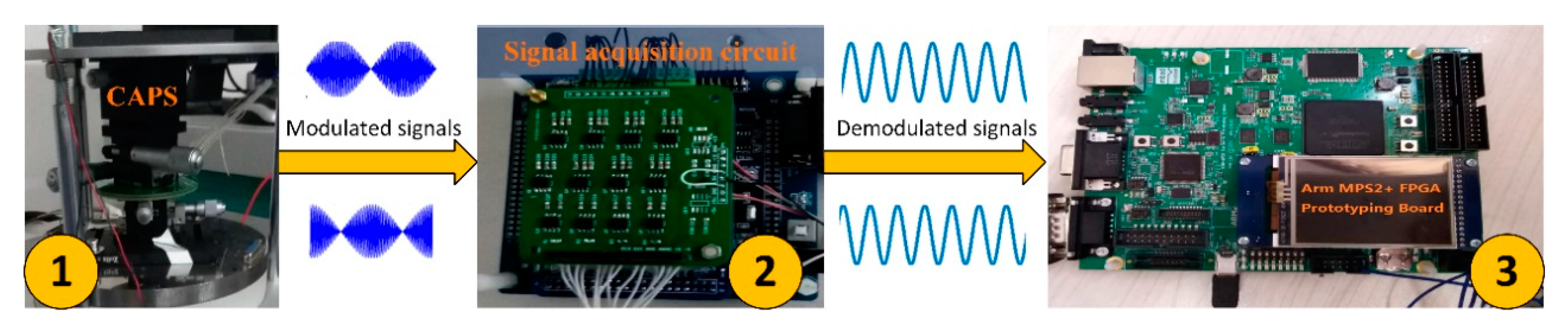

An experiment is conducted to verify the prototype, and the primary experimental equipment is shown in

Figure 15. A CAPS [

3] is placed on the turntable (Aviation Industry Co., Beijing, China) and outputs a measurement signal during rotation. The sensitive petal-form electrodes of the CAPS are sine waves in polar coordinates spanning 1 cycles. The signal is demodulated and converted from analog to digital by the signal acquisition circuit. The digital signal is then self-calibrated on the ARM MPS2+ FPGA prototyping board [

29] and the drive clock frequency is 25 MHz. The static measurement error of the turntable is about 0.0001 degrees and the dynamic measurement error is about 0.001 degrees, which meets the experimental requirements.

In the self-calibration process, the turntable rotates at 18°/s and the sampling frequency is 250 Hz. The resolution of the acquired angle is 0.072° and the exact values are obtained through the turntable.

Figure 16 shows the waveform of the collected signals.

In the experiment, the step factor of signal

is set to

and the step factor of signal

is set to

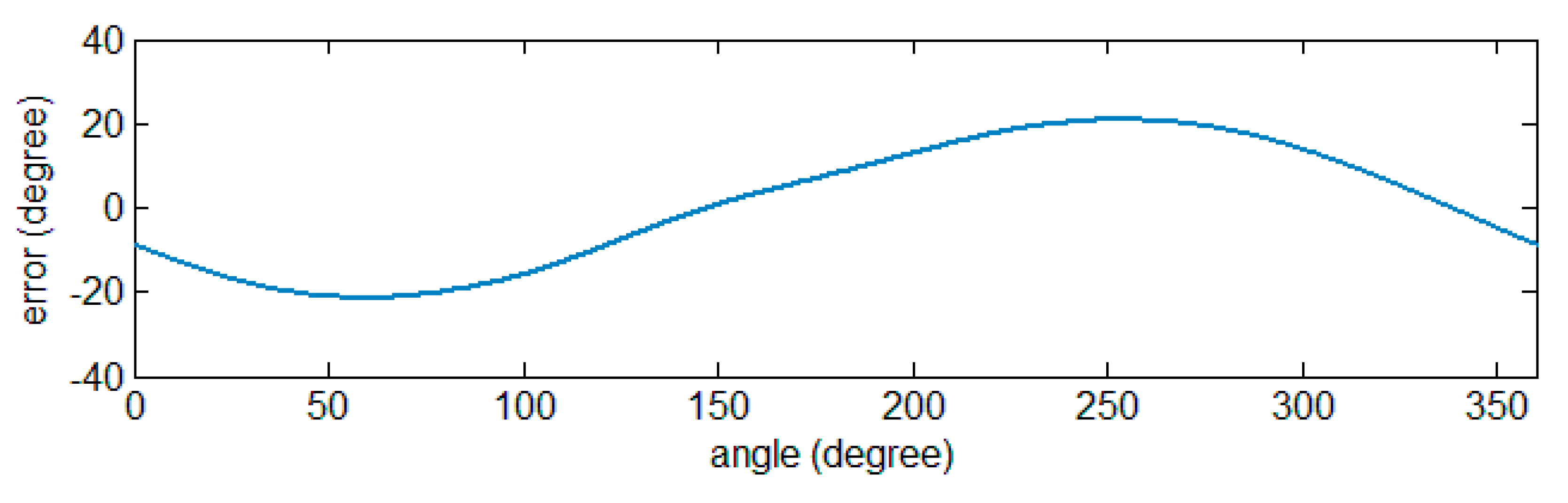

. The angular error without calibration is shown in

Figure 17. The peak-to-peak value and maximum absolute value of the error are 43.3964° and 22.5154°, respectively.

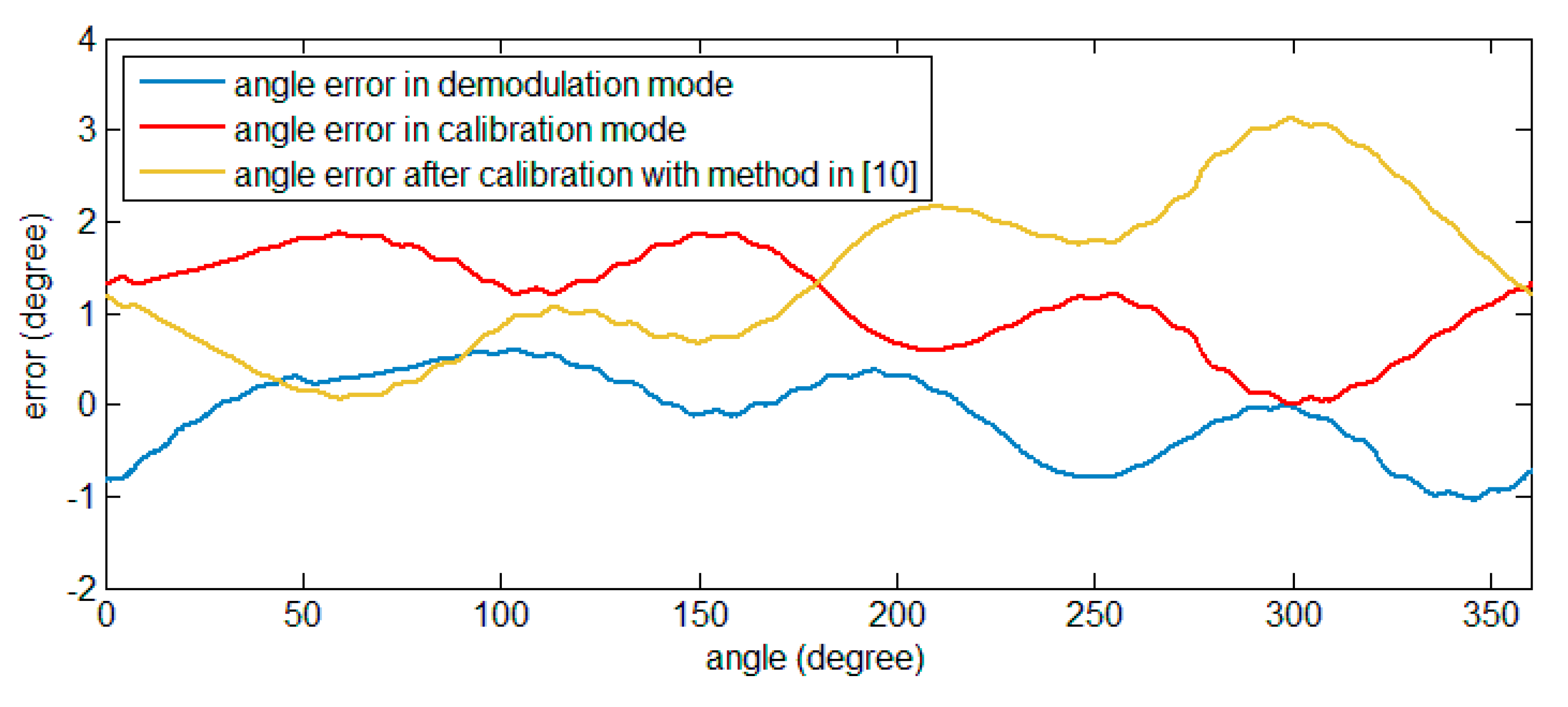

The angle values output by the SoC during the calibration process are also analyzed. The error results are shown in

Figure 18, indicated by the angle error curve in demodulation mode for the evaluation of the accuracy of parameter calculations. The peak-to-peak value of the error is 1.7189°, reduced to 3.96%. The maximum absolute value of the error is 0.9814°, reduced to 4.36%.

When the system is operating with angular input that is not continuous, stored parameter values need to be read, and the signal is calibrated using Equation (4). Under this circumstance, the system works in calibration mode. The values of an identified parameter are read through UART (

Table 9).

Figure 18 also shows the waveform of this angular error, indicated by the angle error curve in calibration mode. The peak-to-peak value of the error is 1.8683°, reduced to 4.31%. The maximum absolute value of the error is 1.1630°, reduced to 5.17%.

In addition, the signal parameters in the calibration mode can also be obtained by other methods and written in the program; the reference signal frequency in the demodulation mode can also be written in the program to achieve closed-loop control of the frequency estimation.

An experiment for another identification method is carried based on previous work [

9], which processes the same error model and the operation is simple. Identification values are summarized in

Table 10 and angular error is shown in

Figure 18, indicated by the angle error curve after calibration with the method used in [

9].

The peak-to-peak value of the error is 3.0617°, reduced to 7.06%. The maximum absolute value of the error is 1.7284°, reduced to 7.68%. The effect of the proposed scheme is not worse than the original work, and even has a better error suppression effect in the experiment.

As for the analysis of execution time, the results are summarized in

Table 11 for the proposed scheme and the method in [

9], in which the parameter convergence time is defined as the total execution time.

The device in the experiment is a Cyclone V FPGA with a clock frequency of 25 MHz. The algorithm in [

9] is executed under the Windows 7 operating system. The programming language is python3.6 and the CPU model is i7-7700K of Intel Corporation, clocked at 4.2 GHz. Since both schemes are iterative algorithms, comparing the execution time of one iteration is beneficial to distinguish the efficiency of the two schemes (the total execution time of the iterative algorithm is affected by the parameters and the actual processed data). Each iteration completes an update of the parameters. In the experiment, the time to complete an iteration is 40 ns at a frequency of 25 MHz. Since the calculation is completed in one clock cycle and the pipeline operation guarantees the data throughput rate, one iteration time is the length of one clock cycle. However, the highest frequency of the circuit design is also affected by the delay of the critical path in the circuit. When using PrimeTime for timing analysis, the maximum frequency of the system is expected to be around 70 MHz. For the execution speed in [

9], the total time of 100,000 iterations is calculated and averaged, and the time of a single iteration is 0.464 ms. From this result, the circuit execution speed is faster, but the algorithm in the circuit has low utilization of data, and the parameters are not optimal. These reasons make the total execution time in the experiment longer than that in [

9].

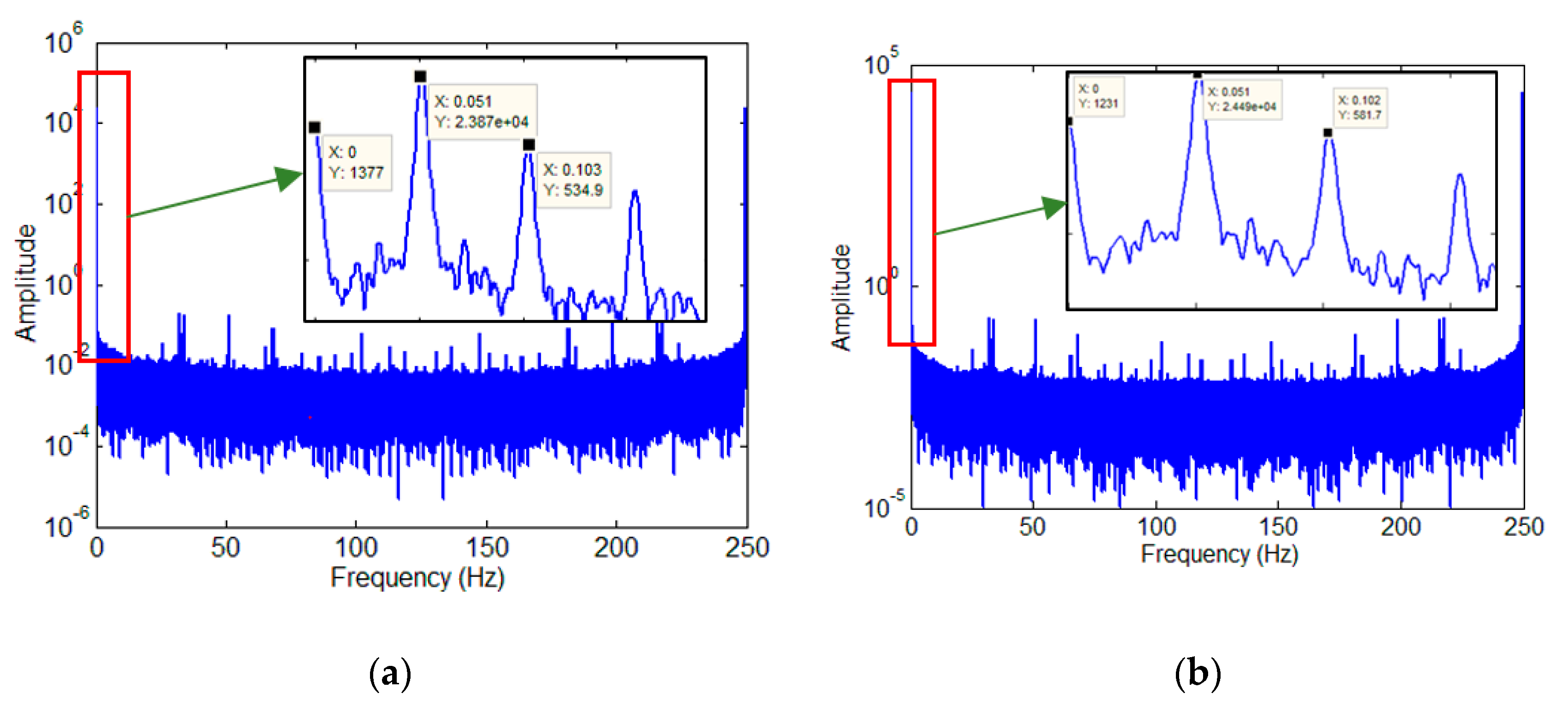

In addition to the velocity analysis, the Fourier analysis of the signal was also carried out. The result is shown in

Figure 19. The signal contains harmonic components, and the fundamental frequency value is 0.051 Hz, which deviates from the set value.

In addition, the error curve in the experiment has a certain periodicity, which may be caused by the speed fluctuation and the harmonic component of the signal. It is beyond the capability of the coprocessor and needs to be processed by a more efficient algorithm running in the processor.