An AC/DC LED Driver with Unity Power Factor and Soft Switching

Abstract

:1. Introduction

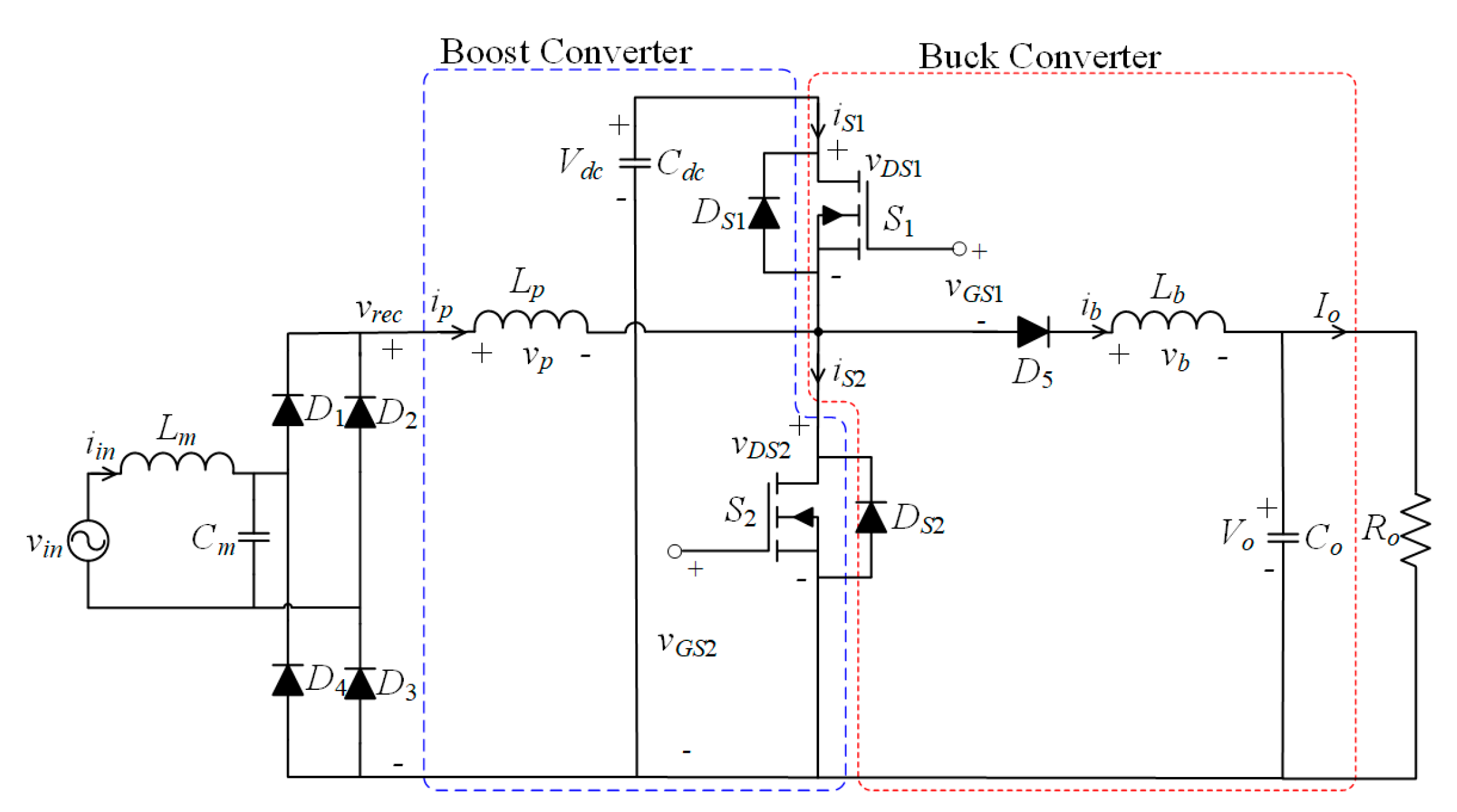

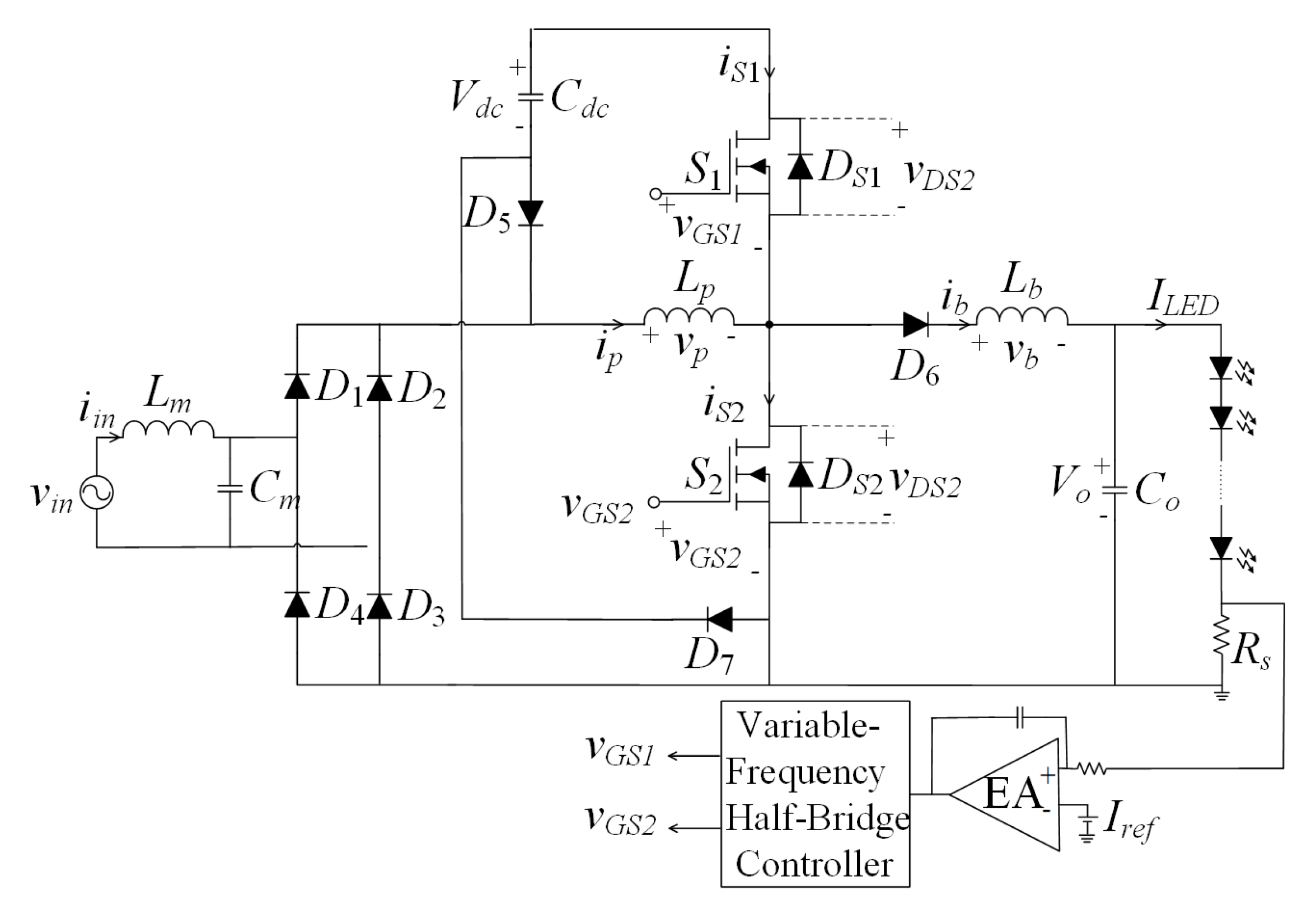

2. Proposed Circuit Topology and Operation Analysis

2.1. Circuit Topology

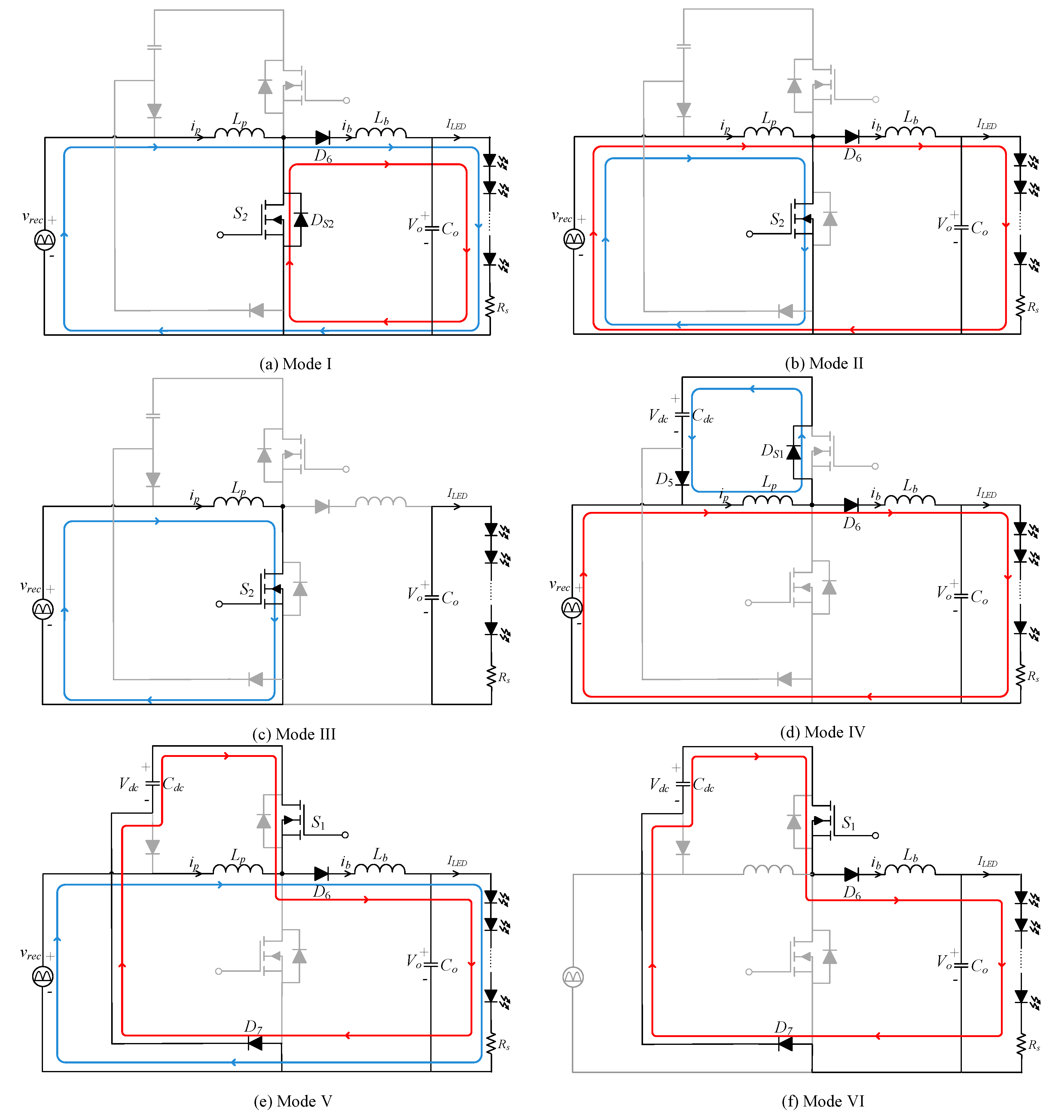

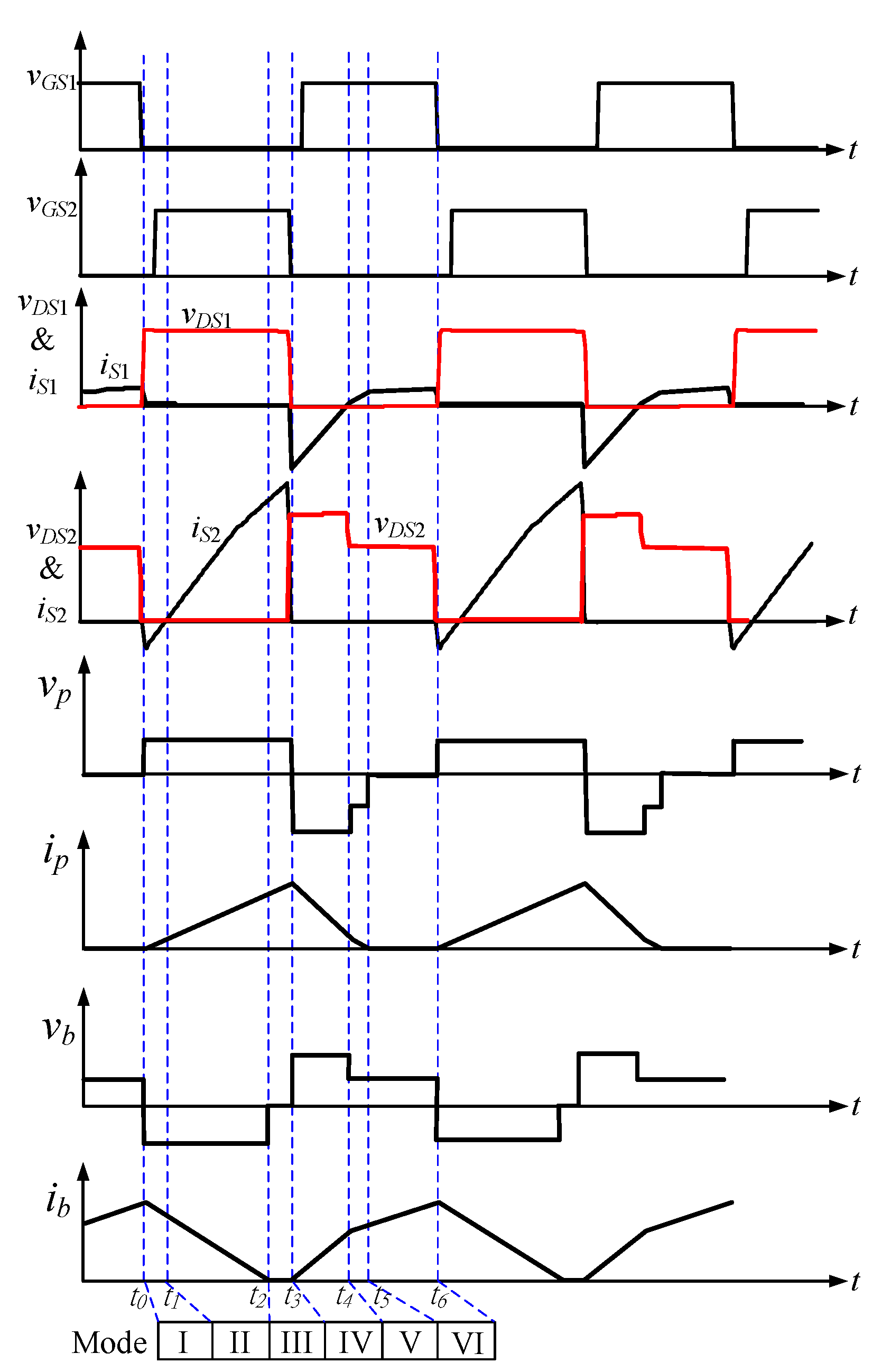

2.2. Operation Analysis

- All the semiconductor devices are ideal except that the parasitic capacitances and the intrinsic diodes of the MOSFETs are considered.

- The DC-link capacitor Cdc and the output capacitor Co are both large enough; thus, the DC-link voltage Vdc and the output voltage Vo can be regarded as constant.

- The switching frequency of the active switches, fs, is much higher than that of the input-line voltage, fs. Hence, the input-line voltage is considered as constant during each high-frequency cycle.

2.2.1. Mode I (t0 < t < t1; in Figure 3a)

2.2.2. Mode II (t1 < t < t2; in Figure 3b)

2.2.3. Mode III (t2 < t < t3; in Figure 3c)

2.2.4. Mode IV (t3 < t < t4; in Figure 3d)

2.2.5. Mode V (t4 < t < t5; in Figure 3e)

2.2.6. Mode VI (t5 < t < t6; in Figure 3f)

3. Design Equation

3.1. Buck–Boost Converter Equations

3.2. Buck Converter Equations

4. Parameters Design and Experimental Results

4.1. Parameters Design

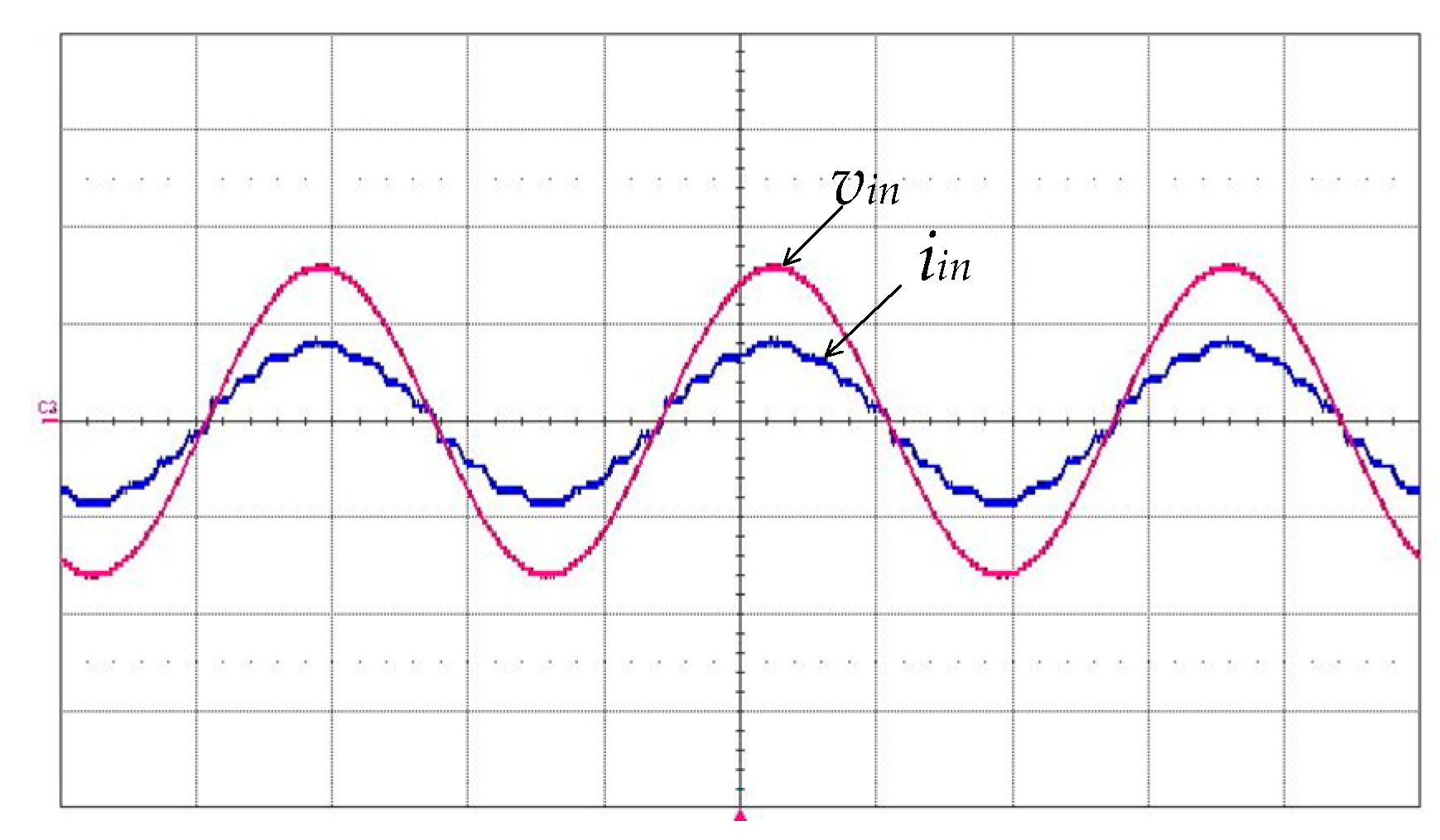

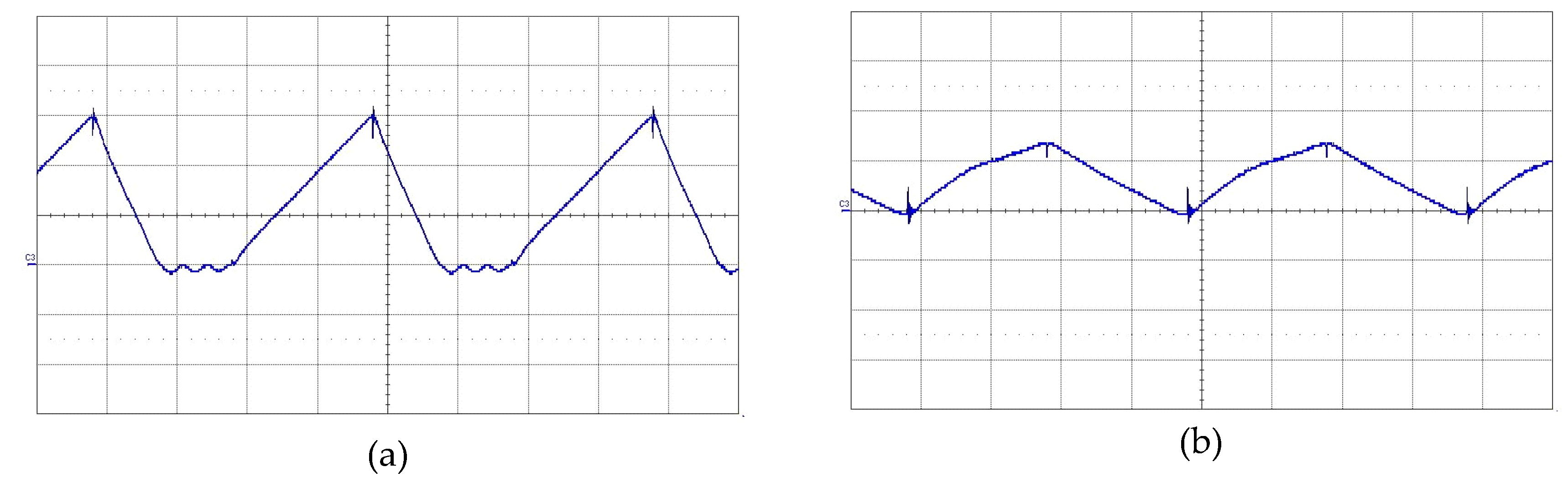

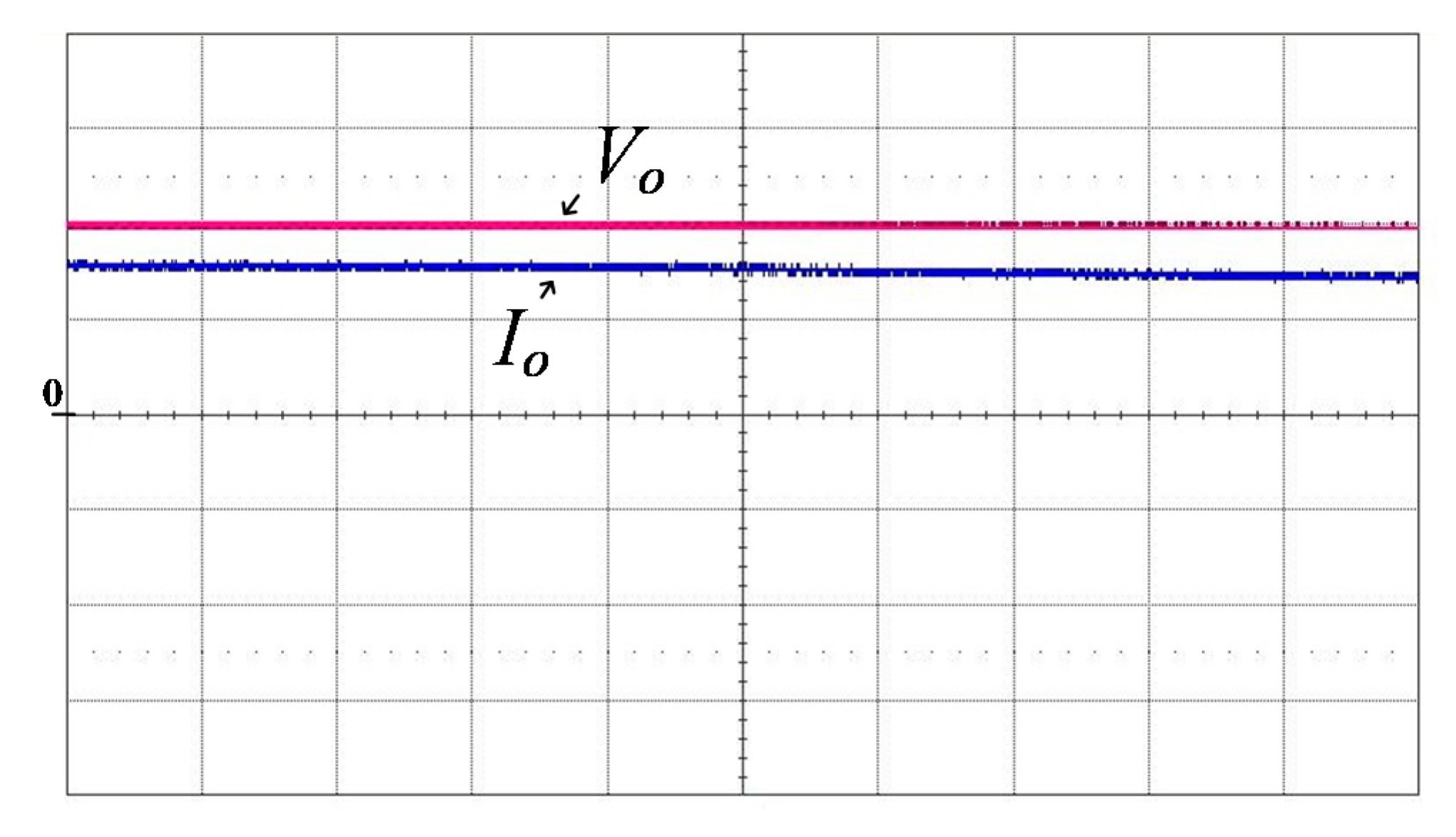

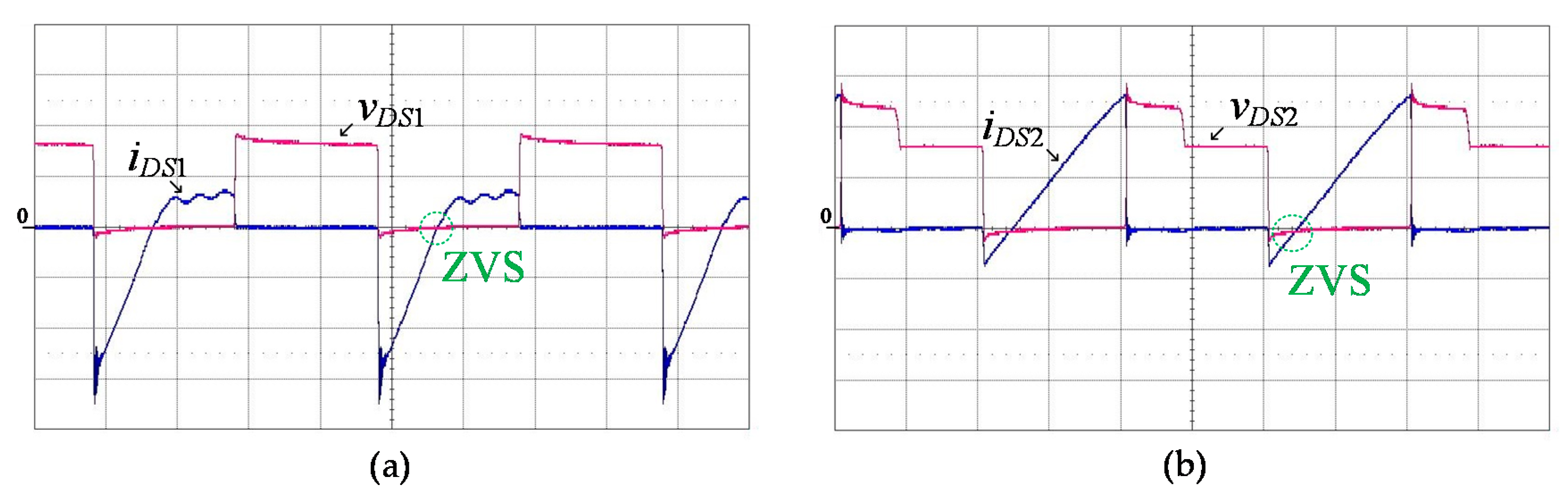

4.2. Experimental Results

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Ma, H.; Zheng, C.; Yu, W.; Gu, B.; Lai, J.S.; Feng, Q. Bridgeless electrolytic capacitor-less valley-fill AC/DC converter for offline twin-bus light-emitting diode lighting application. IET Power Electron. 2013, 6, 1132–1141. [Google Scholar] [CrossRef]

- Wang, Y.; Guan, Y.; Ren, K.; Wang, W.; Xu, D. A single-stage LED driver based on BCM boost circuit and LLC converter for street lighting system. IEEE Trans. Ind. Electron. 2015, 62, 5446–5457. [Google Scholar] [CrossRef]

- Wang, C.C.; Wu, K.H.; Liu, Y.C.; Yang, C.Y.; Alam, M.M.; Lo, Y.K.; Chiu, H.J. Study and implementation of an improved-power factor alternating-current light-emitting diode driver. IET Power Electron. 2015, 8, 1156–1163. [Google Scholar] [CrossRef]

- Wang, Y.; Huang, J.; Wang, W.; Xu, D. A single-stage single-switch LED driver based on class-E converter. IEEE Trans. Ind. 2016, 52, 2618–2626. [Google Scholar] [CrossRef]

- Gacio, D.; Alonso, J.M.; Calleja, A.J.; García, J.; Rico-Secades, M. A universal-input single-stage high-power-factor power supply for HB-LEDs based on integrated buck–flyback converter. IEEE Trans. Ind. Electron. 2011, 58, 589–599. [Google Scholar] [CrossRef]

- Xie, X.; Li, J.; Peng, K.; Zhao, C.; Lu, Q. Study on the single-stage forward-flyback PFC converter with QR control. IEEE Trans. Power Electron. 2016, 31, 430–442. [Google Scholar] [CrossRef]

- Fang, P.; Liu, Y.F.; Sen, P.C. A flicker-free single-stage offline LED driver with high power factor. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 654–665. [Google Scholar] [CrossRef]

- Weise, N.D.; Castelino, G.; Basu, K.; Mohan, N. A single-stage dual-active-bridge-based soft switched AC–DC converter with open-loop power factor correction and other advanced features. IEEE Trans. Power Electron. 2014, 29, 4007–4016. [Google Scholar] [CrossRef]

- Almeida, P.S.; Braga, H.A.C.; Dalla Costa, M.A.; Alonso, J.M. Offline soft-switched LED driver based on an integrated bridgeless boost–asymmetrical half-bridge converter. IEEE Trans. Ind. Appl. 2015, 51, 761–769. [Google Scholar] [CrossRef]

- Cheng, C.A.; Chang, C.H.; Chung, T.Y.; Yang, F.L. Design and implementation of a single-stage driver for supplying an LED street-lighting module with power factor corrections. IEEE Trans. Power Electron. 2015, 30, 956–966. [Google Scholar] [CrossRef]

- Cheng, H.L.; Lin, C.W. Design and implementation of a high-power-factor LED driver with zero-voltage switching-on characteristics. IEEE Trans. Power Electron. 2014, 31, 4949–4958. [Google Scholar] [CrossRef]

- Chang, C.H.; Cheng, C.A.; Chang, E.C.; Cheng, H.L.; Yang, B.E. An Integrated High-Power-Factor Converter with ZVS Transition. IEEE Trans. Power Electron. 2016, 31, 2362–2371. [Google Scholar] [CrossRef]

- Ma, H.; Lai, J.S.; Zheng, C.; Sun, P. A high-efficiency quasi-single-stage bridgeless electrolytic capacitor-free high-power AC–DC driver for supplying multiple LED strings in parallel. IEEE Trans. Power Electron. 2016, 31, 5825–5836. [Google Scholar] [CrossRef]

- Liu, K.H.; Lin, Y.L. Current waveform distortion in power factor correction circuits employing discontinuous-mode boost converters. In Proceedings of the 20th Annual IEEE Power Electronics Specialists Conference, Milwaukee, WI, USA, 26–29 June 1989; pp. 825–829. [Google Scholar]

- Cheng, H.L.; Hsieh, Y.C.; Lin, C.S. A novel single-stage high-power-factor AC/DC converter featuring high circuit efficiency. IEEE Trans. Ind. 2011, 58, 524–532. [Google Scholar] [CrossRef]

| Input voltage vin | 110 V ± 10% (rms), 60 Hz |

| Output power Po | 60 W |

| Output voltage Vo | 3.25 V × 60 = 195 V |

| Output Current Io | 0.308 A |

| Equivalent LED Resistance RLED | 633 Ω |

| Switching frequency fs | 50 kHz |

| Duty ratio D | 0.5 |

| The low-pass inductance Lm | 2.0 mH |

| The low-pass capacitance Cm | 0.47 μF |

| Dc-link capacitance Cdc | 100 μF |

| Output capacitance Co | 100 μF |

| Buck–boost inductor Lp | 0.47 mH |

| Buck inductor Lb | 2.26 mH |

| Active switches S1, S2 | IRF840 |

| Diodes D1–D7 | MUR460 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chang, Y.-N.; Cheng, H.-L.; Chang, C.-H.; Yen, H.-C.; Lin, R.-Z. An AC/DC LED Driver with Unity Power Factor and Soft Switching. Appl. Sci. 2018, 8, 780. https://doi.org/10.3390/app8050780

Chang Y-N, Cheng H-L, Chang C-H, Yen H-C, Lin R-Z. An AC/DC LED Driver with Unity Power Factor and Soft Switching. Applied Sciences. 2018; 8(5):780. https://doi.org/10.3390/app8050780

Chicago/Turabian StyleChang, Yong-Nong, Hung-Liang Cheng, Chien-Hsuan Chang, Hau-Chen Yen, and Rong-Zong Lin. 2018. "An AC/DC LED Driver with Unity Power Factor and Soft Switching" Applied Sciences 8, no. 5: 780. https://doi.org/10.3390/app8050780

APA StyleChang, Y.-N., Cheng, H.-L., Chang, C.-H., Yen, H.-C., & Lin, R.-Z. (2018). An AC/DC LED Driver with Unity Power Factor and Soft Switching. Applied Sciences, 8(5), 780. https://doi.org/10.3390/app8050780