SiGe-Surrounded Bitline Structure for Enhancing 3D NAND Flash Erase Speed

Abstract

1. Introduction

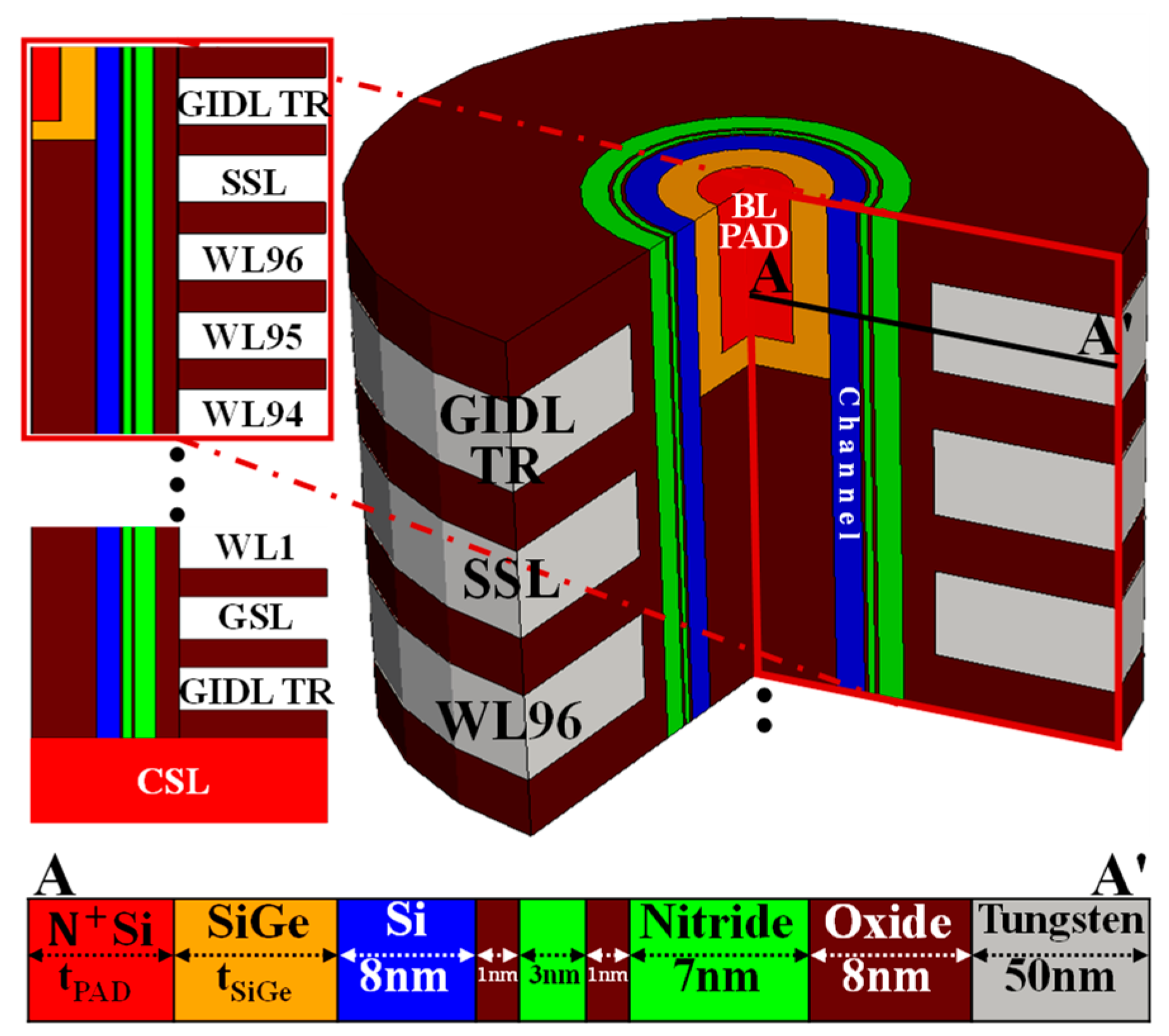

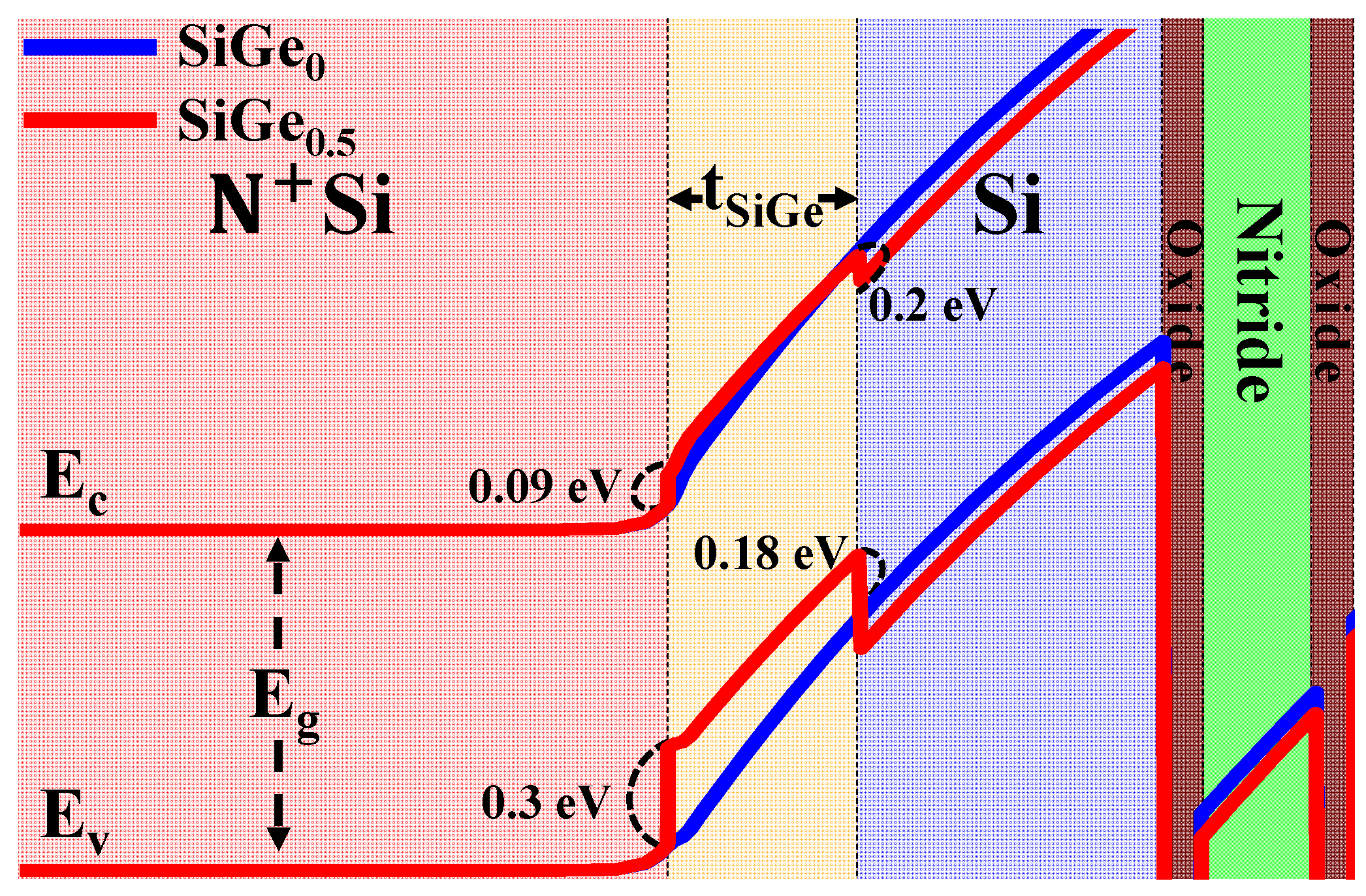

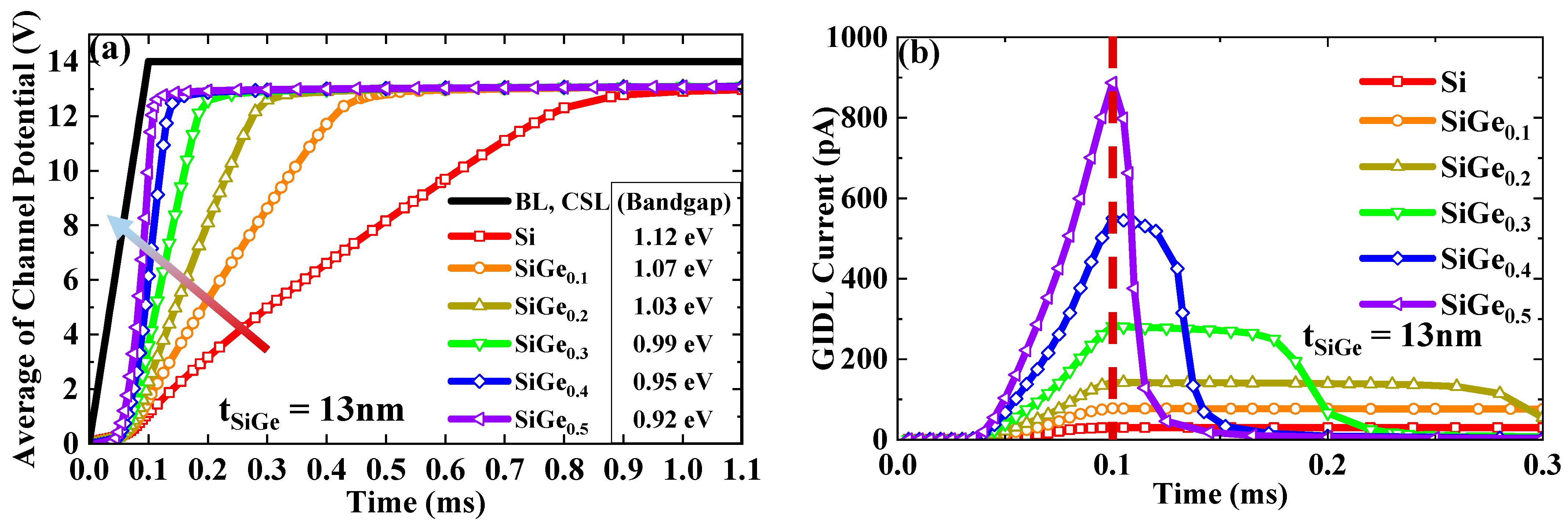

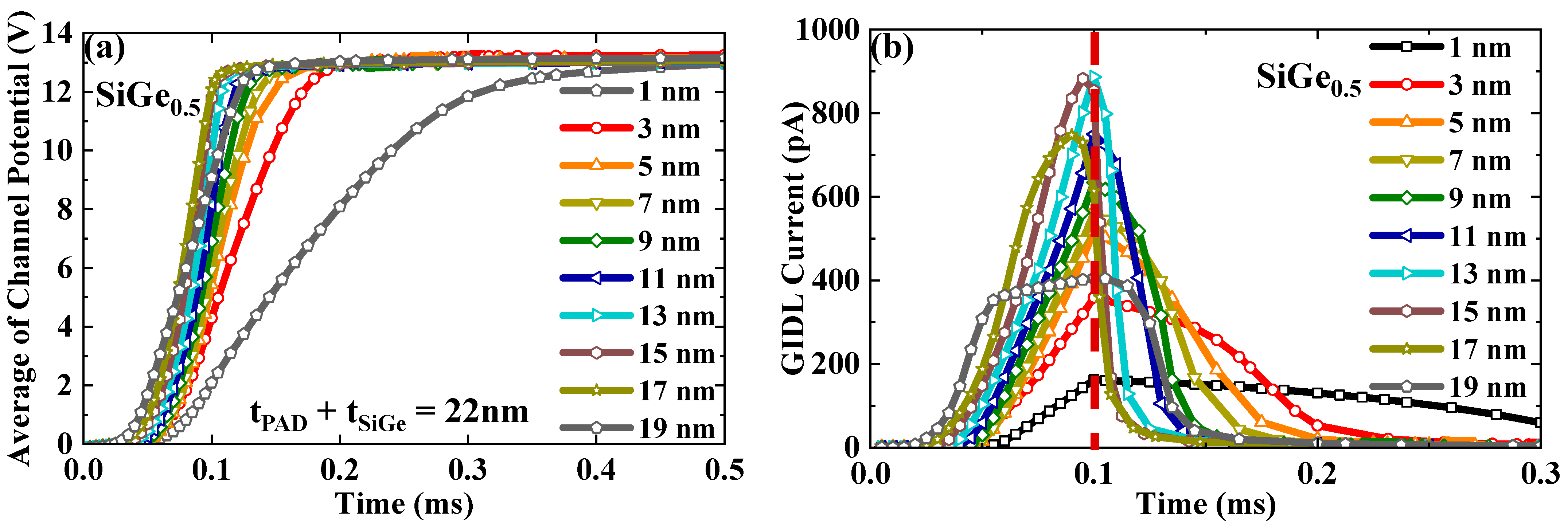

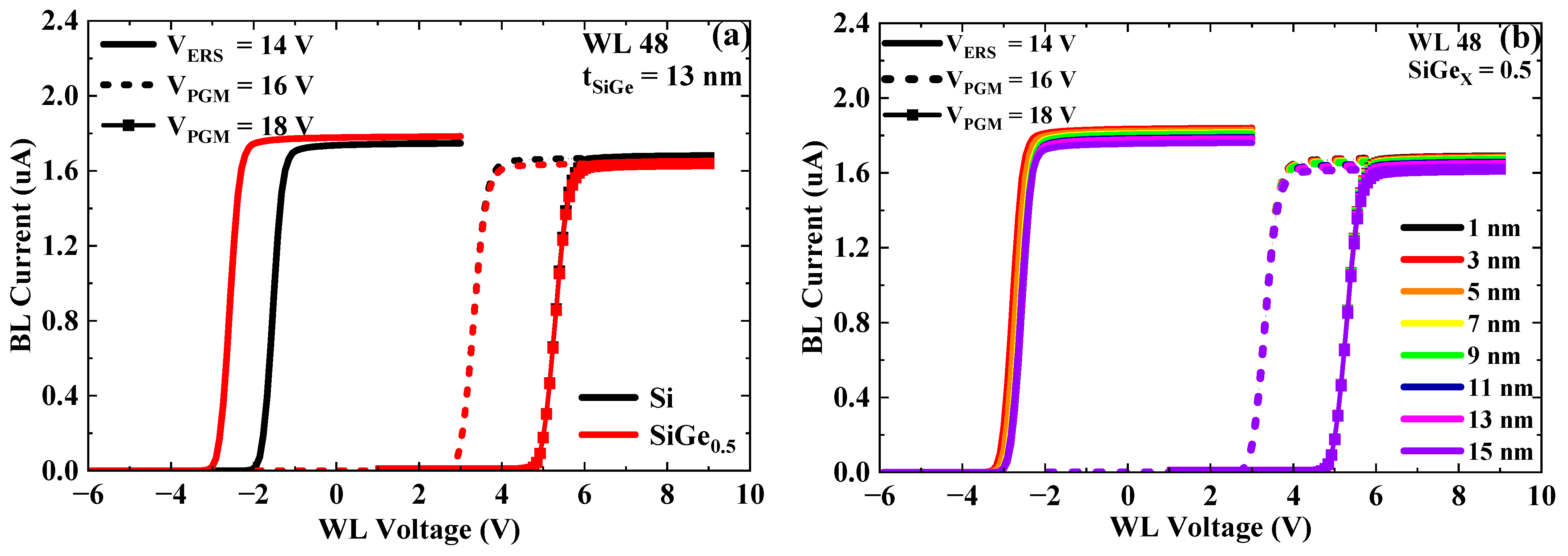

2. SiGe-Surrounded BL PAD Structure and Erase Speed Enhancement

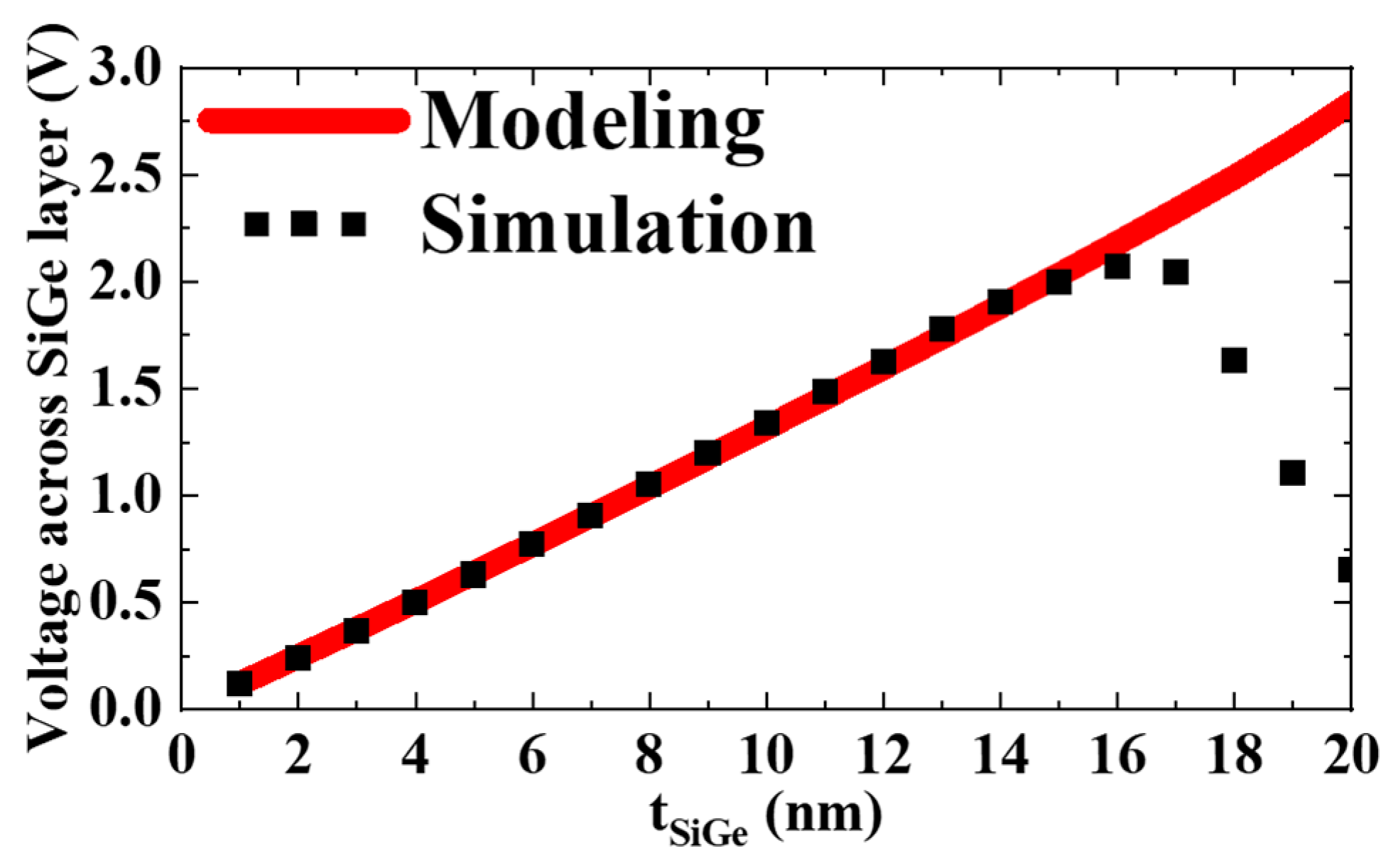

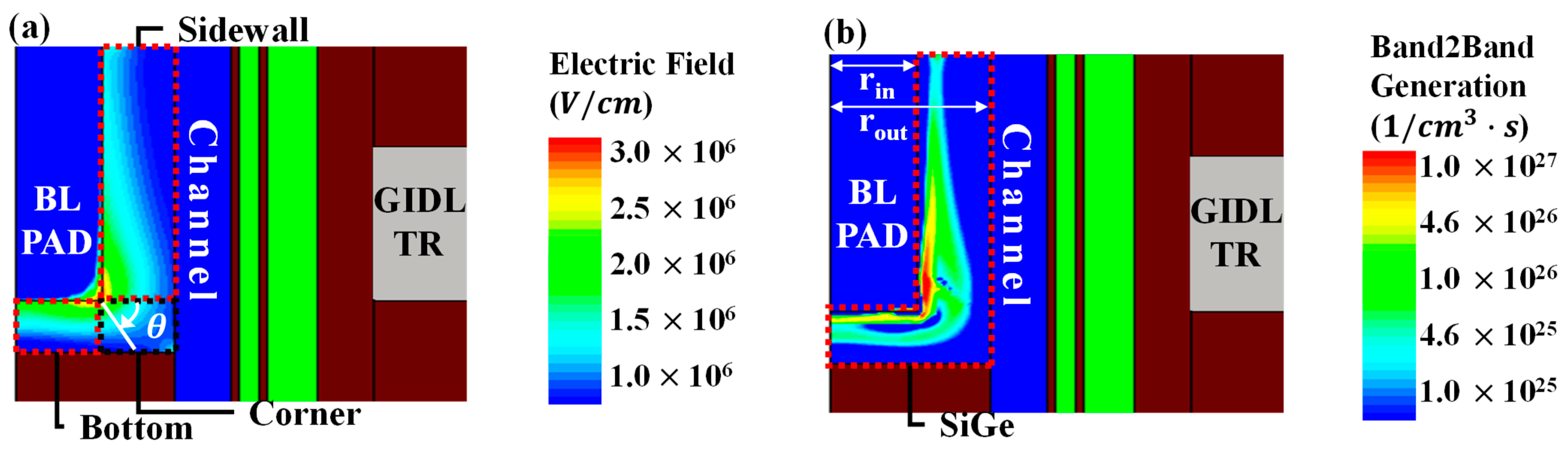

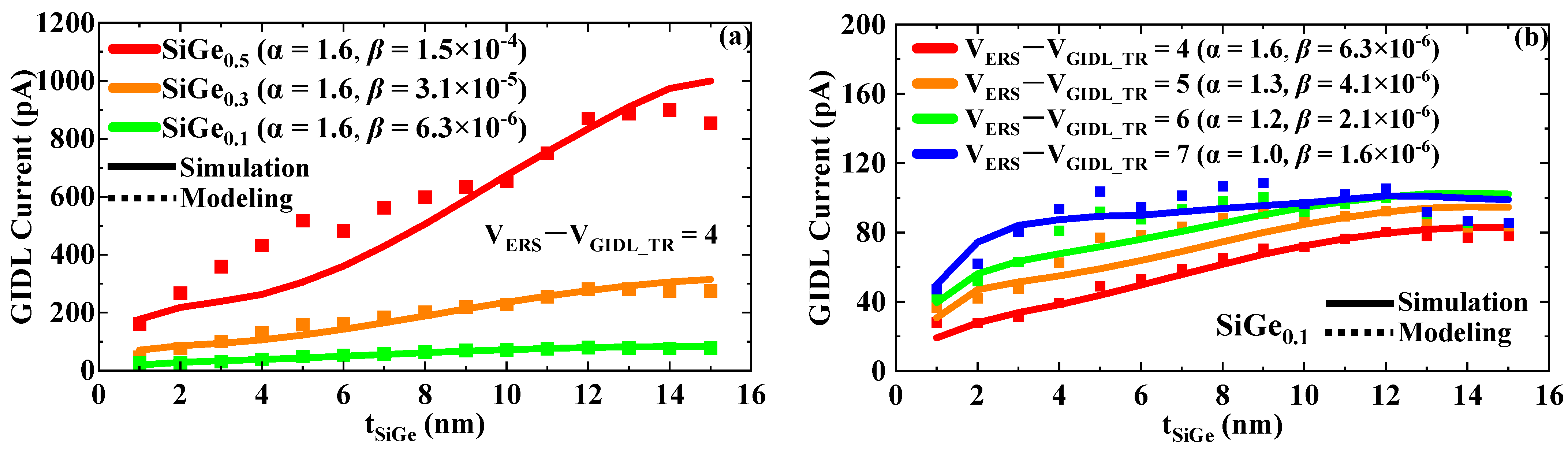

3. Modeling of GIDL Erase with SiGe Surrounded Structures

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Parat, K. NAND Technology. In Proceedings of the IEEE Hot Chips 25 Symposium (HCS), Stanford, CA, USA, 25–27 August 2013; pp. 1–18. [Google Scholar] [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar] [CrossRef]

- Jang, J.; Kim, H.; Cho, W.; Cho, H.; Kim, J.; Shim, S.; Goan, Y.; Jeong, J.; Son, B.; Kim, D.; et al. Vertical Cell Array Using TCAT (Terabit Cell Array Transistor) Technology for Ultra High Density NAND Flash Memory. In Proceedings of the Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 192–193. [Google Scholar]

- Seo, Y.; Park, J.K. Improving Z-Interference and Program Disturbance in 3D NAND Flash Memory using Asymmetric Program-pass Voltage. J. Semicond. Technol. Sci. 2024, 24, 565–571. [Google Scholar] [CrossRef]

- Oh, Y.-J.; Suh, Y.; Son, S.-W.; Cho, S.; Kang, D.; Cho, I.-H. A Novel Self-aligned Processing for Doubling the Integration Density of 3D NAND Flash Memory. J. Semicond. Technol. Sci. 2025, 25, 199–205. [Google Scholar] [CrossRef]

- Kim, J.H.; Yim, Y.; Lim, J.; Kim, H.S.; Cho, E.S.; Yeo, C. Highly Manufacturable 7th Generation 3D NAND Flash Memory with COP Structure and Double Stack Process. In Proceedings of the Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Caillat, C.; Beaman, K.; Bicksler, A.; Camozzi, E.; Ghilardi, T.; Huang, G.; Liu, H.; Liu, Y.; Mao, D.; Mujumdar, S.; et al. 3DNAND GIDL-Assisted Body Biasing for Erase Enabling CMOS under Array (CUA) Architecture. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Huh, H.; Cho, W.; Lee, J.; Noh, Y.; Park, Y.; Ok, S.; Kim, J.; Cho, K.; Lee, H.; Kim, G.; et al. 13.2 A 1Tb 4b/Cell 96-Stacked-WL 3D NAND Flash Memory with 30MB/s Program Throughput Using Peripheral Circuit Under Memory Cell Array Technique. In Proceedings of the IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 220–221. [Google Scholar]

- Komori, Y.; Kito, M.; Katsumata, R.; Fukuzumi, Y.; Tanaka, H.; Nagata, Y.; Ishiduki, M.; Aochi, H.; Nitayama, A. Disturbless flash memory due to high boost efficiency on BiCS structure and optimal memory film stack for ultra high density storage device. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Choi, S.; Choi, C.; Jeong, J.K.; Song, Y.-H. Innovative Structure to Improve Erase Speed in 3-D NAND Flash Memory with Cell-on-Peri (COP) Applied. IEEE Trans. Electron Devices 2022, 69, 4883–4888. [Google Scholar] [CrossRef]

- Choi, S.; Kang, M.; Song, Y.-H. An Improved Structure Enabling Hole Erase Operation When Using an IGZO Channel in a 3D NAND Flash Structure to Which COP (Cell-On-Peri) Structure Is Applied. Electronics 2023, 12, 2945. [Google Scholar] [CrossRef]

- Wang, B.; Gao, B.; Wu, H.; Qian, H. A new 3D NAND flash structure to improve program/erase operation speed. In Proceedings of the International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hsinchu, Taiwan, 18–20 October 2017; pp. 1–2. [Google Scholar]

- Lim, S.; Kim, S.; Lee, C.; Choi, H.; Kim, N.; Jung, J.; Yang, H.; Kim, T.-H.; Lim, J.; Ha, D.; et al. Improvement of GIDL-assisted Erase by using Surrounded BL PAD Structure for VNAND. In Proceedings of the IEEE International Memory Workshop (IMW), Monterey, CA, USA, 21–24 May 2023; pp. 1–4. [Google Scholar]

- Lee, D.; Liu, T.-J.K. SiGe/Si Heterojunction Drain Transistor for Faster 3D NAND Flash Memory Erase. In Proceedings of the IEEE International Memory Workshop (IMW), Seoul, Republic of Korea, 12–15 May 2024; pp. 1–4. [Google Scholar]

- Pratticò, D.; Laganà, F.; Oliva, G.; Fiorillo, A.S.; Pullano, S.A.; Calcagno, S.; De Carlo, D.; La Foresta, F. Integration of LSTM and U-Net models for monitoring electrical absorption with a system of sensors and electronic circuits. IEEE Trans. Instrum. Meas. 2025, 74, 1–11. [Google Scholar] [CrossRef]

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A new recombination model for device simulation including tunneling. IEEE Trans. Electron Devices 1992, 39, 331–338. [Google Scholar] [CrossRef]

- Levinshtein, M.E.; Rumyantsev, S.L.; Shur, M.S. Properties of Advanced Semiconductor Materials GaN, AlN, InN, BN, SiC, SiGe; John Wiley & Sons, Inc.: New York, NY, USA, 2001; pp. 149–185. [Google Scholar]

- Sentaurus Device User Guide, Version N-2023.09; Synopsys: Mountain View, CA, USA, 2023.

- Lee, S.; Lim, J.; Kim, J.H.; Cho, S.; Lee, Y.K.; Choi, B. High-Density 3-D NAND Cell Array Design with Hybrid Bonding. IEEE Trans. Electron Devices 2023, 70, 5638–5644. [Google Scholar] [CrossRef]

| Contact | Erase | Program | Read |

|---|---|---|---|

| BL | VERS | 0 V | 0.2 V |

| CSL | VERS | 0 V | 0 V |

| SSL | 10 V | 7 V | 7 V |

| GSL | 10 V | 7 V | 7 V |

| GIDL transistor | 10 V | 7 V | 7 V |

| Selected WL | 0 V | VPGM | VRead |

| Unselected WLs | 0 V | 7 V | 5 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, D.; Shim, W. SiGe-Surrounded Bitline Structure for Enhancing 3D NAND Flash Erase Speed. Appl. Sci. 2025, 15, 7405. https://doi.org/10.3390/app15137405

Kim D, Shim W. SiGe-Surrounded Bitline Structure for Enhancing 3D NAND Flash Erase Speed. Applied Sciences. 2025; 15(13):7405. https://doi.org/10.3390/app15137405

Chicago/Turabian StyleKim, Dohyun, and Wonbo Shim. 2025. "SiGe-Surrounded Bitline Structure for Enhancing 3D NAND Flash Erase Speed" Applied Sciences 15, no. 13: 7405. https://doi.org/10.3390/app15137405

APA StyleKim, D., & Shim, W. (2025). SiGe-Surrounded Bitline Structure for Enhancing 3D NAND Flash Erase Speed. Applied Sciences, 15(13), 7405. https://doi.org/10.3390/app15137405