A Low-Power Read-Decoupled Radiation-Hardened 16T SRAM for Space Applications

Abstract

1. Introduction

2. The Proposed LDRH16T Cell and Its Operation

2.1. Basic Operation

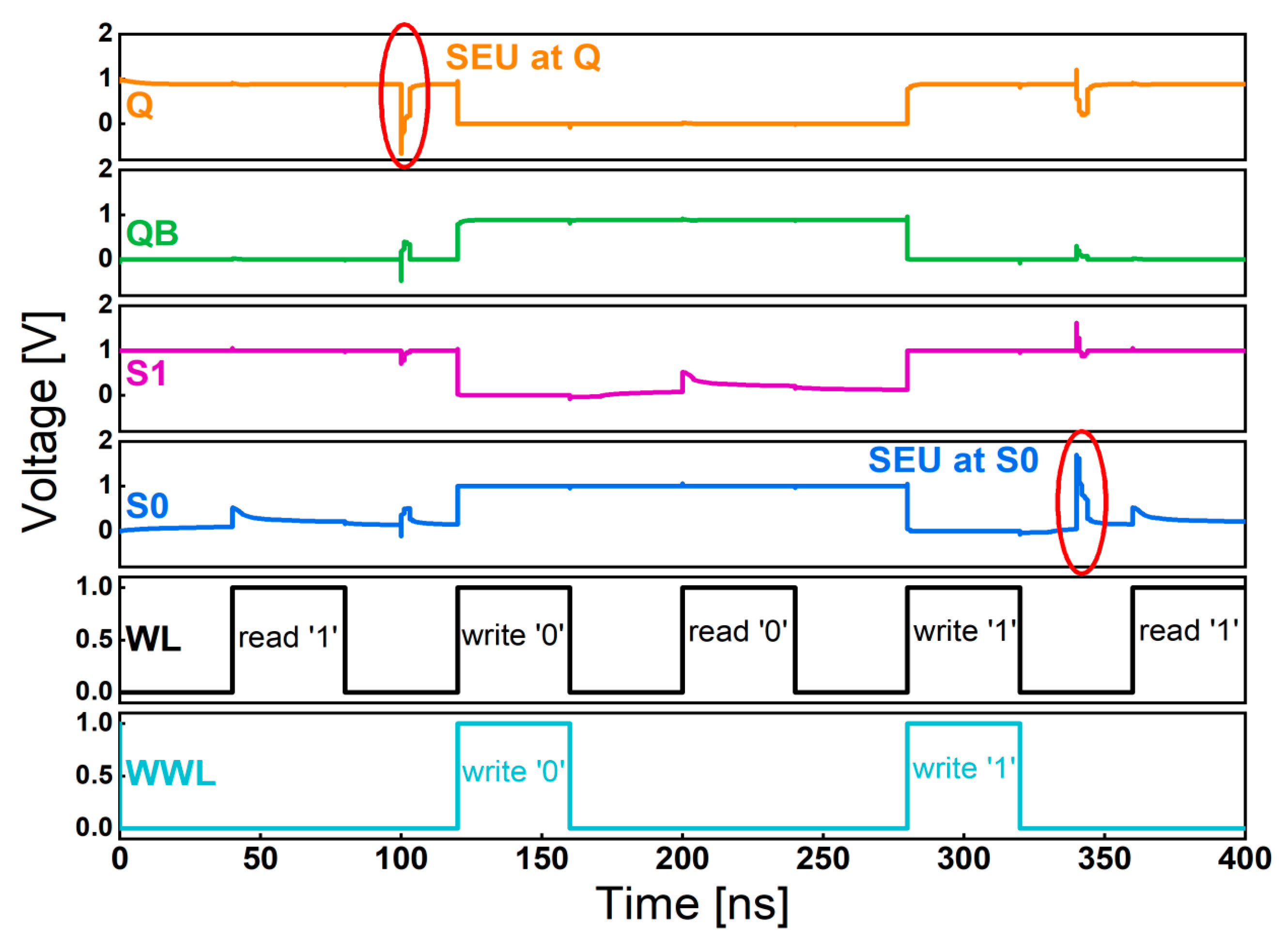

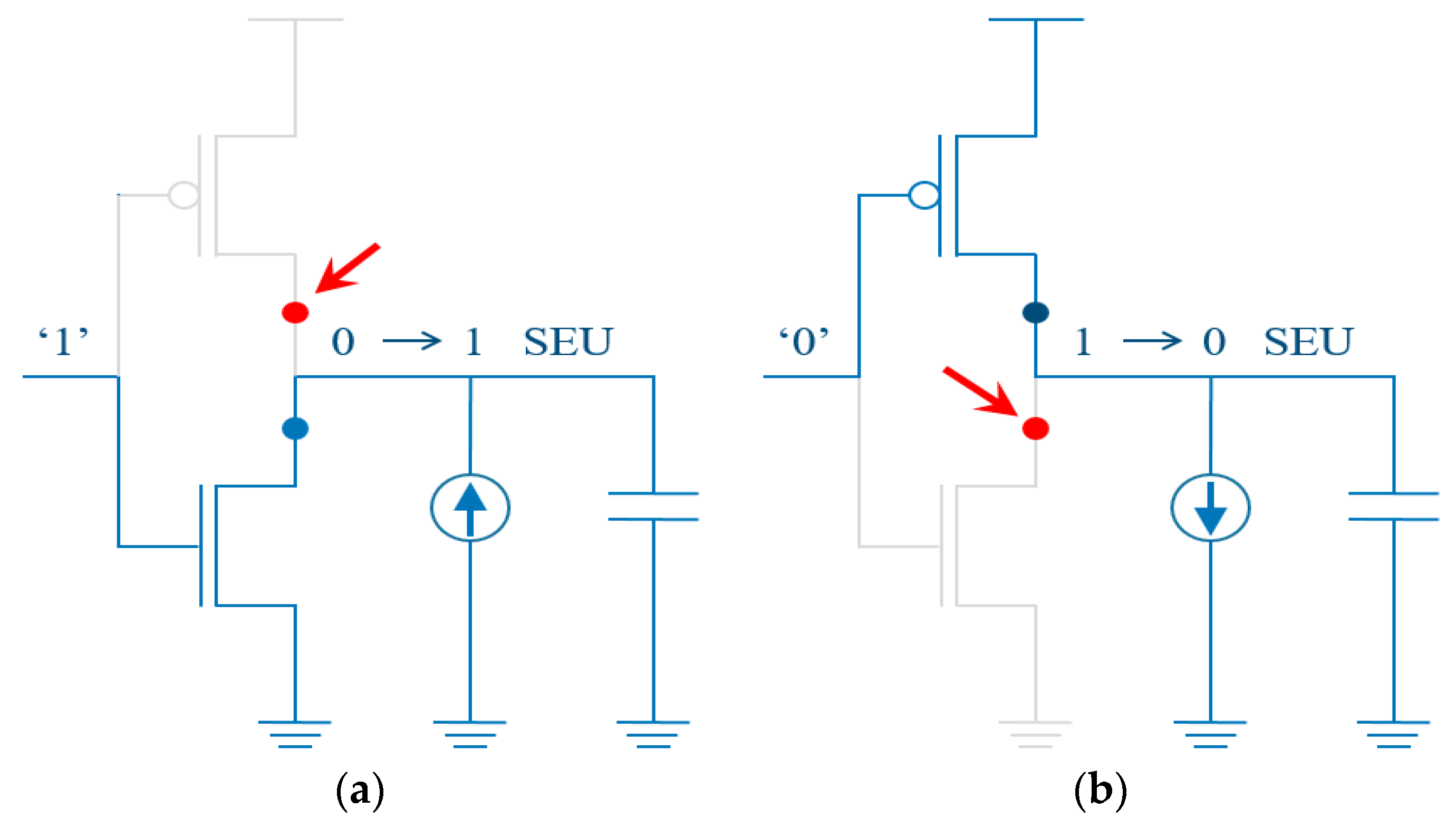

2.2. Soft-Error Recovery Analysis

3. Simulation Results and Analysis

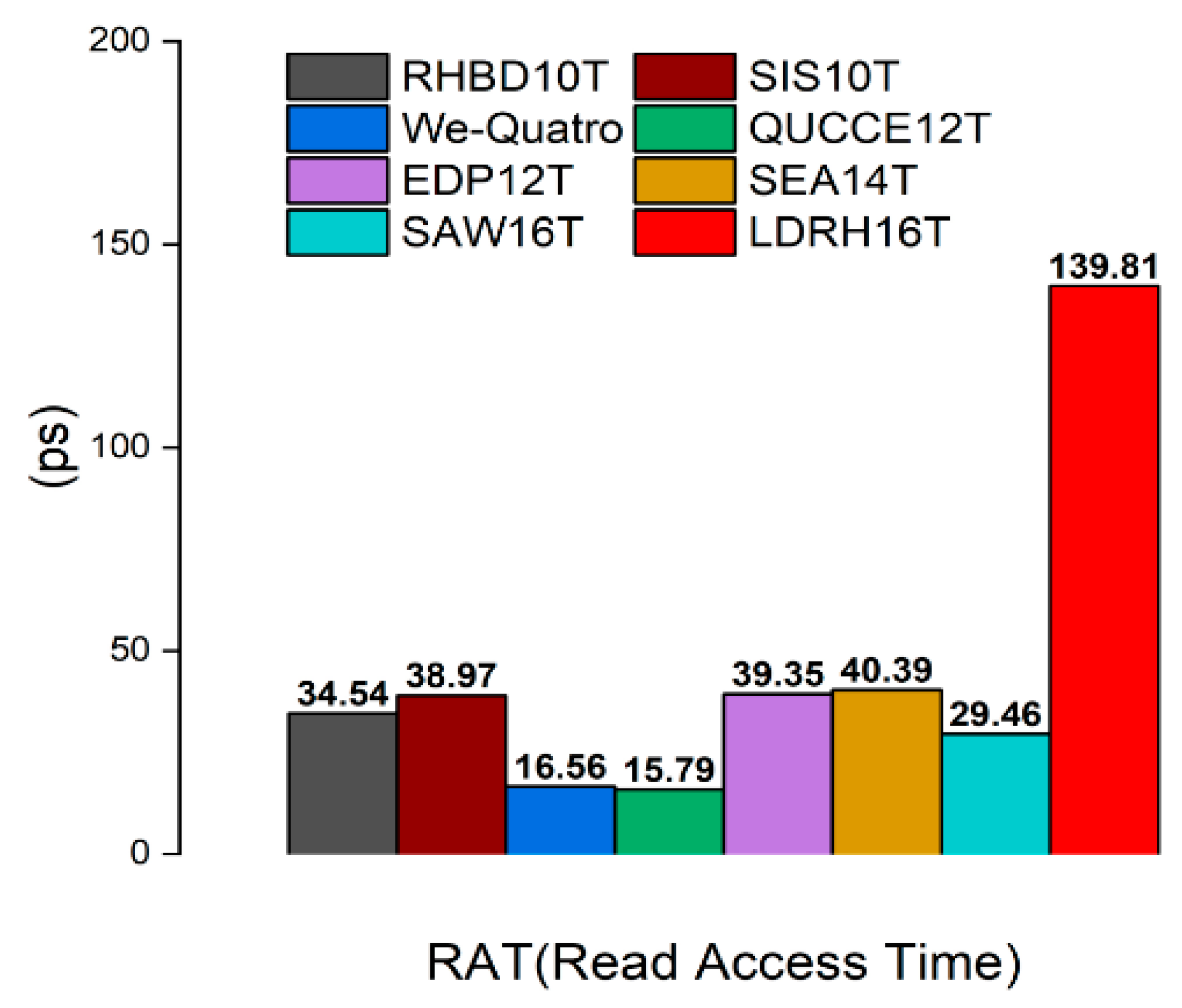

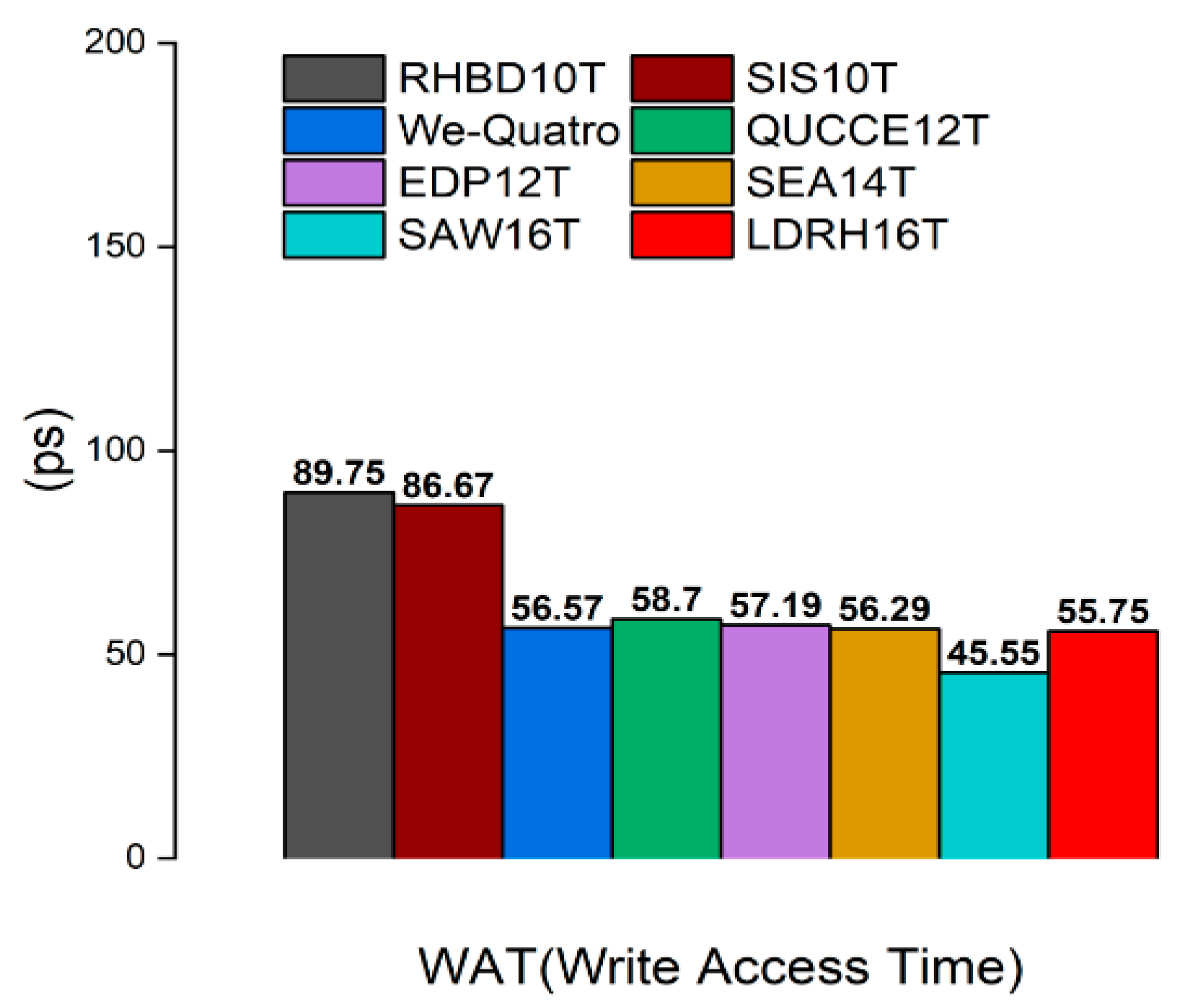

3.1. Read and Write Access Time Comparison

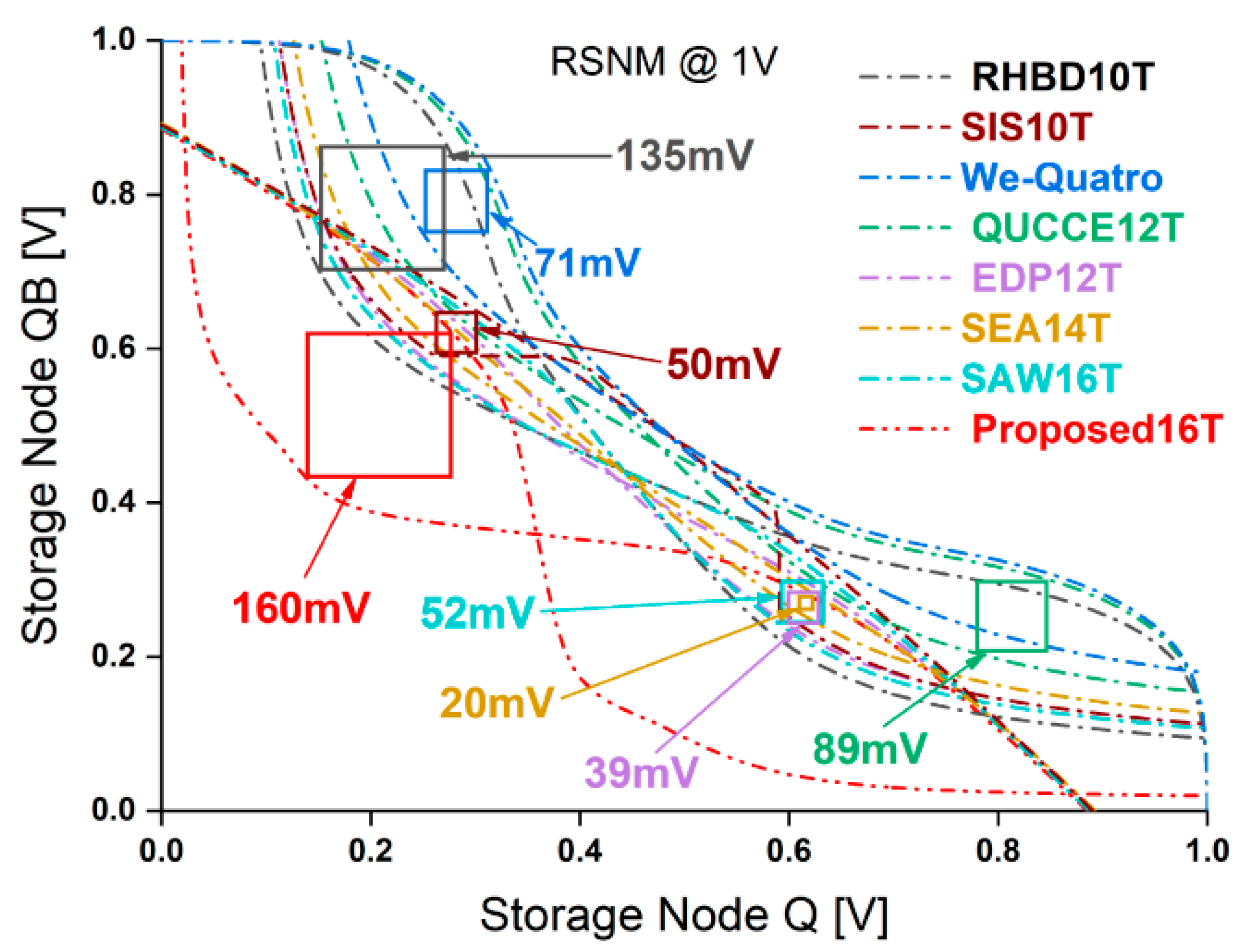

3.2. Read Stability Comparison

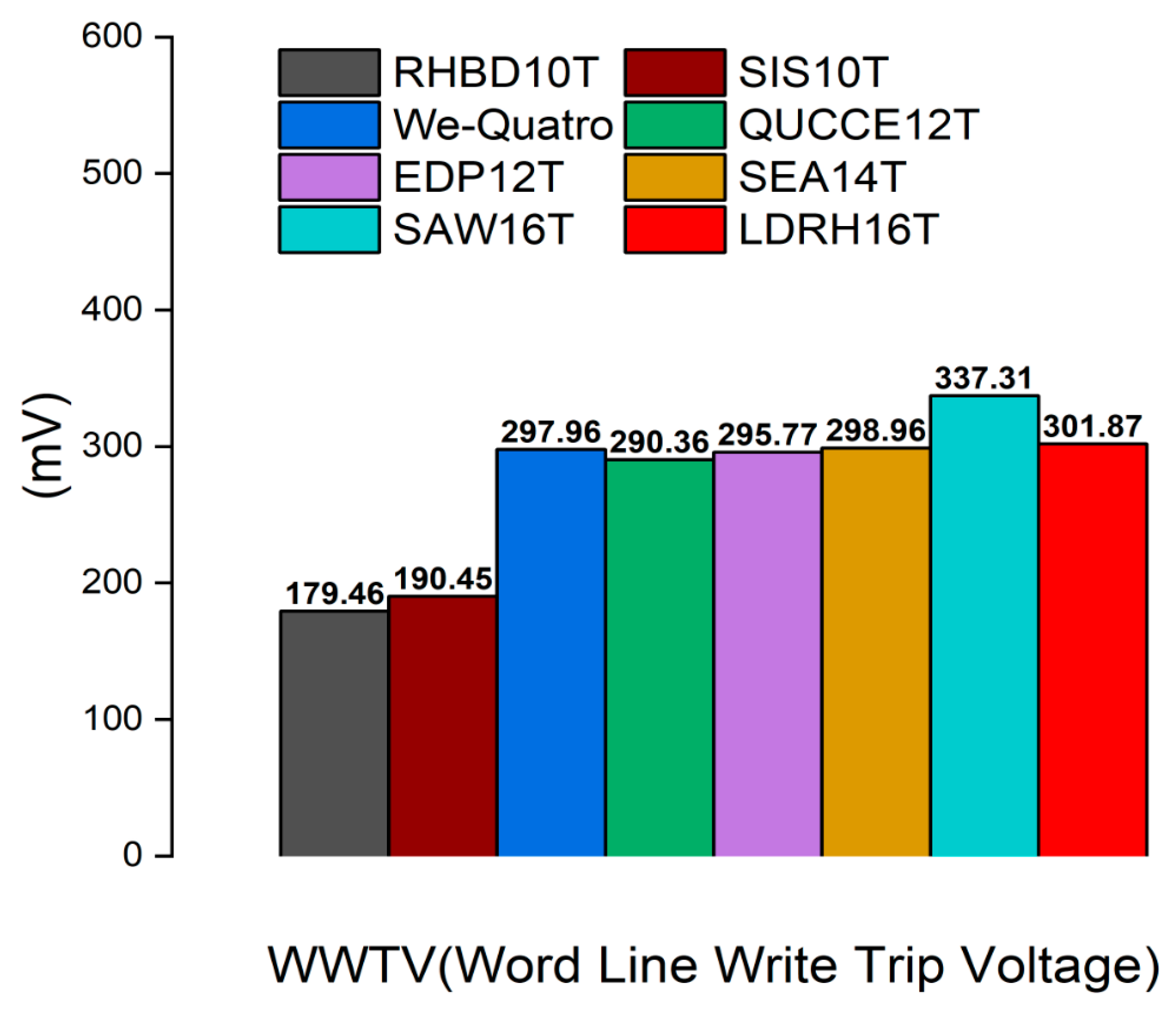

3.3. Write Ability Comparison

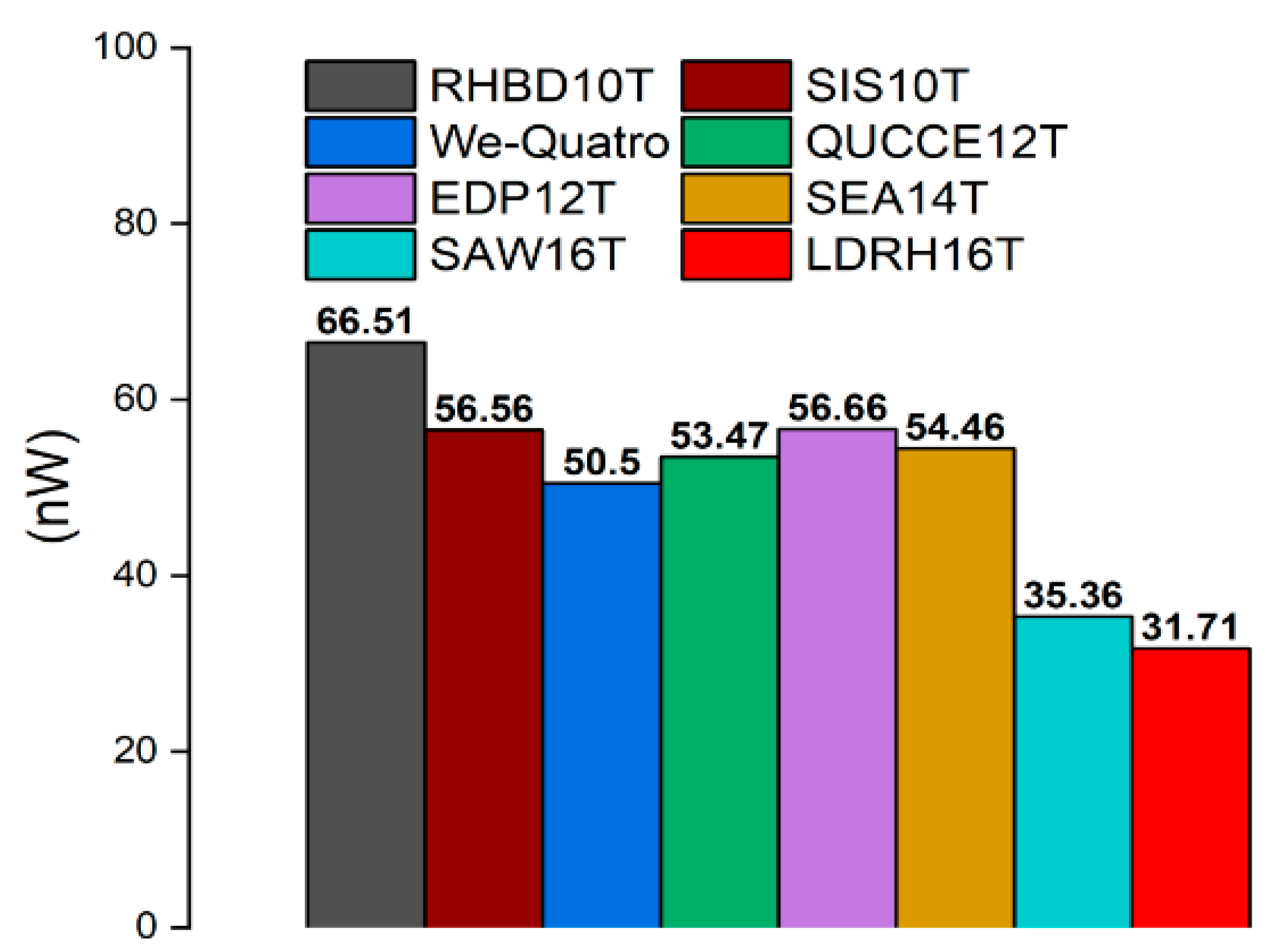

3.4. Hold Power Comparison

3.5. Verification and Comparison of Soft-Error Robustness

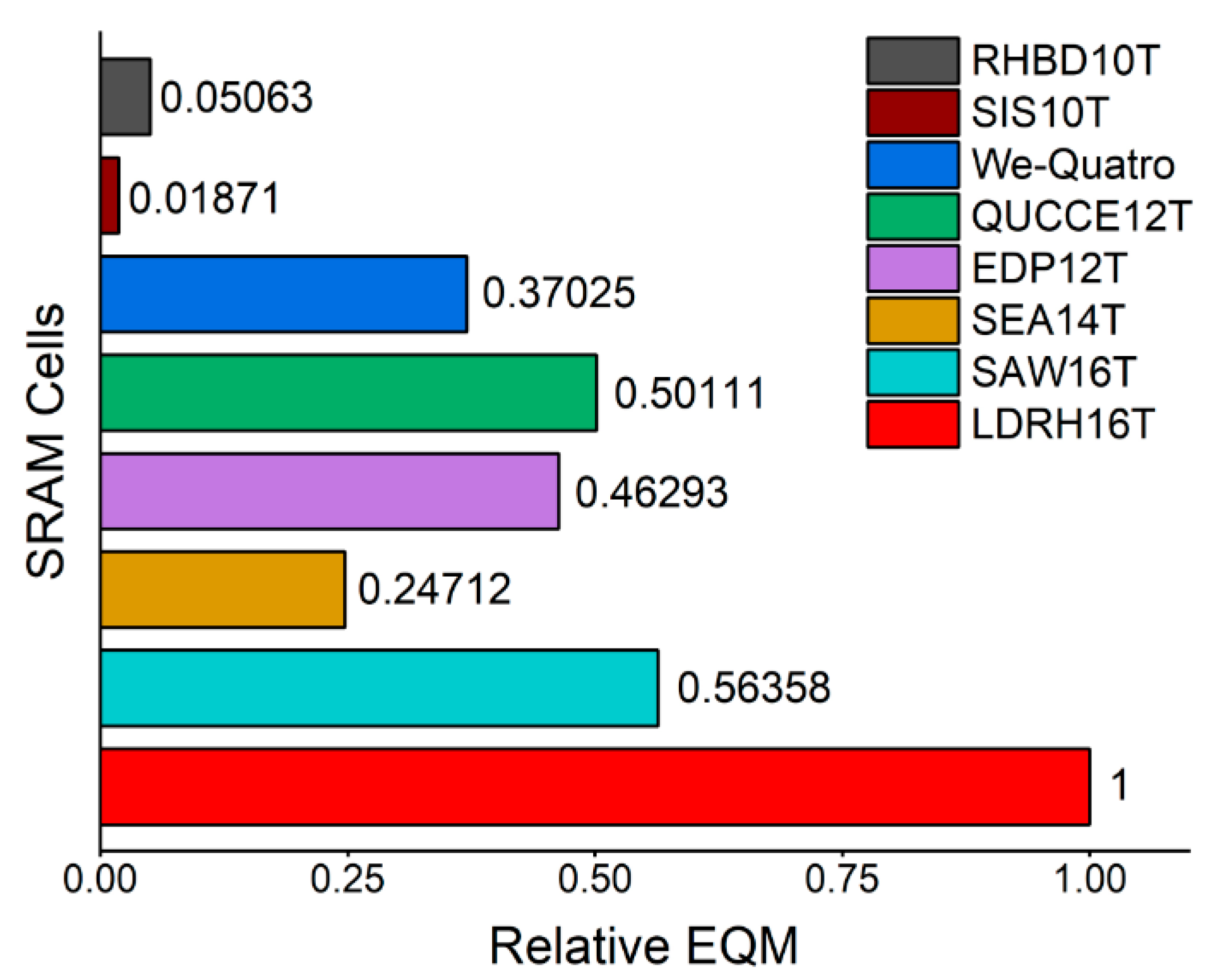

3.6. Electric Quality Metric Comparison

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Pal, S.; Sri, D.D.; Ki, W.-H.; Islam, A. Soft-Error Resilient Read Decoupled SRAM with Multi-Node Upset Recovery for Space Applications. IEEE Trans. Electron Devices 2021, 68, 2246–2254. [Google Scholar] [CrossRef]

- Apollos, E.C. Design Principles of SRAM Memory in Nano-CMOS Technologies. Int. J. Comput. Appl. 2019, 178, 5–11. [Google Scholar]

- De Caro, D.; Di Meo, G.; Napoli, E.; Petra, N.; Strollo, A.G.M. A 1.45 GHz All-Digital Spread Spectrum Clock Generator in 65nm CMOS for Synchronization-Free SoC Applications. IEEE Trans. Circuits Syst. I 2020, 67, 3839–3852. [Google Scholar] [CrossRef]

- Bai, N.; Xiao, X.; Xu, Y.; Wang, Y.; Wang, L.; Zhou, X. Soft-Error-Aware Sram with Multinode Upset Tolerance for Aerospace Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2023, 32, 128–136. [Google Scholar] [CrossRef]

- Amusan, O.A.; Witulski, A.F.; Massengill, L.W.; Bhuva, B.L.; Fleming, P.R.; Alles, M.L.; Sternberg, A.L.; Black, J.D.; Schrimpf, R.D. Charge Collection and Charge Sharing in a 130 Nm CMOS Technology. IEEE Trans. Nucl. Sci. 2006, 53, 3253–3258. [Google Scholar] [CrossRef]

- Chen, Z.; Zhang, M.; Han, W. Design of SEU Tolerant 2D-FFT in SRAM-Based FPGA. In Proceedings of the 2021 IEEE 3rd International Conference on Circuits and Systems (ICCS), Chengdu, China, 29–31 October 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 88–93. [Google Scholar]

- Bajura, M.A.; Boulghassoul, Y.; Naseer, R.; DasGupta, S.; Witulski, A.F.; Sondeen, J.; Stansberry, S.D.; Draper, J.; Massengill, L.W.; Damoulakis, J.N. Models and Algorithmic Limits for an ECC-Based Approach to Hardening Sub-100-Nm SRAMs. IEEE Trans. Nucl. Sci. 2007, 54, 935–945. [Google Scholar] [CrossRef]

- Lyons, R.E.; Vanderkulk, W. The Use of Triple-Modular Redundancy to Improve Computer Reliability. IBM J. Res. Dev. 1962, 6, 200–209. [Google Scholar] [CrossRef]

- Pal, S.; Ki, W.-H.; Tsui, C.-Y. Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM with Multi-Node Upset Recoverability for Aerospace Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 1560–1570. [Google Scholar] [CrossRef]

- Jahinuzzaman, S.M.; Rennie, D.J.; Sachdev, M. A Soft Error Tolerant 10T SRAM Bit-Cell with Differential Read Capability. IEEE Trans. Nucl. Sci. 2009, 56, 3768–3773. [Google Scholar] [CrossRef]

- Kim, J.S.; Chang, I.J. We-Quatro: Radiation-Hardened SRAM Cell with Parametric Process Variation Tolerance. IEEE Trans. Nucl. Sci. 2017, 64, 2489–2496. [Google Scholar]

- Jiang, J.; Xu, Y.; Zhu, W.; Xiao, J.; Zou, S. Quadruple Cross-Coupled Latch-Based 10T and 12T SRAM Bit-Cell Designs for Highly Reliable Terrestrial Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 66, 967–977. [Google Scholar] [CrossRef]

- Dohar, S.S.; Siddharth, R.K.; Vasantha, M.H.; YB, N.K. A 1.2 V, Highly Reliable RHBD 10T SRAM Cell for Aerospace Application. IEEE Trans. Electron Devices 2021, 68, 2265–2270. [Google Scholar] [CrossRef]

- Pal, S.; Sahay, S.; Ki, W.-H.; Tsui, C.-Y. A 10T Soft-Error-Immune SRAM with Multi-Node Upset Recovery for Low-Power Space Applications. IEEE Trans. Device Mater. Reliab. 2022, 22, 85–88. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.-H.; Islam, A. Design of Soft-Error-Aware SRAM with Multi-Node Upset Recovery for Aerospace Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2470–2480. [Google Scholar] [CrossRef]

- Pal, S.; Chowdary, G.; Ki, W.-H.; Tsui, C.-Y. Energy-Efficient Dual-Node-Upset-Recoverable 12T SRAM for Low-Power Aerospace Applications. IEEE Access 2022, 11, 20184–20195. [Google Scholar] [CrossRef]

- Bai, N.; Zhao, W.; Xu, Y.; Wang, Y. A Low-Energy Critical Charge-Enhanced SRAM for Aerospace Applications. In Proceedings of the 2024 IEEE International Test Conference in Asia (ITC-Asia), Changsha, China, 18-20 August 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 1–6. [Google Scholar]

- Oh, J.-Y.; Jo, S.-H. Radiation-Hardened 16T SRAM Cell with Improved Read and Write Stability for Space Applications. Appl. Sci. 2024, 14, 11940. [Google Scholar] [CrossRef]

- Qi, C.; Xiao, L.; Wang, T.; Li, J.; Li, L. A Highly Reliable Memory Cell Design Combined with Layout-Level Approach to Tolerant Single-Event Upsets. IEEE Trans. Device Mater. Reliab. 2016, 16, 388–395. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.-H.; Islam, A. Soft-Error-Aware Read-Decoupled SRAM with Multi-Node Recovery for Aerospace Applications. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 3336–3340. [Google Scholar] [CrossRef]

- Naz, S.F.; Mondal, D.; Shah, A.P. Side-Channel Attack Resilient RHBD 12T SRAM Cell for Secure Nuclear Environment. IEEE Trans. Device Mater. Reliab. 2023, 24, 59–67. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.-H.; Islam, A. Soft-Error-Immune Read-Stability-Improved SRAM for Multi-Node Upset Tolerance in Space Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 3317–3327. [Google Scholar] [CrossRef]

- Chetan, P.C.; Dahiya, P.K. Different Leakage Power Reduction Techniques in SRAM Circuits: A State-of-the-Art Review. Int. Res. J. Eng. Technol. 2017, 4, 742–745. [Google Scholar]

- Mukku, P.K.; Lorenzo, R. A Soft Error Upset Recovery SRAM Cell for Aerospace and Military Applications. In Proceedings of the TENCON 2023—2023 IEEE Region 10 Conference (TENCON), Chiang Mai, Thailand, 31 October–3 November 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 744–749. [Google Scholar]

| Structure | QC (fC) | RAT (ps) | WAT (ps) | RSNM (mV) | WWTV (mV) | HPWR (nW) |

|---|---|---|---|---|---|---|

| RHBD10T [13] | 12.63 | 34.54 | 89.75 | 135 | 179.46 | 66.51 |

| SIS10T [14] | 11 | 38.97 | 86.67 | 50 | 190.45 | 56.56 |

| We-Quatro [11] | 24.27 | 16.56 | 56.57 | 71 | 297.96 | 50.5 |

| QUCCE12T [12] | 28.17 | 15.79 | 58.7 | 89 | 290.36 | 53.47 |

| EDP12T [16] | >150 | 39.35 | 57.19 | 39 | 295.77 | 56.66 |

| SEA14T [15] | >150 | 40.39 | 56.29 | 20 | 298.96 | 54.46 |

| SAW16T [17] | 44.69 | 29.46 | 45.55 | 52 | 337.31 | 35.36 |

| LDRH16T | >150 | 139.81 | 55.75 | 160 | 301.87 | 31.71 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lim, S.-J.; Jo, S.-H. A Low-Power Read-Decoupled Radiation-Hardened 16T SRAM for Space Applications. Appl. Sci. 2025, 15, 6536. https://doi.org/10.3390/app15126536

Lim S-J, Jo S-H. A Low-Power Read-Decoupled Radiation-Hardened 16T SRAM for Space Applications. Applied Sciences. 2025; 15(12):6536. https://doi.org/10.3390/app15126536

Chicago/Turabian StyleLim, Sung-Jun, and Sung-Hun Jo. 2025. "A Low-Power Read-Decoupled Radiation-Hardened 16T SRAM for Space Applications" Applied Sciences 15, no. 12: 6536. https://doi.org/10.3390/app15126536

APA StyleLim, S.-J., & Jo, S.-H. (2025). A Low-Power Read-Decoupled Radiation-Hardened 16T SRAM for Space Applications. Applied Sciences, 15(12), 6536. https://doi.org/10.3390/app15126536