Simulation Modelling of Silicon Gated Field Emitter Based Electronic Circuits

Abstract

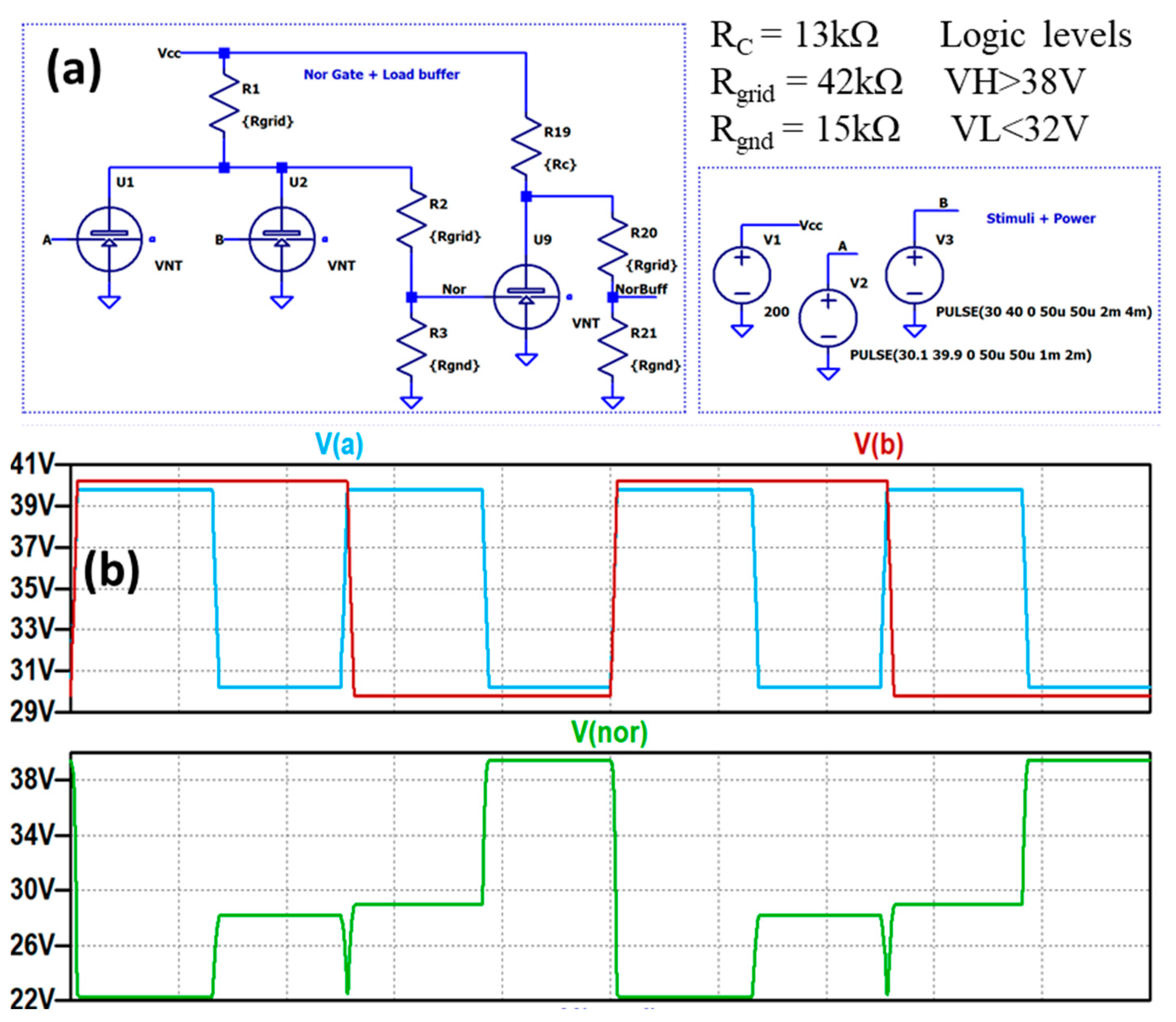

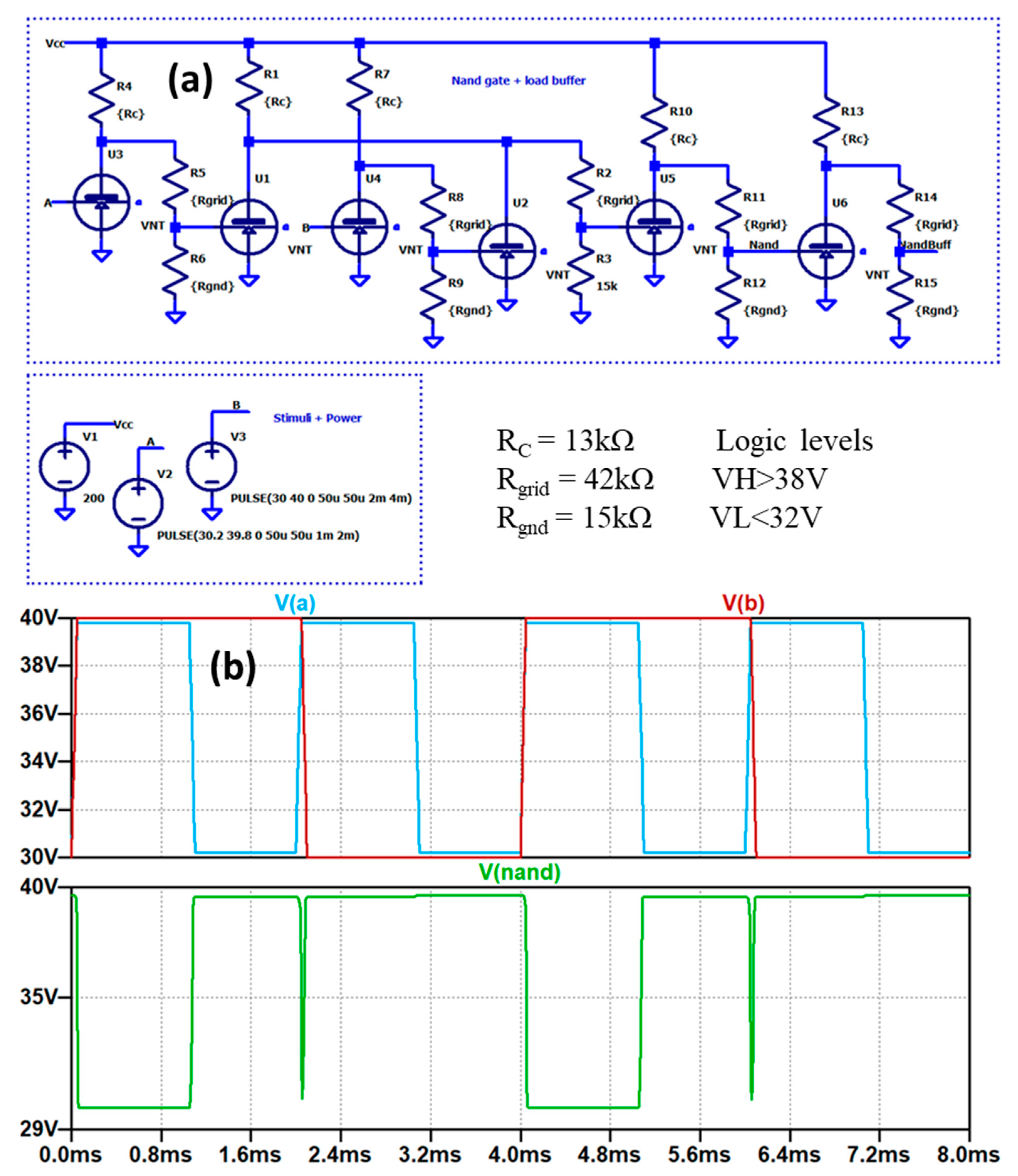

:1. Introduction

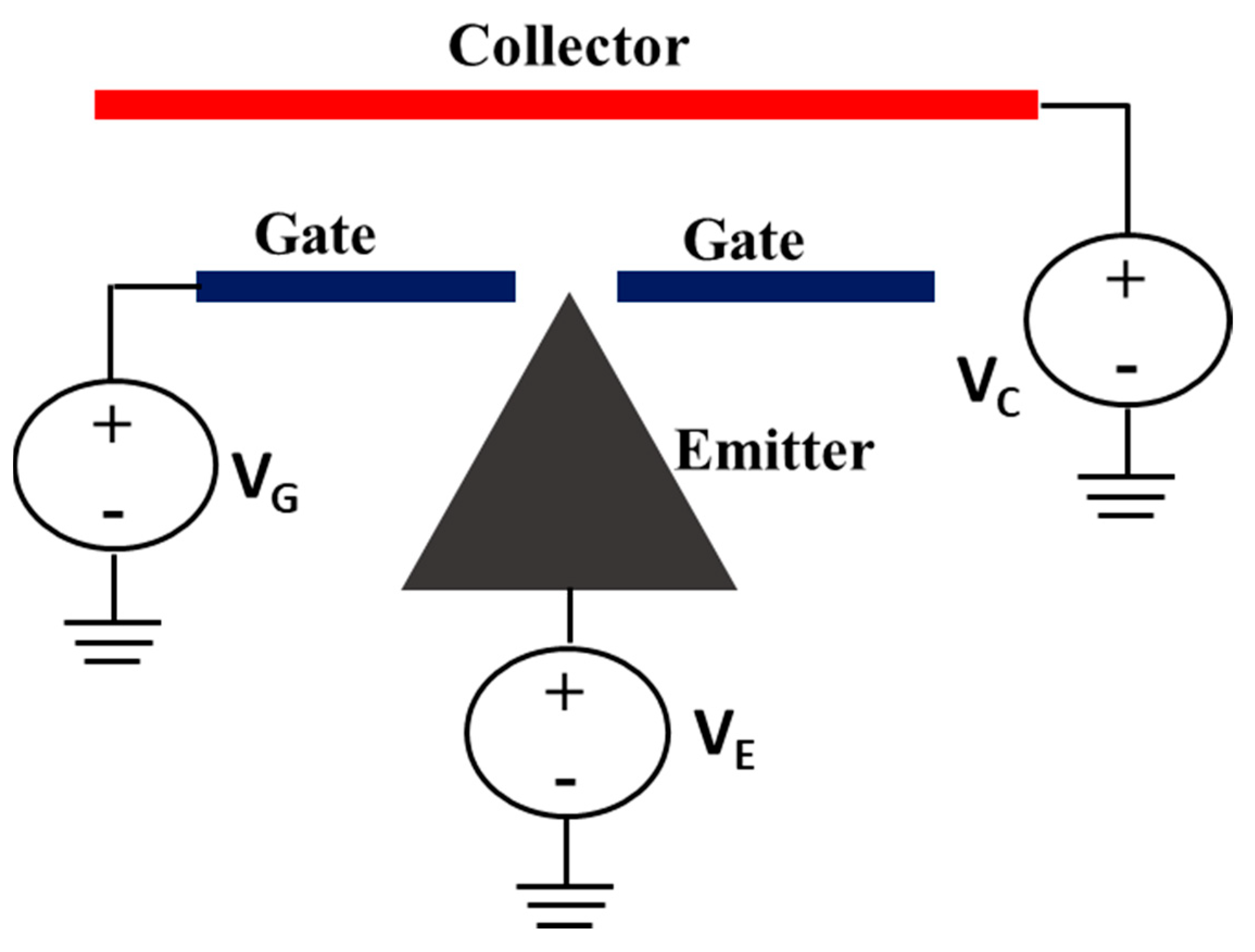

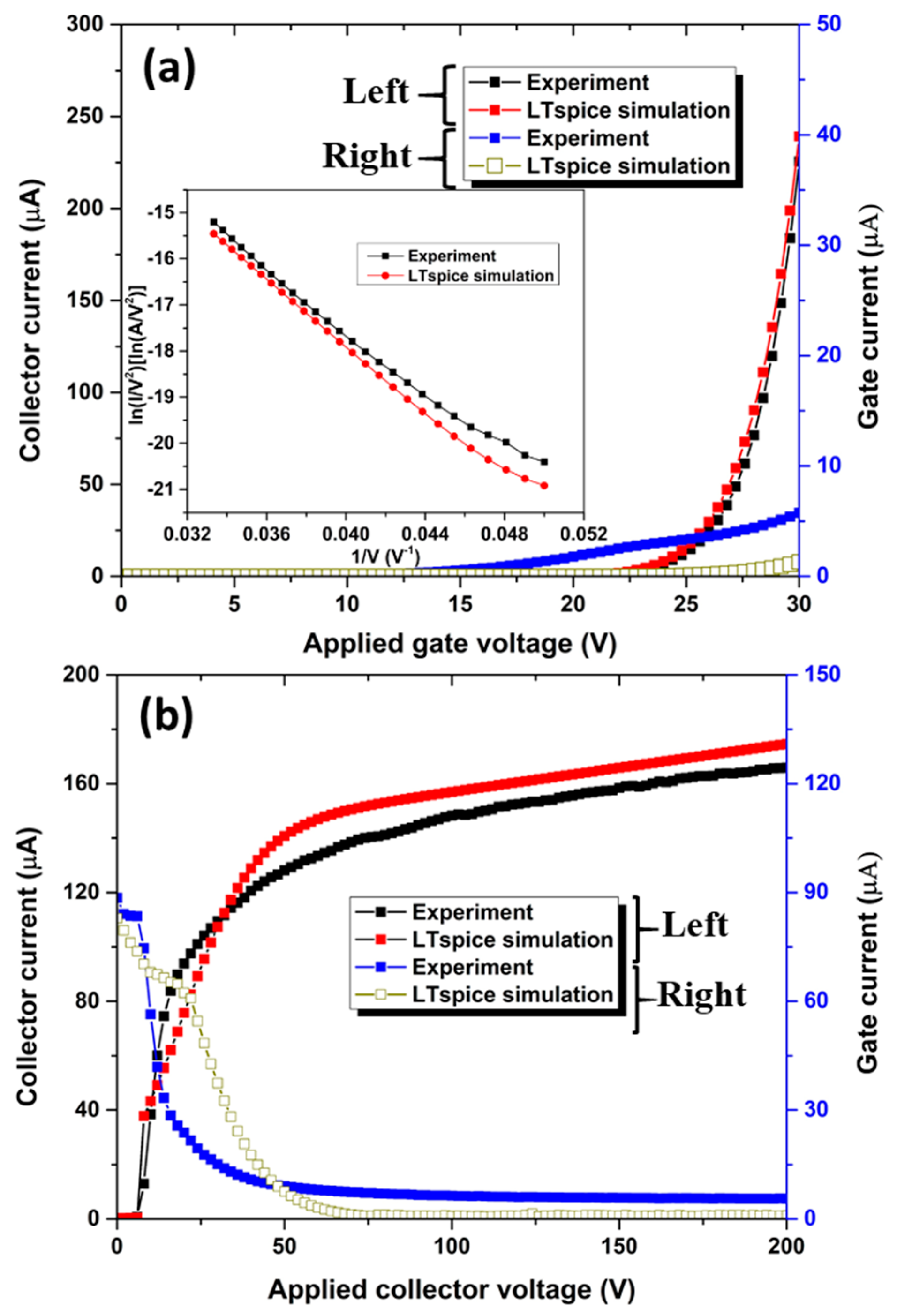

2. I-V Characterization Experiment

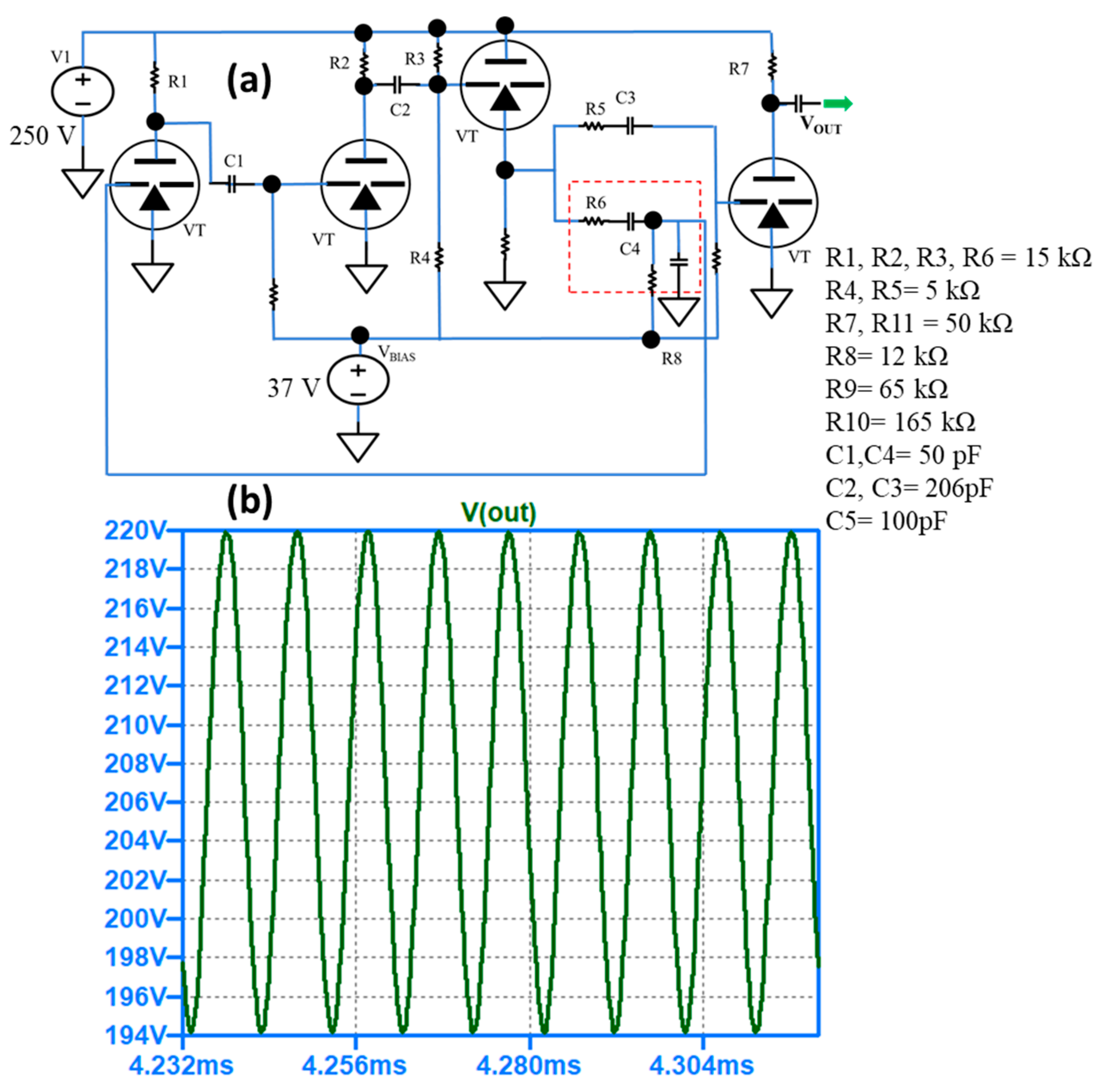

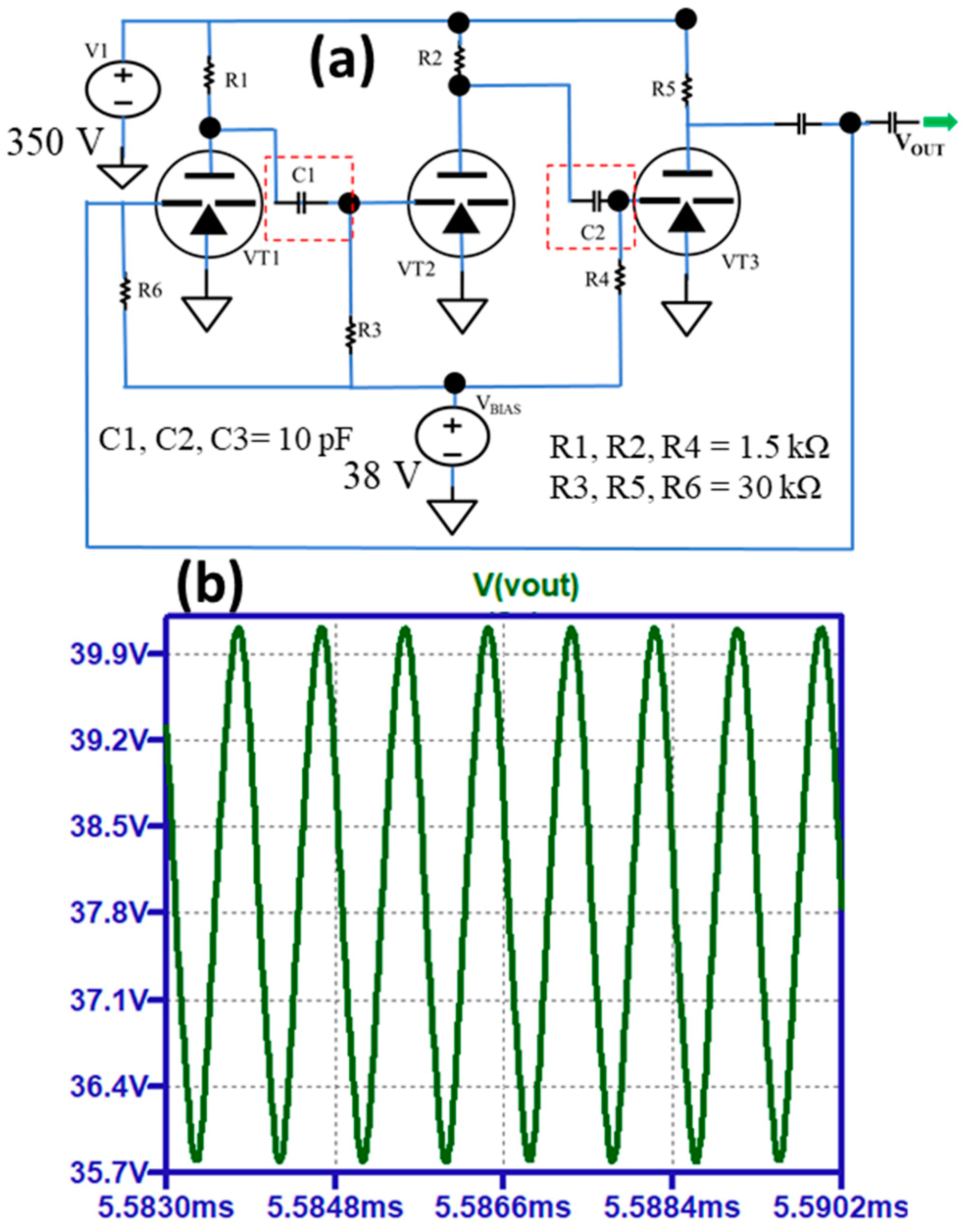

3. Simulation Model

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Han, J.-W.; Moon, D.-I.; Meyyappan, M. Nanoscale Vacuum Channel Transistor. Nano Lett. 2017, 17, 2146–2151. [Google Scholar] [CrossRef] [PubMed]

- Han, J.-W.; Sub Oh, J.; Meyyappan, M. Vacuum Nanoelectronics: Back to the Future?—Gate Insulated Nanoscale Vacuum Channel Transistor. Appl. Phys. Lett. 2012, 100, 213505. [Google Scholar] [CrossRef]

- Injo, O.; Lee, C.; Seo, S.-C.; Kim, S. Vertical Vacuum Channel Transistor with Minimized Air Gap between Tip and Gate 2019. U.S. Patent US10431682B2, 23 April 2019. [Google Scholar]

- Park, I.J.; Jeon, S.-G.; Shin, C. A New Slit-Type Vacuum-Channel Transistor. IEEE Trans. Electron Devices 2014, 61, 4186–4191. [Google Scholar] [CrossRef]

- Srisonphan, S.; Jung, Y.S.; Kim, H.K. Metal–Oxide–Semiconductor Field-Effect Transistor with a Vacuum Channel. Nat. Nanotechnol. 2012, 7, 504. [Google Scholar] [CrossRef] [PubMed]

- Guerrera, S.; Akinwande, A.I. Nanofabrication of Arrays of Silicon Field Emitters with Vertical Silicon Nanowire Current Limiters and Self-Aligned Gates. Nanotechnology 2016, 27, 295302. [Google Scholar] [CrossRef] [PubMed]

- Bhattacharya, R.; Karaulac, N.; Chern, W.; Akinwande, A.; Browning, J. Temperature Effects on Gated Silicon Field Emission Array Performance. J. Vac. Sci. Technol. B 2021, 39, 023201. [Google Scholar] [CrossRef]

- Davidson, J.L.; Kang, W.P.; Subramanian, K.; Holmes-Siedle, A.G.; Reed, R.A.; Galloway, K.F. Diamond Vacuum Electronic Device Behavior after High Neutron Fluence Exposure. IEEE Trans. Nucl. Sci. 2009, 56, 2225–2229. [Google Scholar] [CrossRef]

- Kang, W.; Davidson, J.; Subramanian, K.; Choi, B.; Galloway, K. Nanodiamond Lateral VFEM Technology for Harsh Environments. IEEE Trans. Nucl. Sci. 2007, 54, 1061–1065. [Google Scholar] [CrossRef]

- Han, J.-W.; Oh, J.S.; Meyyappan, M. Cofabrication of Vacuum Field Emission Transistor (VFET) and MOSFET. IEEE Trans. Nanotechnol. 2014, 13, 464–468. [Google Scholar] [CrossRef]

- Fowler, R.H.; Nordheim, L. Electron Emission in Intense Electric Fields. Proc. R. Soc. London. Ser. A Contain. Pap. A Math. Phys. Character 1928, 119, 173–181. [Google Scholar]

- Han, J.-W.; Seol, M.-L.; Moon, D.-I.; Hunter, G.; Meyyappan, M. Nanoscale Vacuum Channel Transistors Fabricated on Silicon Carbide Wafers. Nat. Electron. 2019, 2, 405–411. [Google Scholar] [CrossRef]

- Ding, M.; Sha, G.; Akinwande, A.I. Silicon Field Emission Arrays with Atomically Sharp Tips: Turn-on Voltage and the Effect of Tip Radius Distribution. IEEE Trans. Electron Devices 2002, 49, 2333–2342. [Google Scholar] [CrossRef]

- Guerrera, S.A.; Akinwande, A.I. Silicon Field Emitter Arrays with Current Densities Exceeding 100 A/cm2 at Gate Voltages below 75 V. IEEE Electron Device Lett. 2015, 37, 96–99. [Google Scholar] [CrossRef]

- Kim, D.Y.; Kim, H.T. Vacuum Channel Transistor and Diode Emitting Thermal Cathode Electrons, and Method of Manufacturing the Vacuum Channel Transistor 2012. U.S. Patent US8159119B2, 17 April 2012. [Google Scholar]

- Schaller, R.R. Moore’s Law: Past, Present and Future. IEEE Spectr. 1997, 34, 52–59. [Google Scholar] [CrossRef]

- Bhattacharya, R.; Hay, R.; Cannon, M.; Karaulac, N.; Rughoobur, G.; Akinwande, A.I.; Browning, J. Demonstration of a Silicon Gated Field Emitter Array Based Low Frequency Colpitts Oscillator at 400 °C. J. Vac. Sci. Technol. B 2023, 41, 023201. [Google Scholar] [CrossRef]

- Xu, J.; Qin, Y.; Shi, Y.; Shi, Y.; Yang, Y.; Zhang, X. Design and Circuit Simulation of Nanoscale Vacuum Channel Transistors. Nanoscale Adv. 2020, 2, 3582–3587. [Google Scholar] [CrossRef]

- Bhattacharya, R.; Karaulac, N.; Rughoobur, G.; Chern, W.; Akinwande, A.I.; Browning, J. Ultraviolet Light Stimulated Water Desorption Effect on Emission Performance of Gated Field Emitter Array. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2021, 39, 033201. [Google Scholar] [CrossRef]

- Murphy, E.L.; Good Jr, R. Thermionic Emission, Field Emission, and the Transition Region. Phys. Rev. 1956, 102, 1464. [Google Scholar] [CrossRef]

- Jensen, K.L. Improved Fowler–Nordheim Equation for Field Emission from Semiconductors. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 1995, 13, 516–521. [Google Scholar] [CrossRef]

- Forbes, R.G. Renewing the Mainstream Theory of Field and Thermal Electron Emission. In Modern Developments in Vacuum Electron Sources; Springer: Berlin/Heidelberg, Germany, 2020; pp. 387–447. [Google Scholar]

- Holt, A.; Lee, M. A Class of RC Oscillators. Proc. IEEE 1967, 55, 1119. [Google Scholar] [CrossRef]

- Senani, R. New Types of Sinewave Oscillators. IEEE Trans. Instrum. Meas. 1985, IM-34, 461–463. [Google Scholar] [CrossRef]

- Hoffmann, K. Applying the Wheatstone Bridge Circuit; HBM: Darmstadt, Germany, 1974. [Google Scholar]

- Lee, S.-J.; Kim, B.; Lee, K. A Novel High-Speed Ring Oscillator for Multiphase Clock Generation Using Negative Skewed Delay Scheme. IEEE J. Solid-State Circuits 1997, 32, 289–291. [Google Scholar]

- Gate, B.N.; Gate, G.N.; Upper, U.I.L.I.O.; Gate, O.; Gate, N.; Gate, X.; Gate, X. Introduction to Digital Logic Design; University of California San Diego: La Jolla, CA, USA, 1993. [Google Scholar]

- Alipour-Banaei, H.; Serajmohammadi, S.; Mehdizadeh, F. All Optical NOR and NAND Gate Based on Nonlinear Photonic Crystal Ring Resonators. Optik 2014, 125, 5701–5704. [Google Scholar] [CrossRef]

- haq Shaik, E.; Rangaswamy, N. Realization of All-Optical NAND and NOR Logic Functions with Photonic Crystal Based NOT, OR and AND Gates Using De Morgan’s Theorem. J. Opt. 2018, 47, 8–21. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hay, R.; Bhattacharya, R.; Chern, W.; Rughoobur, G.; Akinwande, A.I.; Browning, J. Simulation Modelling of Silicon Gated Field Emitter Based Electronic Circuits. Appl. Sci. 2023, 13, 12807. https://doi.org/10.3390/app132312807

Hay R, Bhattacharya R, Chern W, Rughoobur G, Akinwande AI, Browning J. Simulation Modelling of Silicon Gated Field Emitter Based Electronic Circuits. Applied Sciences. 2023; 13(23):12807. https://doi.org/10.3390/app132312807

Chicago/Turabian StyleHay, Robert, Ranajoy Bhattacharya, Winston Chern, Girish Rughoobur, Akintunde I. Akinwande, and Jim Browning. 2023. "Simulation Modelling of Silicon Gated Field Emitter Based Electronic Circuits" Applied Sciences 13, no. 23: 12807. https://doi.org/10.3390/app132312807

APA StyleHay, R., Bhattacharya, R., Chern, W., Rughoobur, G., Akinwande, A. I., & Browning, J. (2023). Simulation Modelling of Silicon Gated Field Emitter Based Electronic Circuits. Applied Sciences, 13(23), 12807. https://doi.org/10.3390/app132312807