The Research on the Signal Generation Method and Digital Pre-Processing Based on Time-Interleaved Digital-to-Analog Converter for Analog-to-Digital Converter Testing

Abstract

:1. Introduction

2. Related Works and Problems

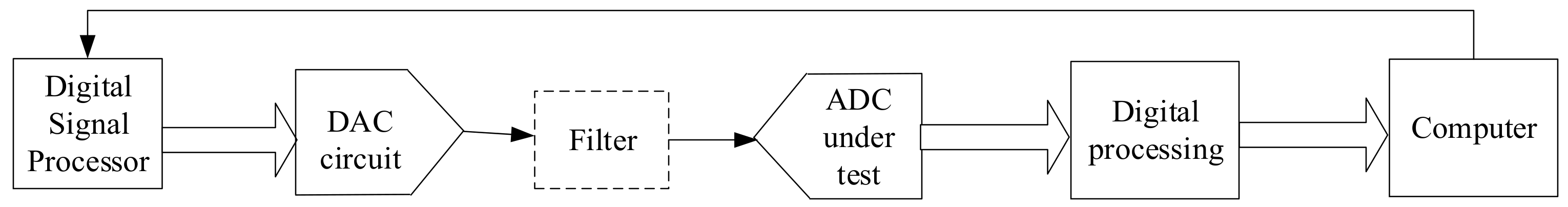

3. Signal Generation Method and Circuit Design Based on Time-Interleaving

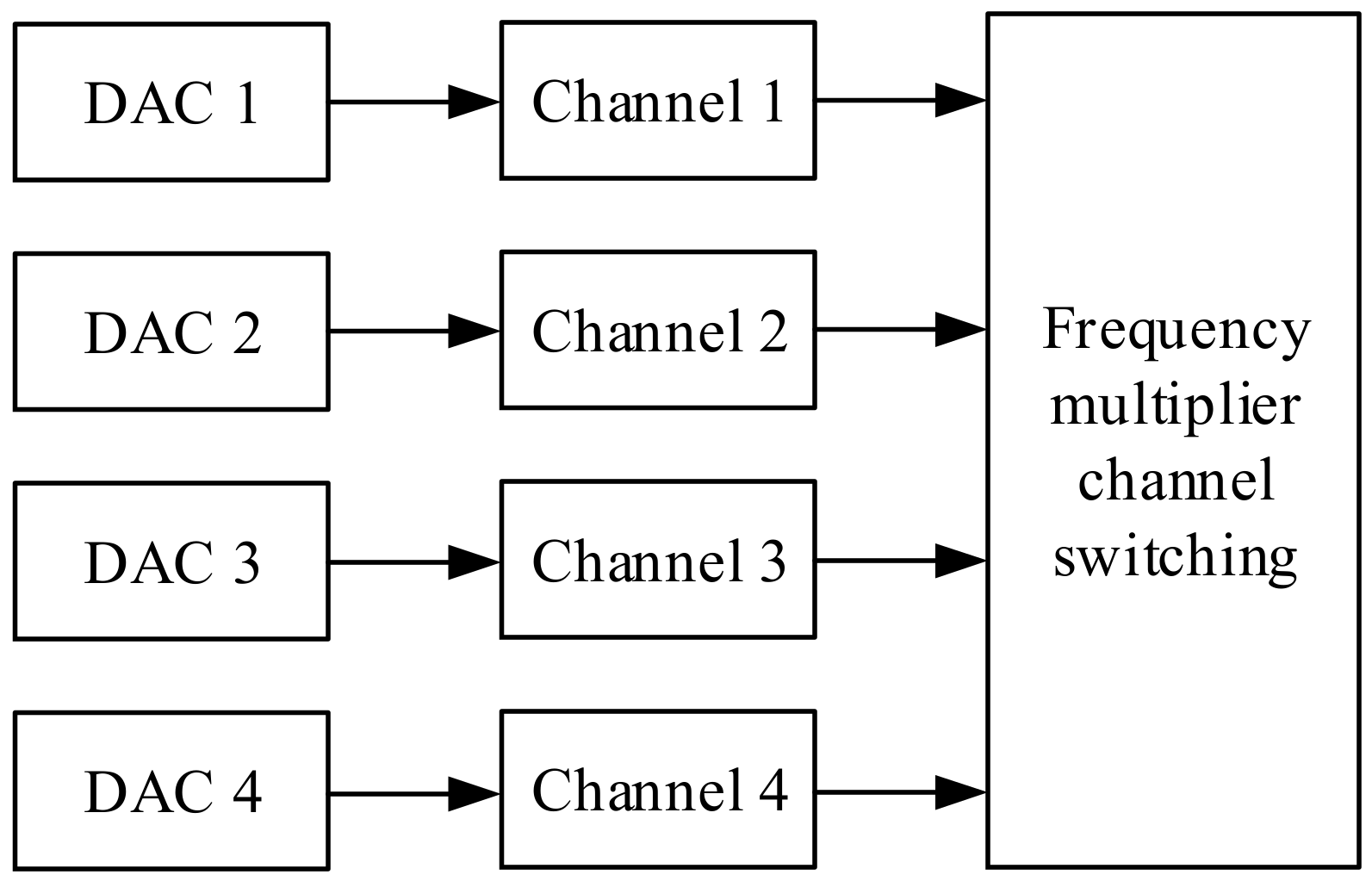

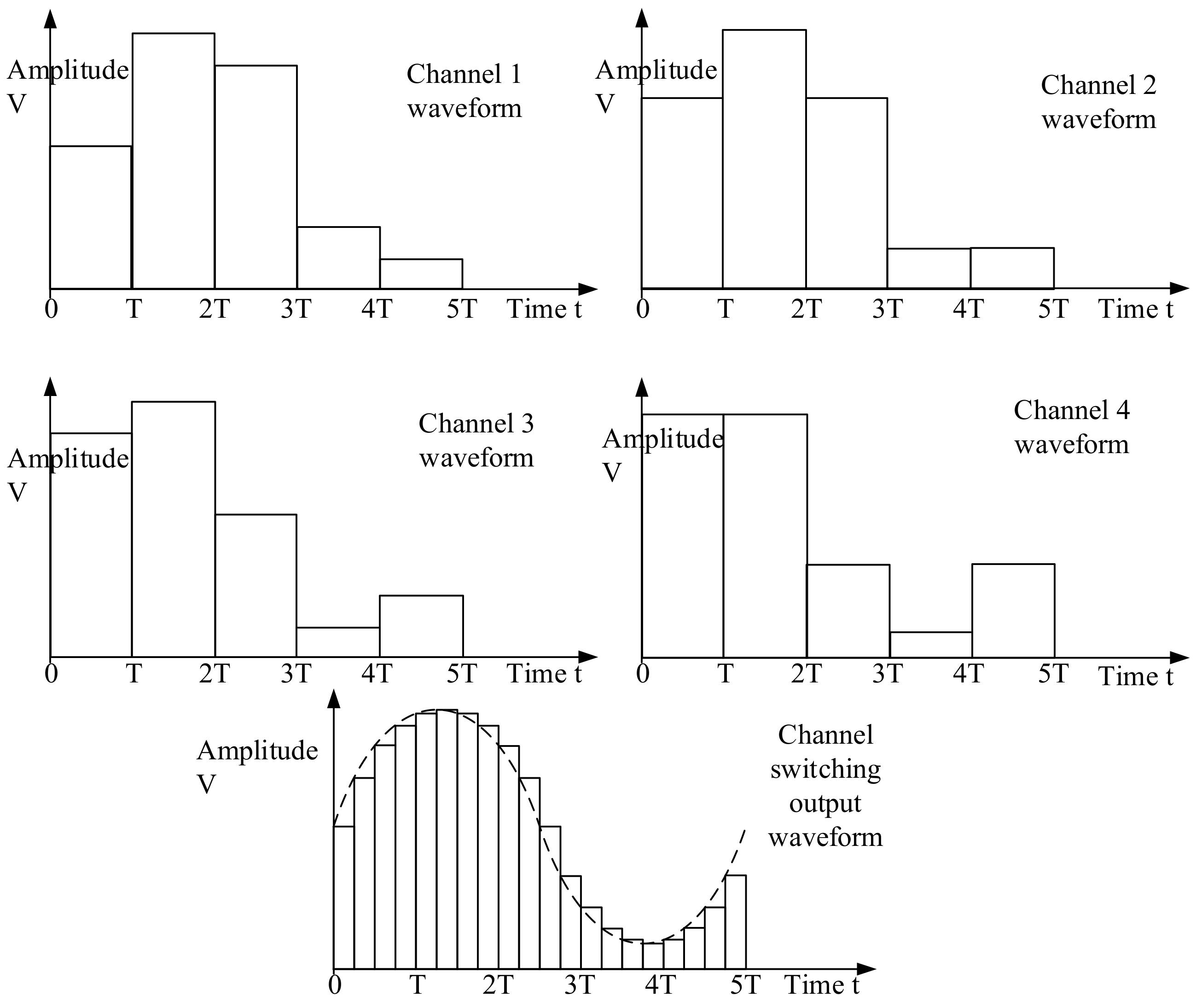

3.1. Signal Generation Method Based on TIDAC

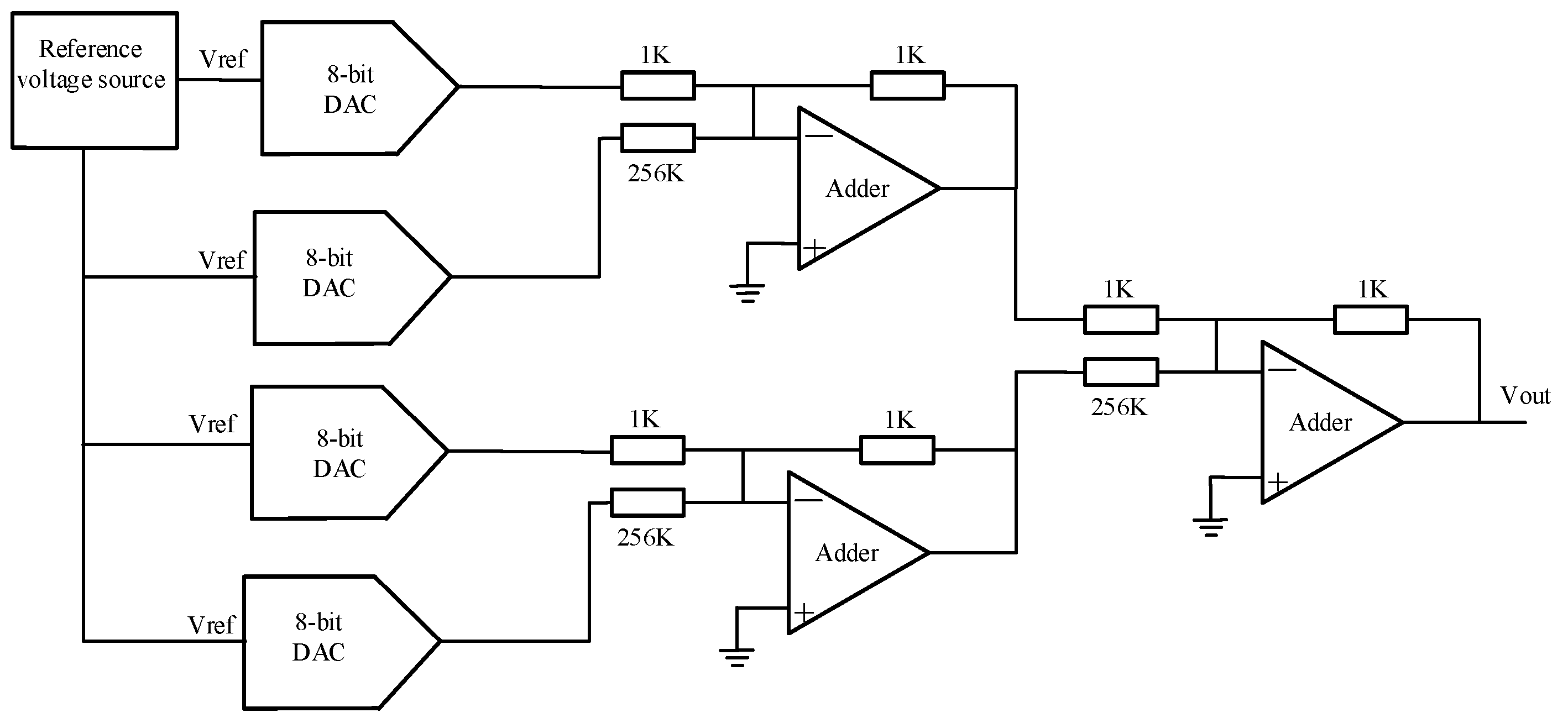

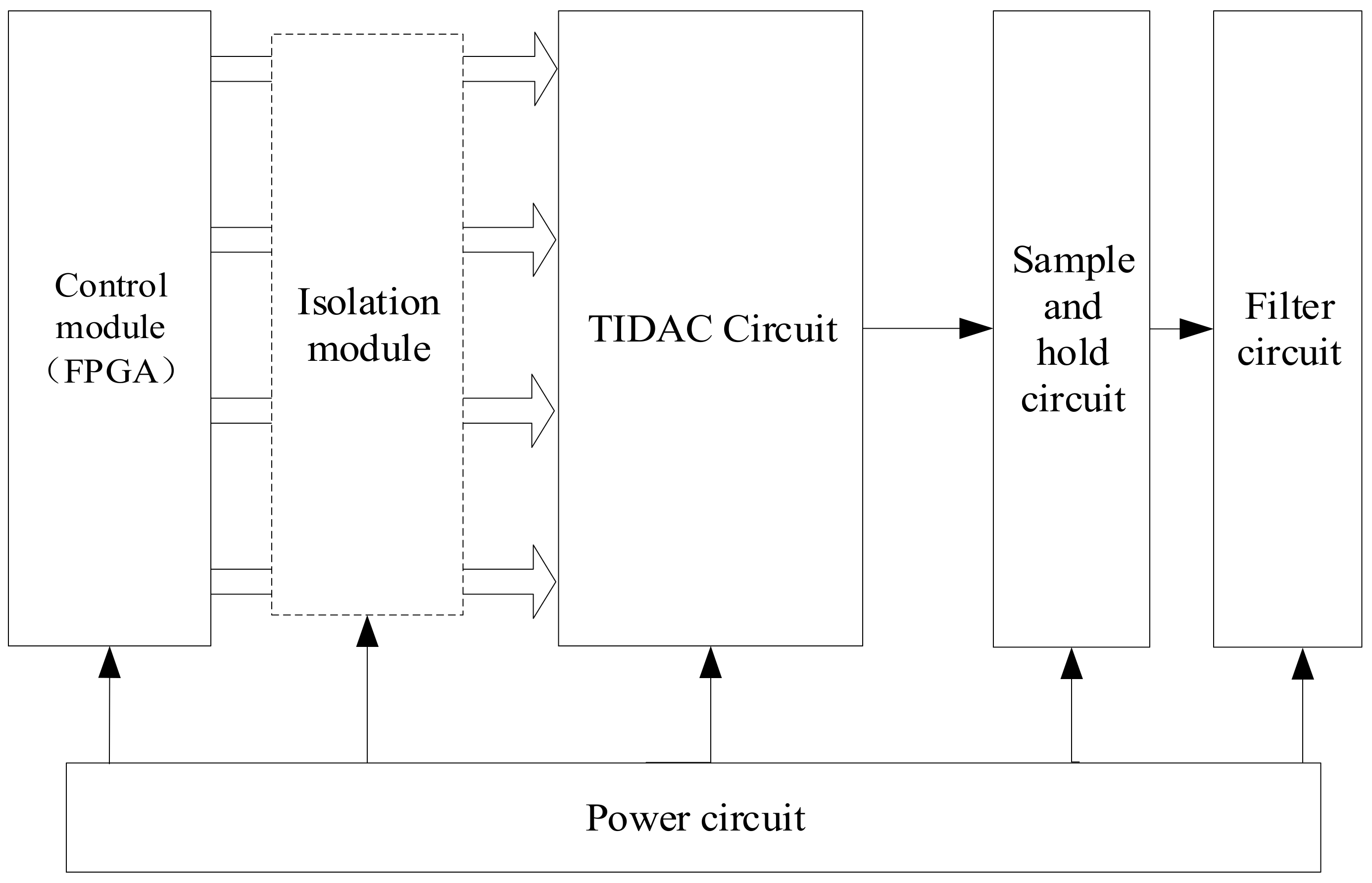

3.2. Circuit Design

4. Error Analysis and Processing

4.1. Amplitude Error Analysis and Digital Pre-Processing

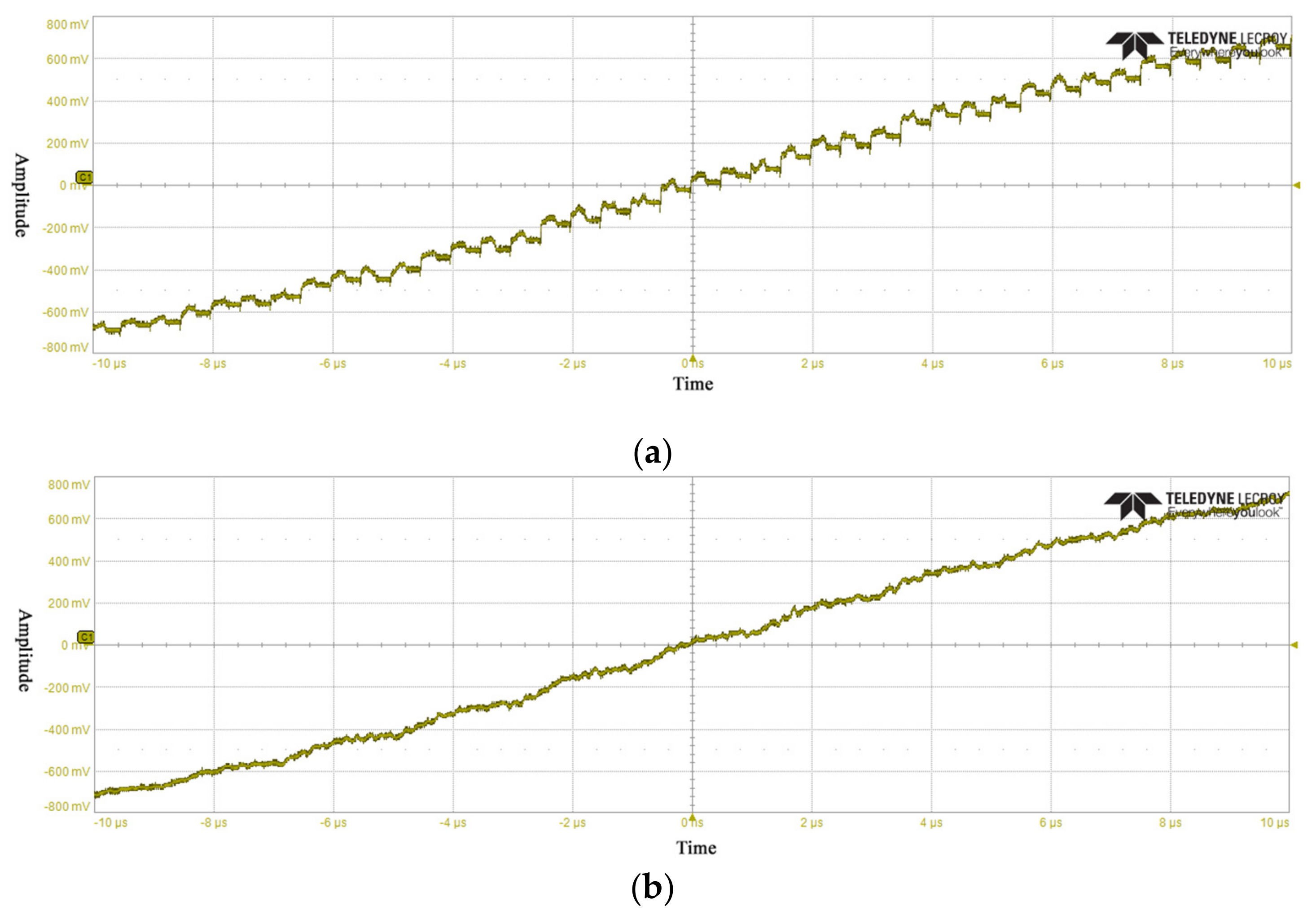

4.2. Time Error Analysis and Digital Pre-Processing

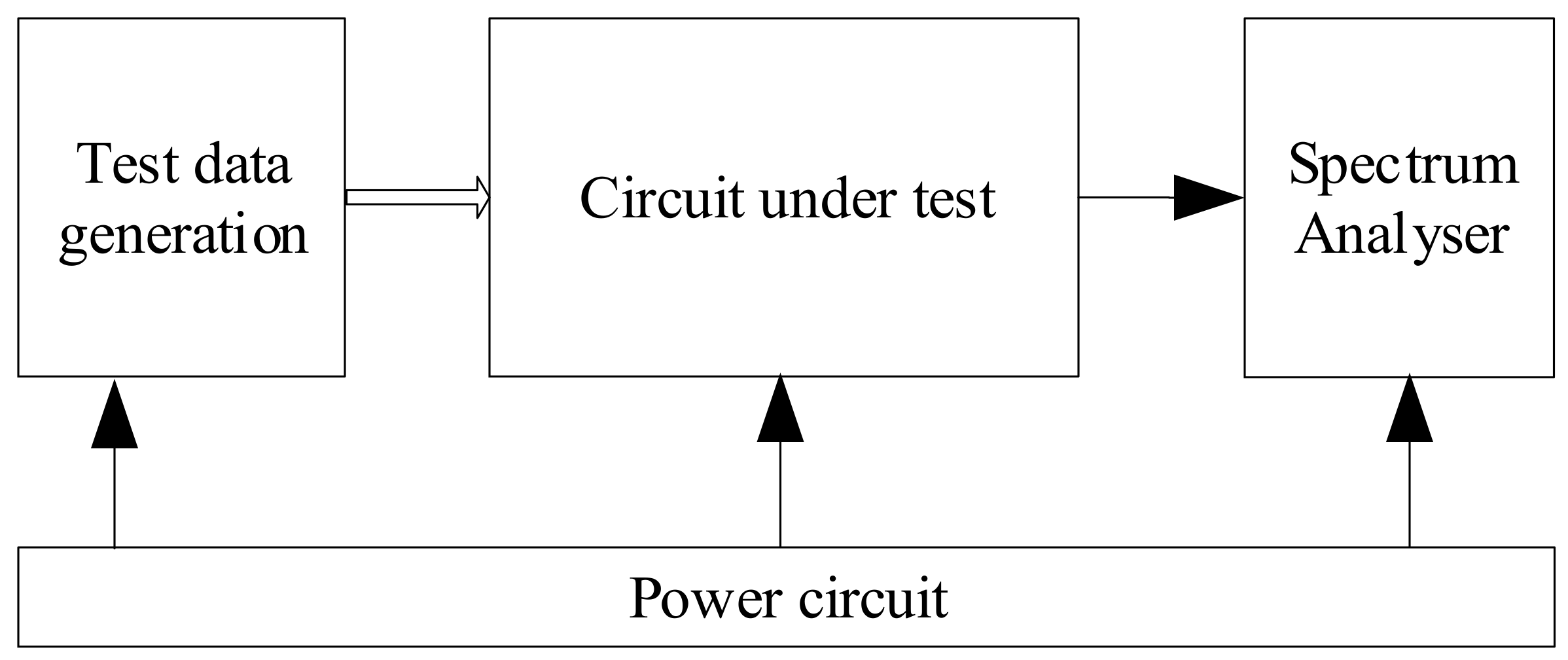

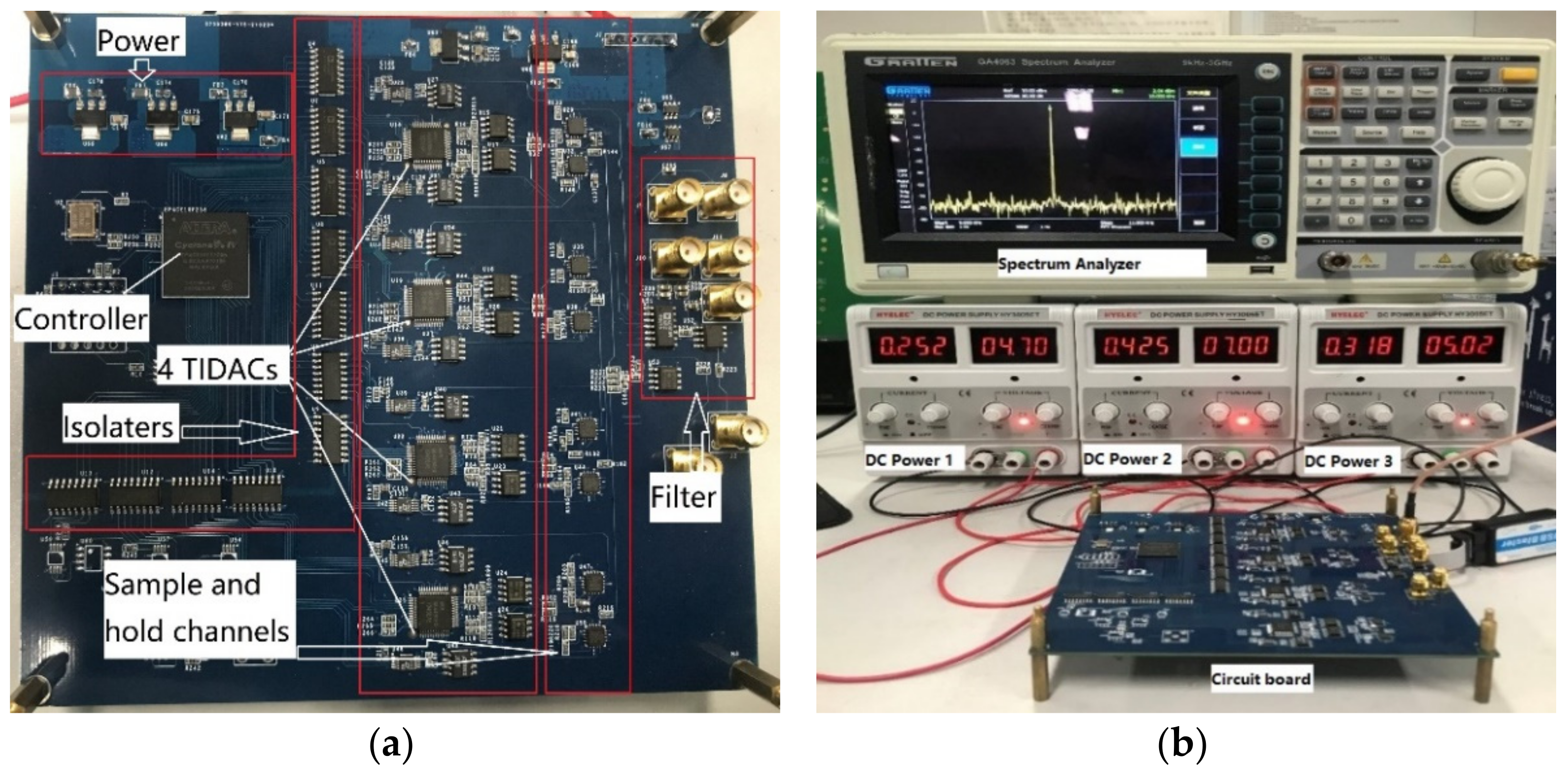

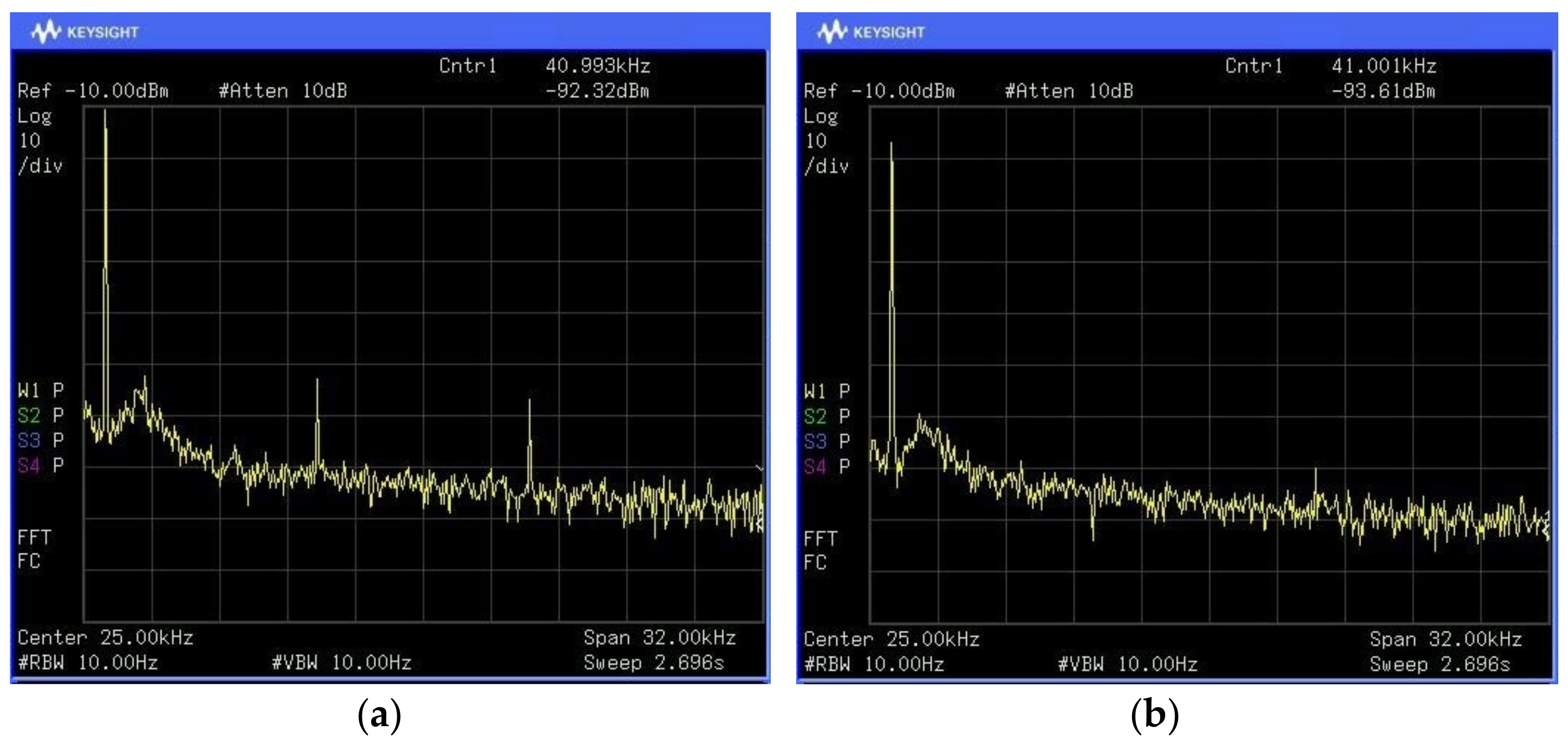

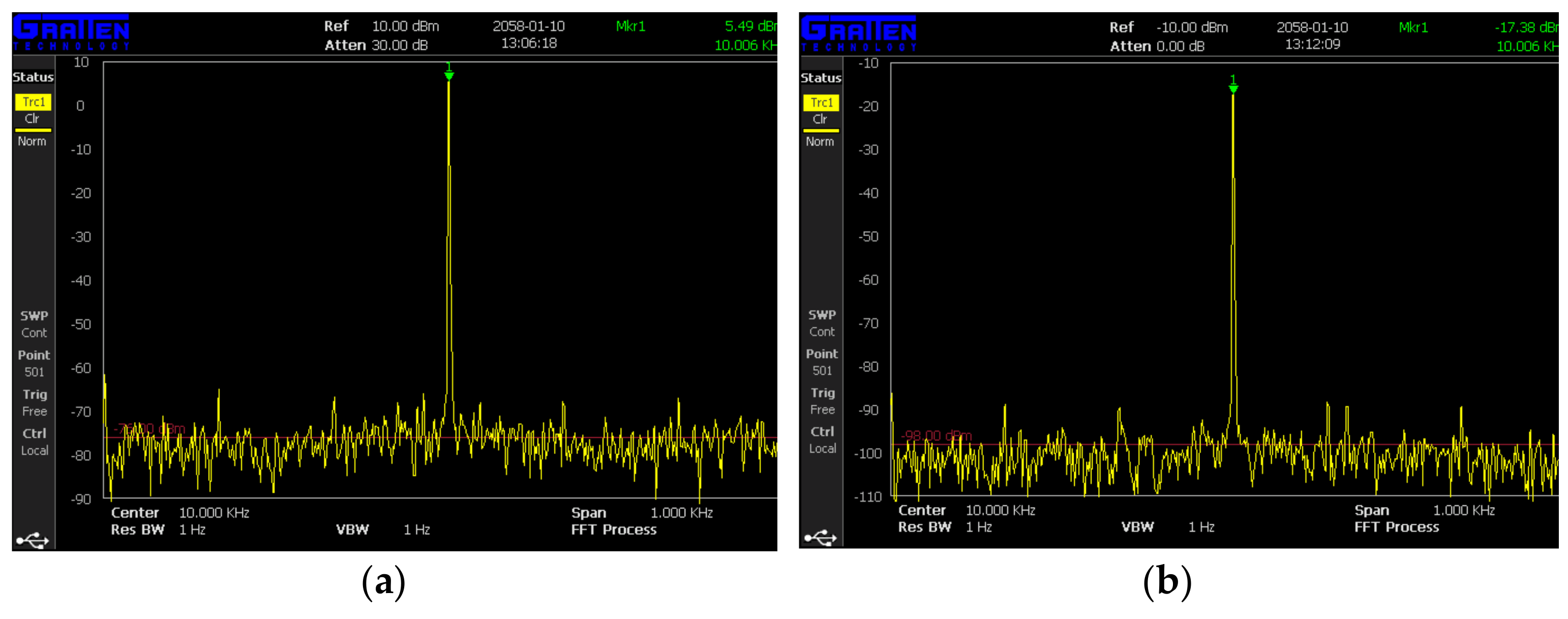

5. Test Results and Analyses

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Li, G.; Ou, B.; Shi, H. A Review of the Development of Modern Analog Circuit Fault Diagnosis Technology. Comput. Meas. Control 2019, 27, 5–8. [Google Scholar] [CrossRef]

- Liu, G. The first IC testing technology forum was successfully held in Beijing. Semicond. Inf. 2008, 6, 78. [Google Scholar]

- Long, T. Research on Test Generation and Fault Diagnosis of Analog Circuits; University of Electronic Science and Technology of China: Chengdu, China, 2011. [Google Scholar]

- Fu, W. Design of Time Parameter and DC Parameter Measurement Unit in IC Test System; University of Electronic Science and Technology of China: Chengdu, China, 2013; pp. 15–18. [Google Scholar]

- Tan, L.; Fang, Y. The Research of IC Test Based on LTX-77 Test System. Appl. Mech. Mater. 2014, 496–500, 1176–1179. [Google Scholar] [CrossRef]

- Zhang, J.; Wang, J.; Hou, L.; Gong, N. Reusable IO technique for improved utility of IC test circuit area. In Proceedings of the 2015 IEEE 11th International Conference on ASIC (ASICON), Chengdu, China, 3–6 November 2015; pp. 1–5. [Google Scholar]

- Tektronix. AWG5200 Series Arbitrary Waveform Generators. Available online: https://www.tek.com/arbitrary-waveform-generator/awg5200 (accessed on 4 February 2022).

- NI, The PXIe-54x3 Arbitrary Waveform Generator Family. Available online: https://www.ni.com/zh-cn/innovations/white-papers/17/the-pxie-54x3-arbitrary-waveform-generator-family.html (accessed on 4 February 2022).

- Applicos, PG24192 PXI Dual channel 24-bit / 192ksps Arbitrary Waveform Generator. Available online: https://www.cnrood.com/en/pg24192 (accessed on 4 February 2022).

- IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters in IEEE Std 1241-2010 (Revision of IEEE Std 1241-2000); IEEE: Piscataway, NJ, USA, 2011; pp. 1–139. [CrossRef]

- He, H. Research and Realization of High-Resolution and High-Speed DA Conversion Circuit; University of Electronic Science and Technology of China: Chengdu, China, 2019. [Google Scholar]

- Balasubramanian, S.; Creech, G.; Wilson, J.; Yoder, S.M.; McCue, J.J.; Verhelst, M.; Khalil, W. Systematic Analysis of Interleaved Digital-to-Analog Converters. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 882–886. [Google Scholar] [CrossRef]

- Zhang, J.; Zheng, Z.; Chen, P. Design of 20 bit resolution using 16 bit DAC. Electron. Prod. 2003, 12, 17–18. [Google Scholar] [CrossRef]

- Song, F.; Gu, M.; Yang, Z. Realize 32-bit D/A high resolution with DAC0832 chip. Microcomput. Inf. 2007, 23, 293–294. [Google Scholar]

- Jia, L.; He, Z.; Zeng, D. Measurement of resistance thermal noise based on digital phase locked amplifier. Phys. Exp. 2018, 38, 1–5. [Google Scholar] [CrossRef]

- Gao, J.; Ye, P.; Zeng, H. An adaptive calibration technique of timing skew mismatch in time-interleaved analog-to-digital converters. Rev. Sci. Instrum. 2019, 90, 025102. [Google Scholar] [CrossRef]

- Zeng, H. Research and Design of 1GHz Broadband Low Noise Analog Channel; University of Electronic Science and Technology: Chengdu, China, 2017. [Google Scholar]

- Mou, F. Design and Application of Reference Source with Low Temperature Coefficient and High Power Suppression; University of Electronic Science and technology: Chengdu, China, 2010. [Google Scholar] [CrossRef]

- An, C. Design of Self-Adjusting Bipolar Voltage Source DAC; Xiangtan University: Xiangtan, China, 2012. [Google Scholar] [CrossRef]

- Zheng, Y.; Yao, X.; Guo, H.; Bao, D.; Wang, Y. Research on resistance noise characteristics based on digital phase locked amplifier. Phys. Exp. 2021, 41, 11–18. [Google Scholar] [CrossRef]

- Zhang, J.; Zhang, L.; Wang, Z.; Huang, M.; Zhao, Z. Noise analysis and disposal of preamplifier circuit of vortex flowmeter. Ind. Technol. Innov. 2021, 8, 132–134 + 144. [Google Scholar] [CrossRef]

- Sun, Y.; Li, X.; Ma, X. Several techniques for improving circuit reliability. J. Hebei Univ. Sci. Technol. 2002, 23, 41–44. [Google Scholar] [CrossRef]

- Ying, J.; Liu, Q. Linear error analysis method of voltage source R-2R ladder network DAC. Microelectronics 2006, 36, 257–260. [Google Scholar] [CrossRef]

- Shang, J. Analysis of the Dynamic Range of Spectrum Analyzer. China Radio 2005, 10, 37–41. [Google Scholar] [CrossRef]

| Number | Frequency (Hz) | Single DAC Circuit Test Results | TIDAC Circuit Test Results | ||||

|---|---|---|---|---|---|---|---|

| Signal Power (dBm) | Noise Power (dBm) | SNR (dB) | Signal Power (dBm) | Noise Power (dBm) | SNR (dB) | ||

| 1 | 9 K | 5.35 | −101.00 | 106.35 | 5.50 | −99.00 | 104.50 |

| 2 | 10 K | 5.32 | −99.00 | 104.32 | 5.49 | −98.00 | 103.49 |

| 3 | 50 K | 5.30 | −97.00 | 102.30 | 5.49 | −97.00 | 102.49 |

| 4 | 100 K | 4.47 | −92.00 | 96.47 | 5.49 | −95.00 | 100.49 |

| 5 | 150 K | 1.23 | −90.00 | 91.23 | 5.24 | −93.00 | 98.24 |

| 6 | 200 K | 0.59 | −89.00 | 89.59 | 4.09 | −91.00 | 95.09 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, L.; Chen, W.; Chen, K.; He, R.; Zhou, W. The Research on the Signal Generation Method and Digital Pre-Processing Based on Time-Interleaved Digital-to-Analog Converter for Analog-to-Digital Converter Testing. Appl. Sci. 2022, 12, 1704. https://doi.org/10.3390/app12031704

Wang L, Chen W, Chen K, He R, Zhou W. The Research on the Signal Generation Method and Digital Pre-Processing Based on Time-Interleaved Digital-to-Analog Converter for Analog-to-Digital Converter Testing. Applied Sciences. 2022; 12(3):1704. https://doi.org/10.3390/app12031704

Chicago/Turabian StyleWang, Li, Wenli Chen, Kai Chen, Renjun He, and Wenjian Zhou. 2022. "The Research on the Signal Generation Method and Digital Pre-Processing Based on Time-Interleaved Digital-to-Analog Converter for Analog-to-Digital Converter Testing" Applied Sciences 12, no. 3: 1704. https://doi.org/10.3390/app12031704

APA StyleWang, L., Chen, W., Chen, K., He, R., & Zhou, W. (2022). The Research on the Signal Generation Method and Digital Pre-Processing Based on Time-Interleaved Digital-to-Analog Converter for Analog-to-Digital Converter Testing. Applied Sciences, 12(3), 1704. https://doi.org/10.3390/app12031704