1. Introduction

The emergence of the Internet of Things (IoT) demands low-power circuits to perform on-device data processing [

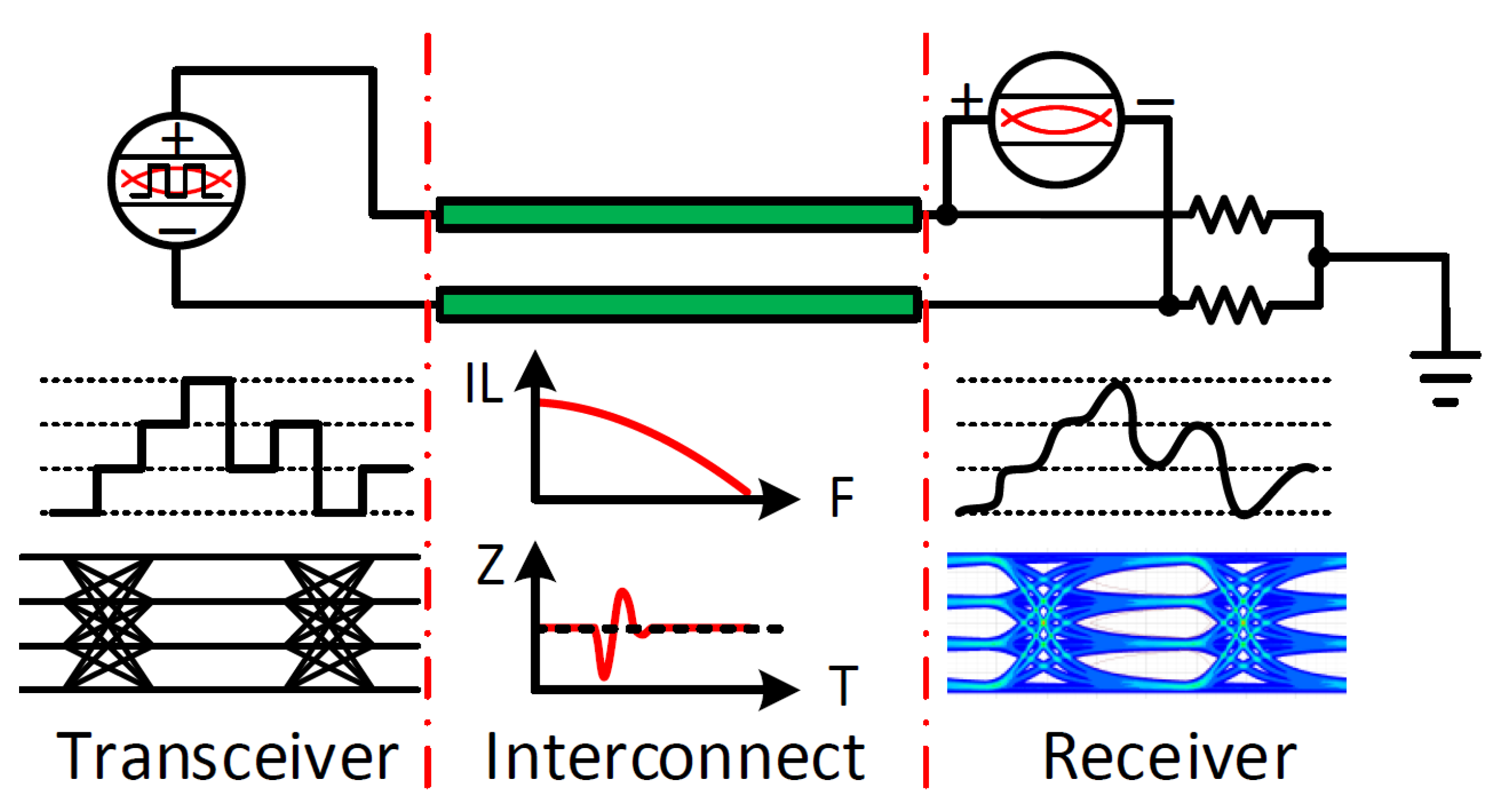

1]. Hence, the IoT applications expect energy-efficient solutions at all design levels. On the hardware level, the interconnect acts as the communication channel between circuits that also consumes power. A typical data transmission that system includes driver, receiver, and interconnect is shown in

Figure 1 below.

While most effort has been concentrated on the on-chip circuit and interconnects’ optimization [

2,

3,

4,

5,

6,

7,

8], the energy-aware off-chip interconnect optimization in the transceiver circuit has not been investigated thoroughly so far [

9,

10]. The authors in [

2,

3,

4] focused on energy-efficient on-chip interconnect design. The approach in [

2] lessens power consumption based on an adaptive voltage scheme while the authors in [

3,

4] proposed a design framework that models and optimizes the energy-efficient on-chip interconnect. On the other hand, authors in [

5,

6,

7,

8] attempt to reduce power consumption by advanced circuit techniques. While the authors in [

5,

6] diminish the power consumption by an efficient pre-emphasis transmitter, the proposed approach in [

7] minimizes the power consumption by reducing voltage swing with a low-power forward error correction architecture. The authors in [

8] suggest power analysis and optimization by trading off transmitter voltage swing and receiver gain.

These works mentioned above attempt to reduce the transmitter voltage swing without considering its impact on the interconnect leading to two main drawbacks. Firstly, the interconnect has parasitic resistance and capacitance which play a significant role in power dissipation. Secondly, voltage swing reduction at the transmitter due to the signal loss and crosstalk always degrades the receiver signal quality at the receiver. On the other hand, the authors in [

9,

10] are concerned with energy-efficiency evaluation for the off-chip interconnect, while the approach in [

9] proposes an energy-aware analysis with analytical formulas using frequency-domain information. The authors in [

10] provide a more comprehensive methodology to evaluate the energy efficiency of the I/O links. However, these works with the conventional design procedure lack an efficient methodology to investigate the immense design space thoroughly. Although the channel in these works is efficiently modeled by analytical approaches proposed in [

11,

12], these approaches have difficulties modeling the complicated structures.

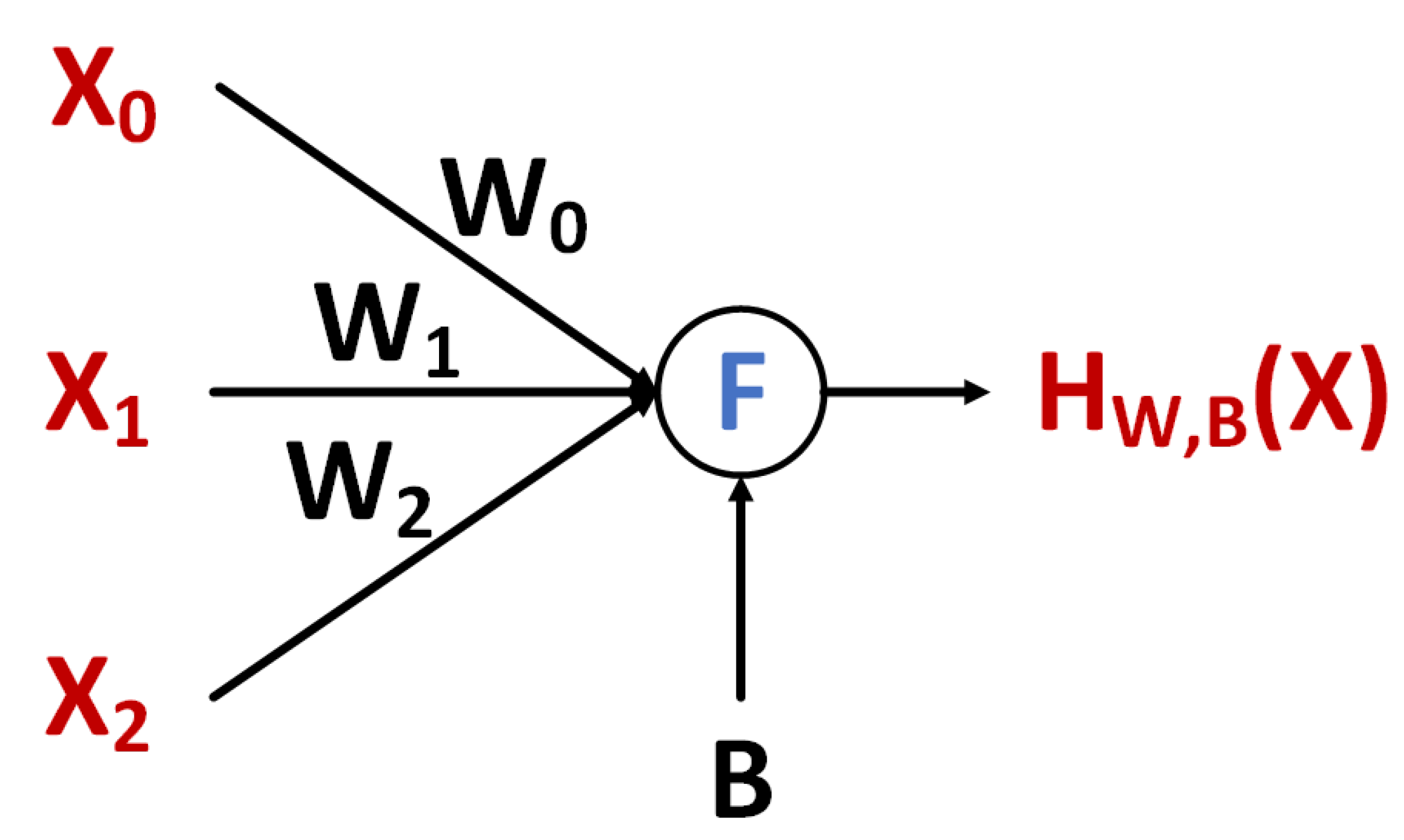

The hardware design procedure including the interconnect design is an iterative process in a human manner. Recently, the rise of machine learning techniques exhibits the hope for an efficient design approach. Hence, many works focus on applying machine learning techniques to improve design efficiency. The approach in [

13] proposes a fast and accurate high-speed channel modeling using an artificial neural network (ANN). Moreover, the genetic algorithm (GA) is utilized to optimize the design. However, this work employs the W-element model for the lossy multi-conductor extracted from the 2-D EM simulator. Hence, it may be inapplicable to the complex structure that requires 3-D EM simulation. Alternatively, the proposed approach in [

14] predicts eye height and eye width based on the ANN model trained by S-parameter in frequency-domain. This approach provides a fast alternative solution in the time-domain. An extension of this approach in [

15] illustrates general applicability with complex numerical examples. Furthermore, the authors in [

15] demonstrates the superior of ANN by a comprehensive comparison. The authors in [

16] enhance the ANN model performance in [

15] with feature selection algorithms described in [

17,

18]. On the other hand, the authors in [

19] use the ANN model to model crosstalk in high-speed transmission lines. However, this approach requires both frequency-domain and time-domain simulation to generate training data for the ANN leading to inefficiency in a complex structure. These approaches require both frequency-domain and time-domain simulation to acquire the training data. Although the ANN model can directly predict the time-domain parameters, both frequency-domain and time-domain simulations in these approaches consume significant effort. Additionally, the frequency-domain is the most time-consuming stage in the design procedure. Moreover, it is a crucial task to analyze and optimize the channel properties in this domain.

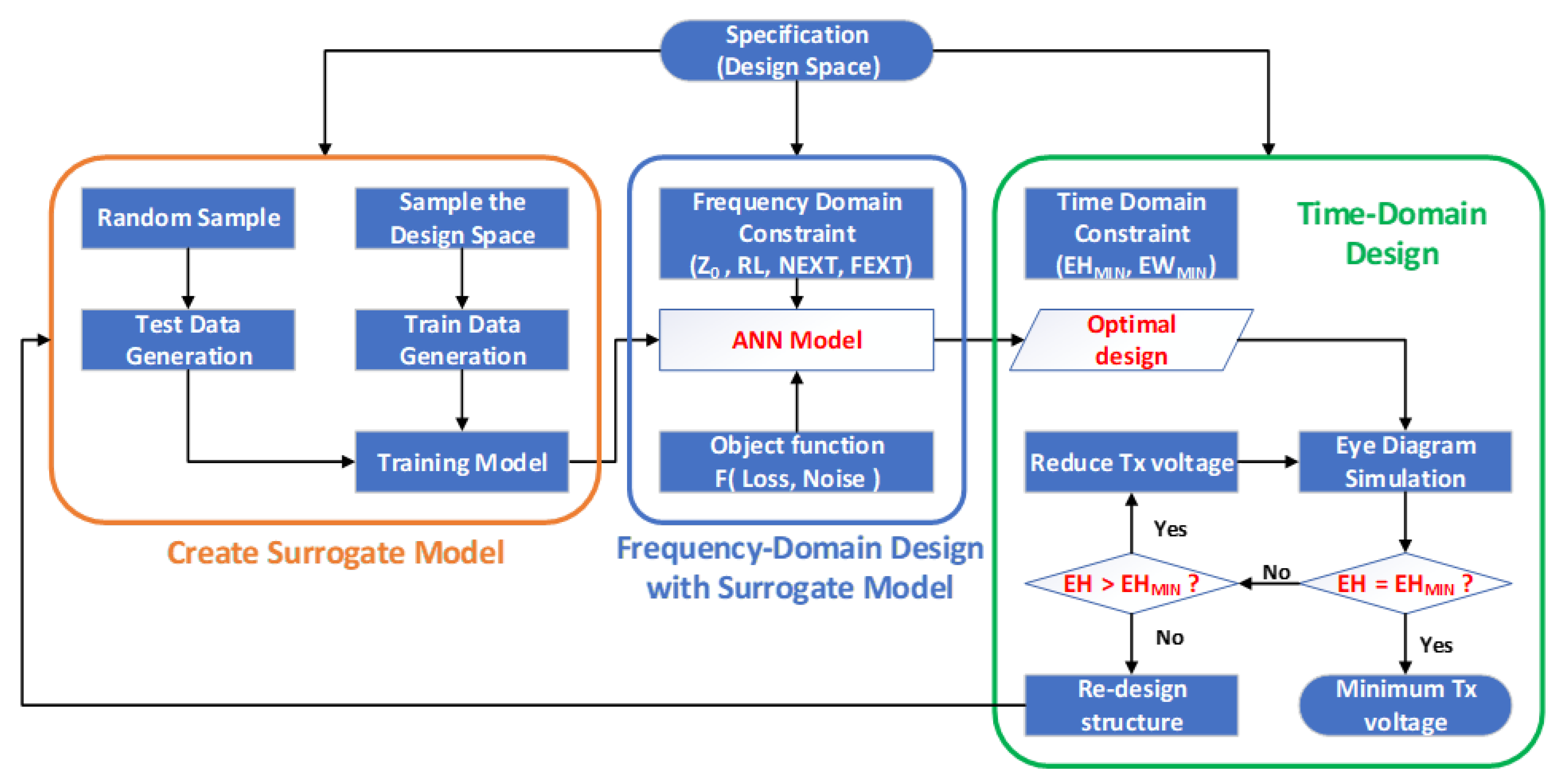

Hence, this paper proposes a low-power design methodology based on ANN to overcome these shortcomings. The proposed methodology leverages the ANN model to produce reliable data in the frequency-domain quickly. This model significantly improves the design efficiency in the frequency-domain. In addition, the method utilizes the ANN model to determine the optimal structure with the objective function. The optimal structure and condition that are found from the proposed approach provides the highest margin in the eye diagram for transmitter supply voltage reduction. Hence, the designer can reduce the voltage swing at the transmitter circuit while the signal quality is still guaranteed.

The rest of the paper is organized as follows:

Section 2 describes the important parameters in the printed circuit board (PCB) interconnect design. Subsequently,

Section 3 introduces the artificial neural network and the proposed approach. Following that,

Section 4 illustrates the approach efficiency in typical structures including microstrip line and stripline. Finally,

Section 5 summarizes the conclusions about the applicability of the proposed approach.

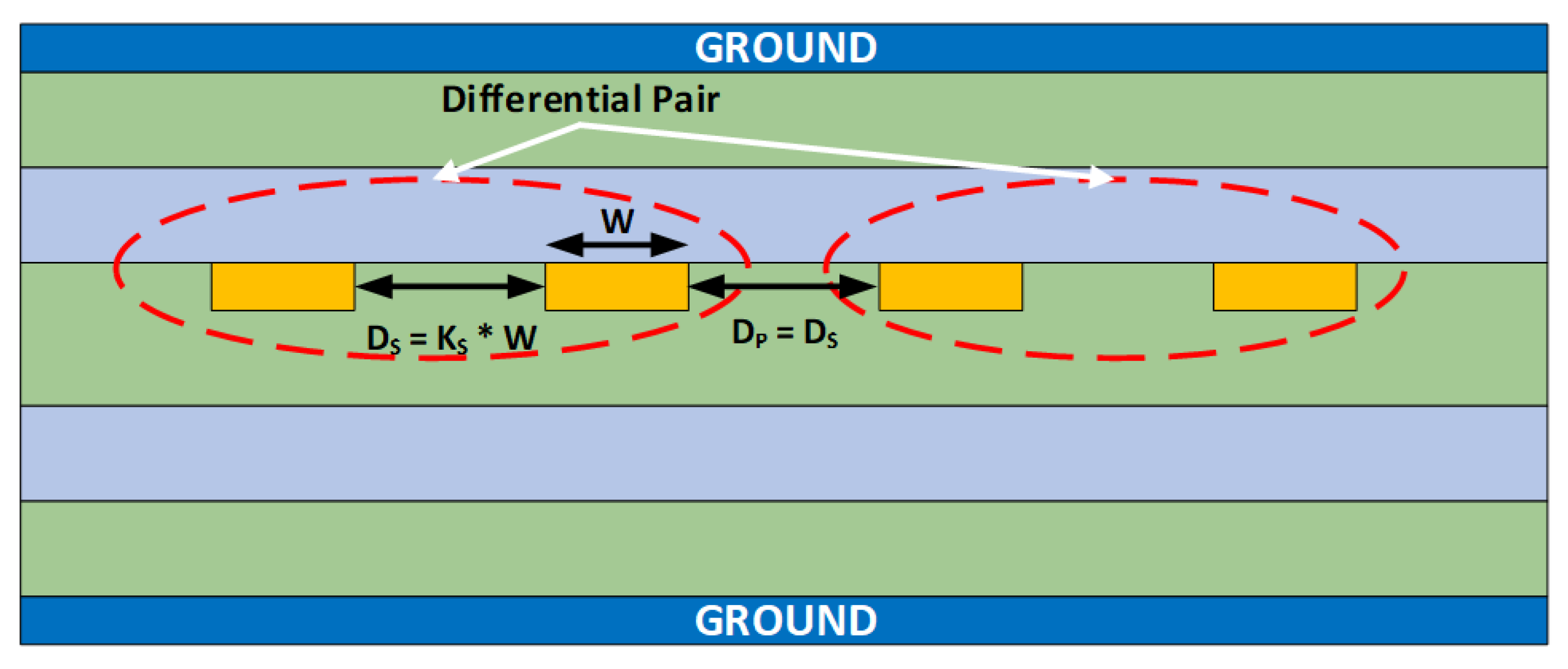

2. Low Power Approach for Interconnect Design

2.1. Off-Chip Interconnect Design Flow

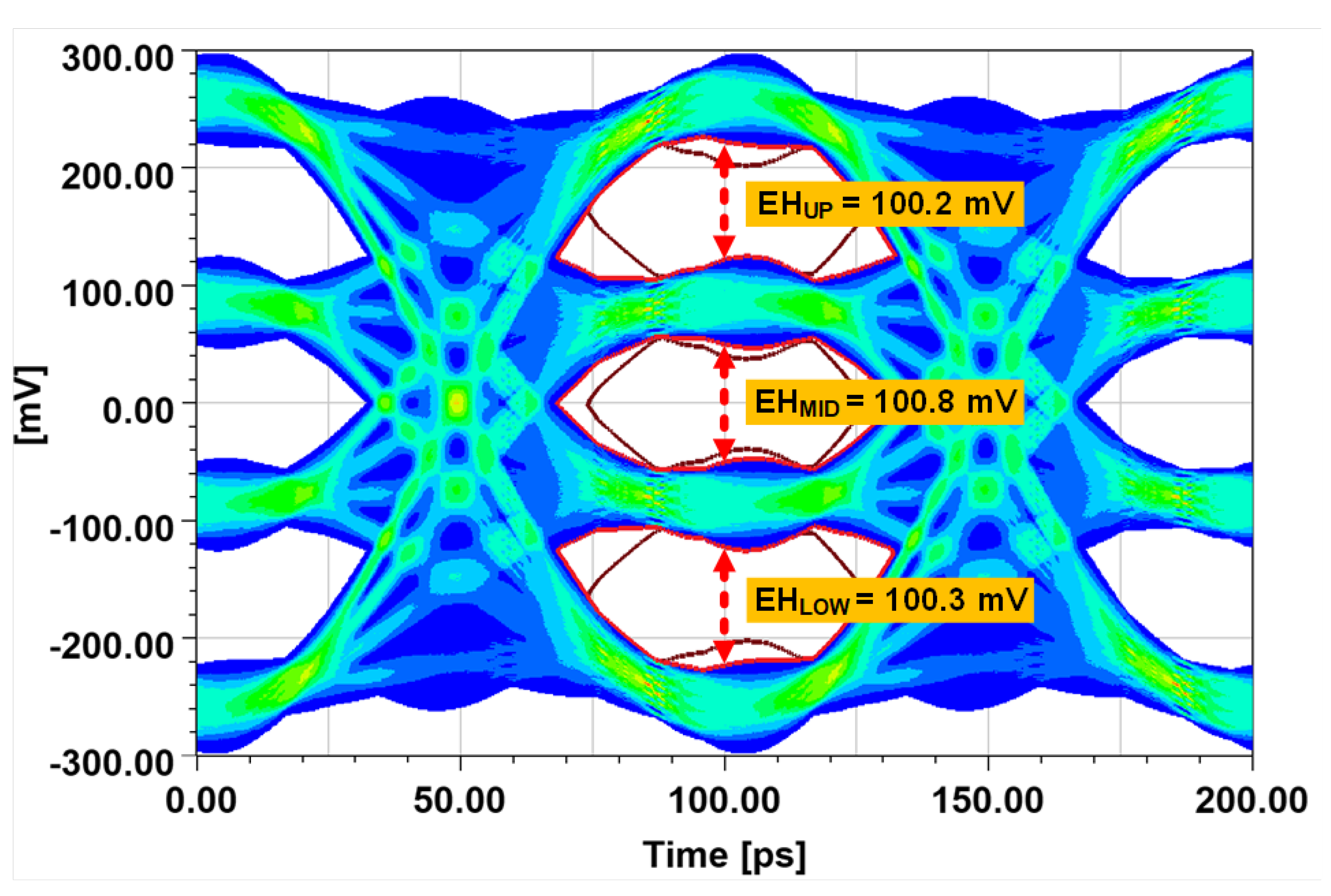

Designing a transmission line for off-chip interconnect is a multi-dimensional process. The design procedure of a transmission line includes both the frequency domain and the time domain due to the its frequency-dependent characteristics. While the scattering parameter (S-parameter) is typically employed to evaluate design properties in the frequency domain, the eye diagram with eye height (EH) and eye width (EW) is generally used to determine the signal quality in the time domain. Additionally, the characteristic impedance (), which is a significant parameter, is required to design carefully to avoid reflection loss along the interconnect.

2.1.1. Frequency Domain Design

According to circuit theory, the lumped model is employed to represent circuit components with neglecting propagation time. At a higher frequency, the propagation time in the interconnect is considerable in comparison to the signal period. Hence, the lumped model is insufficient to describe the structure. In this case, the interconnect is the transmission line modeled by the distributed model. In transmission lines, voltages and currents are expressed as wave propagation along the line. Moreover, the characteristic impedance (

) of the transmission line is defined as the ratio of voltage and current wave propagation along the line [

20]. Alternatively, the characteristic impedance is also a function of the R, L, G, C parameters of the transmission line, which are frequency-dependent. Thus, this characteristic impedance is also a frequency-dependent parameter. Theoretically, this impedance is constant along the length of the transmission line at a specific frequency. However, the system includes not only the transmission line but also other connectors such as vias, SMA, and so on. Hence, the mismatch impedance between these components results in reflection loss. As a consequence, the impedance is one of the most significant parameters in the interconnect design that typically is 50

for a single-ended signal and 100

for a differential signal.

In addition to the characteristic impedance, the values of scattering parameters (S-parameters) need to be investigated carefully in the design procedure. Typically, an N-port network is employed to represent the network at high frequency. The concept of equivalent voltages and current and the related impedance and admittance matrices are developed to describe the network. However, these concepts become abstract when dealing with the high-frequency network. Thus, the scattering matrix is preferable to provide a complete description of an N-port network. While the characteristic impedance represents the ratio between voltage and current wave in the transmission line, the S-parameters express the relationship between the incident and reflected voltage in the N-port network [

20]. In the N-port, a specific parameter

is determined as below

where:

- V−i:

Reflected voltage from port i

- V+j:

Incident voltage at port j

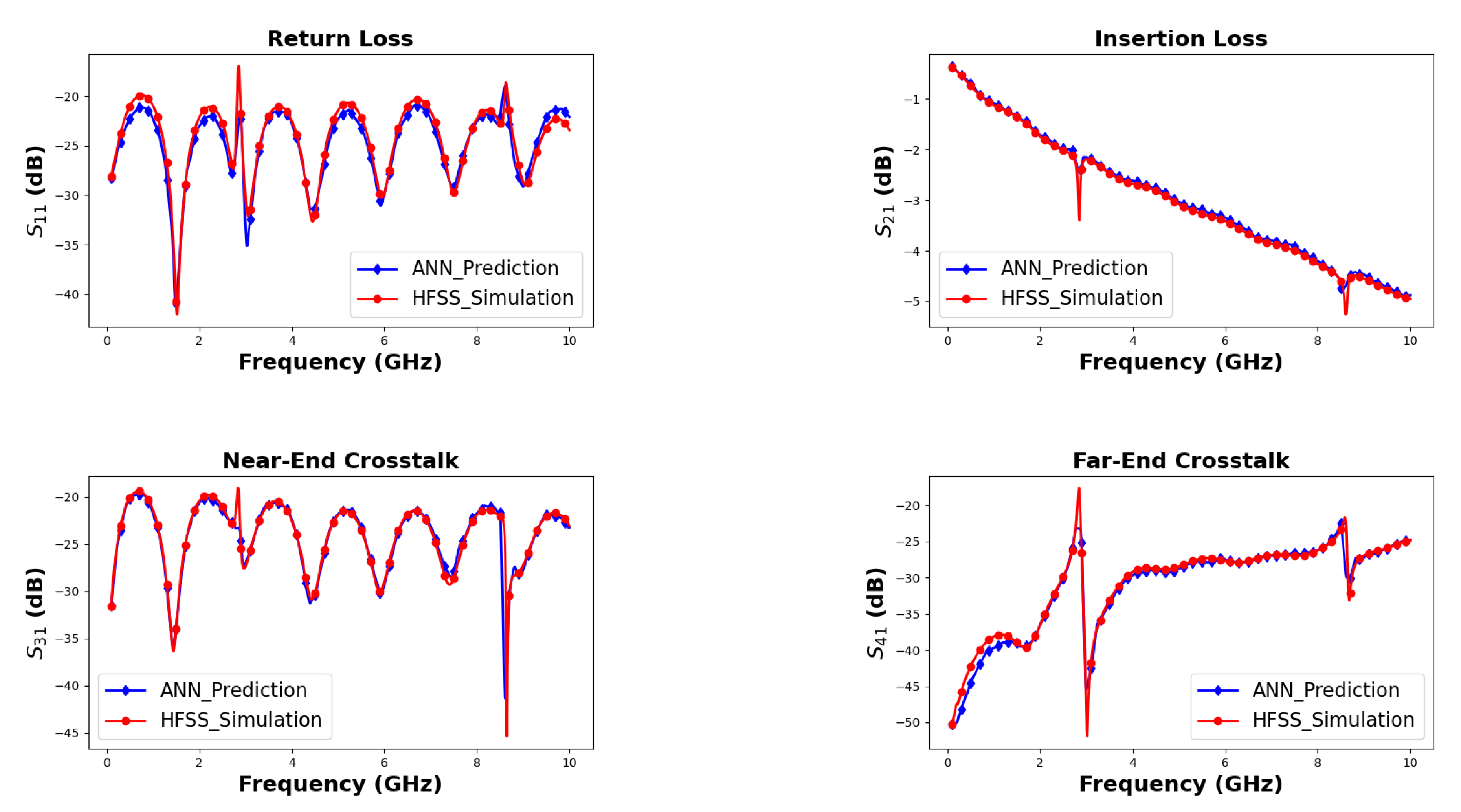

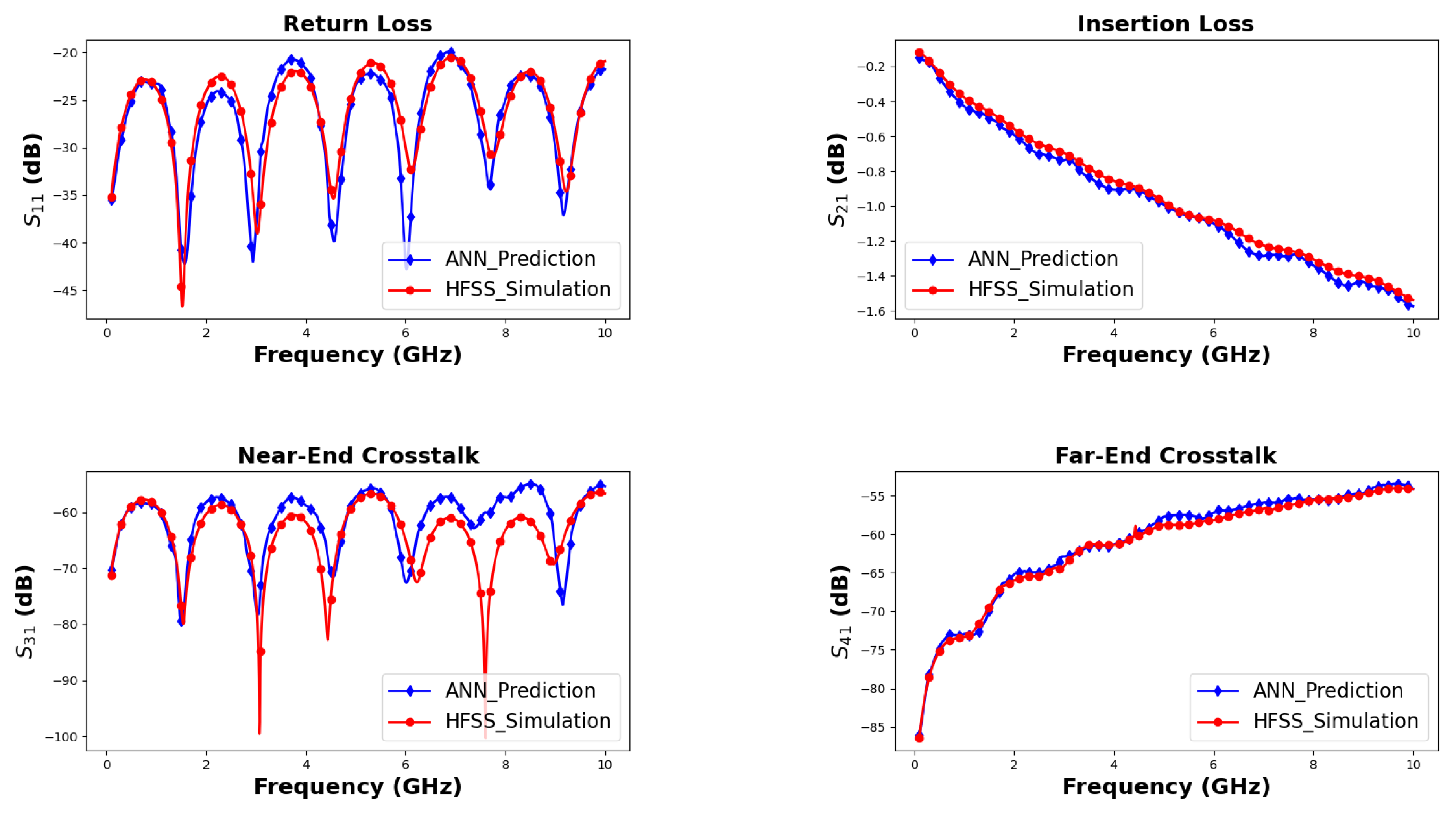

The S-parameters of a four-port network show all the significant parameters of two coupled interconnects. represents the insertion loss throughout the channel including material, conductor, and radiation loss. The reflection loss caused by the mismatch impedance is represented in . Additionally, the crosstalk comprised of near-end crosstalk (NEXT) and far-end crosstalk (FEXT) is represented by and , respectively.

2.1.2. Design in Time Domain

Although

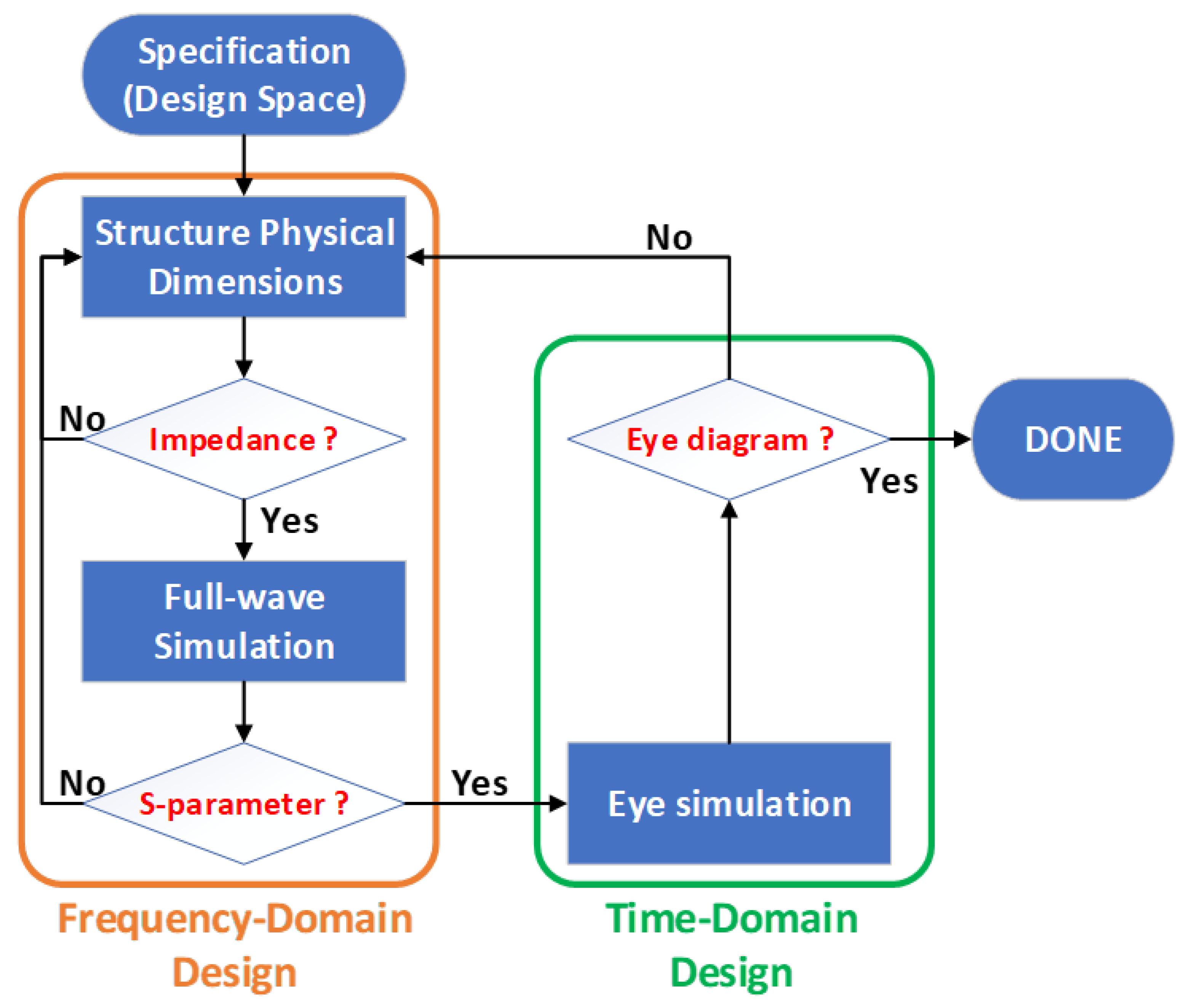

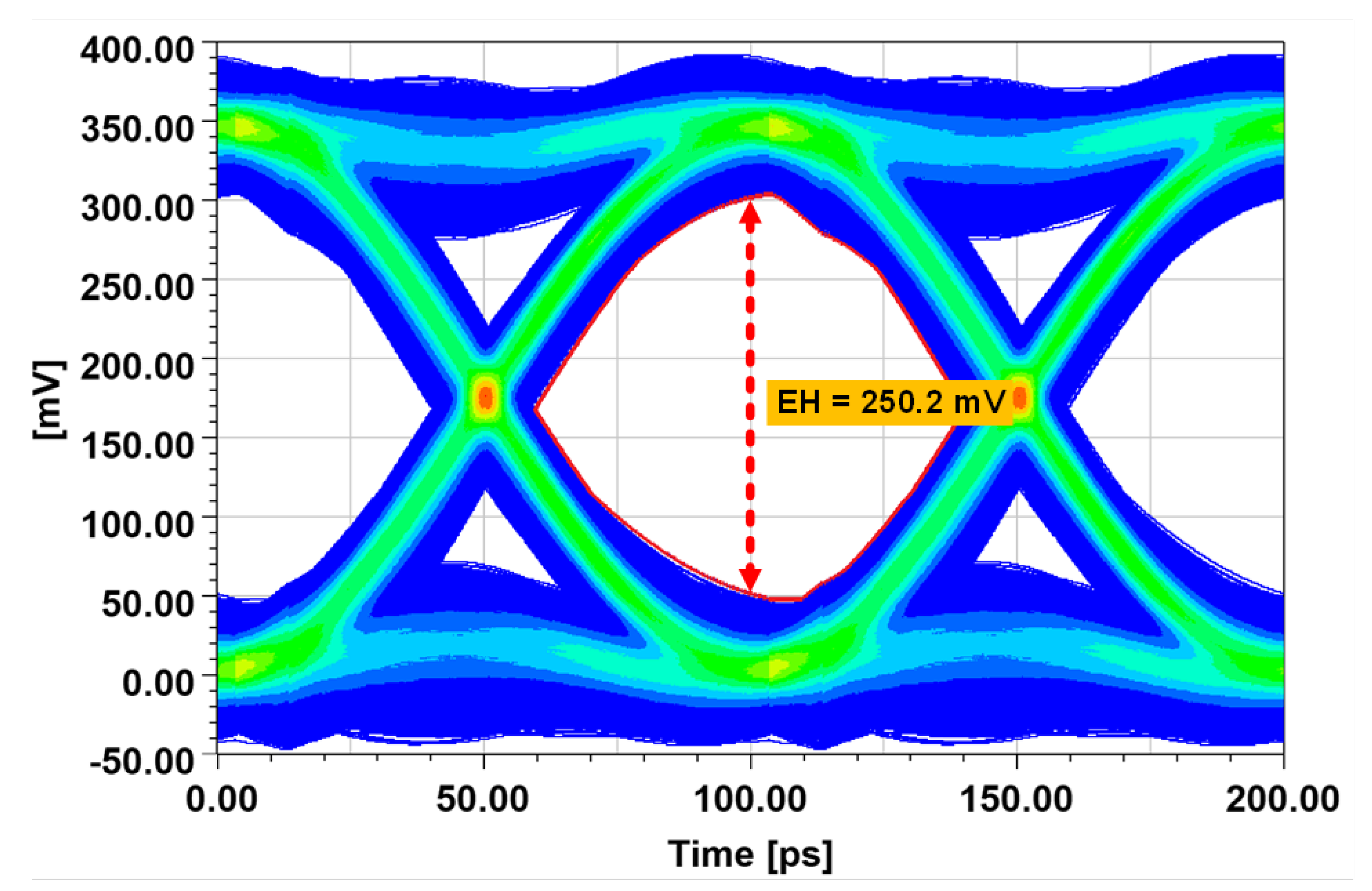

and S-parameters characterized in the frequency domain represent many of the significant performance parameters in the frequency domain, the ultimate figure of merit to evaluate the channel is the eye diagram that belongs to time-domain design. The eye diagram is a statistical convolution of multiple signals at the receiver that forms a figure similar to the eye. The EH and EW are employed to evaluate the quality of the signal arriving at the receiver. However, the frequency domain information is applied to obtain the eye diagram at the receiver. As a consequence, the interconnect design requires both frequency domain and time domain. The conventional flow is shown in

Figure 2 below.

2.2. Low Power Approach for Interconnect Design

According to the proposed approach in [

10], an equivalent circuit with analytical formulas is inferred to evaluate the power performance. In this approach, the power dissipation is directly proportional to the transmitter supply voltage and the input impedance is a function of the interconnect characteristics and termination impedance. While the interconnect characteristics are frequency-dependent, the termination impedance comprises the transmitter output impedance and the receiver input impedance. The termination impedance is generally similar to the channel characteristic impedance to avoid reflection. This impedance value is typically 50

for the single-ended signal and 100

for the differential signal. As a result, the interconnect and the transmitter supply voltage are the controllable parameters for low-power interconnect design.

The power consumption of transceiver system is mainly from the switching activity of the circuits and the leakage current from transistors. This power is directly supplied by the voltage source. Therefore, in addition to reducing the leakage current and switching actions, reducing the voltage source is an efficient method for power saving in which the power is a trade-off with the speeds. Thus, many efforts concentrate on reducing the transmitter supply voltage by advanced circuit techniques. However, a decrease in transmitter voltage swing without considering the interconnect results in unreliable function. This reduction will harm the transmitter signal quality and make it more sensitive to noise along the interconnect. Hence, this voltage reduction degrades the signal to noise ratio (SNR) and this may lead to an inapplicable in transceiver system. Because the interconnect deals with signal transmission, the power consumption throughout the channel is not provided by the voltage source supply. This power directly accounts for the input power leading to worsened signal quality at the receiver determined by the EH and EW. The power consumption in the interconnect comes from the loss throughout the channel including insertion loss, return loss, and noise. Consequently, saving the power-consumption in the interconnect is equivalent to minimizing the channel loss. Thus, the low-power interconnect design has the trade-off relation between performance and power. Therefore, an optimized interconnect should be designed for better power efficiency. As a consequence, it can be applied to design the low-power system without impacting the signal quality.

In addition to the channel loss, the crosstalk also plays a vital role in the design procedure. The induced noise voltage produced by crosstalk can degrade the signal quality at the receiver. However, this signal is proportional to the transmitter supply voltage. Hence, eliminating this noise increases the transmitter supply voltage resulting in additional power consumption. As a consequence, the design procedure contains crosstalk analysis to deliver a low-power structure. In conclusion, the optimal low-power interconnect is a low-loss and low-noise structure that can operate at low transmitter supply voltage with acceptable signal quality.

5. Conclusions

This paper proposes an energy-efficient design methodology for low-power interconnects. The proposed approach leverages the artificial neural network as a surrogate model to significantly improve the design time in the frequency domain. Furthermore, with the design constraints and the objective functions, the ANN based black-box function is used to determine the optimal structure. The objective function specifies a low-loss and low-noise structure for the maximum allowable transmitter supply voltage reduction in the time-domain with given design constraints such as characteristic impedance, return loss, and crosstalk.

The proposed methodology is applied to two typical interconnect structures, microstrip lines and striplines. Moreover, the single-ended and differential signals are tested to guarantee the general applicability of the approach. In the microstrip line design, the proposed methodology significantly improves design efficiency with 43.2 s, 42.7 s for data generation and 0.5 s for design optimization per structure. Additionally, the optimal design found from the proposed approach provides the highest EH resulting in the maximum 25% transmitter supply voltage reduction for the minimum power. For the stripline structures, the proposed methodology shows an impressive improvement in design efficiency with 32.5 s for one design included 31.9 and 0.6 s for the data generation and optimization process, respectively. Moreover, the suggested stripline structure with the highest EH achieves the minimum power by a maximum 30.7% peak to peak voltage reduction.