Generalized Structures for Switched-Capacitor Multilevel Inverter Topology for Energy Storage System Application

Abstract

1. Introduction

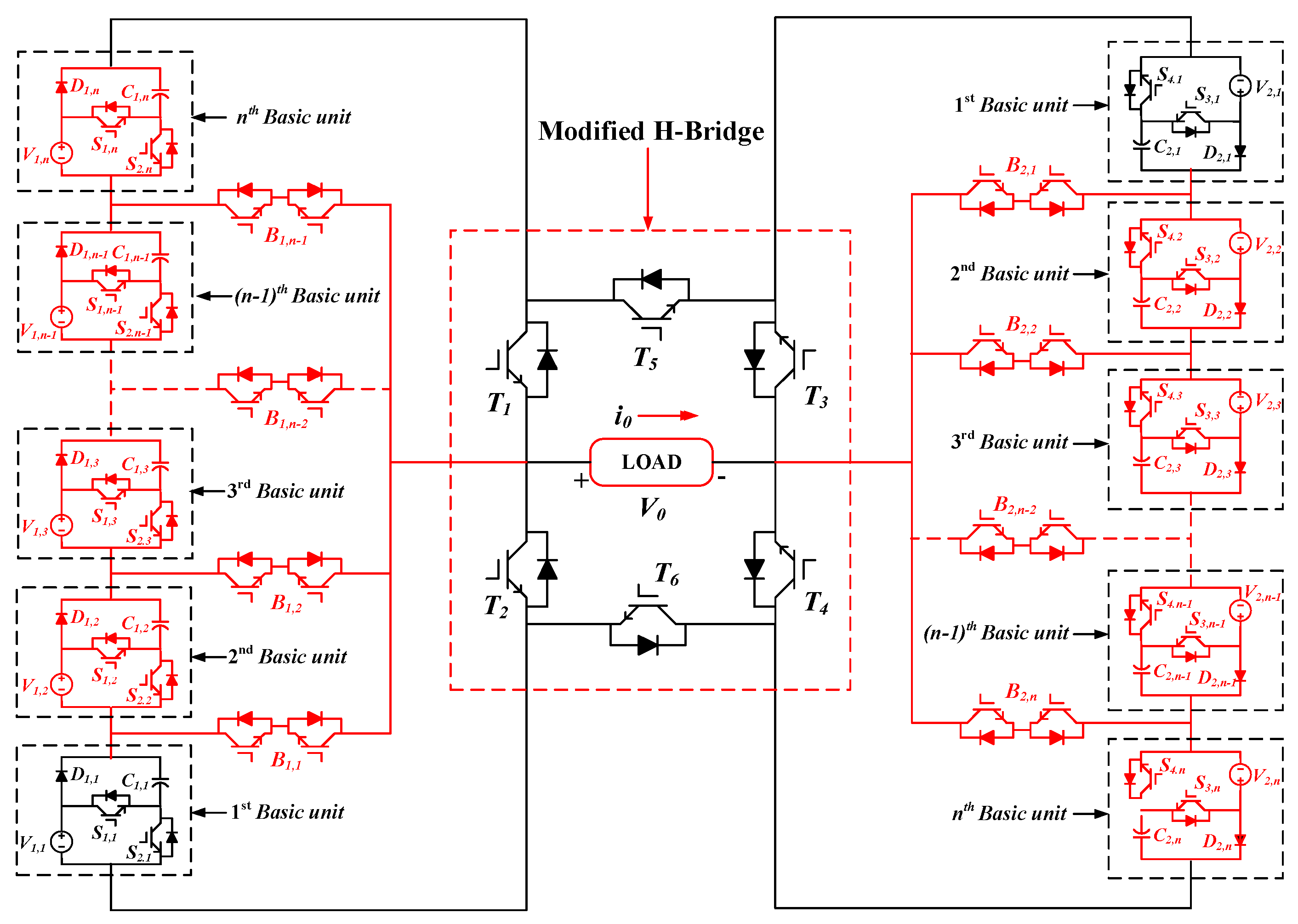

2. Proposed Generalized Structures of the Switched Capacitor Multilevel Inverter

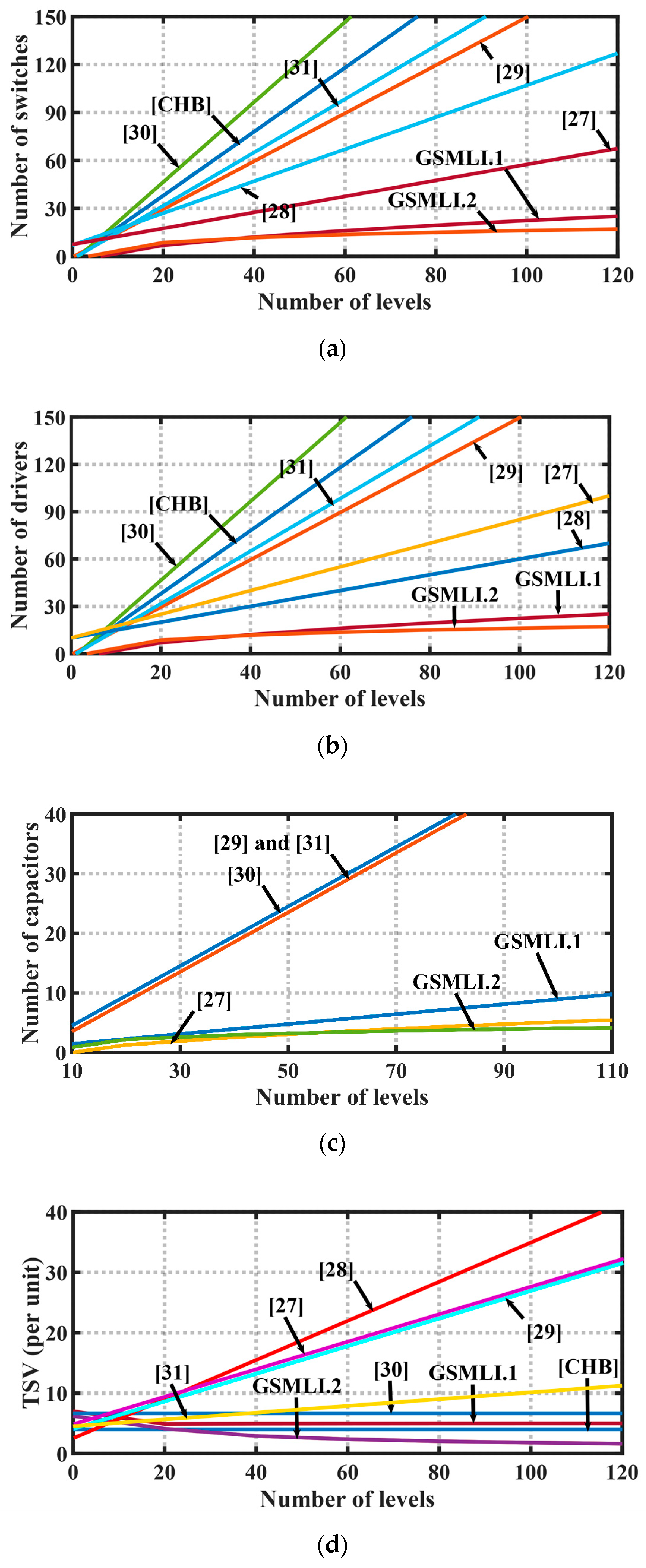

3. Comparative Analysis of the Proposed GSMLI Topology

4. Analysis of the Basic Unit of GSMLI

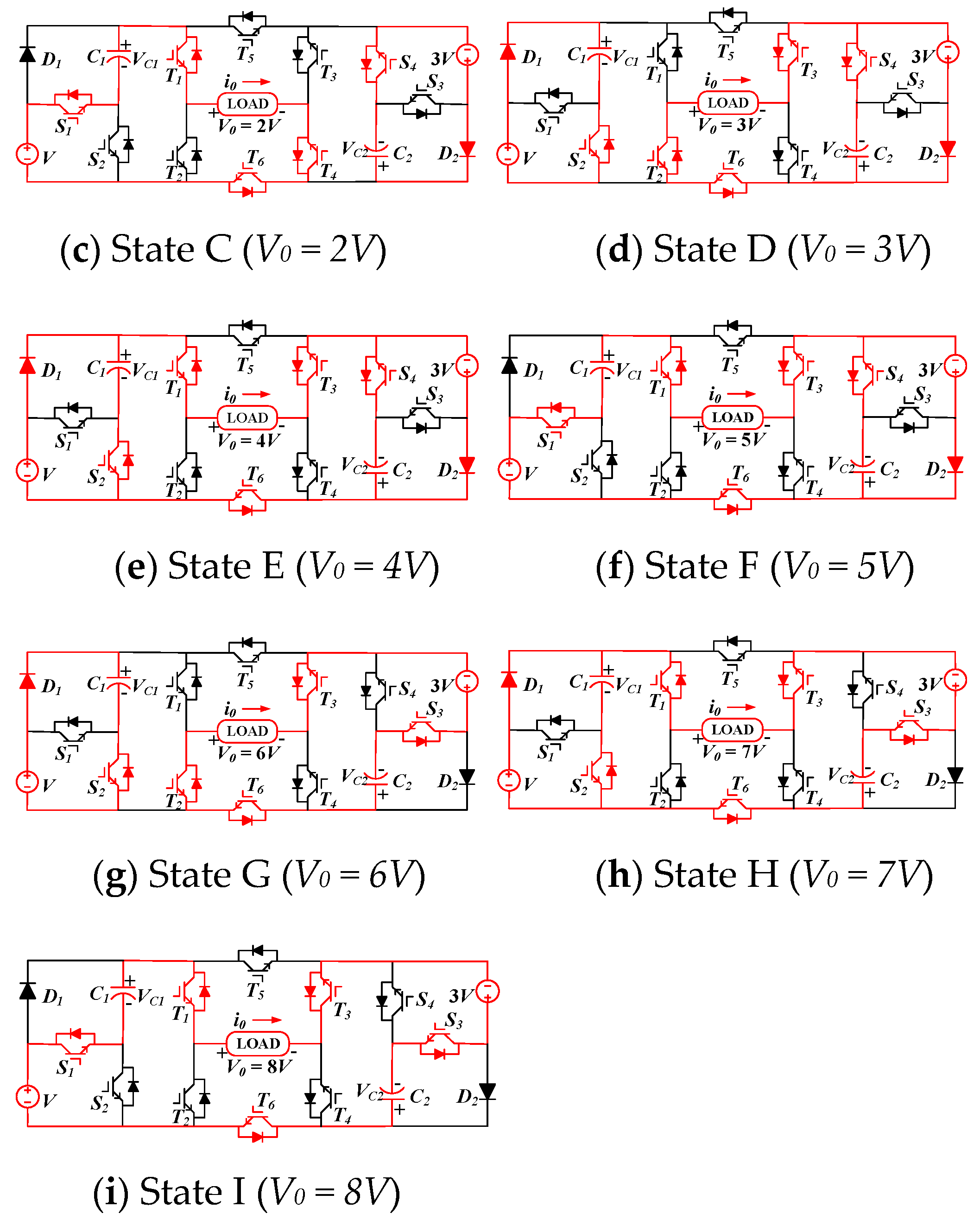

4.1. Operating States

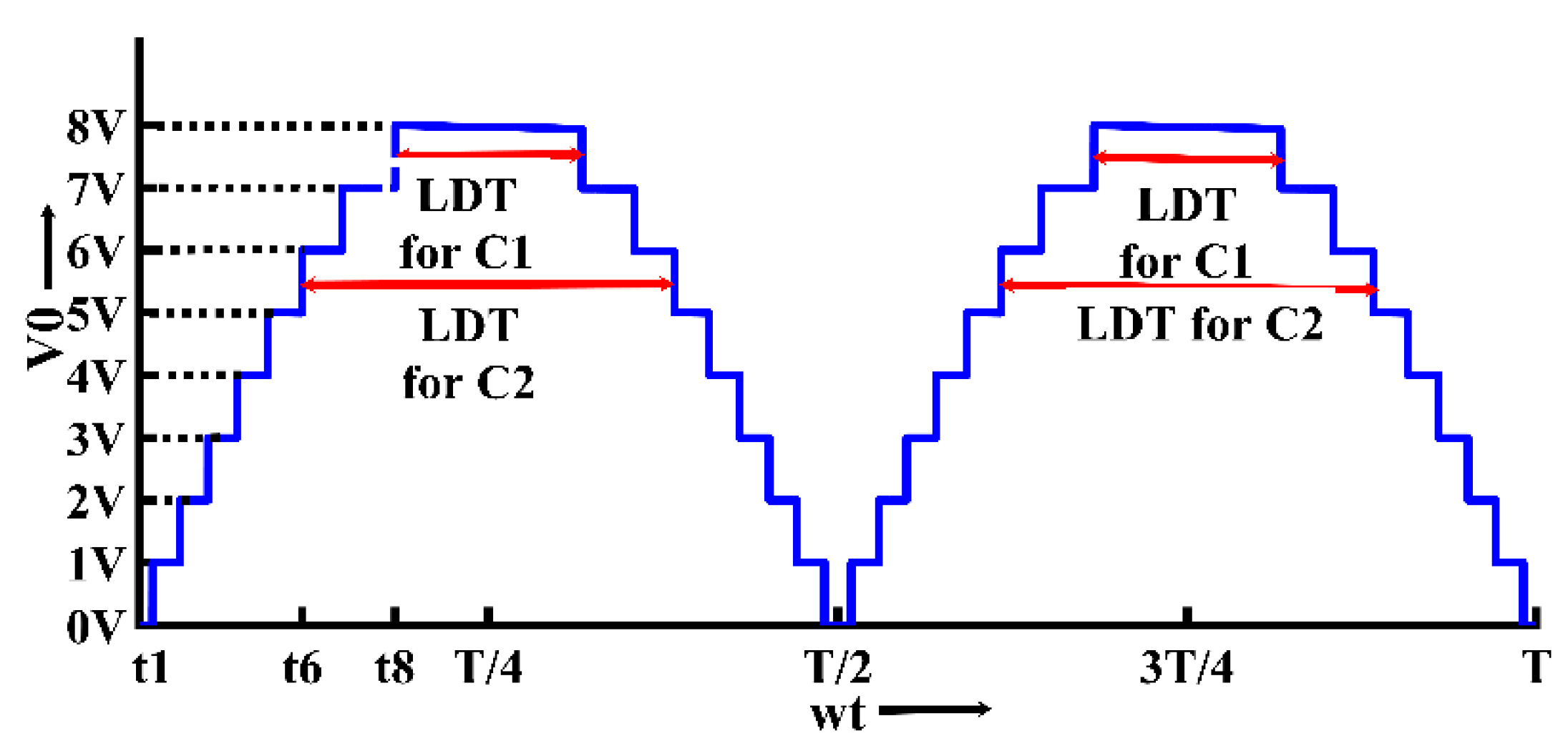

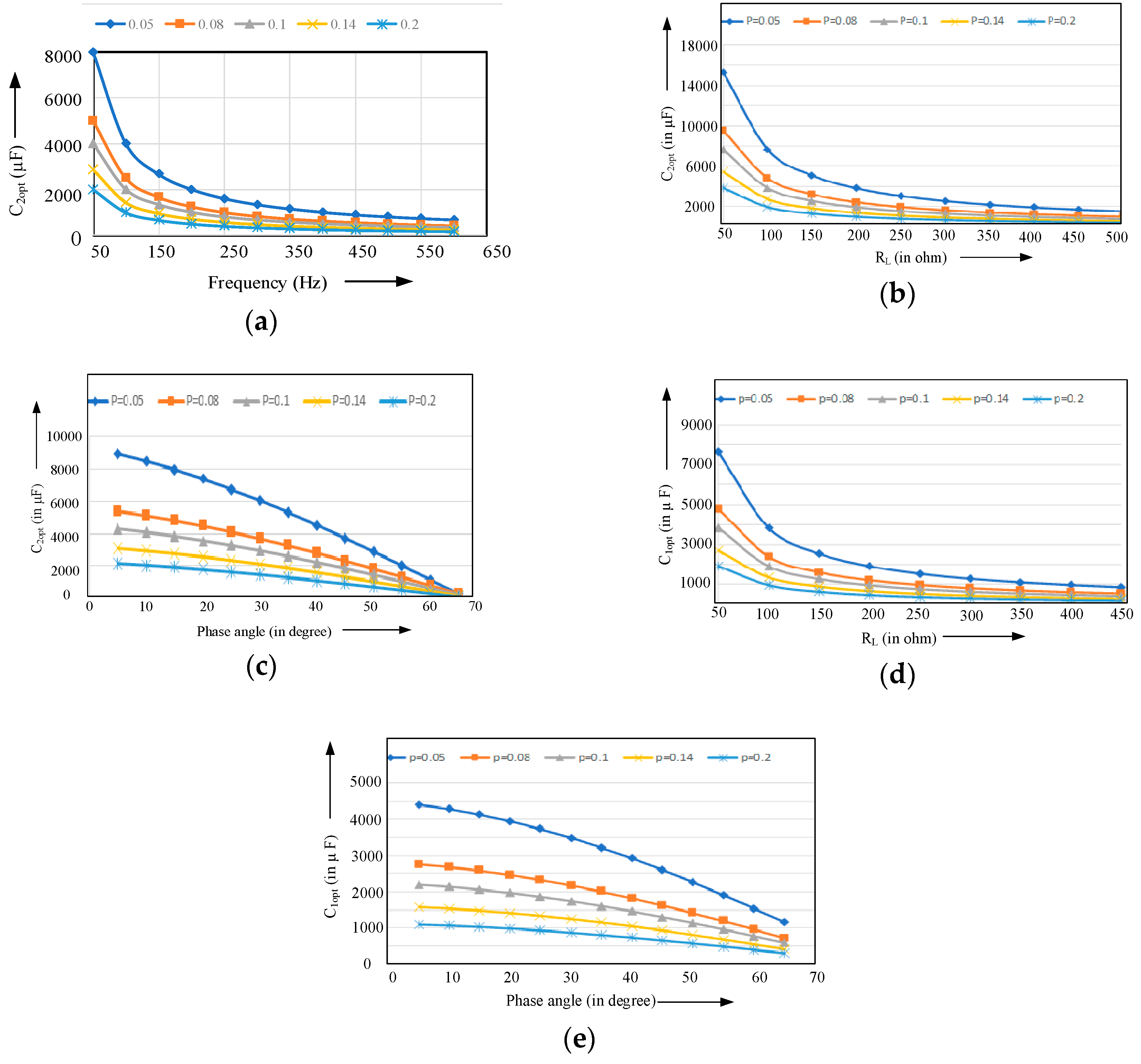

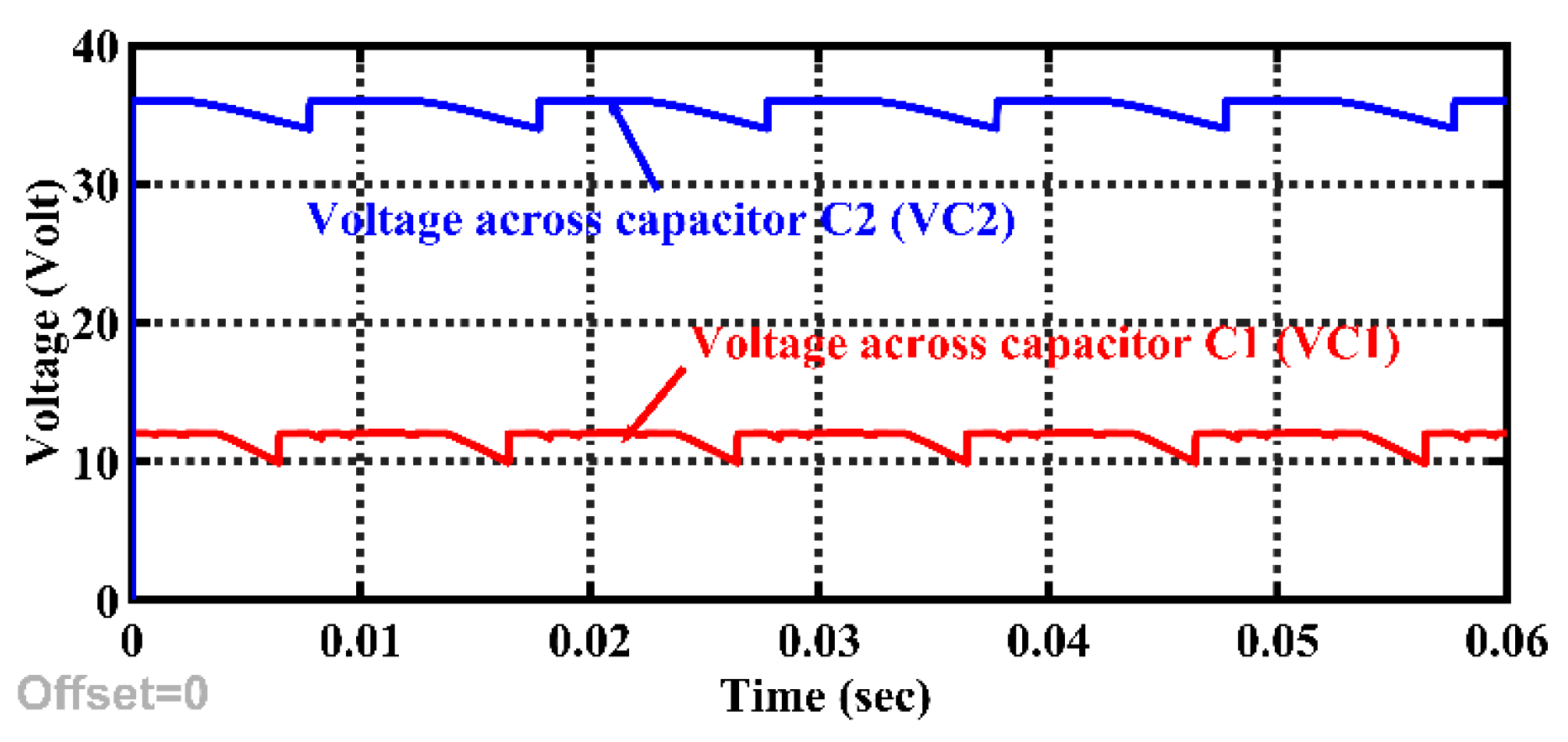

4.2. Capacitance Selection

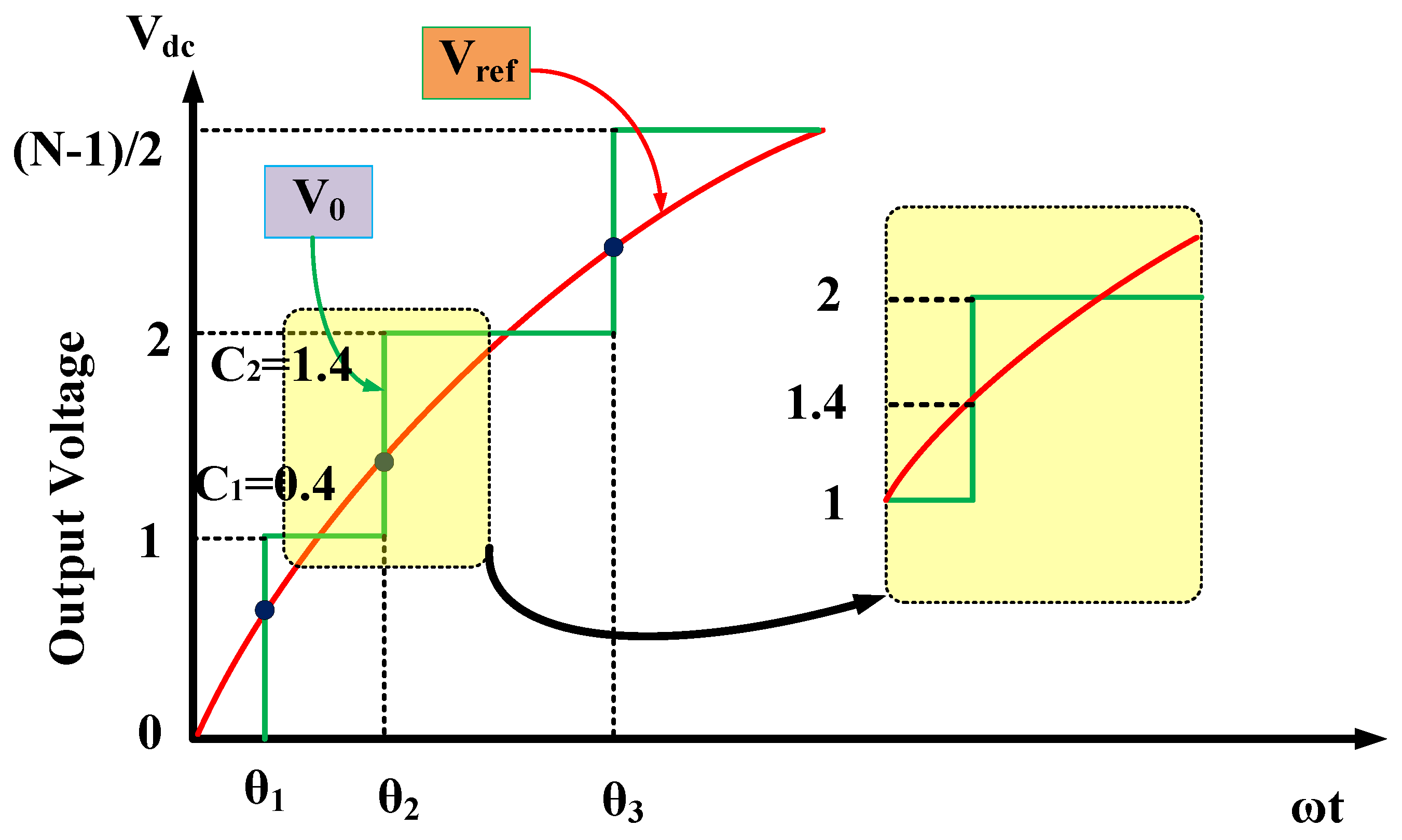

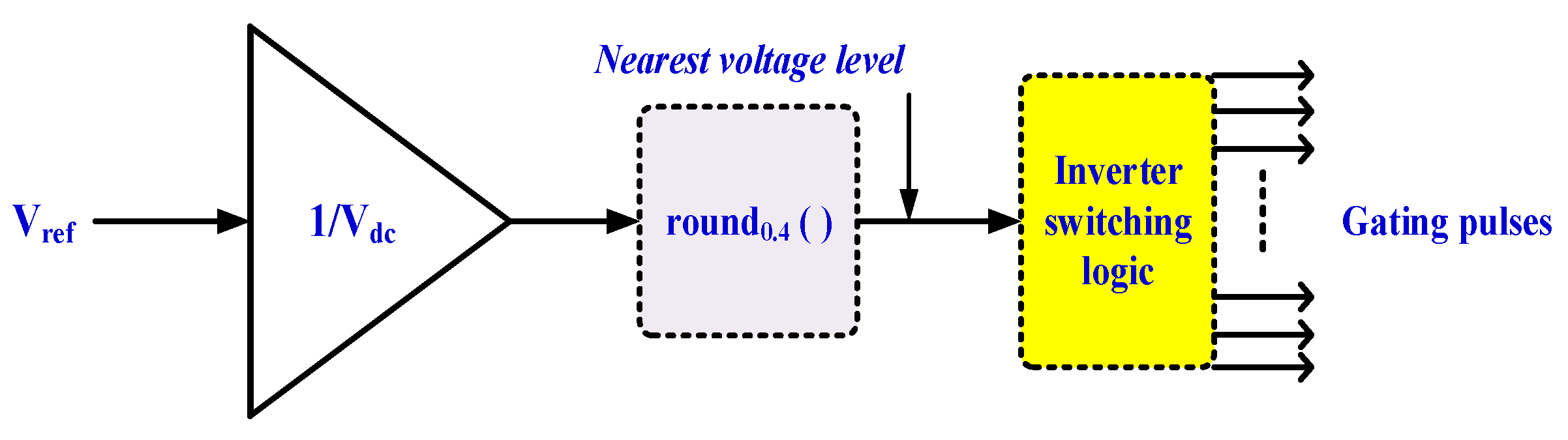

4.3. Modulation Scheme

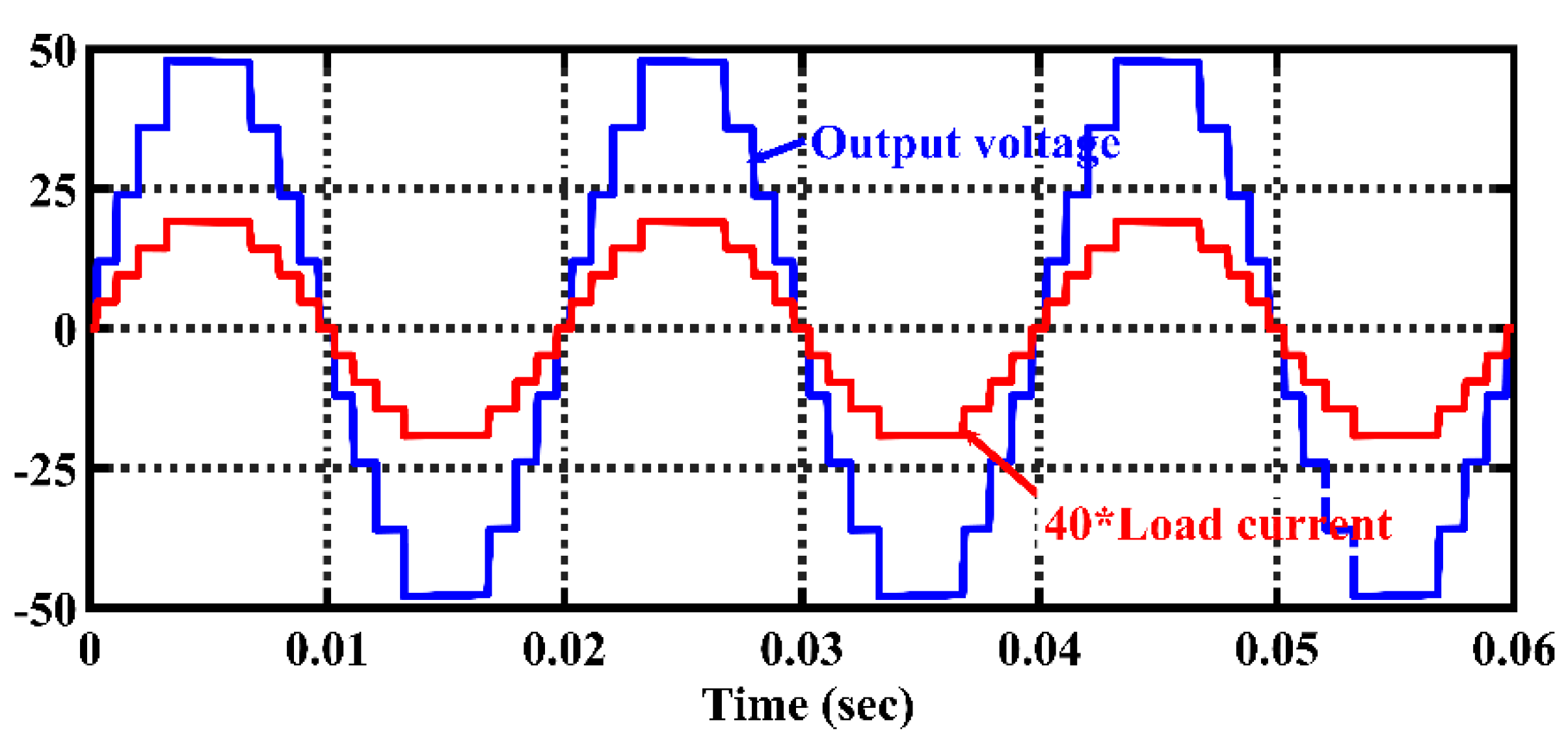

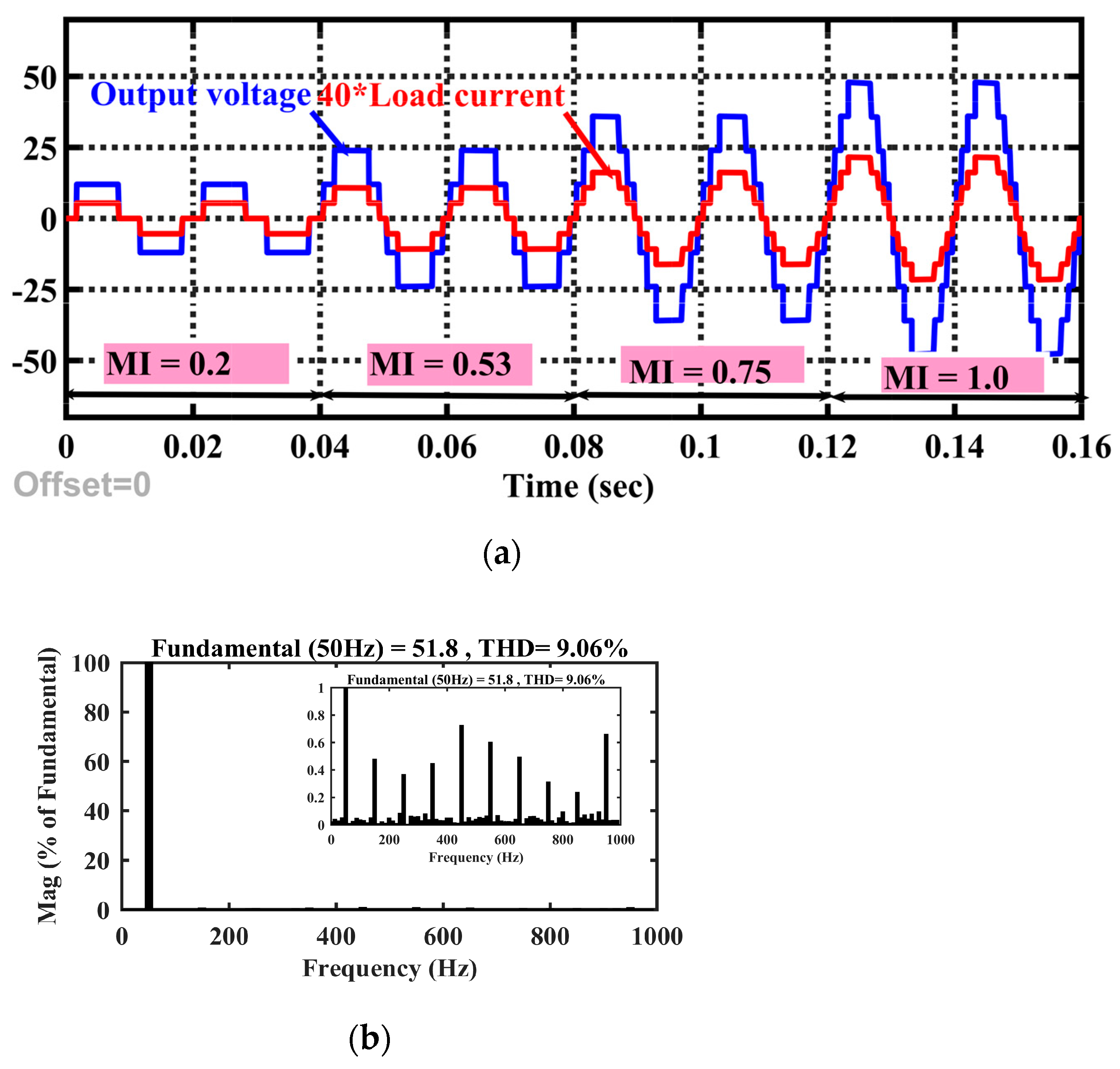

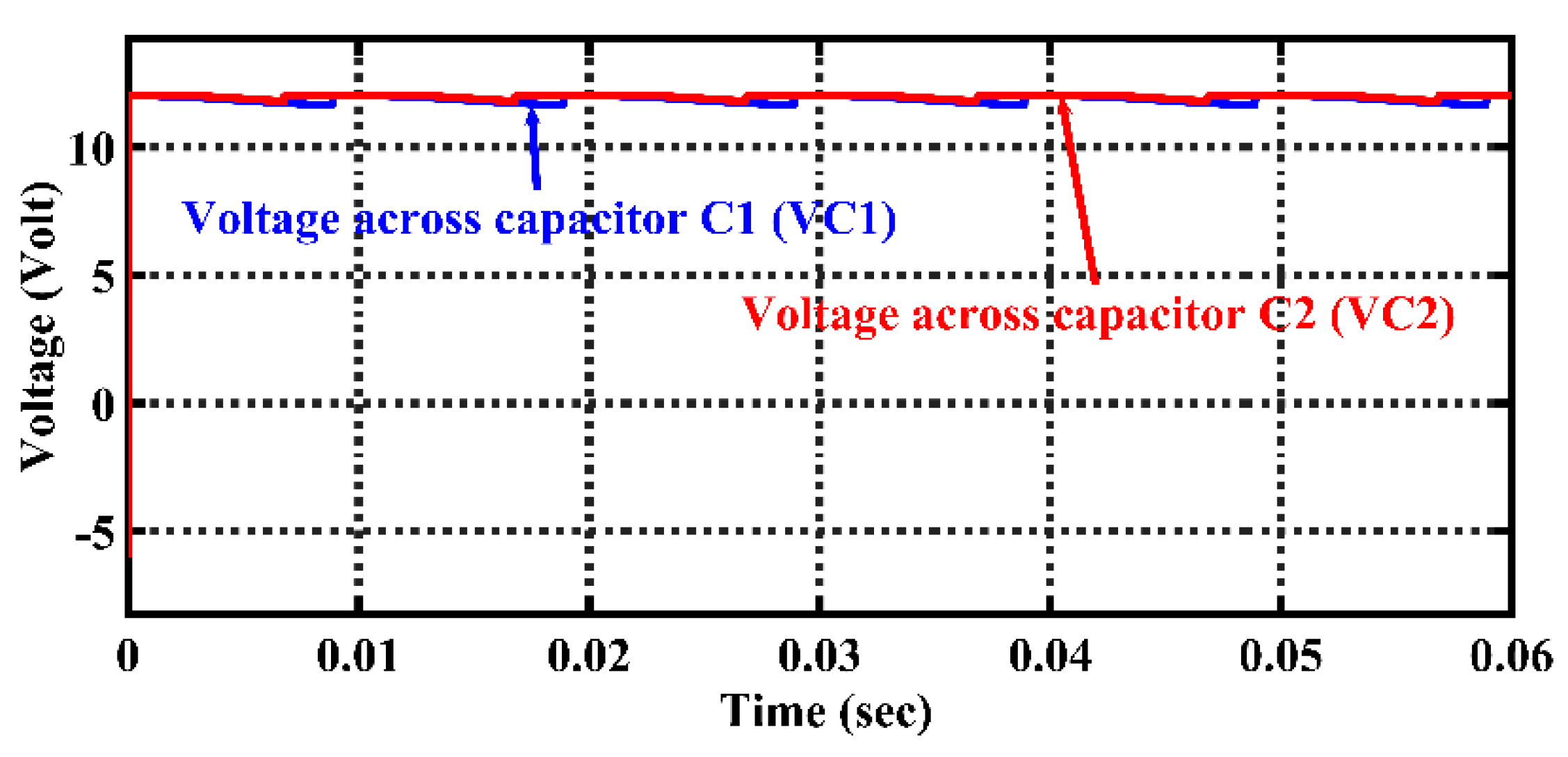

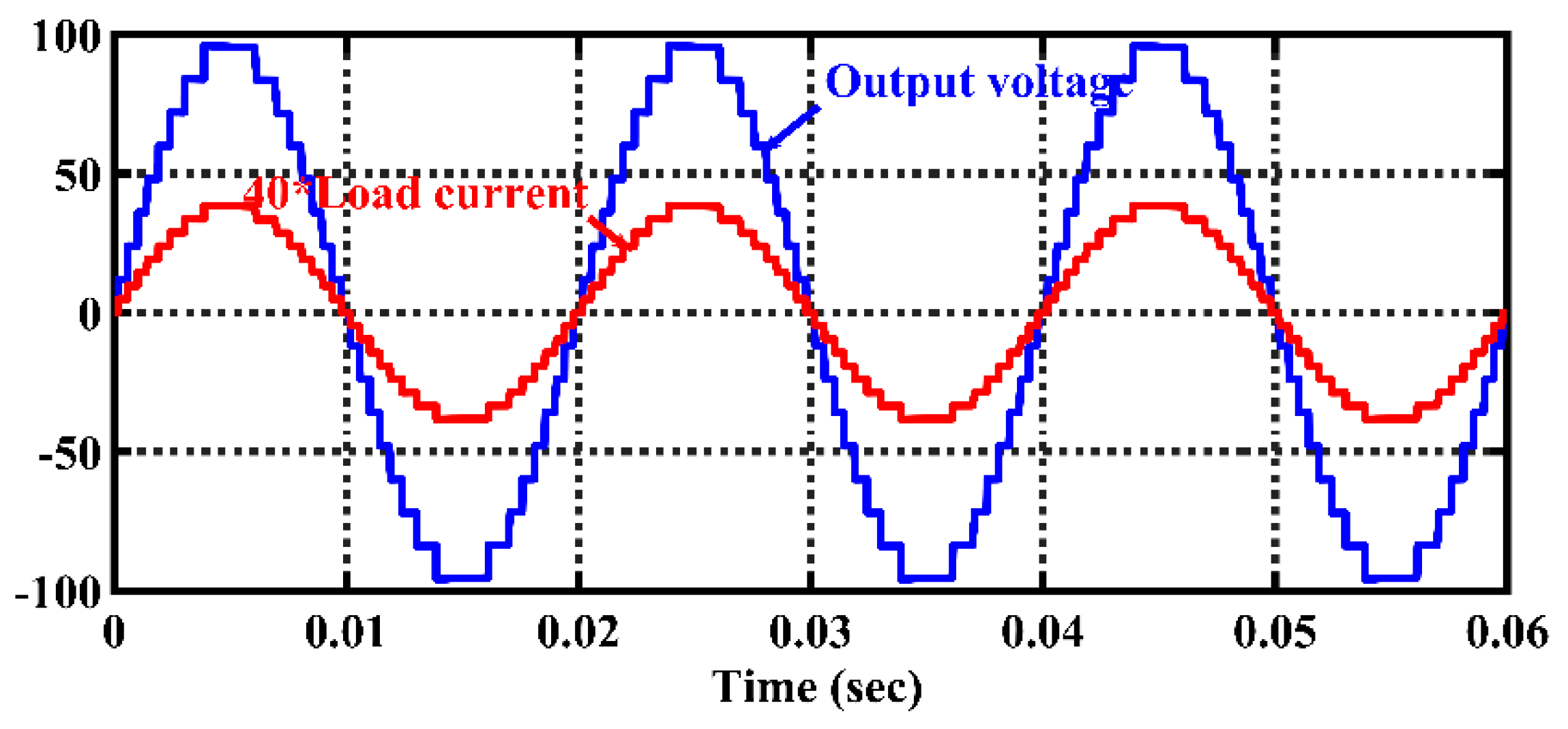

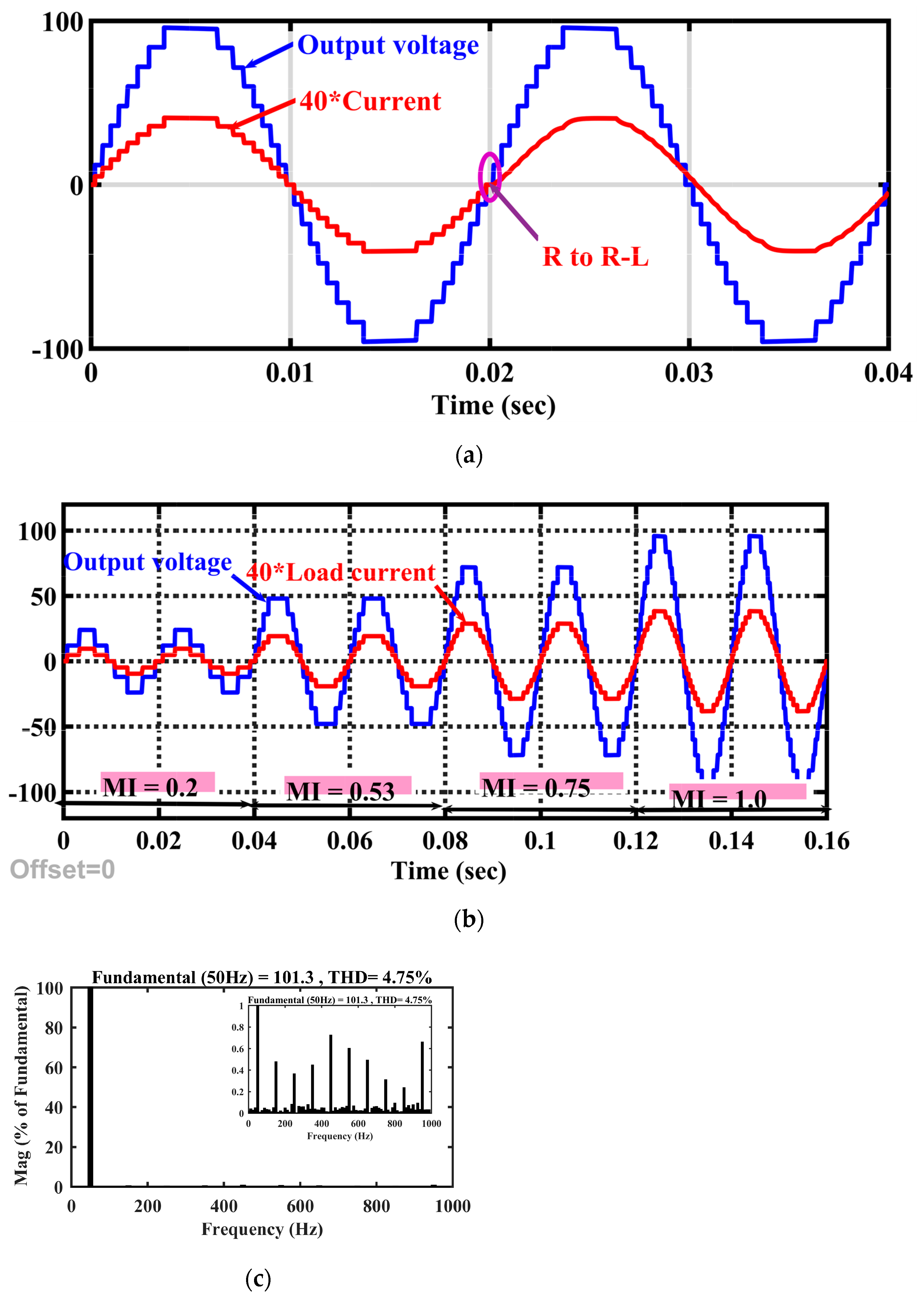

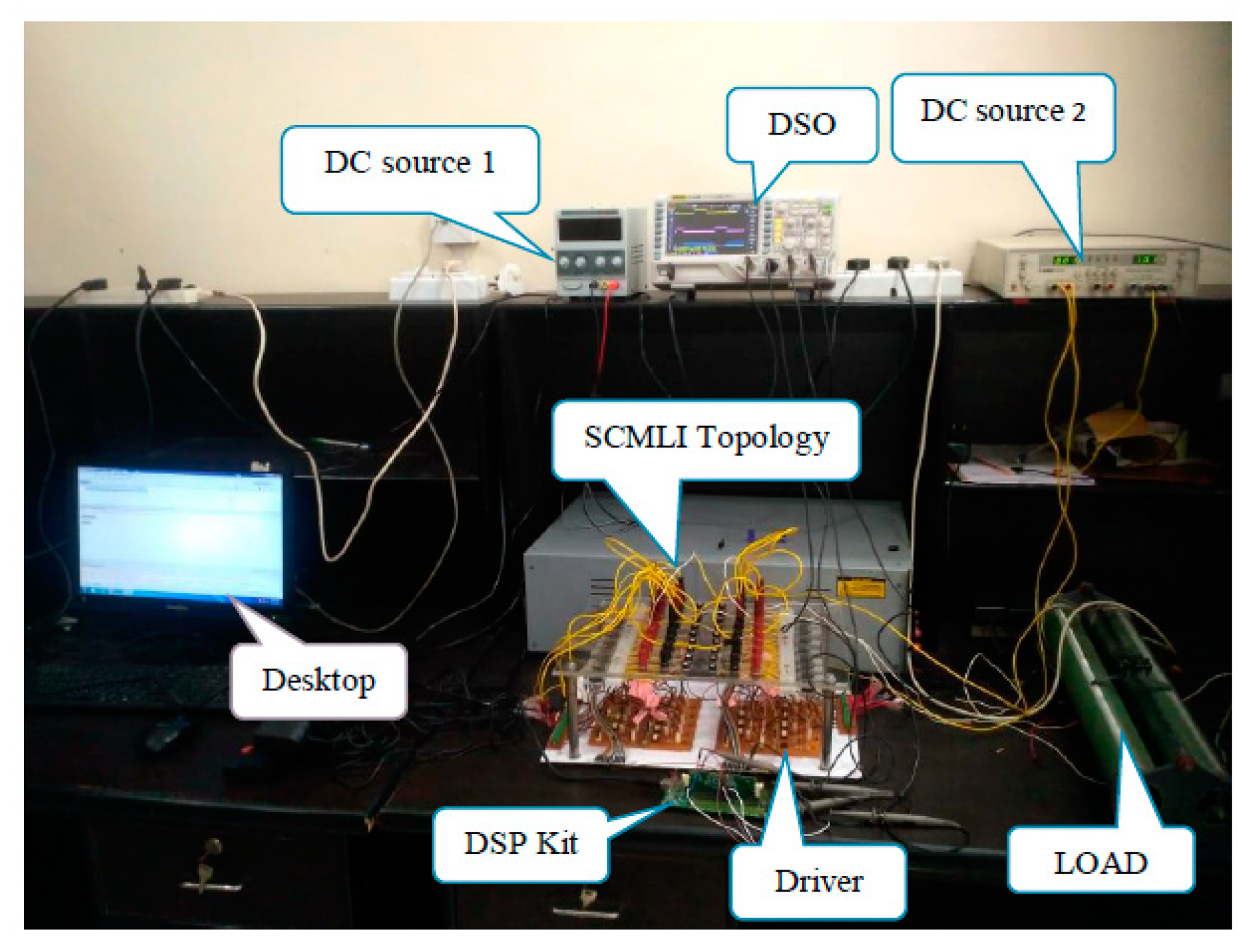

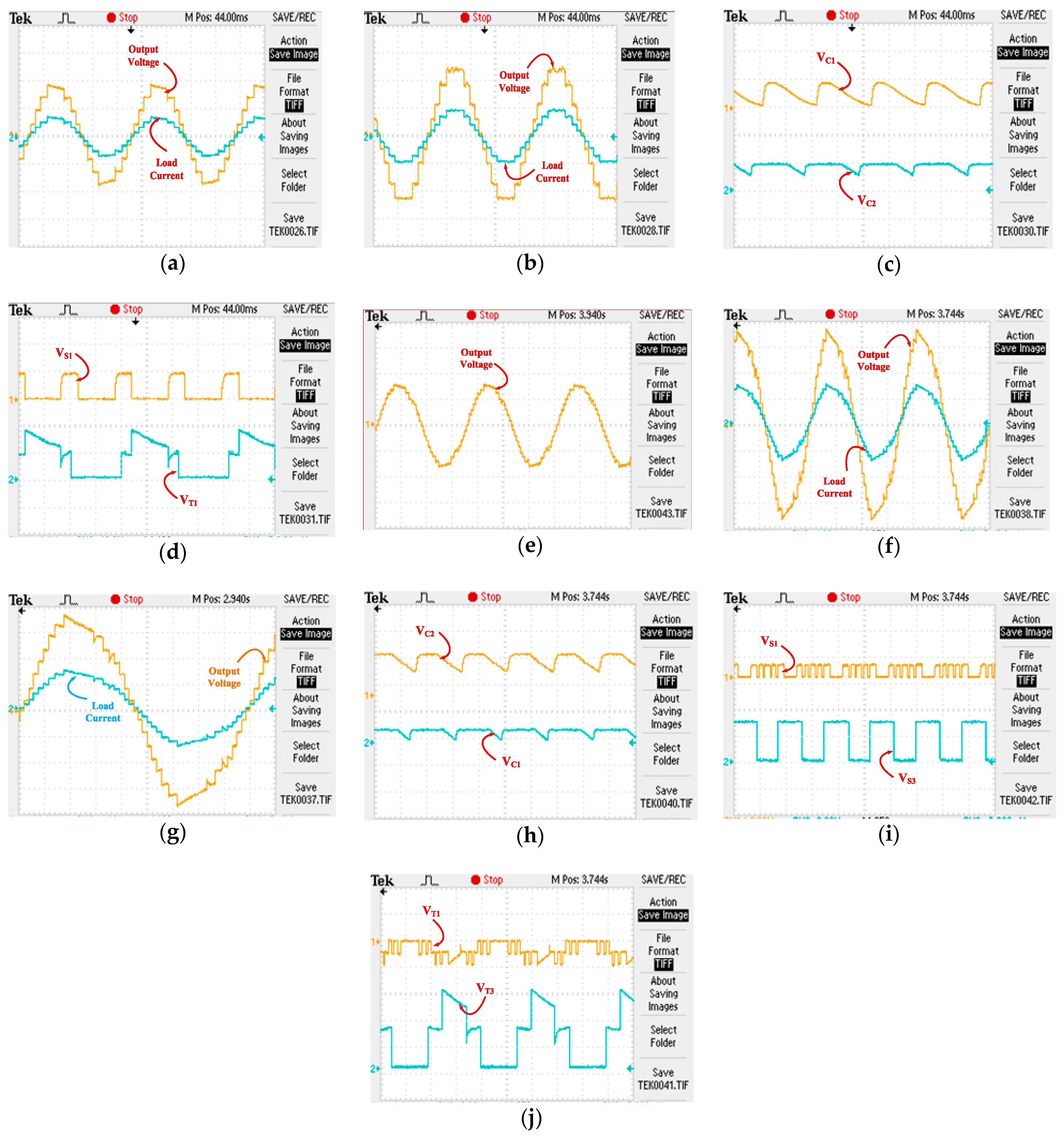

5. Simulation and Hardware Realization of the Basic Unit of the Proposed GSMLI Topologies

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, 17, 518–523. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel inverter topologies with reduced device count: A review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Alishah, R.S.; Sabahi, M.; Nazarpour, D.; Hosseini, S.H. Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches. IET Power Electron. 2014, 7, 3062–3071. [Google Scholar] [CrossRef]

- Zhang, Y.; Adam, G.P.; Lim, T.C.; Finney, S.J.; Williams, B.W. Hybrid Multilevel Converter: Capacitor Voltage Balancing Limits and its Extension. IEEE Trans. Ind. Inform. 2013, 9, 2063–2073. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medet alm-voltage multilevel converters; state of the art challenges and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Rodriguez, J.; Franquelo, L.G.; Kouro, S.; Leon, J.I.; Portillo, R.C.; Prats, M.A.M.; Perez, M.A. Multilevel converters: An enabling technology for high-power applications. Proc. IEEE 2009, 97, 1786–1817. [Google Scholar] [CrossRef]

- Roy, T.; Sadhu, P.K.; Dasgupta, A. Cross-Switched Multilevel Inverter Using Novel Switched Capacitor Converters. IEEE Trans. Ind. Electron. 2019, 66, 8521–8532. [Google Scholar] [CrossRef]

- Babaei, E.; Hosseini, S.H. New cascaded multilevel inverter topology with minimum number of switches. J. Energy Convers. Manag. 2009, 50, 2761–2767. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E.; Laali, S. Symmetric multilevel inverter with reduced components based on non-insulated dc voltage sources. IET Power Electron. 2012, 5, 571–581. [Google Scholar] [CrossRef]

- Alishah, R.S.; Nazarpour, D.; Hosseini, S.H.; Sabahi, M. New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels. IET Power Electron. 2014, 1, 96–104. [Google Scholar] [CrossRef]

- Siddique, M.D.; Saad, M.; Sarwar, A.; Alam, A.; Shah, N.M. Dual asymmetrical dc voltage source based switched capacitor boost multilevel inverter topology. IET Power Electron. 2020, 7, 1481–1486. [Google Scholar] [CrossRef]

- Waltrich, G.; Barbi, I. Three-phase cascaded multilevel inverter using power cells with two inverter legs in series. IEEE Trans. Ind. Electron. 2010, 57, 2605–2612. [Google Scholar] [CrossRef]

- Alishah, R.S.; Nazarpour, D.; Hosseini, S.H.; Sabahi, M. Reduction of power electronic elements in multilevel converters using a new cascade structure. IEEE Trans. Ind. Electron. 2015, 62, 256–269. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans. Ind. Electron. 2014, 61, 6664–6671. [Google Scholar] [CrossRef]

- Boora, K.; Kumar, J. General topology for asymmetrical multilevel inverter with reduced number of switches. IET Power Electron. 2017, 10, 2034–2041. [Google Scholar] [CrossRef]

- Banaei, M.R.; Salary, E. Verification of new family for cascade multilevel inverter switch reduction of components. J. Electr. Eng. Technol. 2011, 6, 245–254. [Google Scholar] [CrossRef]

- Banaei, M.R.; JannatiOskuee, M.R.; Khounjahan, H. Reconfiguration of semi-cascaded multilevel inverter to improve systems performance parameters. IET Power Electron. 2014, 7, 1106–1112. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H. Novel topologies for symmetric, asymmetric, and cascade switched-diode mutilevel converter with minimum number of power electronic components. IEEE Trans. Ind. Electron. 2014, 61, 5300–5310. [Google Scholar] [CrossRef]

- Hussan, M.R.; Sarwar, A.; Siddique, M.D.; Mekhilef, S.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. A Novel Switched-Capacitor Multilevel Inverter Topology for Energy Storage and Smart Grid Applications. Electronics 2020, 9, 1703. [Google Scholar] [CrossRef]

- Wang, L.; Wu, Q.H.; Tang, W. Novel Cascaded Switched-Diode Multilevel Inverter for Renewable Energy Integration. IEEE Trans. Energy Convers. 2017, 32, 1574–1582. [Google Scholar] [CrossRef]

- Abdullah, R.; Rahim, N.A.; Sheikh Raihan, S.R.; Ahmad, A.Z. Five-level diode-clamped inverter with three-level boost converter. IEEE Trans. Ind. Electron. 2014, 61, 5155–5163. [Google Scholar] [CrossRef]

- Khazraei, M.; Sepahvand, H.; Corzine, K.A.; Ferdowsi, M. Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters. IEEE Trans. Ind. Electron. 2012, 59, 769–778. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Control of dc capacitor voltages in diode-clamped multilevel inverter using bidirectional buck-boost choppers. IET Power Electron. 2012, 5, 1723–1732. [Google Scholar] [CrossRef]

- Mak, O.C.; Ioinovici, A. Switched-capacitor inverter with high power density and enhanced regulation capability. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1998, 45, 336–347. [Google Scholar]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal design of new cascaded switch-ladder multilevel inverter structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.; Sarwar, A.; Iqbal, A.; Tayyab, M.; Ansary, M.K. Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 86374–86383. [Google Scholar] [CrossRef]

- Lee, S.S.; Lee, K.; Alsofyani, I.M.; Bak, Y.; Wong, J.F. Improved Switched-Capacitor Integrated Multilevel Inverter with a DC Source String. IEEE Trans. Ind. Appl. 2019, 55, 7368–7376. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sarwar, A.; Memon, M.A. A New Single-Cascaded Multilevel Inverter Topology with Reduced Number of Switches and Voltage Stress. Int. Trans. Electr. Energy Syst. 2019. [Google Scholar] [CrossRef]

- Hosseini, S.H.; Alishah, R.S.; Gharehkoushan, A.Z. Enhancement of extracted maximum power from partially shaded multi-string PV panels using a new cascaded high step-up DC-DC-AC converter. In Proceedings of the 9th International Conference on Electrical and Electronics Engineering (ELECO 2015), Bursa, Turkey, 26–28 November 2015; pp. 644–648. [Google Scholar]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Liu, J.; Zhu, X.; Zeng, J. A Seven-level Inverter with Self-balancing and Low Voltage Stress. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 8, 685–696. [Google Scholar] [CrossRef]

| Parameters | n is the Number of Stages | NL is the Number of Levels | ||

|---|---|---|---|---|

| First Method | Second Method | First Method | Second Method | |

| NL | 8 + 8n + 1 | + 1 | NL | NL |

| Nsw | 8n + 2 | 8n + 2 | 2[−3+)] | 8log2[2 + )] − 14 |

| Ndri | 6n + 4 | 6n + 4 | [−2 + )] | 6log2[2 + )] − 8 |

| Ndiode | 2n | 2n | [−2 + )] | 2log2[2 + )] − 4 |

| Ncap | 2n | 2n | [−2 + )] | 2log2[2 + )] − 4 |

| States | Output Voltage(V0) | C1 | C2 | (V0) Symmetric (V1 = V2 = VC1 = VC2 = V) | (V0) Asymmetric (V1 = VC1 = V & V2 = VC2 = 3V) | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| A | 0V | 0 | 0 | 0 | 0 | 0 | 0 | c | c | 0V | 0V |

| B | V1 | 0 | 0 | 1 | 0 | 0 | 0 | - | - | V1 = V | V1 = V |

| C | V1 + VC1 | 1 | 0 | 1 | 0 | 0 | 0 | d | - | V1 + VC1 = 2V | V1 + VC1 = 2V |

| D | V2 | 0 | 0 | 0 | 0 | 1 | 0 | c | - | V2 = V | V2 = 3V |

| E | V1 + V2 | 0 | 0 | 1 | 0 | 1 | 0 | - | - | V1 + V2 = 2V | V1 + V2 = 4V |

| F | V1 + VC1 + V2 | 1 | 0 | 1 | 0 | 1 | 0 | d | - | V1 + VC1 + V2 = 3V | V1 + VC1 + V2 = 5V |

| G | V2 + VC2 | 0 | 1 | 0 | 0 | 1 | 0 | c | d | V2 + VC2 = 2V | V2 + VC2 = 6V |

| H | V1 + V2 + VC2 | 0 | 1 | 1 | 0 | 1 | 0 | - | d | V1 + V2 + VC2 = 3V | V1 + V2 + VC2 = 7V |

| I | V1 + VC1 + V2 + VC2 | 1 | 1 | 1 | 0 | 1 | 0 | d | d | V1 + VC1 + V2 + VC2= 4V | V1 + VC1 + V2 + VC2= 8V |

| J | −V1 | 0 | 0 | 0 | 1 | 0 | 0 | c | c | −V1 = −V | −V1 = −V |

| K | −(V1 + VC1) | 1 | 0 | 0 | 1 | 0 | 0 | d | - | −(V1 + VC1) = −2V | −(V1 + VC1) = −2V |

| L | −V2 | 0 | 0 | 0 | 0 | 0 | 1 | c | - | −V2 = −V | −V2 = −3V |

| M | −(V1 + V2) | 0 | 0 | 0 | 1 | 0 | 1 | - | - | −(V1 + V2) = −2V | −(V1 + V2) = −4V |

| N | −(V1 + VC1 + V2) | 1 | 0 | 0 | 1 | 0 | 1 | d | - | −(V1 + VC1 + V2) = −3V | −(V1 + VC1 + V2) = −5V |

| O | −(V2 + VC2) | 0 | 1 | 0 | 0 | 0 | 1 | c | d | −(V2 + VC2) = −2V | −(V2 + VC2) = −6V |

| P | −(V1 + V2 + VC2) | 0 | 1 | 0 | 1 | 0 | 1 | - | d | −(V1 + V2 + VC2) = −3V | −(V1 + V2 + VC2) = −7V |

| Q | −(V1 + VC1 + V2 + VC2) | 1 | 1 | 0 | 1 | 0 | 1 | d | d | −(V1 + VC1 + V2 + VC2) = −4V | −(V1 + VC1 + V2 + VC2) = −8V |

| Parameters | Attributes |

|---|---|

| Switches (T1 to S4) | IGBT/Diode |

| Switching frequency (fs) | 50 Hz |

| Load (purely resistive) | 100 Ω, |

| Capacitors C1,C2 | 2200 µF, 4300 µF |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Anas, M.; Sarwar, A.; Ahmad, A.; Alam, A.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. Generalized Structures for Switched-Capacitor Multilevel Inverter Topology for Energy Storage System Application. Appl. Sci. 2021, 11, 1319. https://doi.org/10.3390/app11031319

Anas M, Sarwar A, Ahmad A, Alam A, Ahmad S, Sharaf M, Zaindin M, Firdausi M. Generalized Structures for Switched-Capacitor Multilevel Inverter Topology for Energy Storage System Application. Applied Sciences. 2021; 11(3):1319. https://doi.org/10.3390/app11031319

Chicago/Turabian StyleAnas, Mu, Adil Sarwar, Anzar Ahmad, Afroz Alam, Shafiq Ahmad, Mohamed Sharaf, Mazen Zaindin, and Muhammad Firdausi. 2021. "Generalized Structures for Switched-Capacitor Multilevel Inverter Topology for Energy Storage System Application" Applied Sciences 11, no. 3: 1319. https://doi.org/10.3390/app11031319

APA StyleAnas, M., Sarwar, A., Ahmad, A., Alam, A., Ahmad, S., Sharaf, M., Zaindin, M., & Firdausi, M. (2021). Generalized Structures for Switched-Capacitor Multilevel Inverter Topology for Energy Storage System Application. Applied Sciences, 11(3), 1319. https://doi.org/10.3390/app11031319