HVdc Circuit Breakers: Prospects and Challenges

Abstract

1. Introduction

2. High Voltage Direct Current Networks

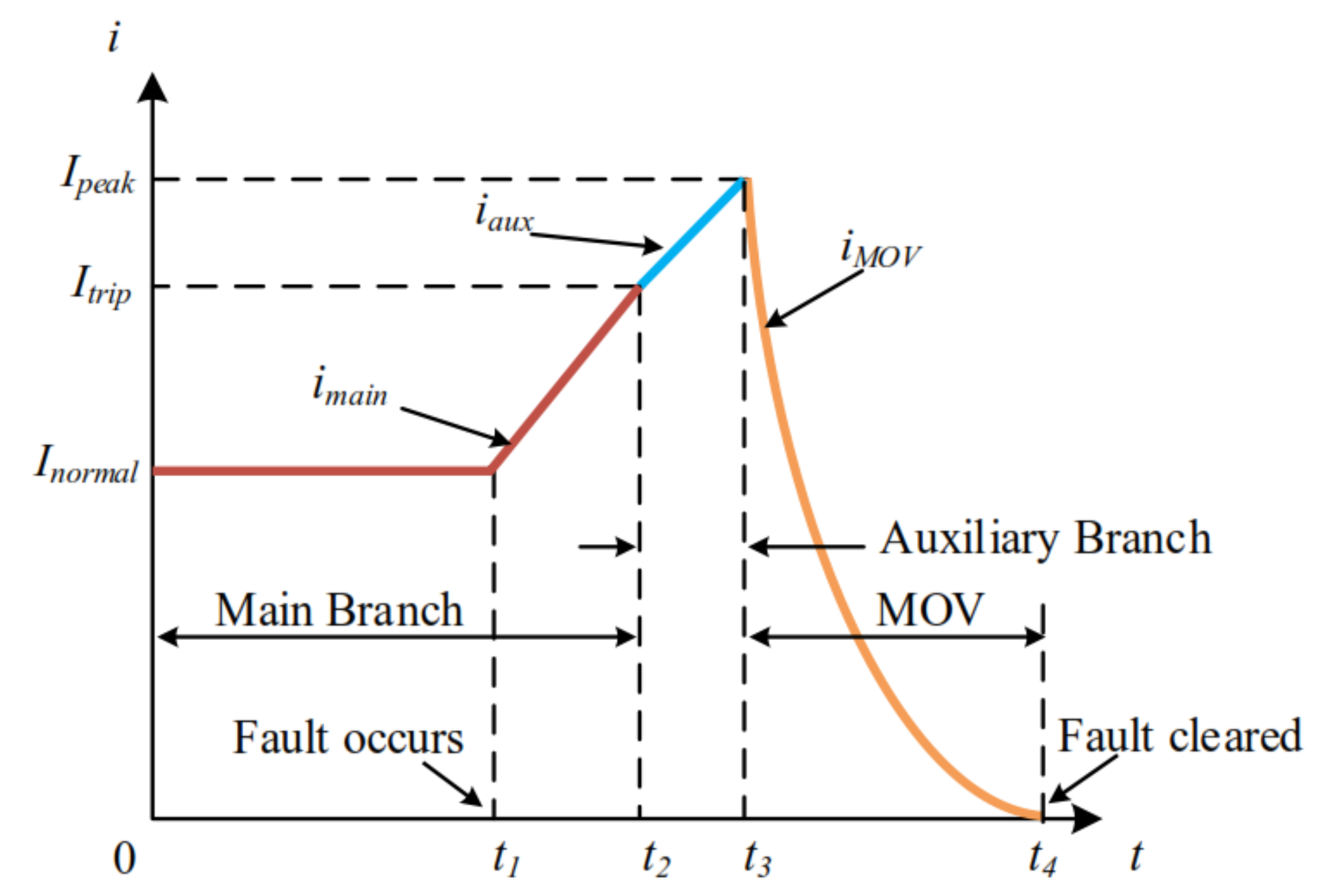

3. HVdc Circuit Breakers

- Develop a zero–crossing current to interrupt the fault current

- Must dissipate the stored energy of the inductance

- Able to hold the voltage profile of the system after the interruption of fault current

- The dc breaker must interrupt the fault current, as mentioned earlier, in the VSC–based M–HVdc system.

- The maximum voltage produced across the breaker must be within safe limits to coordinate with the system’s insulation. This is of prime importance when the system operates at a nominal voltage to switch heavy load currents.

Distinctiveness of HVdc Breakers

4. HVdc Circuit Breaker Topologies

4.1. Electro–Mechanical HVdc Breakers

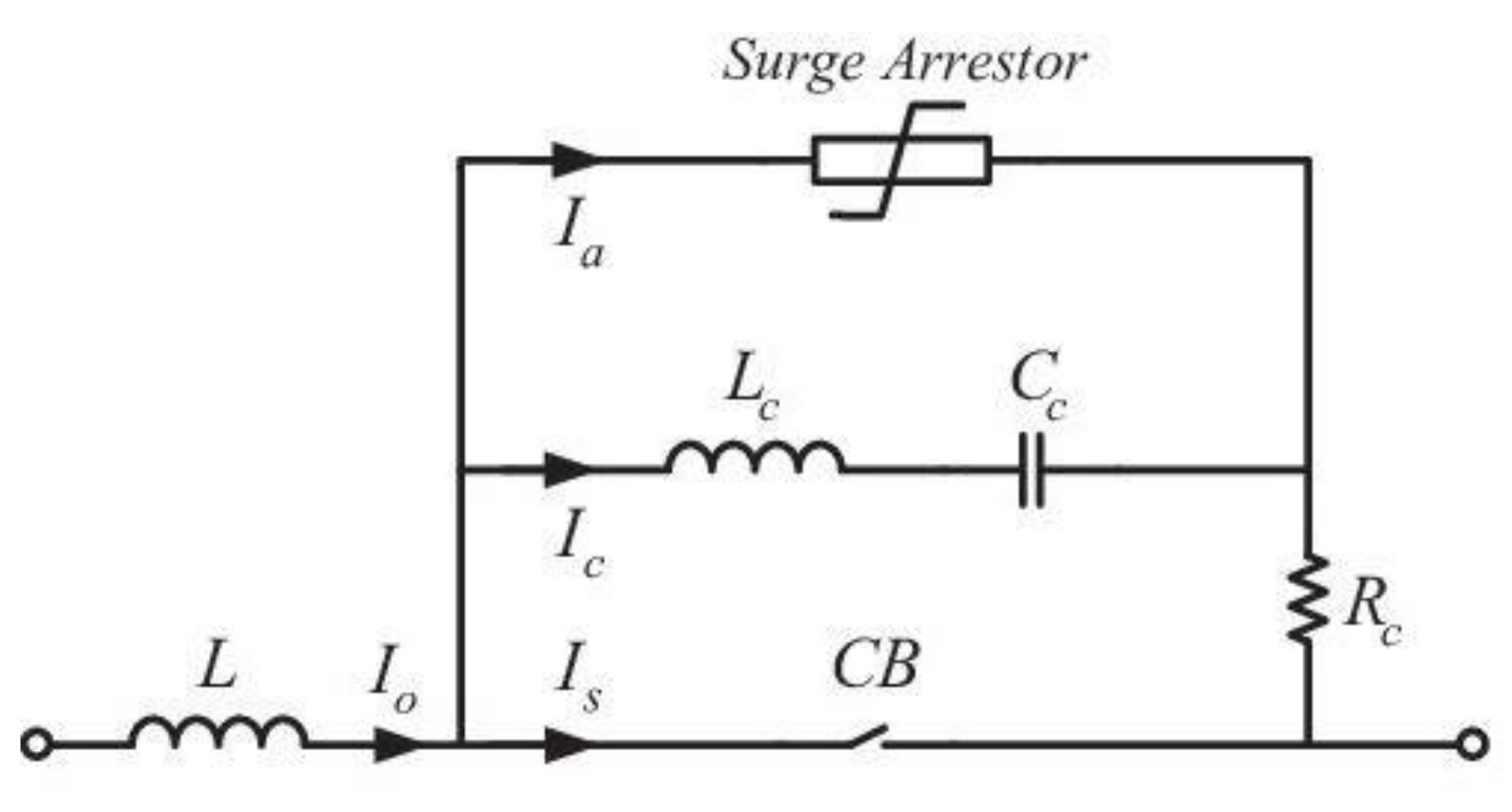

4.1.1. Electro–Mechanical Passive Resonance HVdc Breakers

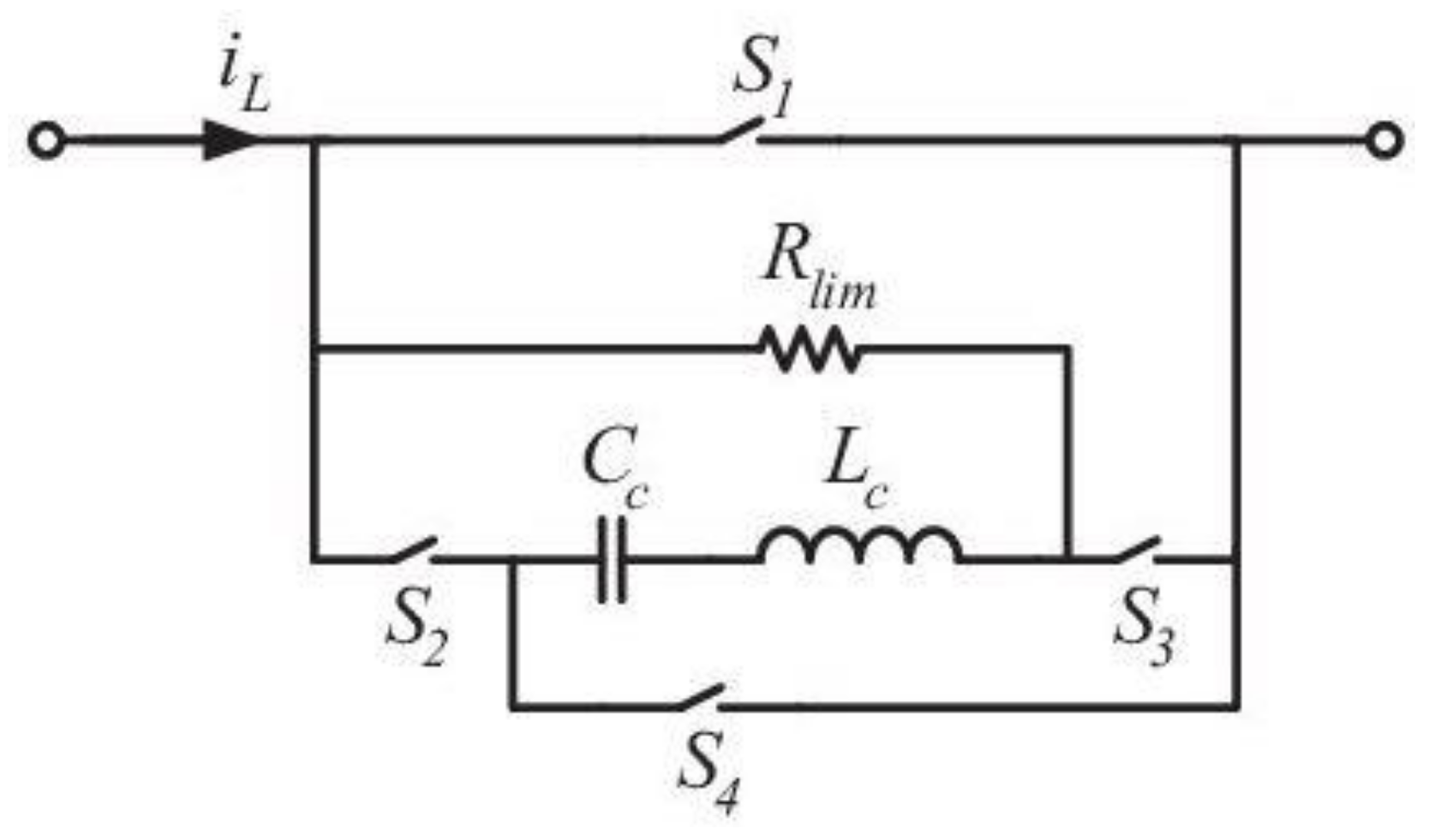

4.1.2. Electro–Mechanical Active Resonance HVdc Breakers

4.2. Solid State HVdc Breakers

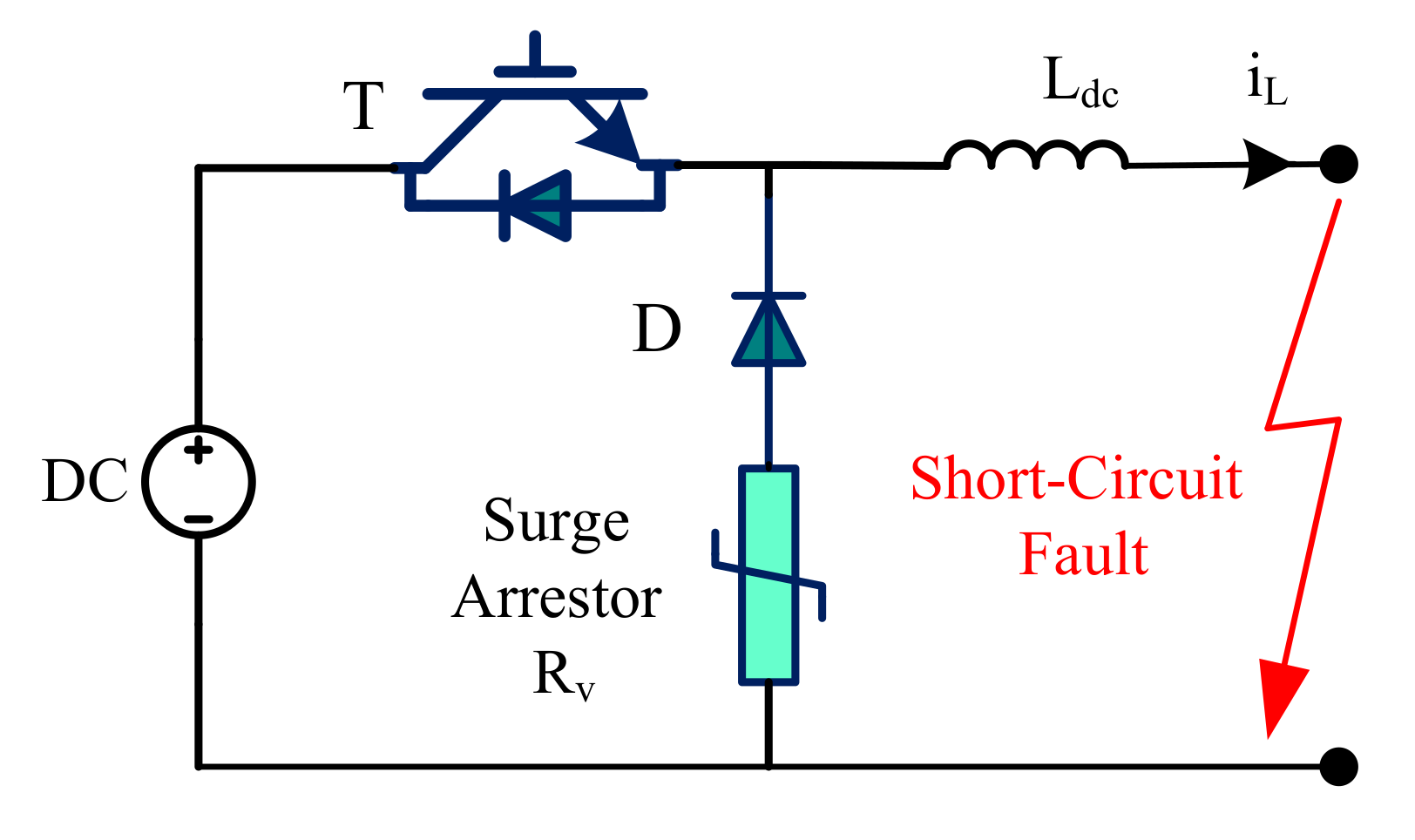

4.2.1. Solid State HVdc Breakers Employing Surge Arrestors (SA)

4.2.2. Solid State HVdc Breakers Employing Free–Wheeling Diode

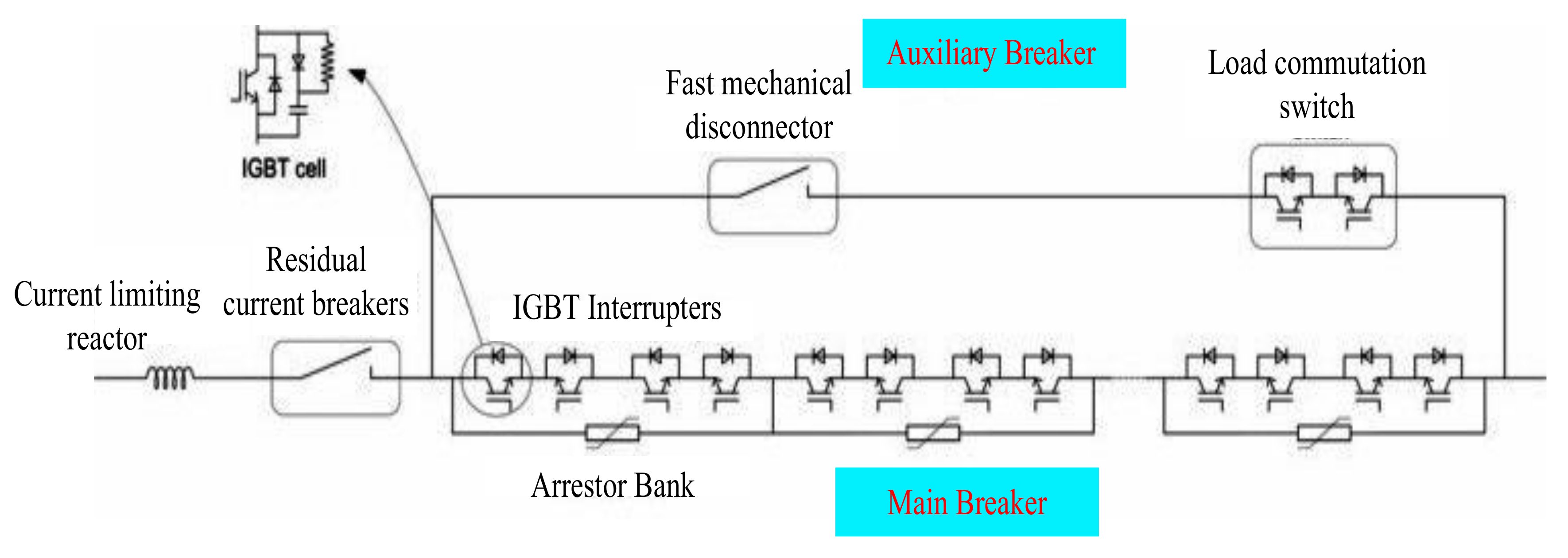

4.3. Hybrid HVdc Circuit Breakers

5. Comparison

5.1. Interruption Time

5.2. Power Losses

5.3. Voltage Rating

5.4. Current Rating

6. More Recent Activities and HVdc Breaker Related Technologies

6.1. Combined Optimization of HVdc Breaker’s Topology and Control

6.2. Standardization

6.3. Fault Current Limiters

6.4. Testing, Only HVdc Breakers Are Tested So Far

7. Available HVdc Breakers from Tech Giants

7.1. ABB’s Hybrid HVdc Breaker

7.2. Alstom’s Hybrid HVdc Breaker

7.3. General Electric’s Superfast Medium Voltage HVdc Breaker/Switch

8. Summary and Future Research Needs

- i.

- Improvements in the existing dc breaker topology can be fetched by optimizing the size of components such as; inductors, capacitors, varistors, etc. The goal is to reduce interruption time, size, and cost.

- ii.

- The switching arc’s oscillation growth and interruption capability can be optimized by studying the arc characteristics in detail under various vacuum and gas breaker conditions. Verification and derivation of the constraints are in mathematical arc models.

- iii.

- Comsol Multiphysics® simulations of dc arcs are recommended for high oscillatory current and during the interruption.

- iv.

- Medium–voltage dc breakers can be employed for high–voltage levels by enhancing the technology, series connections, or by smearing dc breakers across the medium–voltage levels in multilevel converter topologies.

- v.

- The use of hybrid dc breakers is recommended. As it can have features of both mechanical and solid–state breakers with reduced ratings of switches. Thus, size, cost, and interruption time are reduced.

- vi.

- Fast mechanical disconnectors with low on–state losses and high recovery of withstand voltage have sufficient arcing voltage for swift commutation. Such switches can be deployed in hybrid dc breakers for fast actions.

- vii.

- The use of new wide–bandgap power semiconductor devices (e.g., SiC or GaN) is recommended to have negligible on–state losses.

- viii.

- Active gate driving technologies that may improve the performance of semiconductor switches in a pure solid–state circuit breaker are recommended.

- ix.

- Integrated optimization of the whole M–HVdc system should be done to comply with the necessities of breaker–control protection.

- x.

- The standards and norms for the operation of multi–terminal HVdc systems must be defined to develop the proper dc–grid protection.

- xi.

- New testing methods for the dc breaker or its components should be designed. As dc breakers have strong network interaction, power–hardware–in–the–loop techniques would be advantageous.

- xii.

- GE Plasma switches that may operate at high temperature, more economical, and are adjusted in confined space of smaller footprints are recommended for medium dc voltage.

9. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chaudhuri, N.R.; Chaudhuri, B. Adaptive droop control for effective power–sharing in multi–terminal DC (MTDC) Grids. IEEE Trans. Power Syst. 2013, 28, 21–29. [Google Scholar] [CrossRef]

- Abdel–Khalik, A.S.; Massoud, A.M.; Elserougi, A.A.; Ahmed, S. Optimum power transmission–based droop control design for multi–terminal HVDC of offshore wind farms. IEEE Trans. Power Syst. 2013, 28, 3401–3409. [Google Scholar] [CrossRef]

- Raza, A.; Dianguo, X.; Yuchao, L.; Xunwen, S.; Williams, B.W.; Cecati, C. Coordinated Operation and Control of VSC Based Multiterminal High Voltage DC Transmission Systems. IEEE Trans. Sustain. Energy 2016, 7, 364–373. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Miranian, A.; Candela, J.; Luna, A.; Rodriguez, P. A generalized voltage droop strategy for control of multi–terminal dc grids. IEEE Trans. Ind. Appl. 2015, 51, 607–618. [Google Scholar] [CrossRef]

- Adam, G.P.; Williams, B.W. Multi–pole voltage source converter HVDC transmission systems. IET Gener. Transm. Distrib. 2016, 10, 496–507. [Google Scholar] [CrossRef]

- Feldman, R.; Tomasini, M.; Amankwah, E.; Clare, J.C.; Wheeler, P.W.; Trainer, D.R.; Whiteho, R.S. A hybrid modular multilevel voltage source converter for HVDC power transmission. IEEE Trans. Ind. Appl. 2013, 49, 1577–1588. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Miranian, A.; Luna, A.; Rodriguez, P. Optimized control of multi–terminal dc grids using particle swarm optimization. EPE J. 2014, 24, 1–9. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Miranian, A.; Candela, J.I.; Luna, A.; Rodriguez, P. Proposals for flexible operation of multi–terminal dc grids: Introducing flexible dc transmission system (FDCTS). In Proceedings of the ICRERA 2014 International Conference, Milwaukee, WI, USA, 19–22 October 2014; pp. 180–184. [Google Scholar]

- Dierckxsens, C.; Srivastava, K.; Reza, M.; Cole, S.; Beerten, J.; Belmans, R. A distributed DC voltage control method for VSC MTDC systems. Electr. Power Syst. Res. 2012, 82, 54–58. [Google Scholar] [CrossRef]

- Van Hertem, D.; Ghandhari, M. Multi–terminal VSC HVDC for the European supergrid: Obstacles. Renew. Sustain. Energy Rev. 2010, 14, 3156–3163. [Google Scholar] [CrossRef]

- Pierri, E.; Binder, O.; Hemdan, N.G.; Kurrat, M. Challenges and opportunities for a European HVDC grid. Renew. Sustain. Energy Rev. 2017, 70, 427–456. [Google Scholar] [CrossRef]

- Taggart, S.; James, G.; Dong, Z.; Russell, C. The Future of Renewables Linked by a Transnational Asian Grid. Proc. IEEE 2012, 100, 348–359. [Google Scholar] [CrossRef]

- Einsiedler, A. Enabling DESERTEC in EUMENA—Deutsche Bank; London, UK,, 28 September 2010. [Google Scholar]

- Ram, M.; Bogdanov, D.; Aghahosseini, A.; Oyewo, S.; Gulagi, A.; Child, M.; Breyer, C.; Fell, J.H. Global Energy System Based on 100% Renewable Energy—Power Sector; LUT Univeristy: Lappeenranta, Finland, 2019. [Google Scholar]

- Dai, J.; Phulpin, Y.; Sarlette, A.; Ernst, D. Coordinated primary frequency control among non–synchronous systems connected by a multi–terminal high–voltage direct current grid. Gener. Transm. Distrib. IET 2012, 6, 99–108. [Google Scholar] [CrossRef]

- Ruan, S.-Y.; Li, G.-J.; Jiao, X.-H.; Sun, Y.-Z.; Lie, T.T. Adaptive control design for VSC–HVDC systems based on backstepping method. Electr. Power Syst. Res. 2007, 77, 559–565. [Google Scholar] [CrossRef]

- Johnson, B.K.; Lasseter, R.H.; Alvarado, F.L.; Adapa, R. Expandable multi–terminal DC systems based on voltage–droop. IEEE Trans. Power Del. 1993, 8, 1926–1932. [Google Scholar] [CrossRef]

- Pérez-Molina, M.J.; Larruskain, D.M.; López, P.E.; Buigues, G. Challenges for protection of future HVDC grids. Front. Energy Res. 2020, 8, 33. [Google Scholar] [CrossRef]

- Greenwood, A.; Kanngiessner, K.; Lesclae, V.; Margaard, T.; Schultz, W. Circuit breakers for meshed multi–terminal HVDC systems. Part II: Switching of transmission lines in meshed MTDC systems. Electra 1996, 164, 62–82. [Google Scholar]

- Bergstrom, L.; Juhlin, L.-E.; Liss, G.; Svensson, S. Simulator study of multiterminal HVDC system performance. IEEE Trans. Power Appar. Syst. 1978, PAS-97, 2057–2066. [Google Scholar] [CrossRef]

- Choi, H.; Jeong, I.; Choi, H. Stability Improvement of DC Power System According to Applied DC Circuit Breaker Combined with Fault Current Limitation Characteristics of Superconductivity. IEEE Trans. Appl. Supercond. 2018, 28, 1–4. [Google Scholar] [CrossRef]

- Kanngiesser, K.; Ring, H.; Wess, T. Simulator study on line fault clearing by DC circuit breakers in a meshed MTDC system. In Proceedings of the International Conference on AC and DC Power Transmission, London, UK, 17–20 September 1991; pp. 102–107. [Google Scholar]

- Xiao, H.; Xu, Z.; Xiao, L.; Gan, C.; Xu, F.; Dai, L. Components sharing based integrated hvdc circuit breaker for meshed hvdc grids. IEEE Trans. Power Deliv. 2019, 35, 1856–1866. [Google Scholar] [CrossRef]

- Arrillaga, J. High. Voltage Direct Current Transmission, 2nd ed.; Short Run Press: Exeter, UK, 1998. [Google Scholar]

- Arrillaga, J.; Liu, Y.H.; Watson, N.R. Flexible Power Transmission: The HVDC Option; Wiley: Hoboken, NJ, USA, 2007. [Google Scholar]

- Bahrman, M.; Johnson, B. The ABCs of HVDC transmission technologies. IEEE Power Energy Mag. 2007, 5, 32–44. [Google Scholar] [CrossRef]

- Flourentzou, N.; Agelidis, V.; Demetriades, G. VSC–based HVDC power transmission systems: An overview. IEEE Trans. Power Electron. 2009, 24, 592–602. [Google Scholar] [CrossRef]

- Andersen, B.; Xu, L.; Horton, P.; Cartwright, P. Topologies for VSC transmission. Power Eng. J. 2002, 16, 142. [Google Scholar] [CrossRef]

- Guo, C.; Liu, Y.; Zhao, C.; Wei, X.; Xu, W. Power Component Fault Detection Method and Improved Current Order Limiter Control for Commutation Failure Mitigation in HVDC. IEEE Trans. Power Deliv. 2015, 30, 1585–1593. [Google Scholar] [CrossRef]

- Pang, H.; Tang, G.; He, Z. Evaluation of losses in VSC–HVDC transmission system. In Proceedings of the 2008 IEEE Power and Energy Society General Meeting—Conversion and Delivery of Electrical Energy in the 21st Century, Pittsburgh, PA, USA, 20–24 July 2008; pp. 1–6. [Google Scholar]

- Carlsson, L. Classical HVDC: Still continuing to evolve. Mod. Power Syst. 2002, 22, 19–21. [Google Scholar]

- Gole, A.; Meisingset, M. Capacitor commutated converters for long–cable HVDC transmission. Power Eng. J. 2002, 16, 129–134. [Google Scholar] [CrossRef]

- Vobecky, J. The current status of power semiconductors. Facta Univ. Ser. Electron. Energetics 2015, 28, 193–203. [Google Scholar] [CrossRef]

- Chen, L.; Li, G.; He, H.; Chen, H.; Li, Y.; Ding, M.; Zhang, X.; Xu, Y.; Ren, L.; Tang, Y. Study on coordination of resistive SFCLs and hybrid–type circuit breakers to protect a HVDC system with LCC and VSC stations. IEEE Trans. Appl. Supercond. 2020, 30, 1–6. [Google Scholar] [CrossRef]

- Schenk, M.; Przybilla, J.; Kellner-Werdehausen, U.; Barthelmess, R.; Dorn, J.; Sachs, G.; Uder, M.; Voelkel, S. State of the Art of Bipolar Semiconductors for Very High Power Applications. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 19–20 May 2015; pp. 1–8. [Google Scholar]

- Vobecky, J.; Botan, V.; Stiegler, K.; Meier, U.; Bellini, M. A novel ultra–low loss four inch thyristor for UHVDC. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 413–416. [Google Scholar]

- Daelemans, G.; Srivastava, K.; Reza, M.; Cole, S.; Belmans, R. Minimization of steady–state losses in meshed networks using VSC HVDC. In Proceedings of the IEEE Power & Energy Society General Meeting, Calgary, AB, Canada, 26–30 July 2009; pp. 1–5. [Google Scholar]

- Jie, Z.; Haibin, L.; Rui, X.; Li, L.; Wenhai, N.; Kun, S.; Feiyang, H.; Dapeng, L. Research of DC circuit breaker applied on Zhoushan multi–terminal VSC–HVDC project. In Proceedings of the 2016 IEEE PES Asia–Pacific Power and Energy Engineering Conference (APPEEC), Xi’an, China, 25–28 October 2016; pp. 1636–1640. [Google Scholar]

- Tang, L.; Ooi, B.-T. Protection of VSC–multi–terminal HVDC against DC faults. In Proceedings of the IEEE 33rd Annual IEEE Power Electronics Specialists Conference. Proceedings, Cairns, QLD, Australia, 23–27 June 2002; Volume 2, pp. 719–724. [Google Scholar]

- Allebrod, S.; Hamerski, R.; Marquardt, R. New transformerless, scalable modular multilevel converters for HVDC–transmission. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 174–179. [Google Scholar]

- Huang, H. Multilevel voltage–source converters for HVDC and FACTS application. In CIGRE SC B4 Bergen Colloqium; CIGRE: Paris, France, 2009; p. 401. [Google Scholar]

- Jacobson, B.; Kalsson, P.; Asplund, G.; Harnefors, L.; Jonsson, T. VSC–HVDC transmission with cascaded two–level converters. In CIGRE Session; CIGRE: Paris, France, 2010; pp. B4–B110. [Google Scholar]

- Trainer, D.; Davidson, C.; Oates, C.; MacLeod, N.; Critchley, D.; Crookes, R. A new hybrid voltage–source converter for HVDC power transmission. In CIGRE Session; CIGRE: Paris, France, 2010; pp. B4–B111. [Google Scholar]

- Adam, G.P.; Anaya-Lara, O.; Burt, G.M.; Telford, D.; Williams, B.W.; McDonald, J.R. Modular multilevel inverter: Pulse width modulation and capacitor balancing technique. IET Power Electron. 2010, 3, 702–715. [Google Scholar] [CrossRef]

- Adam, G.; Davidson, I. Robust and Generic Control of Full–Bridge Modular Multilevel Converter High–Voltage DC Transmission Systems. IEEE Power Electron. Trans. 2015, 30, 2468–2476. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; p. 6. [Google Scholar]

- Li, A.; Cai, Z.; Sun, Q.; Li, X.; Ren, D.; Yang, Z. Study on the dynamic performance characteristics of HVDC control and protections for the HVDC line fault. In Proceedings of the IEEE Power & Energy Society General Meeting, Calgary, AB, Canada, 26–30 July 2009; pp. 1–5. [Google Scholar]

- Qiang, S.; Wenhua, L.; Xiaoqian, L.; Hong, R.; Shukai, X.; Licheng, L. A Steady–State Analysis Method for a Modular Multilevel Converter. Power Electron. IEEE Trans. 2013, 28, 3702–3713. [Google Scholar]

- Glinka, M.; Marquardt, R. A new AC/AC multilevel converter family. IEEE Trans. Ind. Electron. 2005, 52, 662669. [Google Scholar] [CrossRef]

- Yousaf, M.Z.; Liu, H.; Raza, A.; Baig, M.B. Distribution, Primary and backup fault detection techniques for multi–terminal HVdc systems: A review. IET Gener. Transm. 2020, 14, 5261–5276. [Google Scholar] [CrossRef]

- Wang, C.; Jianhui, M.; Wang, Y. A novel protection scheme without DC circuit breaker for VSC-based DC grids. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 3169–3172. [Google Scholar]

- Takasaki, M.; Gibo, N.; Takenaka, K.; Hayashi, T.; Konishi, H.; Tanaka, S.; Ito, H. Control and protection scheme of HVDC system with selfcommutated converter in system fault conditions. Elect. Eng. Jpn. 2000, 132, 6–18. [Google Scholar] [CrossRef]

- Gibo, N.; Takenaka, K.; Verma, S.; Sugimoto, S.; Ogawa, S. Protection scheme of voltage sourced converters based HVDC system under DC fault. In Proceedings of the IEEE/PES Transmission and Distribution Conference and Exhibition, Yokohama, Japan, 6–10 October 2002; Volume 2, pp. 1320–1325. [Google Scholar]

- Lescale, V.; Kumar, A.; Juhlin, L.-E.; Bjorklund, H.; Nyberg, K. Challenges with multi–terminal UHVDC transmissions. In Proceedings of the POWERCON and IEEE Power India Conference, New Delhi, India, 12–15 October 2008. [Google Scholar]

- Long, W.; Reeve, J.; McNichol, J.; Holland, M.; Taisne, J.; LeMay, J. Application aspects of multi–terminal DC power transmission. IEEE Trans. Power Del. 1990, 5, 2084–2098. [Google Scholar] [CrossRef]

- Tang, L.; Ooi, B.-T. Locating and isolating DC faults in multi–terminal DC systems. IEEE Trans. Power Del. 2007, 22, 1877–1884. [Google Scholar] [CrossRef]

- Long, W.; Reeve, J.; Mcnichol, J.; Harrison, R.; Fletcher, D. Consideration for implementing multi–terminal dc systems. IEEE Trans. Power App. Syst. 1985, PAS-104, 2521–2530. [Google Scholar] [CrossRef]

- Gomis-Bellmunta, O.; Liangc, J.; Ekanayakec, J.; Kingc, R.; Jenkinsc, N. Topologies of multi–terminal HVDC–VSC transmission for large offshore wind farms. Electr. Power Syst. Res. 2011, 81, 271–281. [Google Scholar] [CrossRef]

- Reeve, J. Multiterminal HVDC power systems. IEEE Trans. Power Appar. Syst. PAS 1980, 99, 729–737. [Google Scholar] [CrossRef]

- Lamm, U.; Uhlmann, E.; Danfors, P. Some aspects of tapping HVDC transmission systems. Direct Curr. 1963, 8, 124–129. [Google Scholar]

- Reeve, J.; Arrillaga, J. Series connection of converter stations in an HVDC transmission system. Direct Curr. 1965, 10, 72–78. [Google Scholar]

- Bowles, J. Multiterminal HVDC transmission systems incorporating diode rectifier stations. IEEE Trans. Power App. Syst. 1981, PAS-100, 1674–1678. [Google Scholar] [CrossRef]

- Sakurai, T.; Goto, K.; Irokawa, S.; Imai, K.; Sakai, T. A new control method for multi–terminal HVDC transmission without fast communications systems. IEEE Trans. Power App. Syst. 1983, PAS-102, 1140–1150. [Google Scholar] [CrossRef]

- Nozari, F.; Grund, C.; Hauth, R. Current order coordination in multi–terminal DC systems. IEEE Trans. Power App. Syst. 1981; PAS-100, 4628–4635. [Google Scholar]

- Lu, W.; Ooi, B. Optimal acquisition and aggregation of offshore wind power by multi–terminal voltage–source HVDC. IEEE Trans. Power Del. 2003, 18, 201–206. [Google Scholar]

- Jovcic, D. Interconnecting offshore wind farms using multi–terminal VSC–based HVDC. In Proceedings of the IEEE Power Engineering Society General Meeting, Montreal, QC, Canada, 18–22 June 2006; p. 7. [Google Scholar]

- Ishikawa, M.; Horiuchi, S.; Irokawa, S.; Imai, K.; Hirose, S.; Sekiya, K.J. Simulator study of multiterminal HVDC transmission system without fast communication. IEEE Trans. Power Deliv. 1986, 1, 218–227. [Google Scholar] [CrossRef]

- Chen, H.; Wang, C.; Zhang, F.; Pan, W. Control strategy research of VSC based multiterminal HVDC system. In Proceedings of the 2006 IEEE PES Power Systems Conference and Exposition, Atlanta, GA, USA, 29 October–1 November 2006; pp. 1986–1990. [Google Scholar]

- Li, G.; Yin, M.; Zhou, M.; Zhao, C. Decoupling control for multiterminal VSC–HVDC based wind farm interconnection. In Proceedings of the 2007 IEEE Power Engineering Society General Meeting, Tampa, FL, USA, 24–28 June 2007; pp. 1–6. [Google Scholar]

- Raza, A.; Akhtar, A.; Jamil, M.; Abbas, G.; Gilani, S.O.; Yuchao, L.; Khan, M.N.; Izhar, T.; Dianguo, X.; Williams, B.W. A protection scheme for multi–terminal VSC–HVDC transmission systems. IEEE Access 2017, 6, 3159–3166. [Google Scholar] [CrossRef]

- Liu, H.; Xu, Z.; Huang, Y. Study of protection strategy for VSC based HVDC system. In Proceedings of the 2003 IEEE PES Transmission and Distribution Conference and Exposition (IEEE Cat. No. 03CH37495), Dallas, TX, USA, 7–12 September 2003; Volume 1, pp. 49–54. [Google Scholar]

- Franck, C.M.J. HVDC circuit breakers: A review identifying future research needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Mitra, B.; Chowdhury, B.; Willis, A. Protection coordination for assembly HVDC breakers for HVDC multiterminal grids using wavelet transform. IEEE Syst. J. 2019, 14, 1069–1079. [Google Scholar] [CrossRef]

- Kalair, A.; Abas, N.; Khan, N.J. Comparative study of HVAC and HVDC transmission systems. Renew. Sustain. Energy Rev. 2016, 59, 1653–1675. [Google Scholar] [CrossRef]

- Bucher, M.K.; Walter, M.M.; Pfeiffer, M.; Franck, C.M. Options for ground fault clearance in HVDC offshore networks. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 2880–2887. [Google Scholar]

- Faulkner, R.W. Commutating Circuit Breaker. U.S. Patent US8890019, 18 November 2014. [Google Scholar]

- Melvold, D.J.; Shockley, P.R.; Long, W.F.; Hingorani, N.G. Three terminal operation of the Pacific HVDC Intertie for dc circuit breaker testing. IEEE Trans. Power Appar. 1976, 95, 1287–1296. [Google Scholar] [CrossRef]

- Chaudhuri, N.; Chaudhuri, B.; Majumder, R.; Yazdani, A. Multi–Terminal Direct–Current Grids: Modeling, Analysis, and Control.; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Marland, M. Alternatives to SF6 in HV Circuit Breaker Insulation. Bachelor Thesis, University of Southern Queensland, Toowoomba, Australia, 2014. [Google Scholar]

- Callavik, M.; Blomberg, A.; Häfner, J.; Jacobson, B.J. The hybrid HVDC breaker. ABB Grid Syst. Tech. Pap. 2012, 361, 143–152. [Google Scholar]

- Bonkarev, M. Concept Analysis for High.–Voltage Direct–Current Circuit Breakers for Application in a Network of HVDC Transmission. Master’s Thesis, Brandenburg University of Technology, Cottbus, Germany, 2015. [Google Scholar]

- Sima, W.; Fu, Z.; Yang, M.; Yuan, T.; Sun, P.; Han, X.; Si, Y. A novel active mechanical HVDC breaker with consecutive interruption capability for fault clearances in MMC–HVDC systems. IEEE Trans. Ind. Electron. 2018, 66, 6979–6989. [Google Scholar] [CrossRef]

- Wu, Y.; Rong, M.; Wu, Y.; Yang, F.; Yi, Q. Damping HVDC circuit breaker with current commutation and limiting integrated. IEEE Trans. Ind. Electron. 2020, 67, 10433–10441. [Google Scholar] [CrossRef]

- Abedrabbo, M.; Leterme, W.; van Hertem, D. Systematic approach to HVDC circuit breaker sizing. IEEE Trans. Power Deliv. 2019, 35, 288–300. [Google Scholar] [CrossRef]

- Song, Y.; Sun, J.; Saeedifard, M.; Ji, S.; Zhu, L.; Meliopoulos, A.S. Optimum selection of circuit breaker parameters based on analytical calculation of overcurrent and overvoltage in multiterminal HVDC grids. IEEE Trans. Ind. Electron. 2019, 67, 4133–4143. [Google Scholar] [CrossRef]

- Sneath, J.; Rajapakse, A.D. Fault detection and interruption in an earthed HVDC grid using ROCOV and hybrid DC breakers. IEEE Trans. Power Deliv. 2014, 31, 973–981. [Google Scholar] [CrossRef]

- Xiang, W.; Yang, S.; Xu, L.; Zhang, J.; Lin, W.; Wen, J. A transient voltage–based DC fault line protection scheme for MMC–based DC grid embedding DC breakers. IEEE Trans. Power Deliv. 2018, 34, 334–345. [Google Scholar] [CrossRef]

- Abramovitz, A.; Smedley, M.J. Survey of solid–state fault current limiters. IEEE Trans. Power Electron. 2012, 27, 2770–2782. [Google Scholar] [CrossRef]

- Muriuki, J.; Muriithi, C.; Ngoo, L.; Nyakoe, G.J. Review of hvdc circuit breakers topologies. J. Electr. Electron. Eng. 2017, 12, 109–117. [Google Scholar] [CrossRef]

- Jovcic, D.; Van Hertem, D.; Linden, K.; Taisne, J.P.; Grieshaber, W. Feasibility of DC transmission networks. In Proceedings of the 2011 2nd IEEE PES International Conference and Exhibition on Innovative Smart Grid Technologies, Manchester, UK, 5–7 December 2011; pp. 1–8. [Google Scholar]

- Zhou, Y.; Huang, Y.; Liu, H.; Tai, Y.; Yang, H.; Men, B. Research and development of 500kV hybrid HVDC circuit breaker with current commutation drive circuit. In Proceedings of the 2019 4th IEEE Workshop on the Electronic Grid (eGRID), Xiamen, China, 11–14 November 2019; pp. 1–6. [Google Scholar]

- Senda, T.; Tamagawa, T.; Higuchi, K.; Horiuchi, T.; Yanabu, S. Development of HVDC circuit breaker based on hybrid interruption scheme. IEEE Trans. Power Appar. Syst. 1984, PER-4, 545–552. [Google Scholar] [CrossRef]

- Barnes, M.; Vilchis–Rodriguez, D.S.; Pei, X.; Shuttleworth, R.; Cwikowski, O.; Smith, A.C. HVDC Circuit Breakers—A Review. IEEE Access 2020, 8, 211829–211848. [Google Scholar] [CrossRef]

- Du, C.; Wang, C. Review of DC Circuit Breaker Technology for HVDC Application. In Proceedings of the 2019 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 11–14 August 2019; pp. 1–6. [Google Scholar]

- Sano, K.; Takasaki, M. A surge–less solid–state dc circuit breaker for voltage source converter based HVDC transmission systems. In Proceedings of the 2012 IEEE Energy Conversion Congress And Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 4426–4431. [Google Scholar]

- Magnusson, J.; Saers, R.; Liljestrand, L.; Engdahl, G.J. Separation of the energy absorption and overvoltage protection in solid–state breakers by the use of parallel varistors. IEEE Trans. Power Electron. 2013, 29, 2715–2722. [Google Scholar] [CrossRef]

- Available online: http://www2.ee.ic.ac.uk/patrick.sterling10/yr2proj/TechSSCBs.htm (accessed on 24 January 2021).

- Kostoulas, N.; Sitokonstantinou, V.; Idris, M.; Sterling, P.; Sayed, S.; Karaiskos, P. DC Circuit Breakers and Their Use in HVDC grids. Technical Report. 2012. Available online: http://www2.ee.ic.ac.uk/nikolaos.kostoulas10/yr2proj/HVDC%20Circuit%20Breakers%20Report.pdf (accessed on 24 January 2021).

- Shukla, A.; Demetriades, G.D.J. A survey on hybrid circuit–breaker topologies. IEEE Trans. Power Deliv. 2014, 30, 627–641. [Google Scholar] [CrossRef]

- Zhao, S.; Yan, X.; Wang, B.; Wang, E.; Ma, L. Research on reliability evaluation method of DC circuit breaker based on Markov model. Electr. Power Syst. Res. 2019, 173, 1–5. [Google Scholar] [CrossRef]

- Whitehouse, R.J. HVDC breakers & grid protection: Why, what & when? In EES–UETP Course on HVDC HVDC Grids for Future Transmission; KU Leuven: Leuven, Belgium, 2013. [Google Scholar]

- Van Hertem, D.; Gomis, O.G.; Liang, J. HVDC Grids for Offshore and Super Grids of Future; IEEE Press: Piscataway, NJ, USA; Wiley: Hoboken, NJ, USA, 2017. [Google Scholar]

- Davidson, C.; Whitehouse, R.; Barker, C.; Dupraz, J.-P.; Grieshaber, W. A New Ultra–Fast HVDC Circuit Breaker for Meshed DC Networks. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Brimingham, UK, 10–12 February 2015. [Google Scholar]

- Callavik, M.; Bahrman, M.; Sandeberg, P. Technology developments and plans to solve operational challenges facilitating the HVDC offshore grid. In Proceedings of the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, USA, 22–26 July 2012; pp. 1–6. [Google Scholar]

- Pauli, B.; Mauthe, G.; Ruoss, E.; Ecklin, G.J. Development of a high current HVDC circuit breaker with fast fault clearing capability. IEEE Trans. Power Deliv. 1988, 3, 2072–2080. [Google Scholar] [CrossRef]

- Greenwood, A.; Lee, T.J. Theory and application of the commutation principle for HVDC circuit breakers. IEEE Trans. Power Appar. Syst. 1972, PAS-91, 1570–1574. [Google Scholar] [CrossRef]

- Bini, R.; Backman, M.; Hassanpoor, A. Interruption technologies for HVDC transmission: State–of–art and outlook. In Proceedings of the 2017 4th International Conference on Electric Power Equipment–Switching Technology (ICEPE–ST), Xi’an, China, 22–25 October 2017; pp. 318–323. [Google Scholar]

- Steurer, M.; Frohlich, K.; Holaus, W.; Kaltenegger, K.J. A novel hybrid current–limiting circuit breaker for medium voltage: Principle and test results. IEEE Trans. Power Deliv. 2003, 18, 460–467. [Google Scholar] [CrossRef]

- Holaus, W.; Frohlich, K. Ultra–fast switches–a new element for medium voltage fault current limiting switchgear. In Proceedings of the 2002 IEEE Power Engineering Society Winter Meeting, Conference Proceedings (Cat. No. 02CH37309). New York, NY, USA, 27–31 January 2002; Volume 1, pp. 299–304. [Google Scholar]

- Rodrigues, R.; Du, Y.; Antoniazzi, A.; Cairoli, P. A review of solid–state circuit breakers. IEEE Trans. Power Electron. 2020, 36, 364–377. [Google Scholar] [CrossRef]

- Tahata, K.; El Oukaili, S.; Kamei, K.; Yoshida, D.; Kono, Y.; Yamamoto, R.; Ito, H. HVDC Circuit Breakers for HVDC Grid Applications. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Briminghem, UK, 10–12 February 2015. [Google Scholar]

- Koldby, E.; Hyttinen, M. Challenges on the Road to an Offshore HVDC Grid. In Proceedings of the Nordic Wind Power Conference, Bornholm, Denmark, 10–11 September 2009; Volume 19. [Google Scholar]

- Jayamaha, D.; Lidula, N.; Rajapakse, A. Protection and grounding methods in DC microgrids: Comprehensive review and analysis. Renew. Sustain. Energy Rev. 2020, 120, 109631. [Google Scholar] [CrossRef]

- Meyer, C.; Kowal, M.; de Doncker, R.W. Circuit breaker concepts for future high–power DC–applications. In Proceedings of the Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference, Hong Kong, China, 2–6 October 2005; Volume 2, pp. 860–866. [Google Scholar]

- Wang, Y.; Aksoz, A.; Geury, T.; Ozturk, S.B.; Kivanc, O.C.; Hegazy, O. A Review of Modular Multilevel Converters for Stationary Applications. Appl. Sci. 2020, 10, 7719. [Google Scholar] [CrossRef]

- Liu, Y.; Arrillaga, J.; Watson, N.J. Addition of four–quadrant power controllability to multi–level VSC HVDC transmission. IET Gener. Transm. Distrib. 2007, 1, 872–878. [Google Scholar] [CrossRef]

- Ansari, J.A.; Liu, C.; Khan, S.A. MMC Based MTDC Grids: A Detailed Review on Issues and Challenges for Operation, Control and Protection Schemes. IEEE Access 2020, 8, 168154–168165. [Google Scholar] [CrossRef]

- An, T.; Tang, G.; Wang, W. Research and application on multi–terminal and DC grids based on VSC–HVDC technology in China. High. Volt. 2017, 2, 1–10. [Google Scholar] [CrossRef]

- Liu, Z.; Mirhosseini, S.S.; Popov, M.; Audichya, Y.; Colangelo, D.; Jamali, S.; Palensky, P.; Hu, W.; Chen, Z. Protection Testing for Multiterminal High–Voltage dc Grid: Procedures and. IEEE Ind. Electron. Mag. 2020, 14, 46–64. [Google Scholar] [CrossRef]

- Steurer, M.; Fröhlich, K. Current Limiters–State of the Art. In Proceedings of the Fourth Workshop and Conference on EHV Technology, Indian Institute of Science, Bangalore, India, 17–18 July 1998. [Google Scholar]

- CIGRE. A3. 10:“Fault Current Limiters in Electrical Medium and High. Voltage Systems”; CIGRE: Paris, France, 2003. [Google Scholar]

- Meyer, C.; Schroder, S.; de Doncker, R.W.J. Solid–state circuit breakers and current limiters for medium–voltage systems having distributed power systems. IEEE Trans. Power Electron. 2004, 19, 1333–1340. [Google Scholar] [CrossRef]

- Smith, R.; Slade, P.; Sarkozi, M.; Stacey, E.; Bonk, J.; Mehta, H.J. Solid–state distribution current limiter and circuit breaker: Application requirements and control strategies. IEEE Trans. Power Deliv. 1993, 8, 1155–1164. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Rouzbehi, K.; Pou, J. A DC-Reactor-Based Solid-State Fault Current Limiter for HVdc Applications. IEEE Trans. Power Deliv. 2019, 34, 720–728. [Google Scholar] [CrossRef]

- Wright, A.; Newbery, P.G. Electric Fuses; IET: England, UK, 2004. [Google Scholar]

- Saqib, M.; Stokes, A.J. Arc behavior and confinement in a high–voltage, high breaking capacity fuse filler. IEEE Trans. Power Deliv. 2009, 25, 212–220. [Google Scholar] [CrossRef]

- Noe, M.; Steurer, M. High–temperature superconductor fault current limiters: Concepts, applications, and development status. Supercond. Sci. 2007, 20, R15. [Google Scholar] [CrossRef]

- Schultz, T.; Herzog, P.; Franck, C.M. Interruption limits of mechanical circuit breakers and circuit upgrades for current injection in HVDC circuit breakers. High. Volt. 2020, 5, 334–342. [Google Scholar] [CrossRef]

- Belda, N.A.; Smeets, R.P.P.; Nijman, R.M. Experimental investigation of electrical stresses on the main components of HVDC circuit breakers. IEEE Trans. Power Deliv. 2020, 35, 2762–2771. [Google Scholar] [CrossRef]

- Andersson, D.; Henriksson, A. Passive and active DC breakers in the three Gorges–Changzhou HVDC Project. 2001. Available online: https://www.semanticscholar.org/paper/Passive-and-Active-DC-Breakers-in-the-Three-HVDC-Andersson-Henriksson/c4143a649bb72a9b09fc14e7237d8c9f4e3b7a87 (accessed on 20 April 2021).

- Brumshagen, H. Uber die Prüfung von Schalteinrichtungen für Die Hochspannungs–Gleichstrom–Übertragung; Technische Universität Carolo–Wilhelmina zu Braunschweig: Brunswick, Germany, 1975. [Google Scholar]

- McLaren, P.; Kuffel, R.; Wierckx, R.; Giesbrecht, J.; Arendt, L.J. A real time digital simulator for testing relays. IEEE Trans. Power Deliv. 1992, 7, 207–213. [Google Scholar] [CrossRef]

- Terwiesch, P.; Keller, T.; Scheiben, E.J. Rail vehicle control system integration testing using digital hardware–in–the–loop simulation. IEEE Trans. Control. Syst. Technol. 1999, 7, 352–362. [Google Scholar] [CrossRef][Green Version]

- Steurer, M.; Edrington, C.S.; Sloderbeck, M.; Ren, W.; Langston, J.J. A megawatt–scale power hardware–in–the–loop simulation setup for motor drives. IEEE Trans. Ind. Electron. 2009, 57, 1254–1260. [Google Scholar] [CrossRef]

- Schacherer, C.; Langston, J.; Steurer, M.; Noe, M.J. Power hardware–in–the–loop testing of a YBCO coated conductor fault current limiting module. IEEE Trans. Appl. Supercond. 2009, 19, 1801–1805. [Google Scholar] [CrossRef]

- Martinez-Velasco, J.A.; Magnusson, J.J. Parametric analysis of the hybrid HVDC circuit breaker. Int. J. Electr. Power Energy Syst. 2017, 84, 284–295. [Google Scholar] [CrossRef]

- Nguyen, A.-D.; Nguyen, T.-T.; Kim, H.-M.J. A comparison of different hybrid direct current circuit breakers for application in HVDC system. Int. J. Control. Autom. 2016, 9, 381–394. [Google Scholar] [CrossRef]

- Hafner, J. Proactive Hybrid HVDC Breakers–A key innovation for reliable HVDC grids. In Proceedings of the CIGRE Bologna Symposium, Bologna, Italy, 13–15 September 2011; pp. 1–8. [Google Scholar]

- Raza, A.; Dianguo, X.; Xunwen, S.; Weixing, L.; Williams, B.W.J. A novel multiterminal VSC–HVdc transmission topology for offshore wind farms. IEEE Trans. Ind. Appl. 2016, 53, 1316–1325. [Google Scholar] [CrossRef]

- Available online: https://www.ge.com/news/reports/switch–superfast–dc–circuit–breaker–unlock–renewables–full–potential (accessed on 7 January 2021).

- Available online: https://arpa–e.energy.gov/technologies/projects/ultra–efficient–intelligent–mvdc–hybrid–circuit–breaker (accessed on 7 January 2021).

| Country | Project Name | Specifications | |||

|---|---|---|---|---|---|

| Year | Length (km) | Rating (MW) | Dc–Link (kV) | ||

| China | Jinpin Sunan | 2012 | 2093 | 7200 | ±800 |

| Brazil | Rio Madeira | 2013 | 2375 | 2 × 3150 | ±600 |

| India | Biswanath Agra | 2014 | 1728 | 6000 | ±800 |

| China | Xiluodu Zhejiang | 2014 | 1688 | 8000 | ±800 |

| China | Zhundong Sichuan | 2015 | 2600 | 10,000 | ±1100 |

| Country | Project Name | Specifications | |||

|---|---|---|---|---|---|

| Year | Length (km) | Rating (MW) | Dc–Link (kV) | ||

| China | Nan’ao | 2013 | 09 subsea | 200 | ±160 |

| China | Dalian city | 2013 | 43 subsea | 1000 | ±320 |

| Namibia | Caprivi link | 2010 | 951 | 300 | ±350 |

| Norway | Skagerrak 4 | 2014 | 244 | 700 | ±500 |

| France | Inelfe | 2013 | 65 | 1000 | ±320 |

| Property | LCC–HVdc | VSC–HVdc |

|---|---|---|

| Basic building block | Thyristor | IGBT |

| Control of dc grid in the event of dc fault | Control phase angle | Converter control is lost due to diodes |

| Harmonics | Strong low order harmonics | Weak high order harmonics |

| P/Q | Unidirectional, consume a large amount of reactive power | Fully controlled P and Q in both directions |

| Available power ratings | 800 kV, 6400 MW | 400–800 MW, 300 kV |

| Power flow direction | Reversal of poles voltage | Stiff voltage achieved by adjusting PWM |

| Black start | No | Yes |

| The dc inductors | Large | Small |

| The dc capacitors | Small | Large |

| The dc fault current | The rate of increasing a fault current is low and controllable | The rate of growth of a fault current is very high and uncontrollable |

| LCC–HVdc | Benefits | Demerits |

| High power and voltage ratings | dc–link collapse due to commutation failure | |

| Fewer losses | Large consumption of reactive power | |

| Low rate of rising a fault current | Vulnerable to ac side faults | |

| VSC–HVdc | Suitable for cables than overhead lines | Vulnerable to dc side faults The high rate of rising a fault current |

| Soft power reversal No need for voltage polarity reversal | Higher losses | |

| Stiff dc–link voltage | Low power and voltage ratings |

| Types of CB | Interruption Time | Power Losses | Voltage Rating | Current Rating | Cost [105] | Maintenance | Life Span |

|---|---|---|---|---|---|---|---|

| Electro–mechanical | –60 ms | 0.001% | Max. 550 kV | Up to 4–8 kA | High | Required—High | Longest |

| Solid state | <1 ms | 30% | 120–320 kV | 16 kA | Low | Required—Low | Long |

| Hybrid | 2–30 ms | 0.1% | 800 kV exp. | 9–16 kA | Medium | Required—Medium | Longer |

| Type of CB | Alstom | ABB | GE |

|---|---|---|---|

| Size | Large | Medium | Reduced |

| Cooling | Required | Required | Not required |

| On–state losses | Low | High (0.01% of transmitted Power (>Alstom) | Reduced |

| Interruption speed | Medium | High (few ms > Alstom) | High |

| Auxiliary branch | Thyristor stacks in series with a capacitor | IGBT switch with ultra fast disconnector | –– |

| Cost | Lower for HVDC | Lower for MVDC | Reduced |

| Interruption capability | Uni–directional | Bi–directional | –– |

| Suitability | High voltage dc/LCC | MVdc/VSC | MVdc |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Raza, A.; Mustafa, A.; Alqasemi, U.; Rouzbehi, K.; Muzzammel, R.; Guobing, S.; Abbas, G. HVdc Circuit Breakers: Prospects and Challenges. Appl. Sci. 2021, 11, 5047. https://doi.org/10.3390/app11115047

Raza A, Mustafa A, Alqasemi U, Rouzbehi K, Muzzammel R, Guobing S, Abbas G. HVdc Circuit Breakers: Prospects and Challenges. Applied Sciences. 2021; 11(11):5047. https://doi.org/10.3390/app11115047

Chicago/Turabian StyleRaza, Ali, Ali Mustafa, Umar Alqasemi, Kumars Rouzbehi, Raheel Muzzammel, Song Guobing, and Ghulam Abbas. 2021. "HVdc Circuit Breakers: Prospects and Challenges" Applied Sciences 11, no. 11: 5047. https://doi.org/10.3390/app11115047

APA StyleRaza, A., Mustafa, A., Alqasemi, U., Rouzbehi, K., Muzzammel, R., Guobing, S., & Abbas, G. (2021). HVdc Circuit Breakers: Prospects and Challenges. Applied Sciences, 11(11), 5047. https://doi.org/10.3390/app11115047