A Novel Prefix Cache with Two-Level Bloom Filters in IP Address Lookup

Abstract

1. Introduction

2. Background

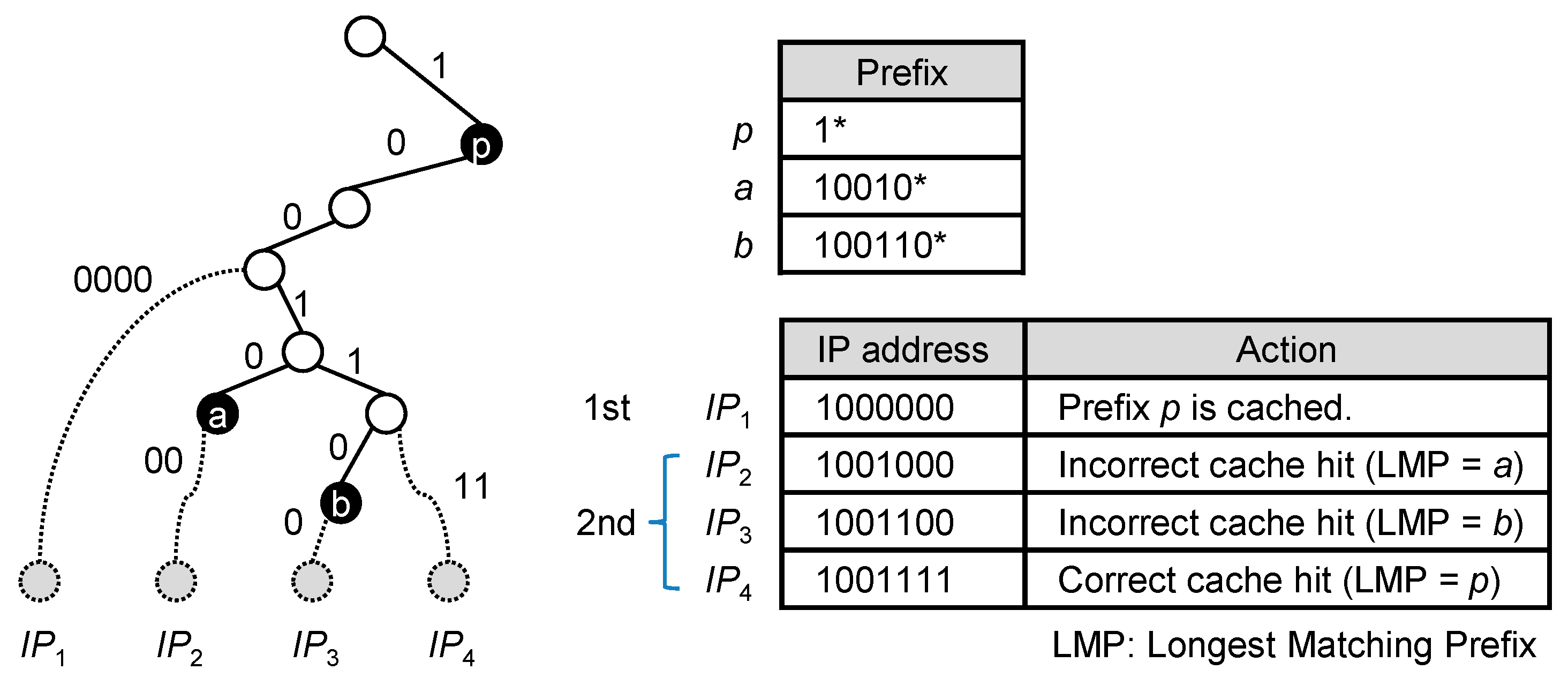

2.1. Prefix Caching and Prefix Expansion

2.2. Related Works

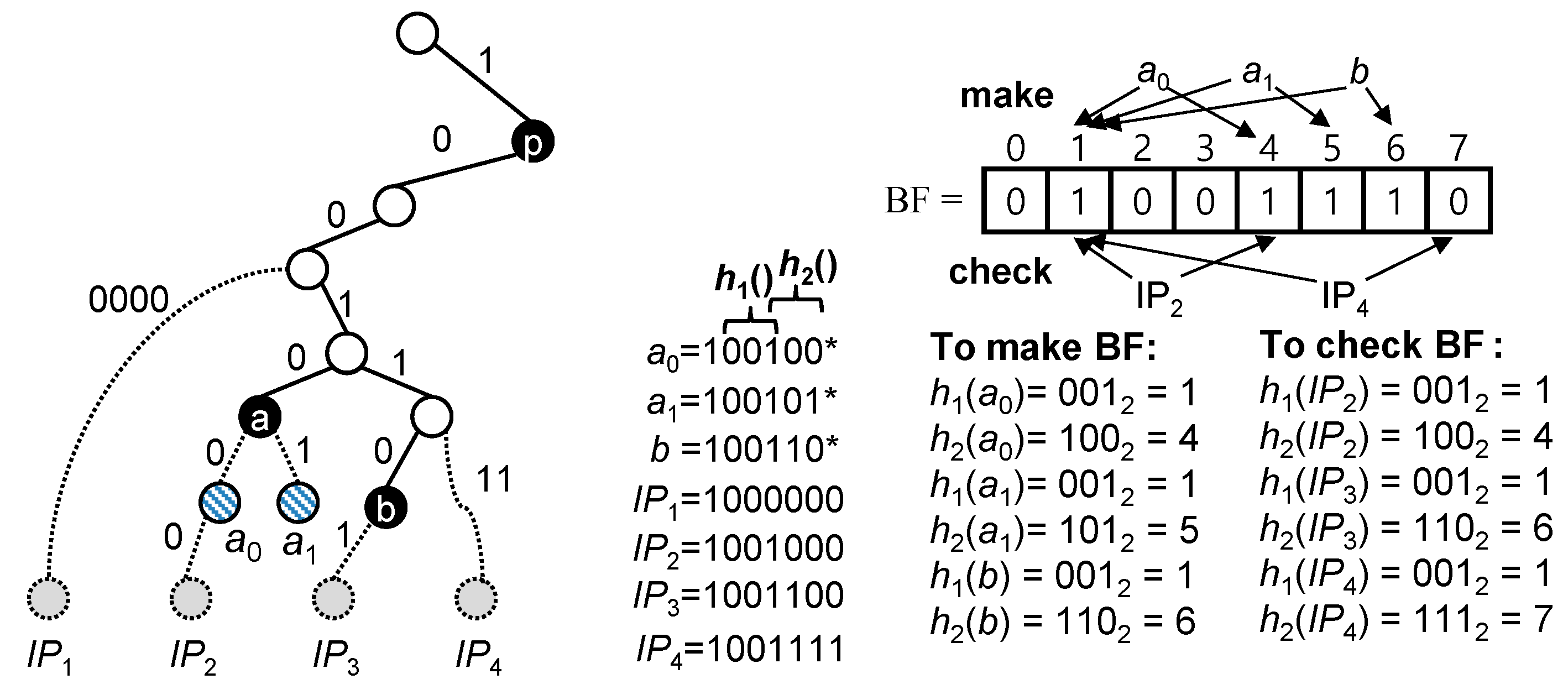

3. Bloom Filter-Based Prefix Caching

4. A Proposed Caching Scheme: Two-Level Bloom Filter-Based Prefix Caching (BFPC)

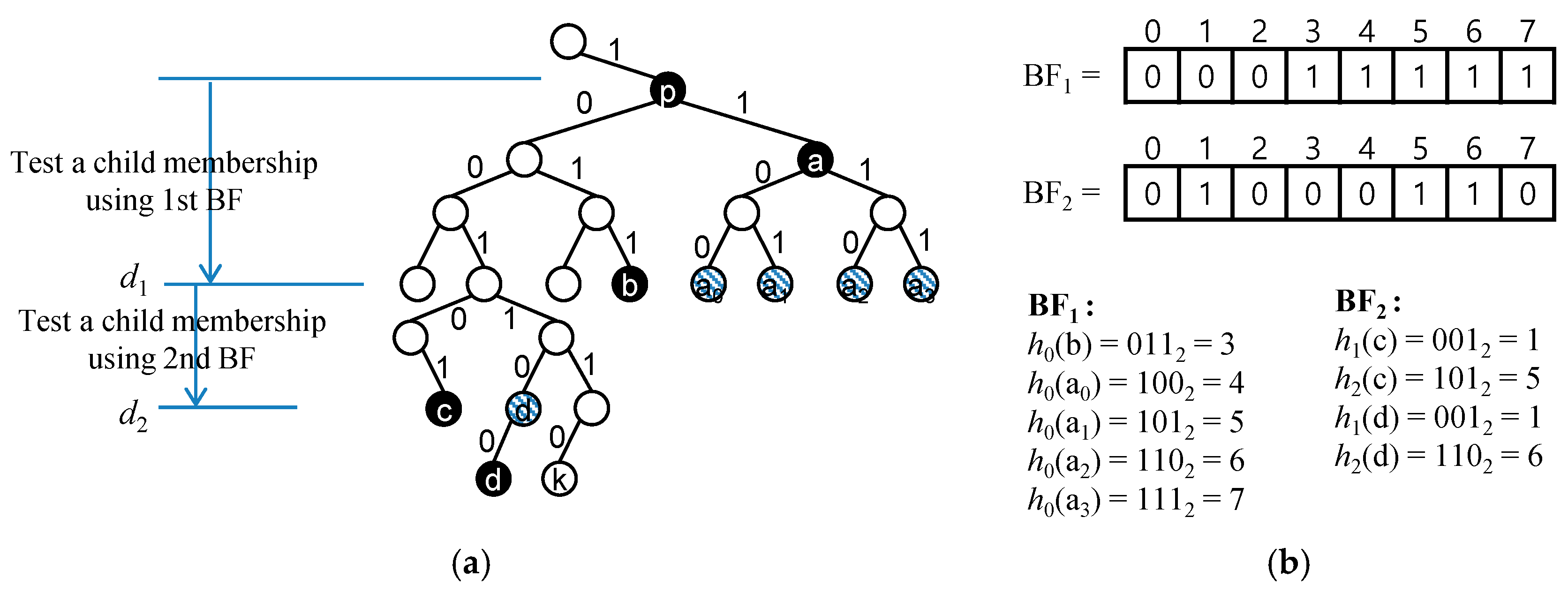

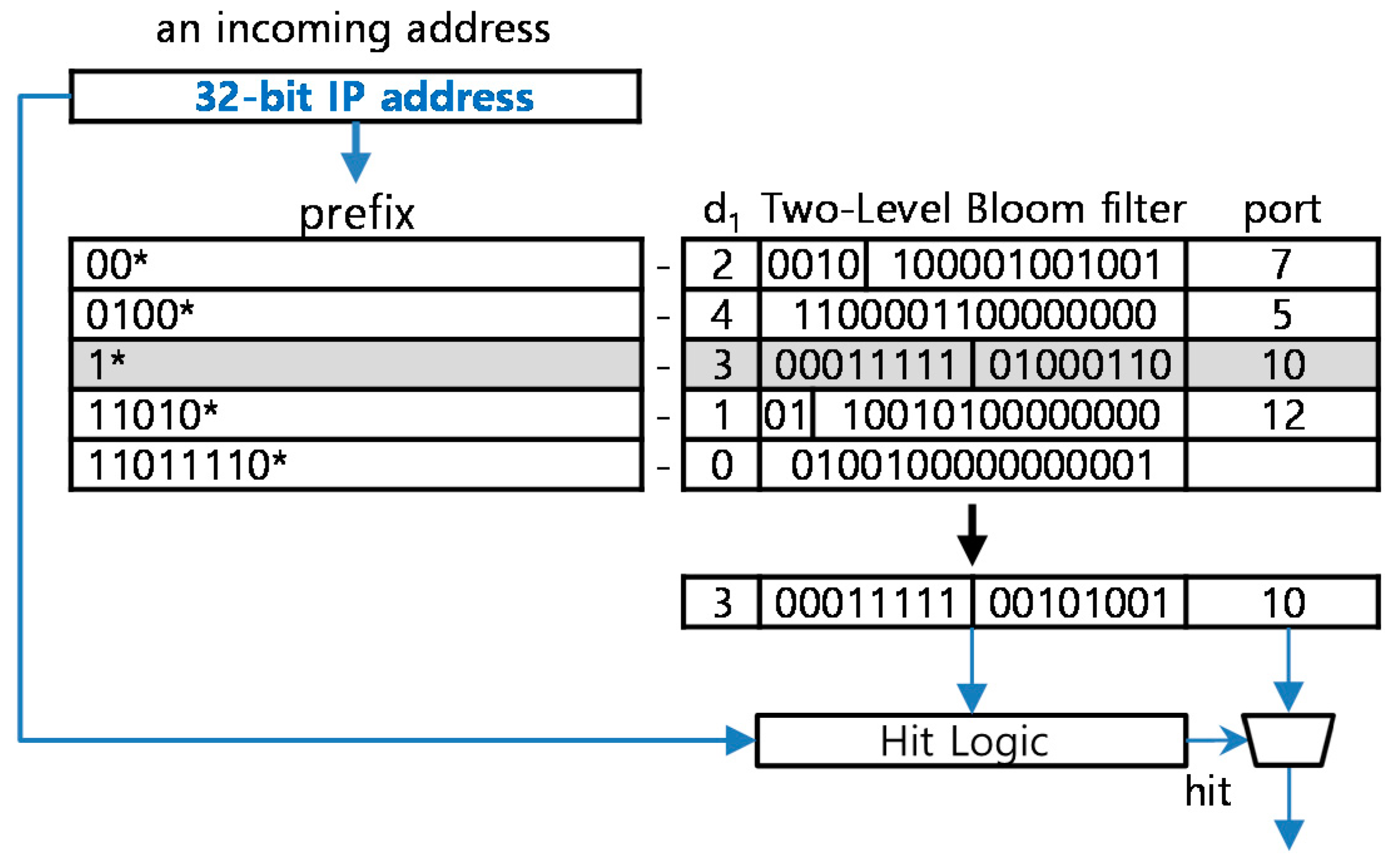

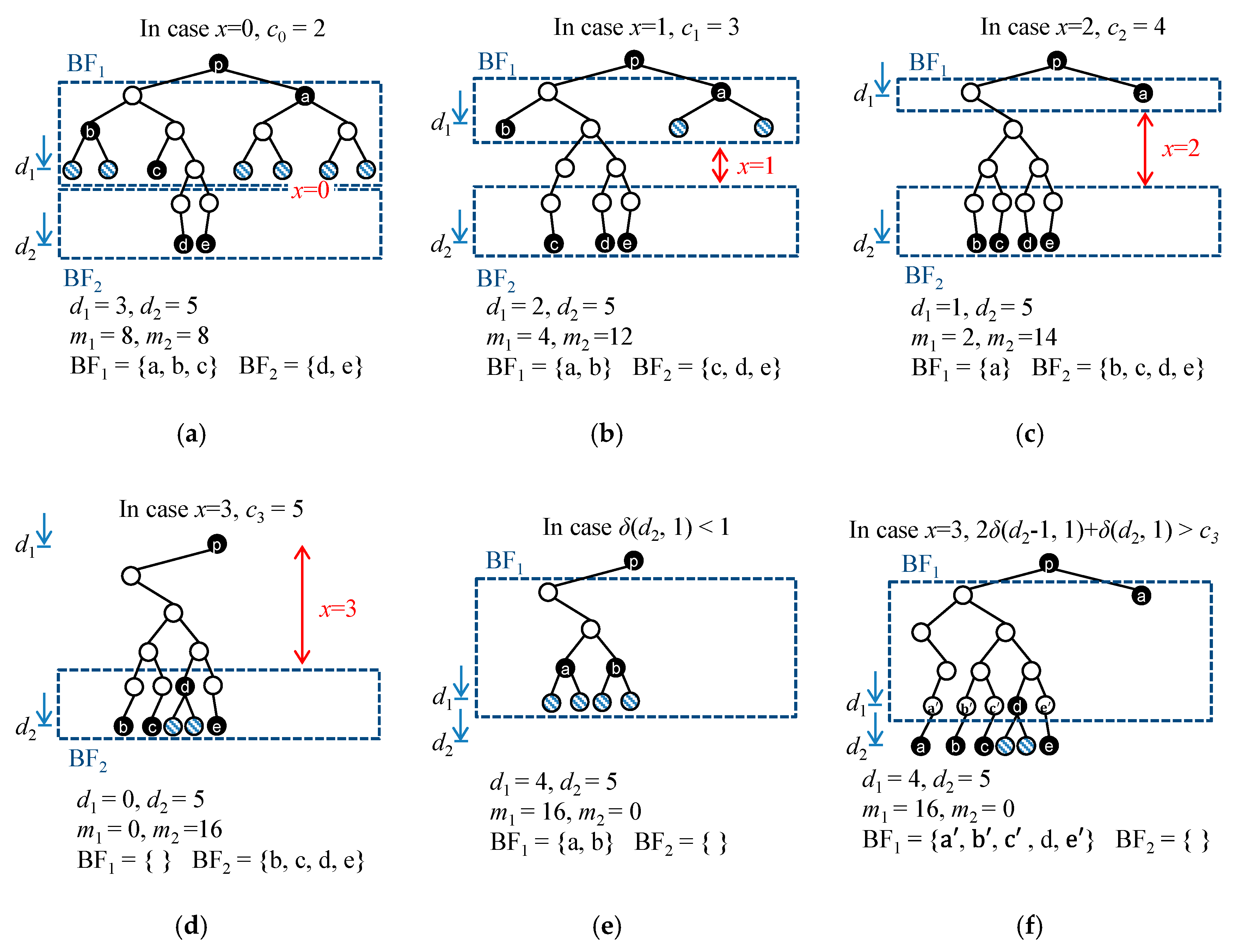

4.1. A Two-Level Bloom Filter-Based Prefix Cache

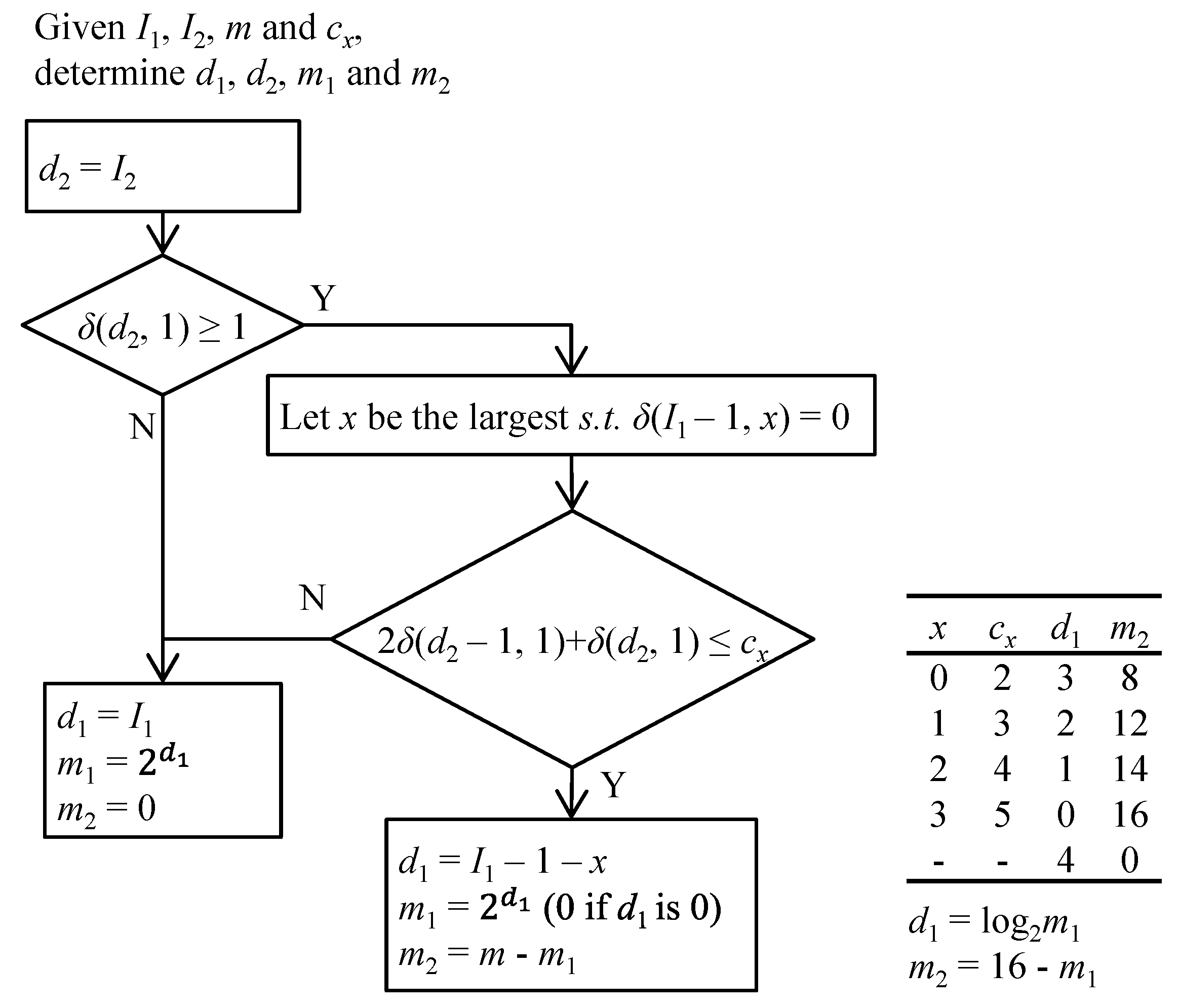

4.2. Construction of a Two-Level Bloom Filter

- n(d) denotes the number of children at a distance ≤d.

- δ(d, x) denotes n(d)—n(d-x).

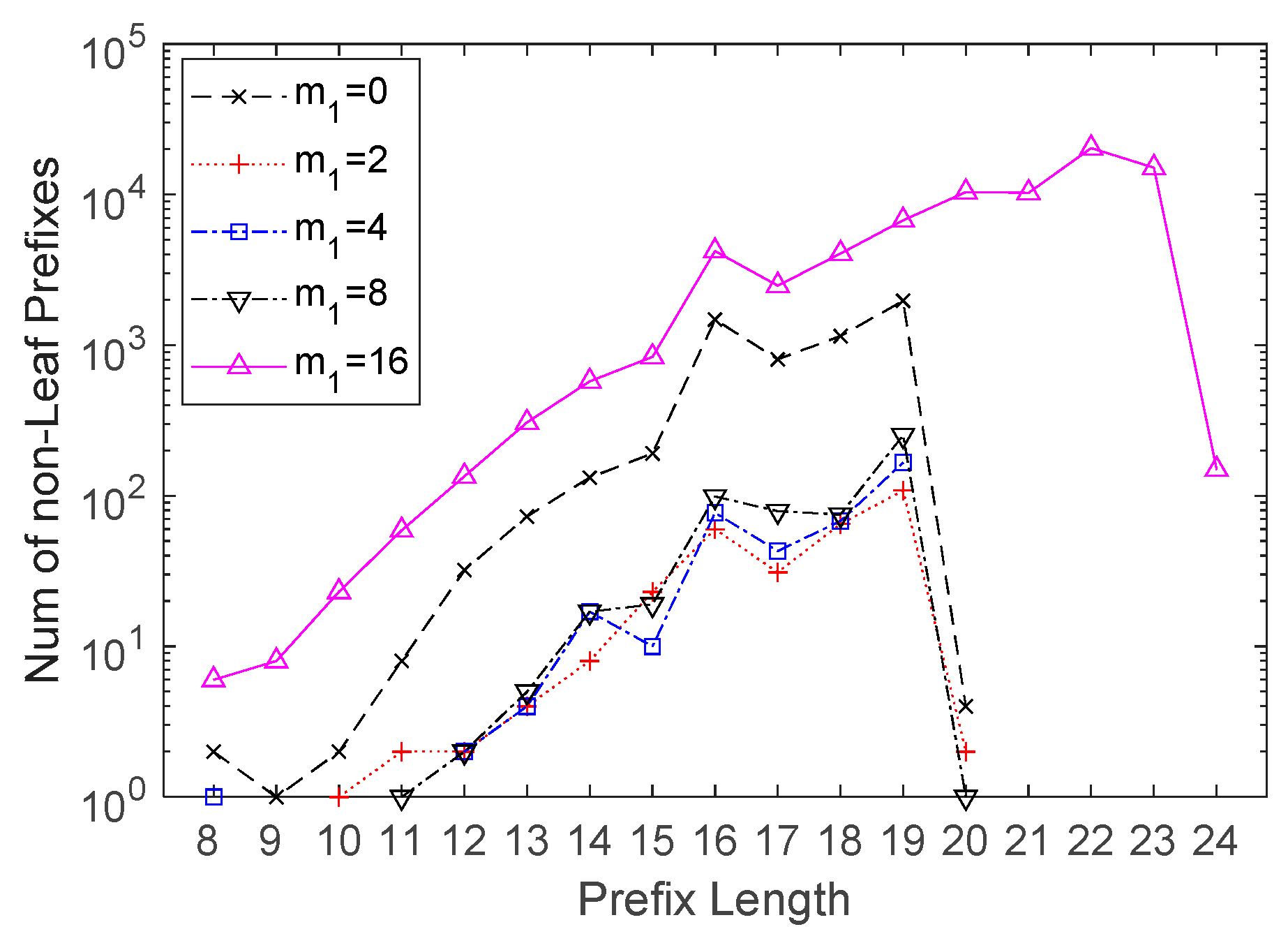

- m1 denotes BF1 size (in the number of bits).

- m2 denotes BF2 size (in the number of bits).

- m denotes the total filter size (= m1 + m2 = 16).

- d1 denotes the distance at which BF1 covers all the expanded children.

- d2 denotes the distance at which BF2 covers all the expanded children except BF1 covers.

- I1 denotes the initial value of d1 (= log2m = 4).

- I2 denotes the initial value of d2 (= 5).

- cx denotes the constraint on a given x.

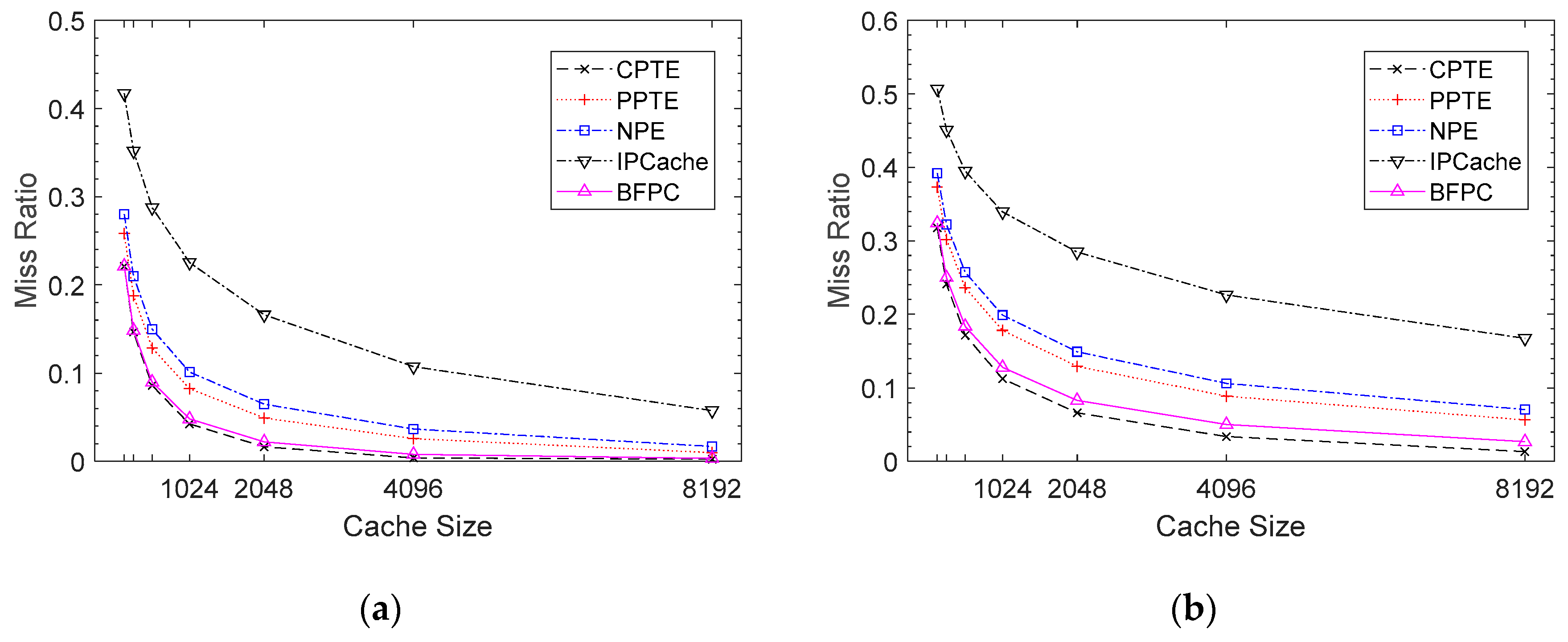

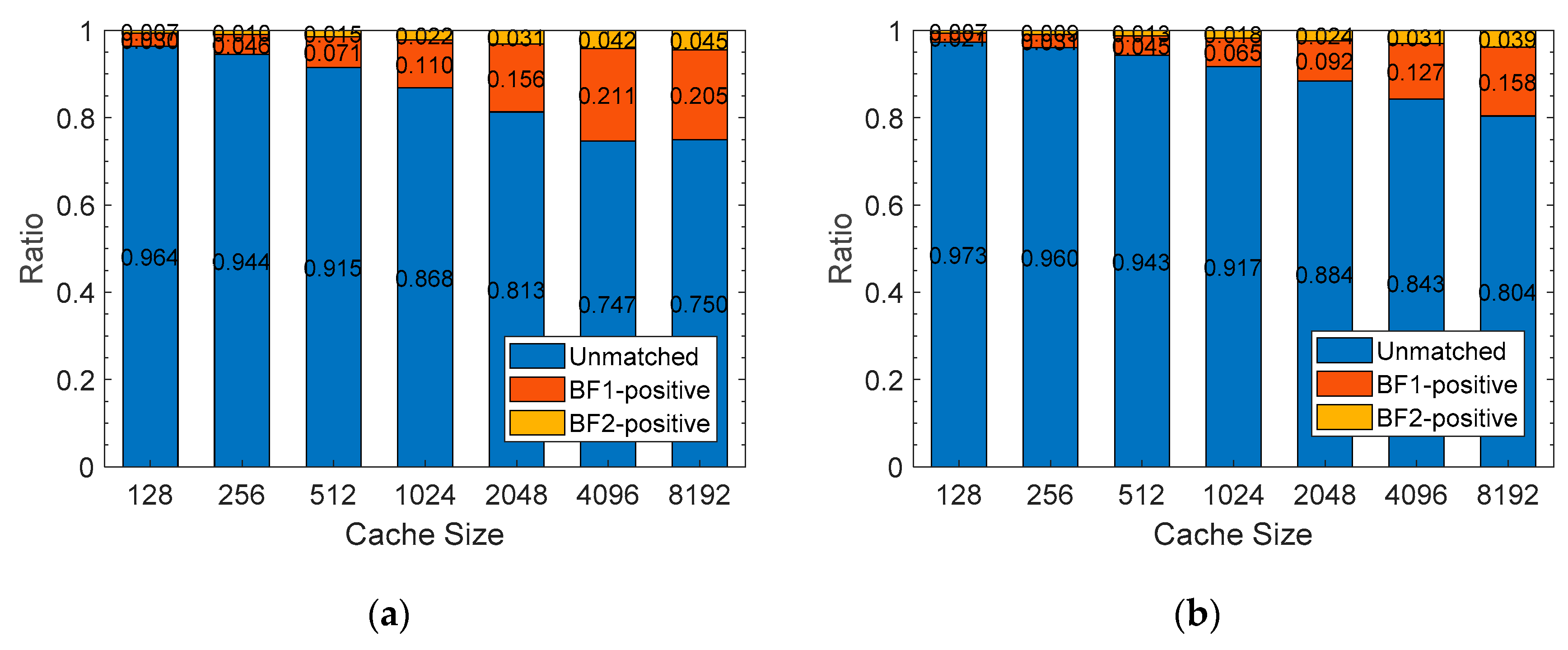

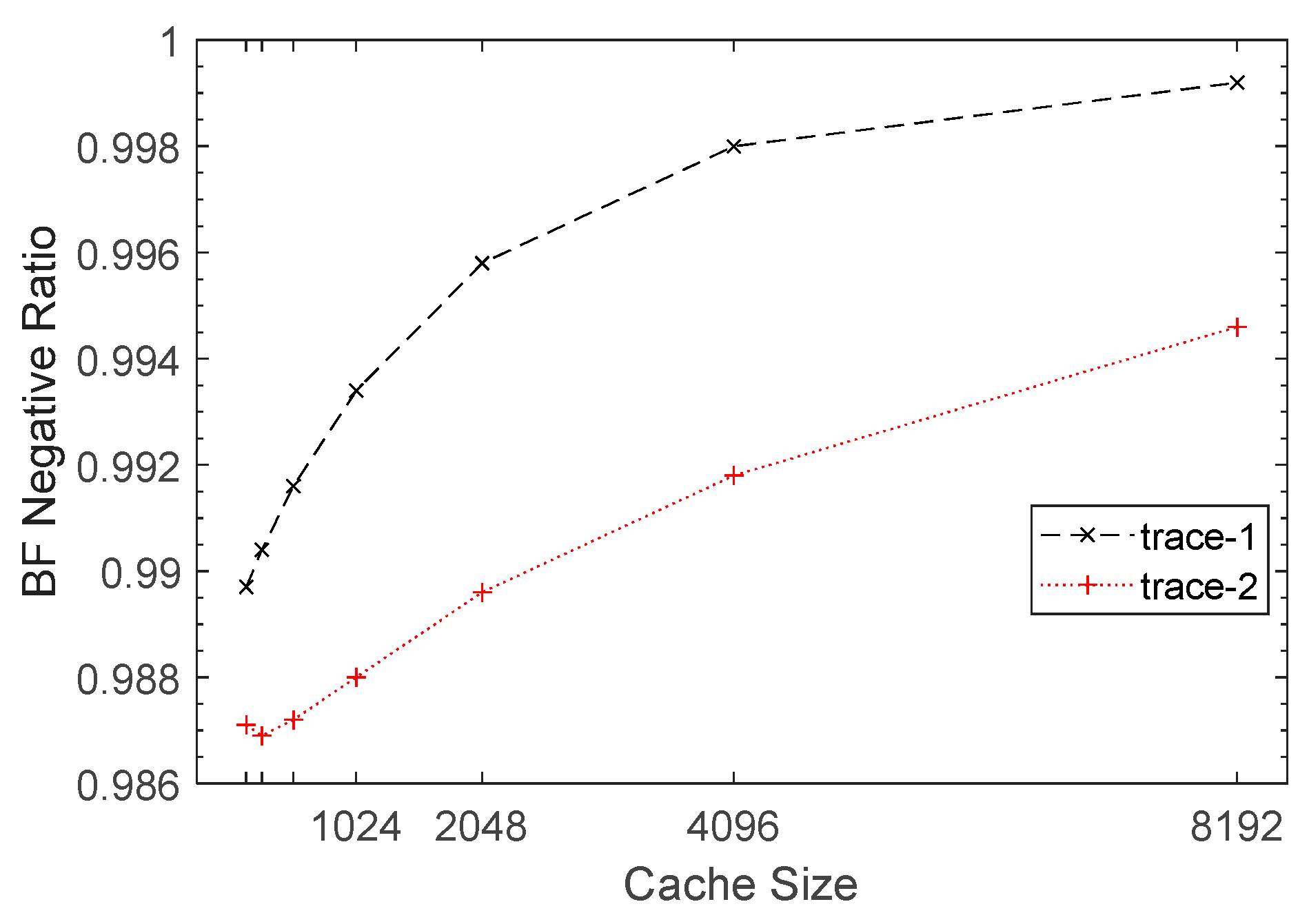

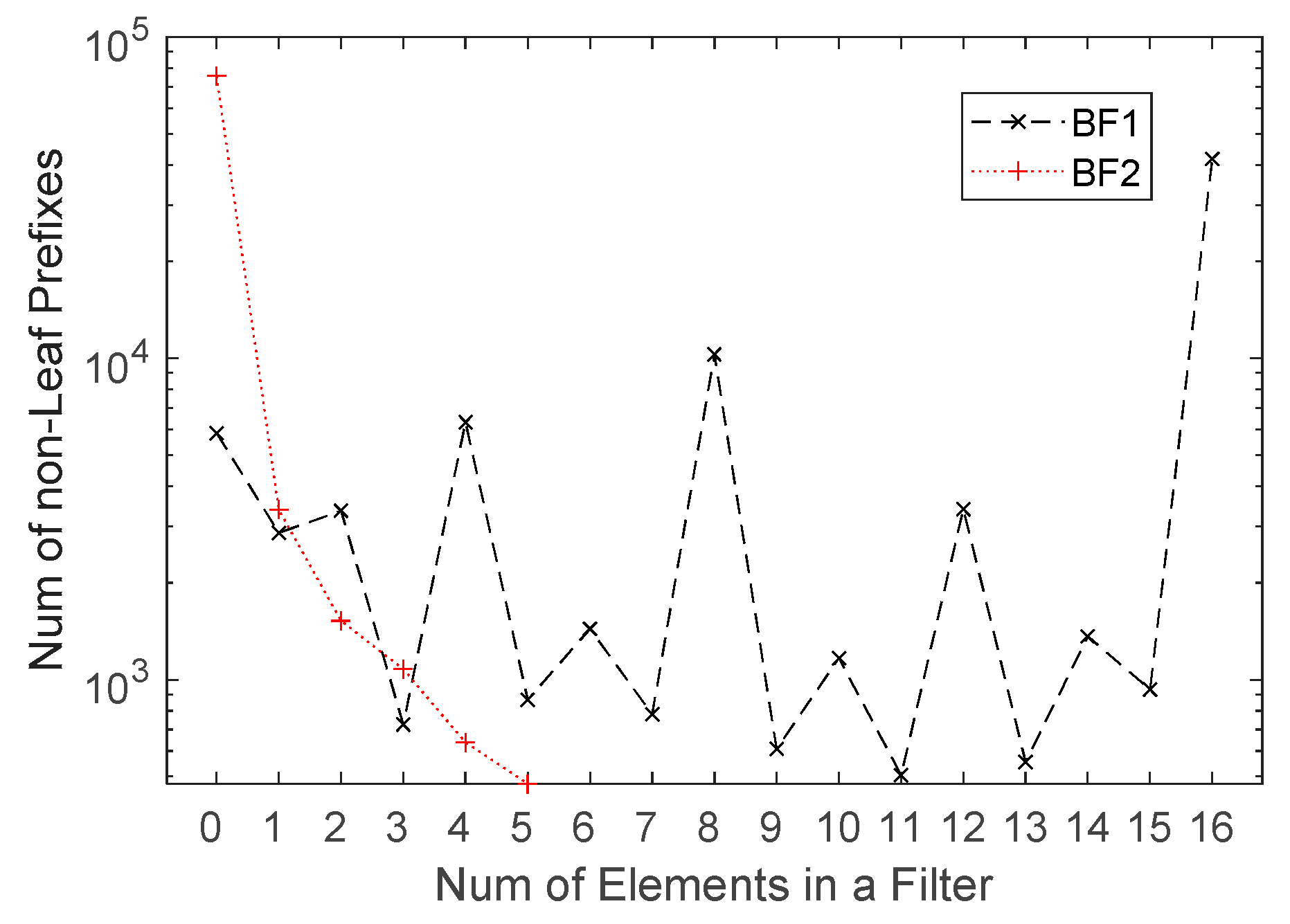

5. Evaluation

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ruiz-Sanchez, M.; Biersack, E.; Dabbous, W. Survey and taxonomy of IP address lookup algorithms. IEEE Netw. 2001, 15, 8–23. [Google Scholar] [CrossRef]

- Ravikumar, V.C.; Mahapatra, R.N. TCAM architecture for IP lookup using prefix properties. IEEE Micro 2004, 24, 60–69. [Google Scholar] [CrossRef]

- Zheng, K.; Hu, C.; Lu, H.; Liu, B. A TCAM-based distributed parallel IP lookup scheme and performance analysis. IEEE/ACM Trans. Netw. 2006, 14, 863–875. [Google Scholar] [CrossRef]

- Huang, J.-Y.; Wang, P.-C. TCAM-Based IP Address Lookup Using Longest Suffix Split. IEEE/ACM Trans. Netw. 2018, 26, 976–989. [Google Scholar] [CrossRef]

- Nilsson, S.; Karlsson, G. IP-address lookup using LC-tries. IEEE J. Sel. Areas Commun. 1999, 17, 1083–1092. [Google Scholar] [CrossRef]

- Wu, Y.; Nong, G.; Hamdi, M. Scalable pipelined IP lookup with prefix tries. Comput. Netw. 2017, 120, 1–11. [Google Scholar] [CrossRef]

- Kim, J.; Ko, M.-C.; Shin, M.S.; Kim, J. IMT: A Memory-Efficient and Fast Updatable IP Lookup Architecture Using an Indexed Multibit Trie. KSII Trans. Internet Inf. Syst. 2019, 13, 1922–1940. [Google Scholar] [CrossRef]

- Lim, H.; Seo, J.-H.; Jung, Y.-J. High speed IP address lookup architecture using hashing. IEEE Commun. Lett. 2003, 7, 502–504. [Google Scholar] [CrossRef]

- Dharmapurikar, S.; Krishnamurthy, P.; Taylor, D.E. Longest prefix matching using bloom filters. IEEE/ACM Trans. Netw. 2006, 14, 397–409. [Google Scholar] [CrossRef]

- Song, H.; Hao, F.; Kodialam, M.; Lakshman, T.V. IPv6 Lookups using Distributed and Load Balanced Bloom Filters for 100Gbps Core Router Line Cards. In Proceedings of the IEEE INFOCOM 2009—The 28th Conference on Computer Communications, Rio de Janeiro, Brazil, 19–25 April 2009; pp. 2518–2526. [Google Scholar]

- Byun, H.; Li, Q.; Lim, H. Vectored-Bloom Filter for IP Address Lookup: Algorithm and Hardware Architectures. Appl. Sci. 2019, 9, 4621. [Google Scholar] [CrossRef]

- Chiueh, T.C.; Pradhan, P. High-Performance IP Routing Table Lookup using CPU Caching. In Proceedings of the IEEE INFOCOM ’99—Conference on Computer Communications, New York, NY, USA, 21–25 March 1999; pp. 1421–1428. [Google Scholar]

- Liu, H. Routing Prefix Caching in Network Processor Design. In Proceedings of the Tenth International Conference on Computer Communications and Networks, Scottsdale, AZ, USA, 15–17 October 2001; pp. 18–23. [Google Scholar]

- Kim, J.; Park, M.; Han, S.; Kim, J. An Efficient Prefix Caching Scheme with Bounded Prefix Expansion for High-Speed IP Lookup. IEICE Trans. Commun. 2012, 95, 3298–3301. [Google Scholar] [CrossRef]

- Bloom, B.H. Space/time trade-offs in hash coding with allowable errors. Commun. ACM 1970, 13, 422–426. [Google Scholar] [CrossRef]

- Akhbarizadeh, M.J.; Nourani, M. Efficient Prefix Cache for Network Processors. In Proceedings of the 12th Annual IEEE Symposium on High Performance Interconnects, Stanford, CA, USA, 27 August 2004; pp. 41–46. [Google Scholar]

- Bitmap-based Prefix Caching for Fast IP Lookup. KSII Trans. Internet Inf. Syst. 2014, 8, 873–889. [CrossRef]

- Kasnavi, S.; Berube, P.; Gaudet, V.; Amaral, J.N. A cache-based internet protocol address lookup architecture. Comput. Netw. 2008, 52, 303–326. [Google Scholar] [CrossRef]

- Zhang, W.; Bi, J.; Wu, J.; Zhang, B. Catching popular prefixes at AS border routers with a prediction based method. Comput. Netw. 2012, 56, 1486–1502. [Google Scholar] [CrossRef]

- Liu, Y.; Lehman, V.; Wang, L. Efficient FIB caching using minimal non-overlapping prefixes. Comput. Netw. 2015, 83, 85–99. [Google Scholar] [CrossRef]

- Grigoryan, G.; Liu, Y.; Kwon, M. Boosting FIB Caching Performance with Aggregation. In Proceedings of the 29th International Symposium on High-Performance Parallel and Distributed Computing, Stockholm, Sweden, 23–26 June 2020; pp. 221–232. [Google Scholar]

- Rottenstreich, O.; Tapolcai, J. Optimal Rule Caching and Lossy Compression for Longest Prefix Matching. IEEE/ACM Trans. Netw. 2016, 25, 864–878. [Google Scholar] [CrossRef]

- Chen, X.; Zhang, G.; Cui, H. Investigating Route Cache in Named Data Networking. IEEE Commun. Lett. 2017, 22, 296–299. [Google Scholar] [CrossRef]

- Kim, J.; Kim, J. An Efficient Prefix Caching Scheme for Fast Forwarding in Named Data Networking. Stud. Inform. Control 2019, 27, 175–182. [Google Scholar] [CrossRef]

- Broder, A.; Mitzenmacher, M. Network Applications of Bloom Filters: A Survey. Internet Math. 2004, 1, 485–509. [Google Scholar] [CrossRef]

- Kiss, S.Z.; Hosszu, E.; Tapolcai, J.; Ronyai, L.; Rottenstreich, O. Bloom Filter with a False Positive Free Zone. In Proceedings of the IEEE INFOCOM 2018—IEEE Conference on Computer Communications, Honolulu, HI, USA, 16–19 April 2018; pp. 1412–1420. [Google Scholar]

- Rottenstreich, O.; Reviriego, P.; Porat, E.; Muthukrishnan, S. Constructions and Applications for Accurate Counting of the Bloom Filter False Positive Free Zone. In Proceedings of the Symposium on SDN Research, San Jose, CA, USA, 3 March 2020; pp. 135–145. [Google Scholar]

- BGP Routing Table. Available online: http://thyme.apnic.net/ap-data/2020/08/18/0400/ (accessed on 19 August 2020).

- BGP in 2019—The BGP Table. Available online: https://blog.apnic.net/2020/01/14/bgp-in-2019-the-bgp-table/ (accessed on 15 January 2020).

| FIB | Num of Prefixes | Avg. Prefix Length | Avg. Length When Cached | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Non-Leaf | Leaf | Total | Non-Leaf | Leaf | All | Non-Leaf | Leaf | All | |

| Original | 82,707 | 734,876 | 817,583 | 20.333 | 23.027 | 22.754 | - | - | - |

| CPTE | 0 | 988,828 | 988,828 | 0 | 22.817 | 22.817 | - | 22.817 | 22.817 |

| PPTE | 82,707 | 759,206 | 841,913 | 20.333 | 22.974 | 22.715 | 32.000 | 22.974 | 23.861 |

| NPE | 82,707 | 734,876 | 817,583 | 20.333 | 23.027 | 22.754 | 32.000 | 23.027 | 23.934 |

| BFPC | 82,707 | 734,876 | 817,583 | 20.333 | 23.027 | 22.754 | 20.333 | 23.027 | 22.754 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.; Ko, M.-C.; Shin, M.S.; Kim, J. A Novel Prefix Cache with Two-Level Bloom Filters in IP Address Lookup. Appl. Sci. 2020, 10, 7198. https://doi.org/10.3390/app10207198

Kim J, Ko M-C, Shin MS, Kim J. A Novel Prefix Cache with Two-Level Bloom Filters in IP Address Lookup. Applied Sciences. 2020; 10(20):7198. https://doi.org/10.3390/app10207198

Chicago/Turabian StyleKim, Junghwan, Myeong-Cheol Ko, Moon Sun Shin, and Jinsoo Kim. 2020. "A Novel Prefix Cache with Two-Level Bloom Filters in IP Address Lookup" Applied Sciences 10, no. 20: 7198. https://doi.org/10.3390/app10207198

APA StyleKim, J., Ko, M.-C., Shin, M. S., & Kim, J. (2020). A Novel Prefix Cache with Two-Level Bloom Filters in IP Address Lookup. Applied Sciences, 10(20), 7198. https://doi.org/10.3390/app10207198