Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations

Abstract

1. Introduction

- (a)

- Many proposed circuitries (except FPAA, FPGA-based) have quite complex topology, with many active and/or passive elements [9,12,16,17,18,19], especially circuits with fractional-order behavior and approximations by higher-order filters [3,5,6,13] or chain of bilinear segments [8,9,14,15,18,19,20,21],

- (b)

- (c)

- (d)

- summing of fractional-order as well as integer-order two ports was not analyzed deeply in the past,

- (e)

- single-parameter electronic adjustment of the time constant of the resulting response of two-port summing was not studied in the past, except R. Sotner et al. [9], but the overall circuit topology is based upon a chain of bilinear sections, and therefore, it is not one of the simplest solutions

- (a)

- the derivation of analytical expressions for mixed transfers, including sum of integer and fractional-order two-ports,

- (b)

- a single parameter electronic adjustment of the respective time constants,

- (c)

- the practical verification and also precautions of real implementation,

- (d)

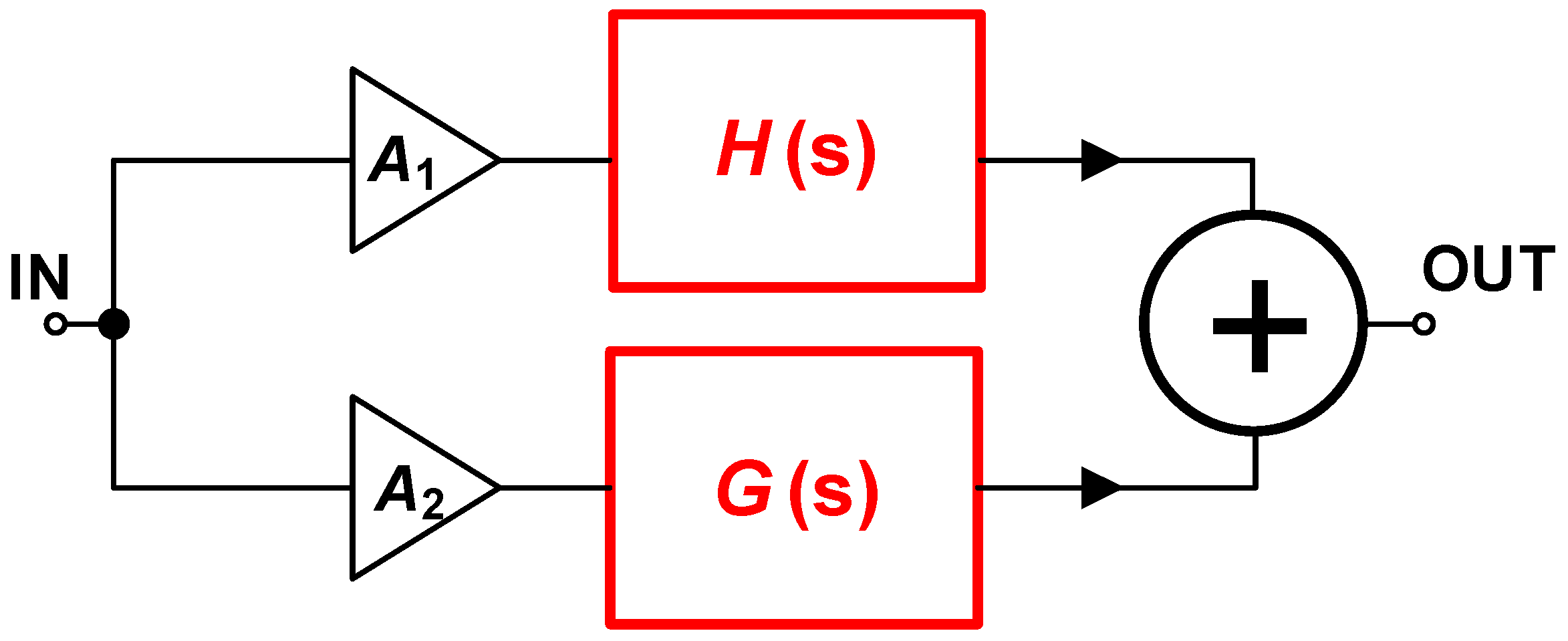

2. General Concept of Two-Port Interconnection

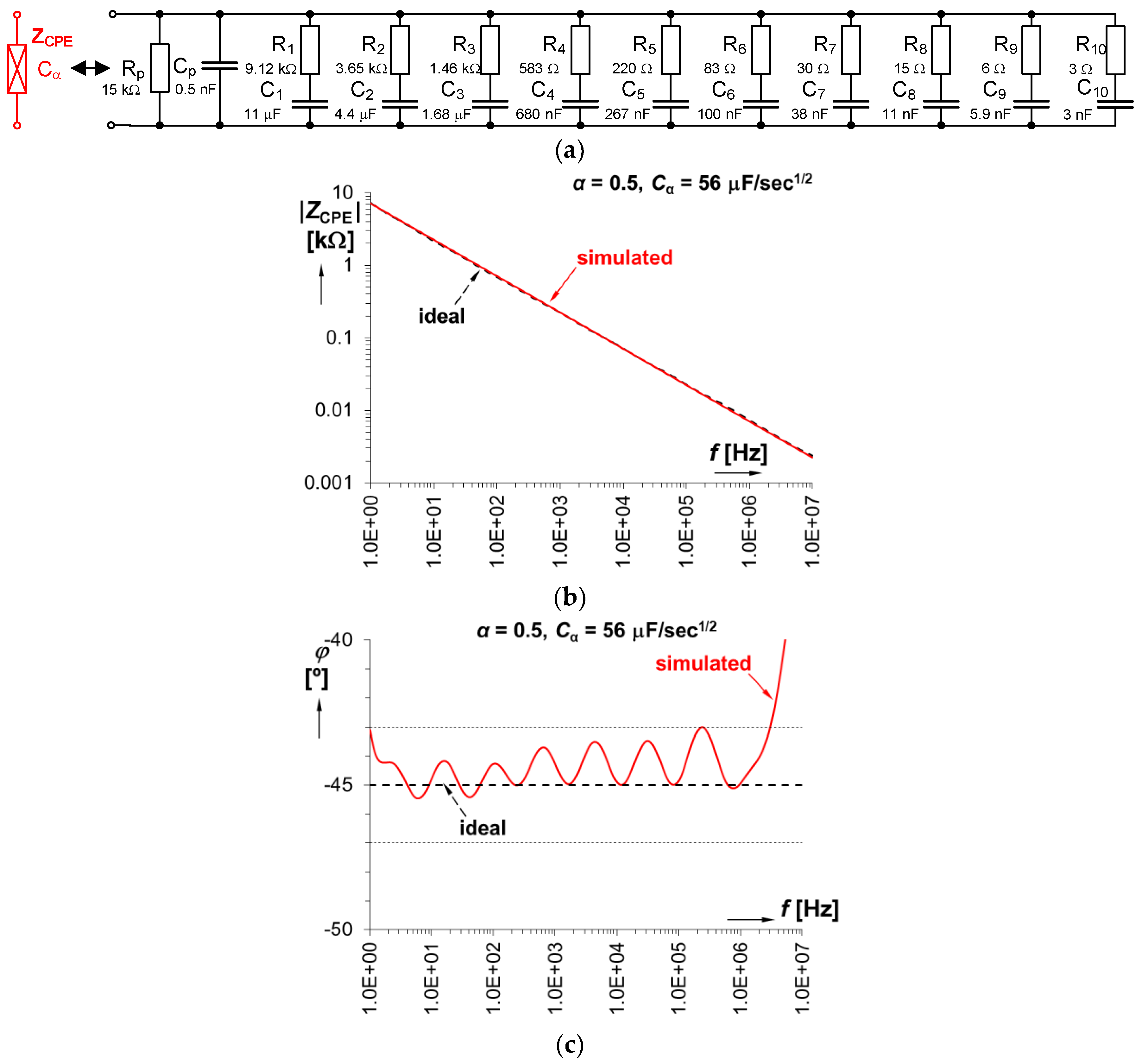

3. Passive Solution of Constant Phase Element

4. Analytical Analysis of Two-Port Interconnections

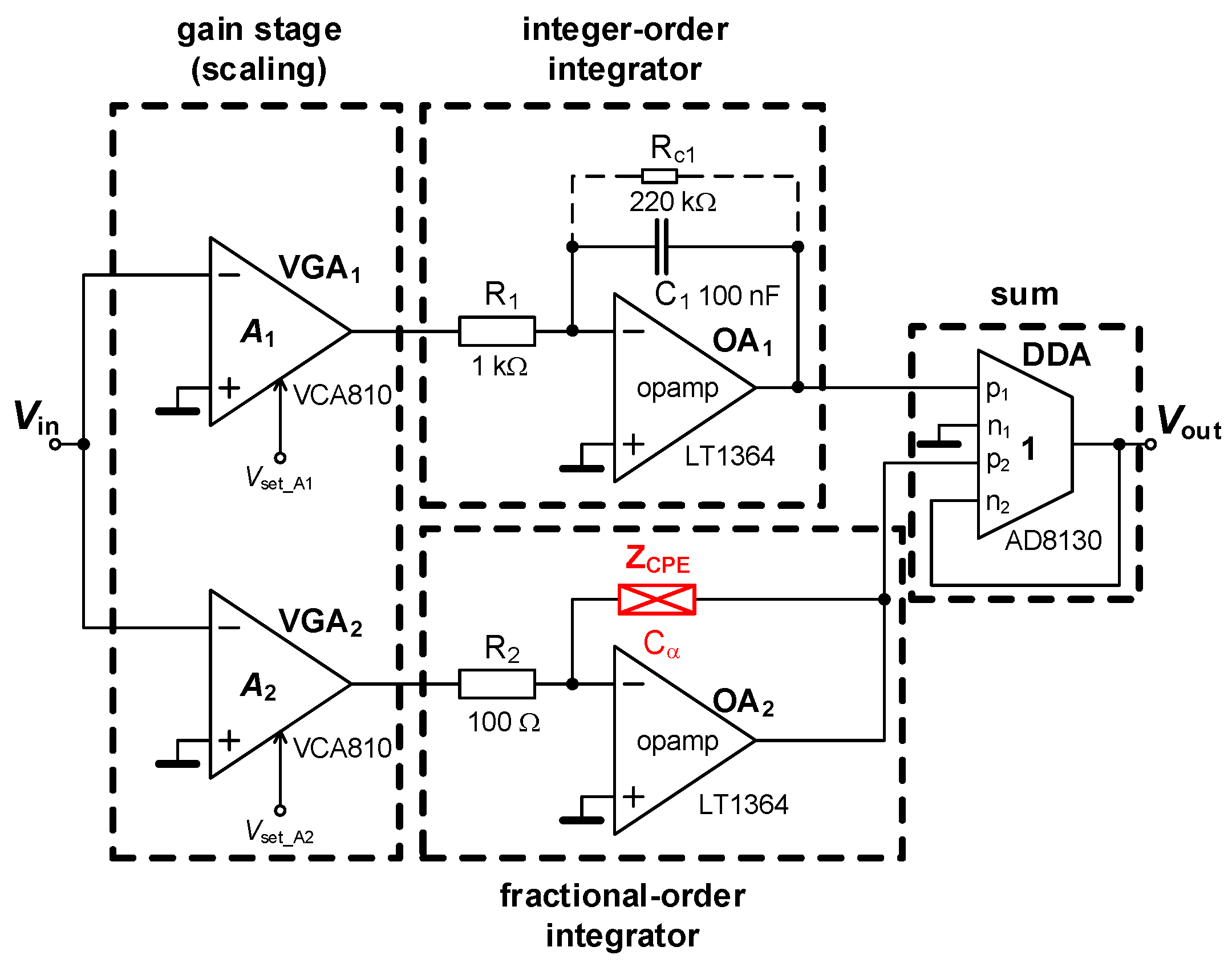

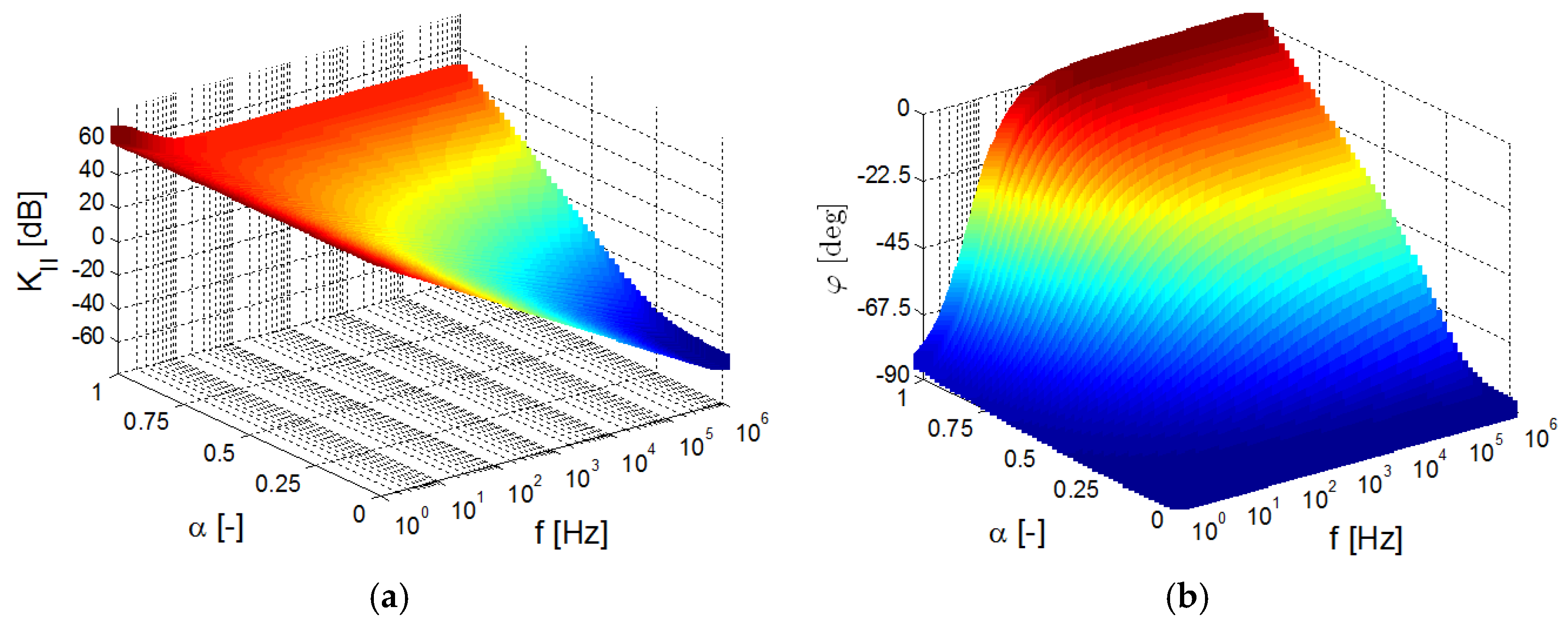

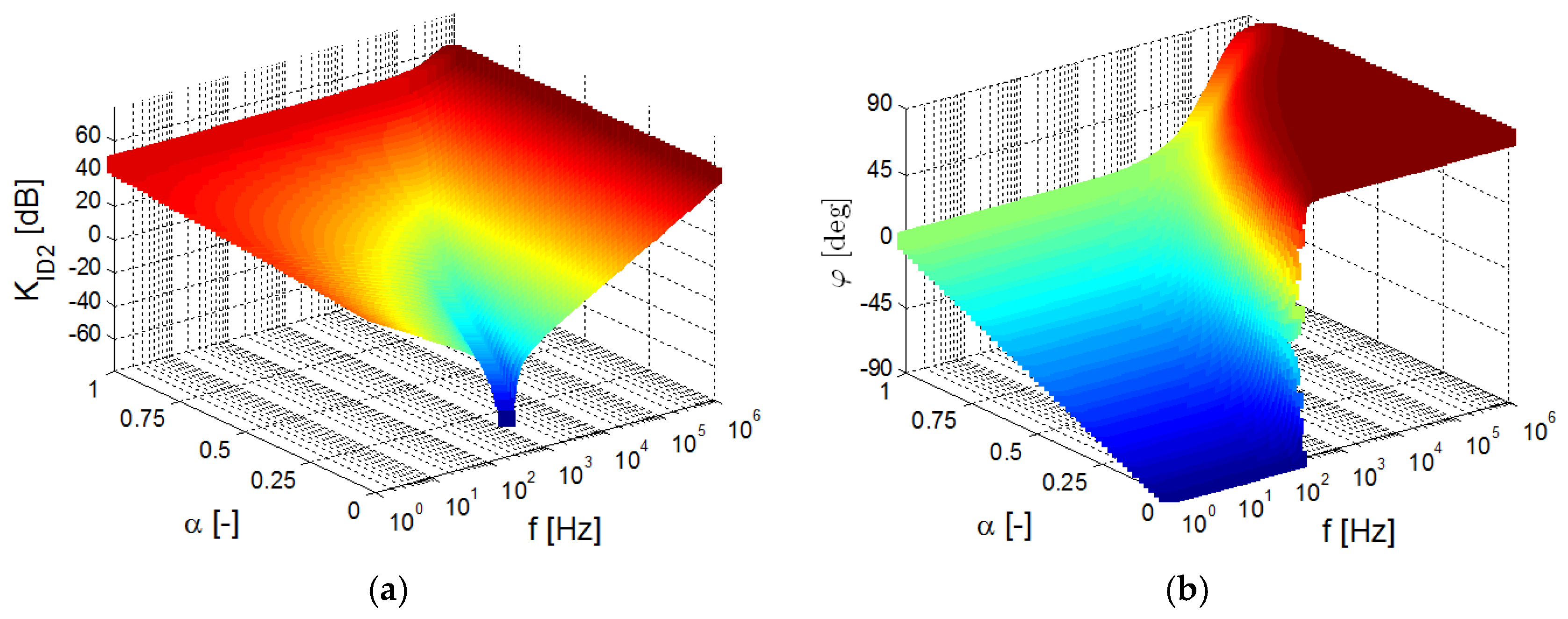

4.1. Sum of Integer and Fractional-Order Integrator Responses

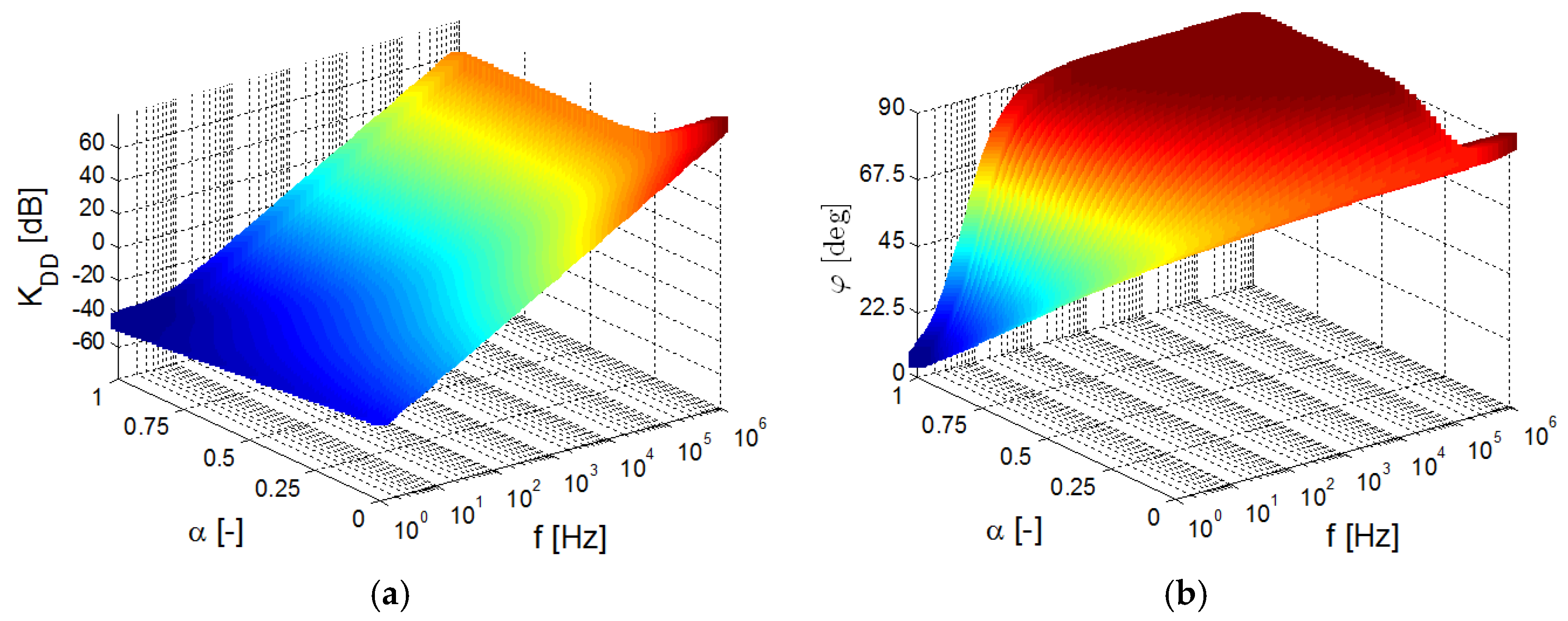

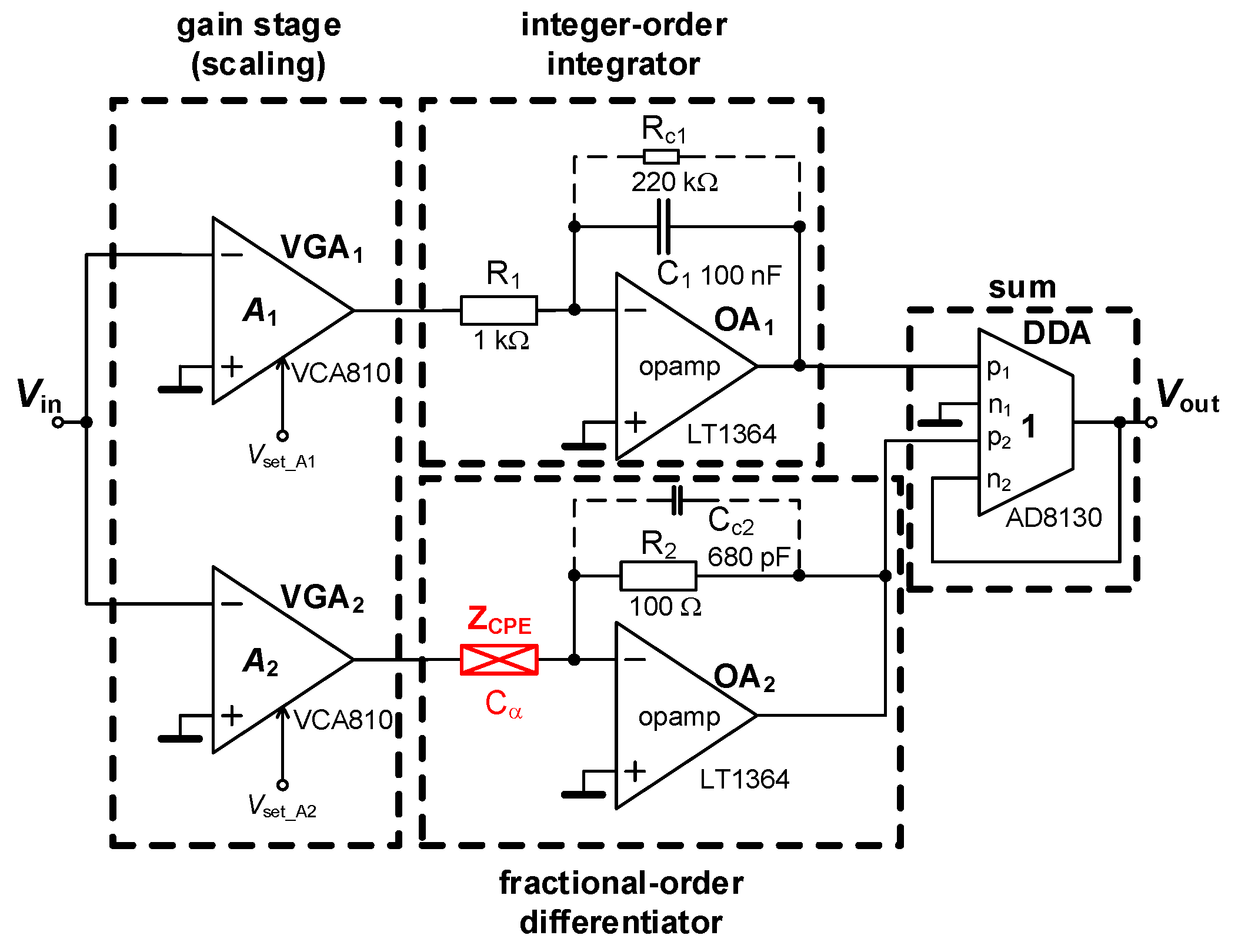

4.2. Sum of Integer and Fractional-Order Differentiator Responses

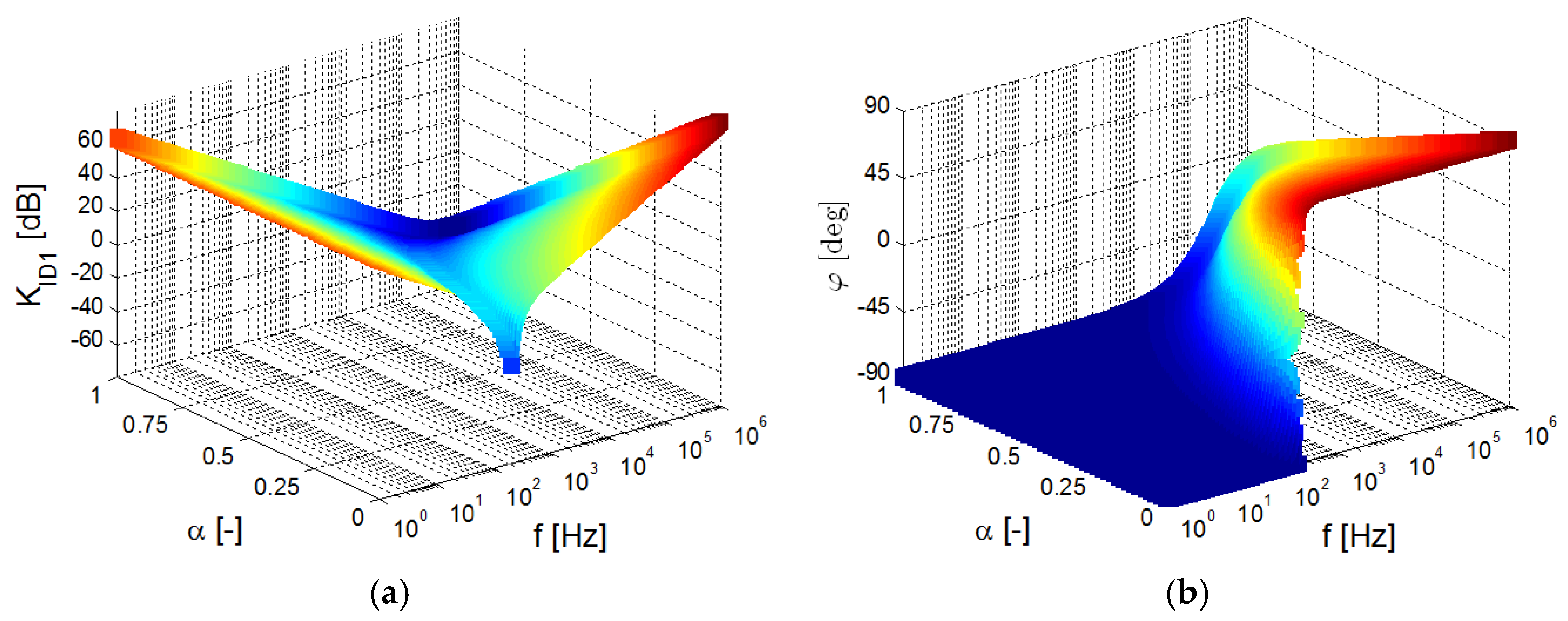

4.3. Sum of Integer-Order Integrator and Fractional-Order Differentiator Responses

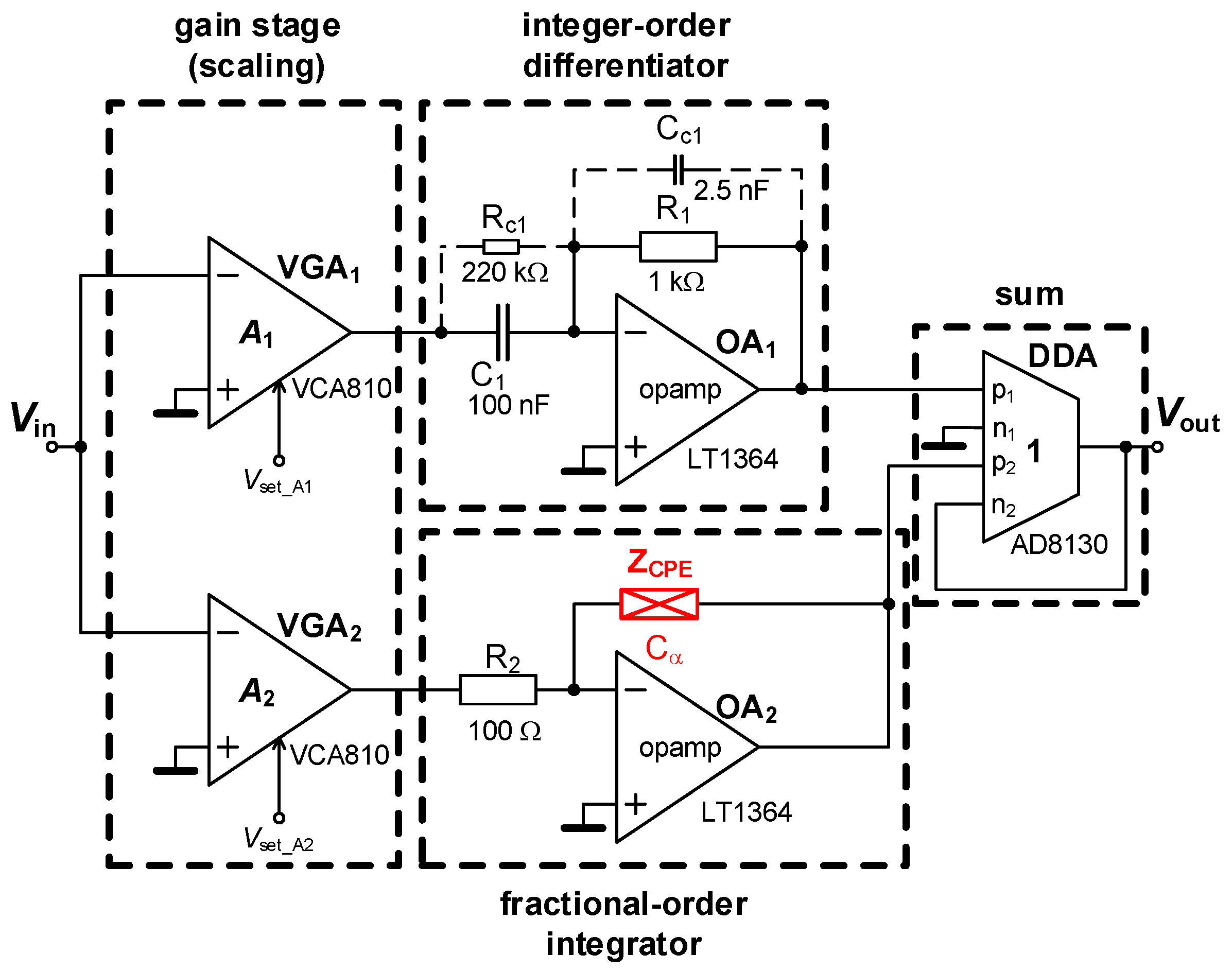

4.4. Sum of Fractional-Order Integrator and Integer-Order Differentiator Responses

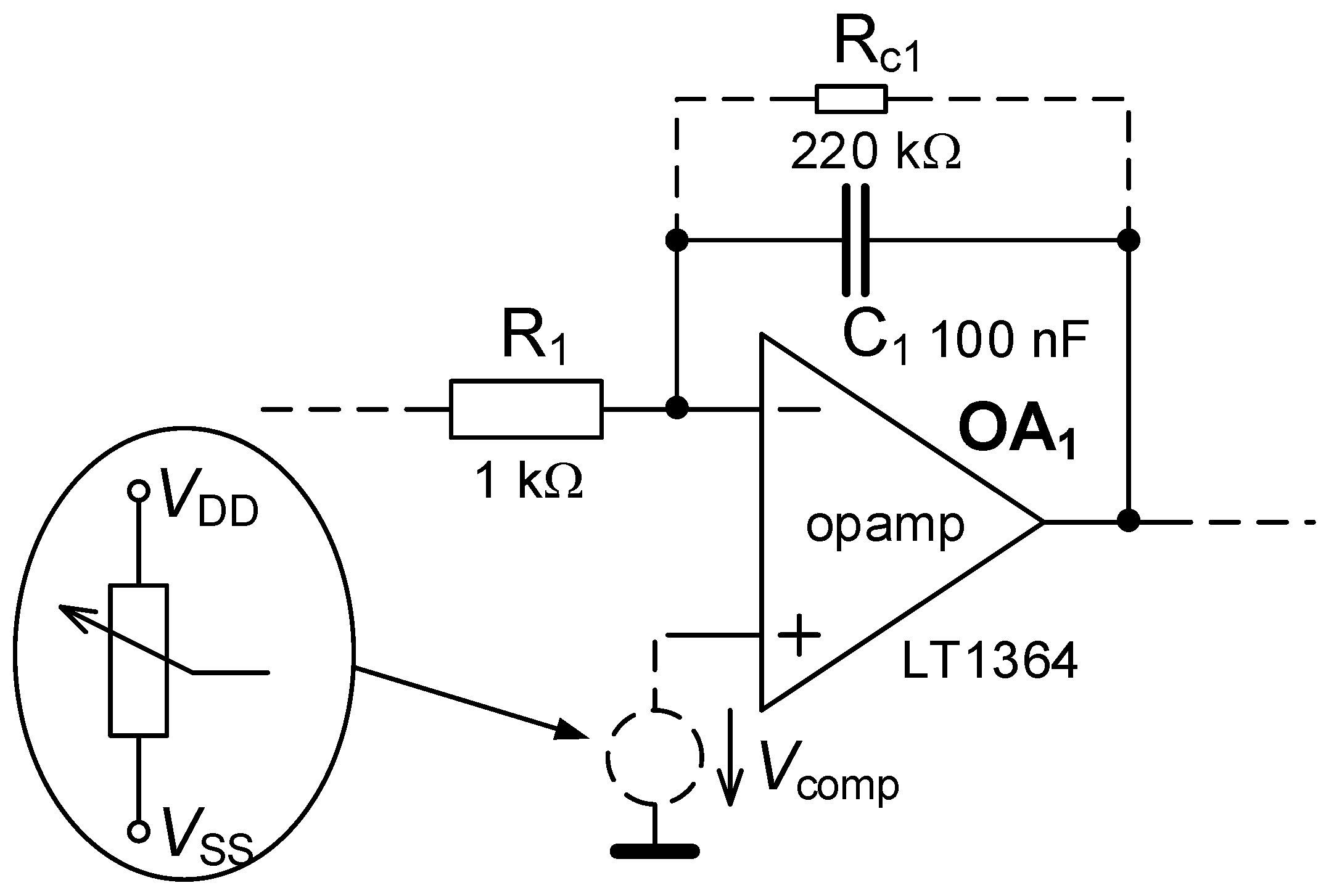

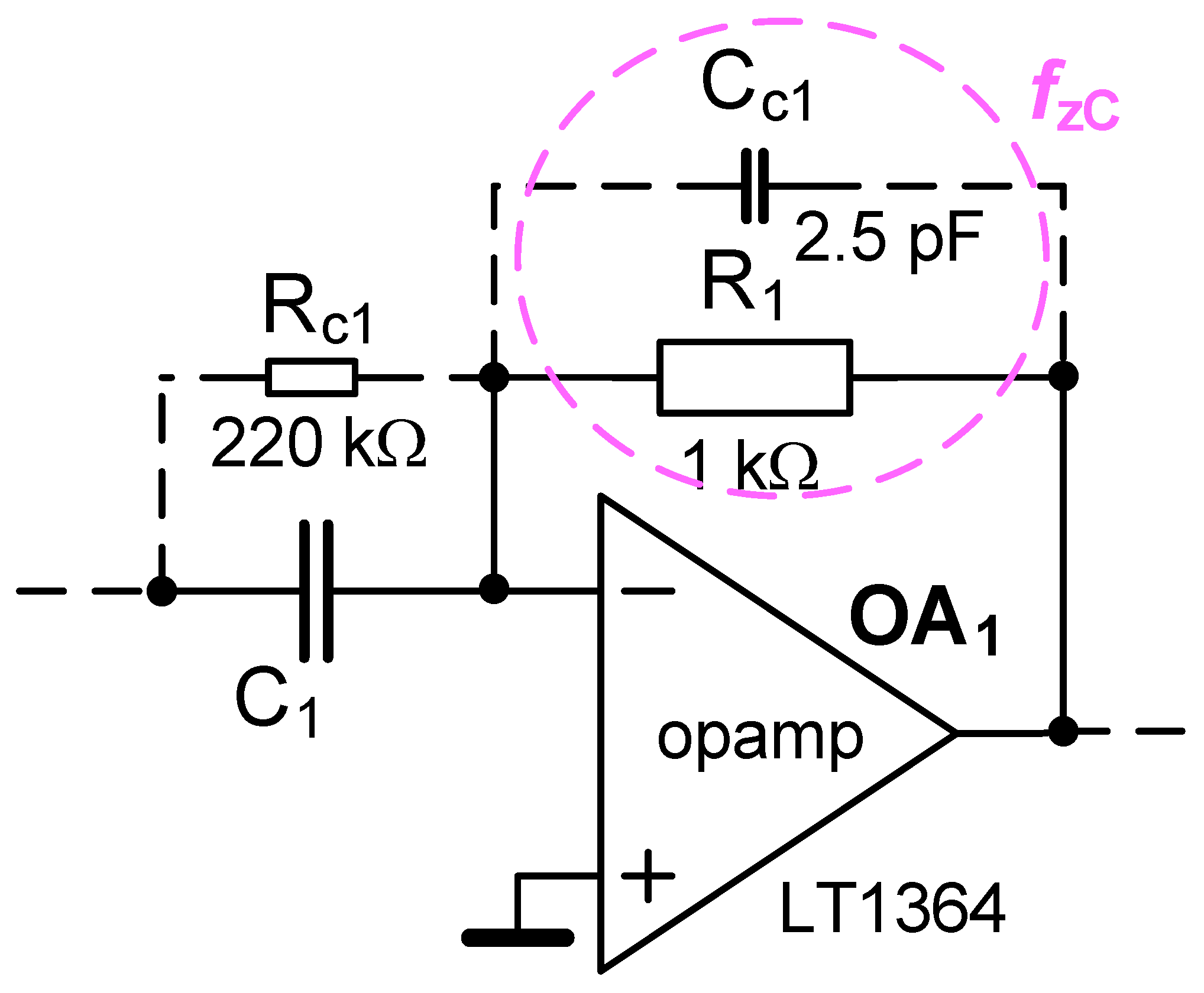

5. Solving Non-Ideal Issues during the Tests

6. Experimental Analysis

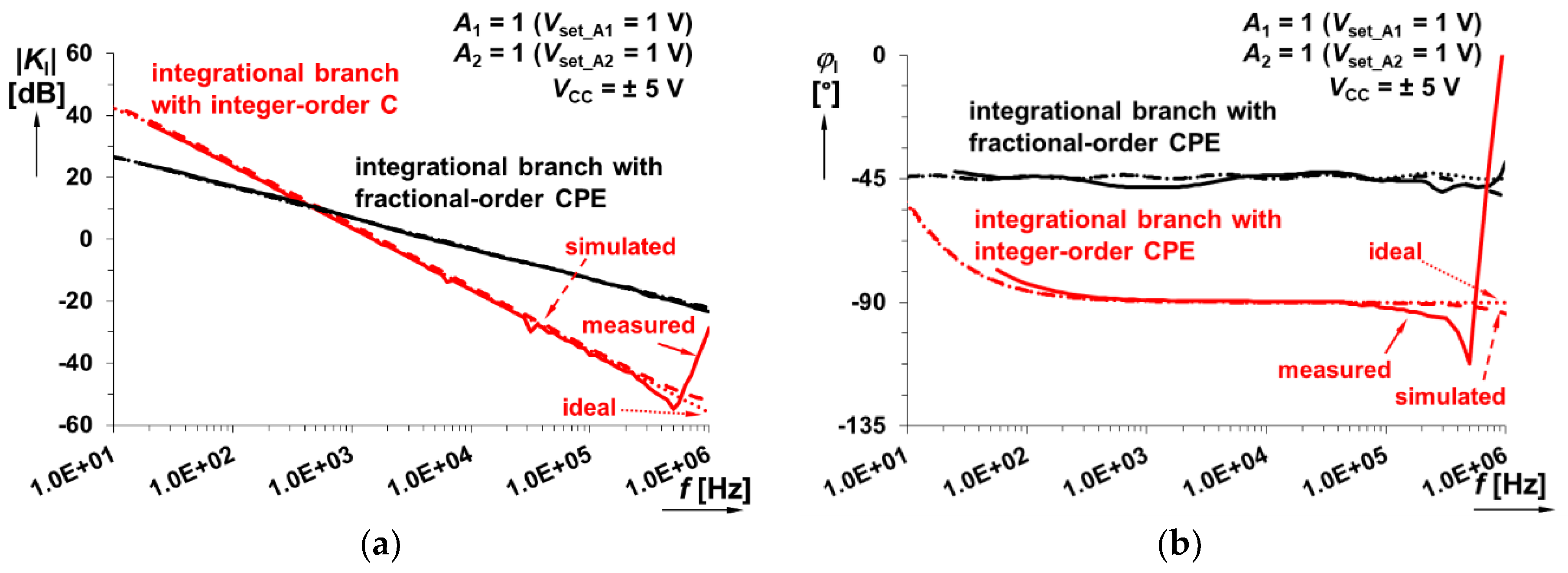

6.1. Analysis of Integer-and Fractional-Order Integrators and Differentiators

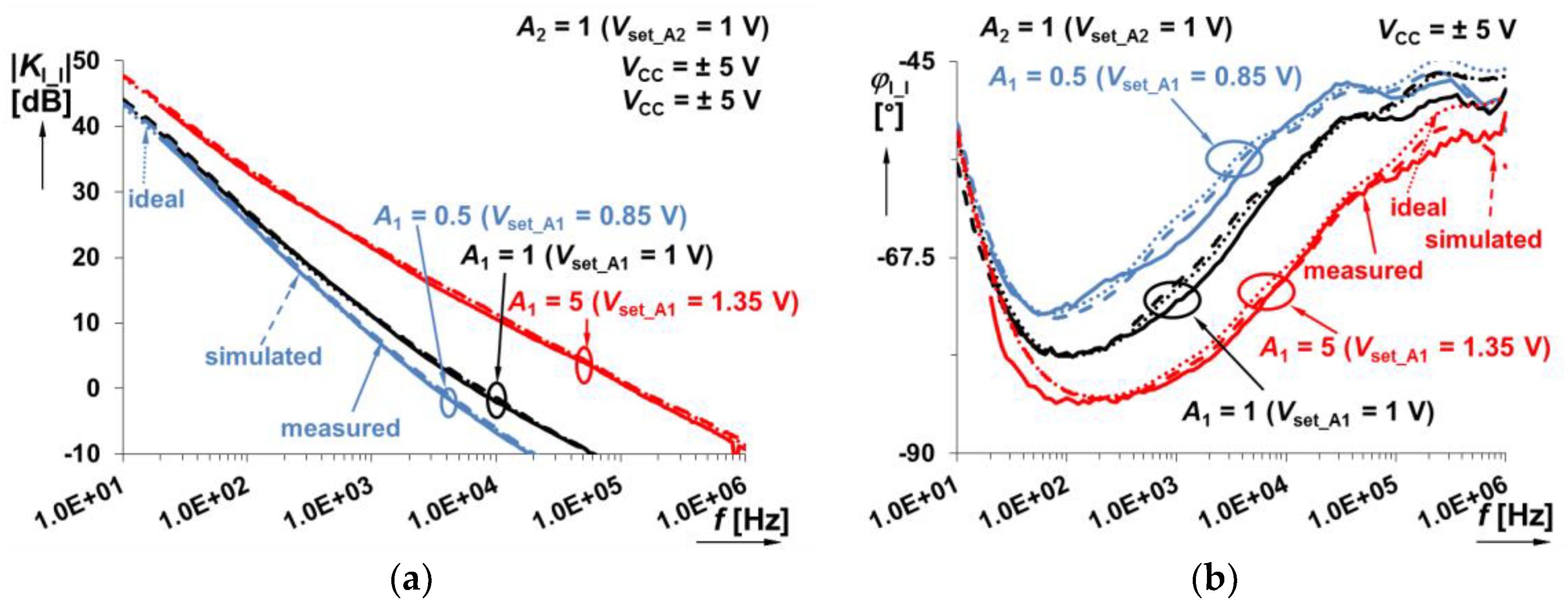

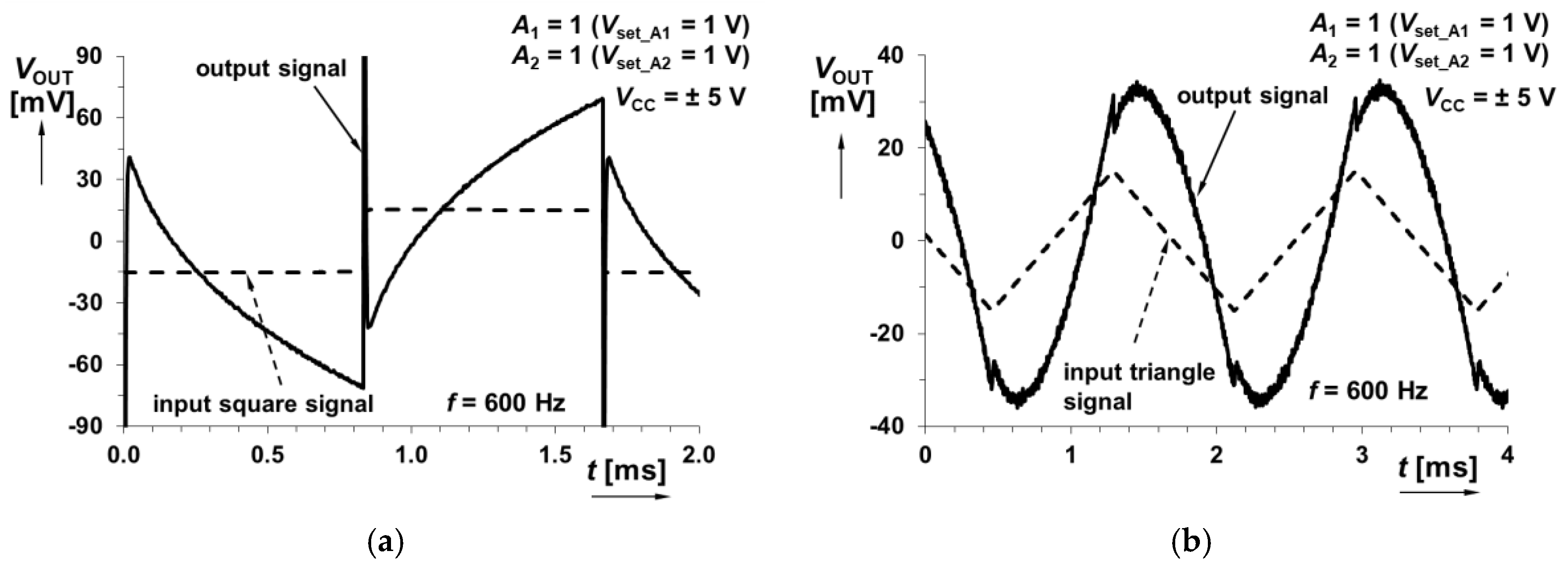

6.2. Analysis of Sum of Integer and Fractional-Order Integrator Responses

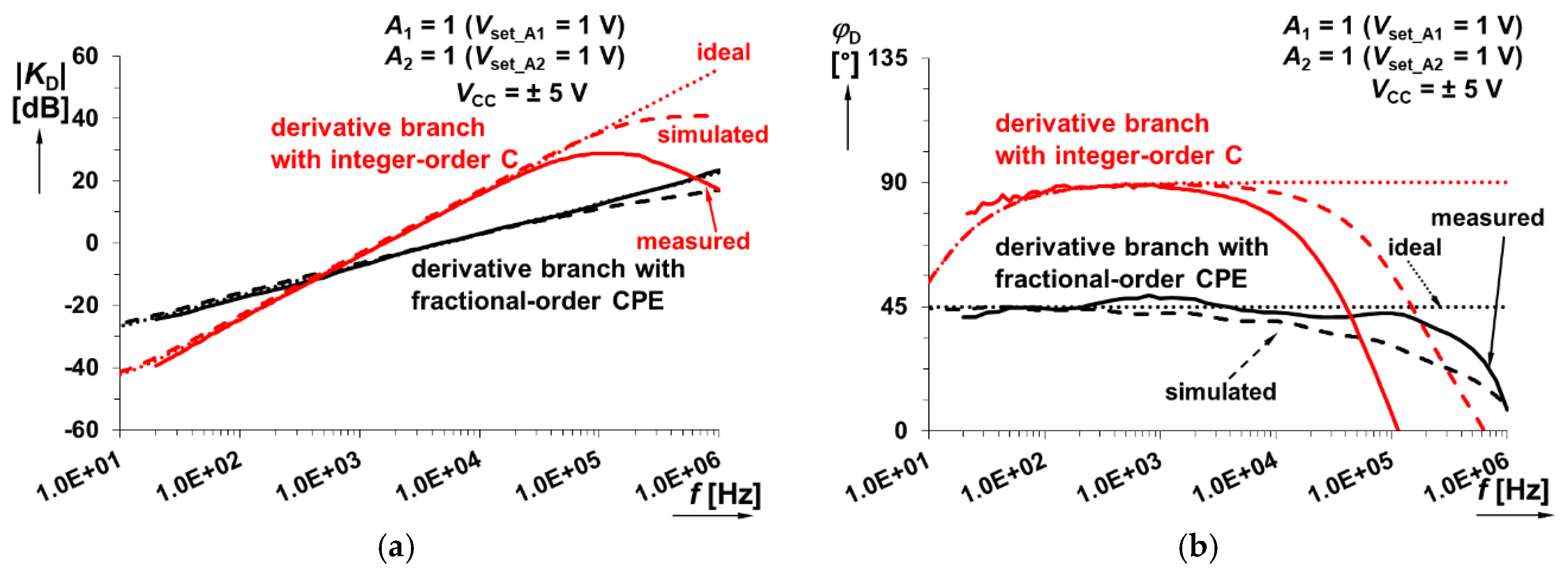

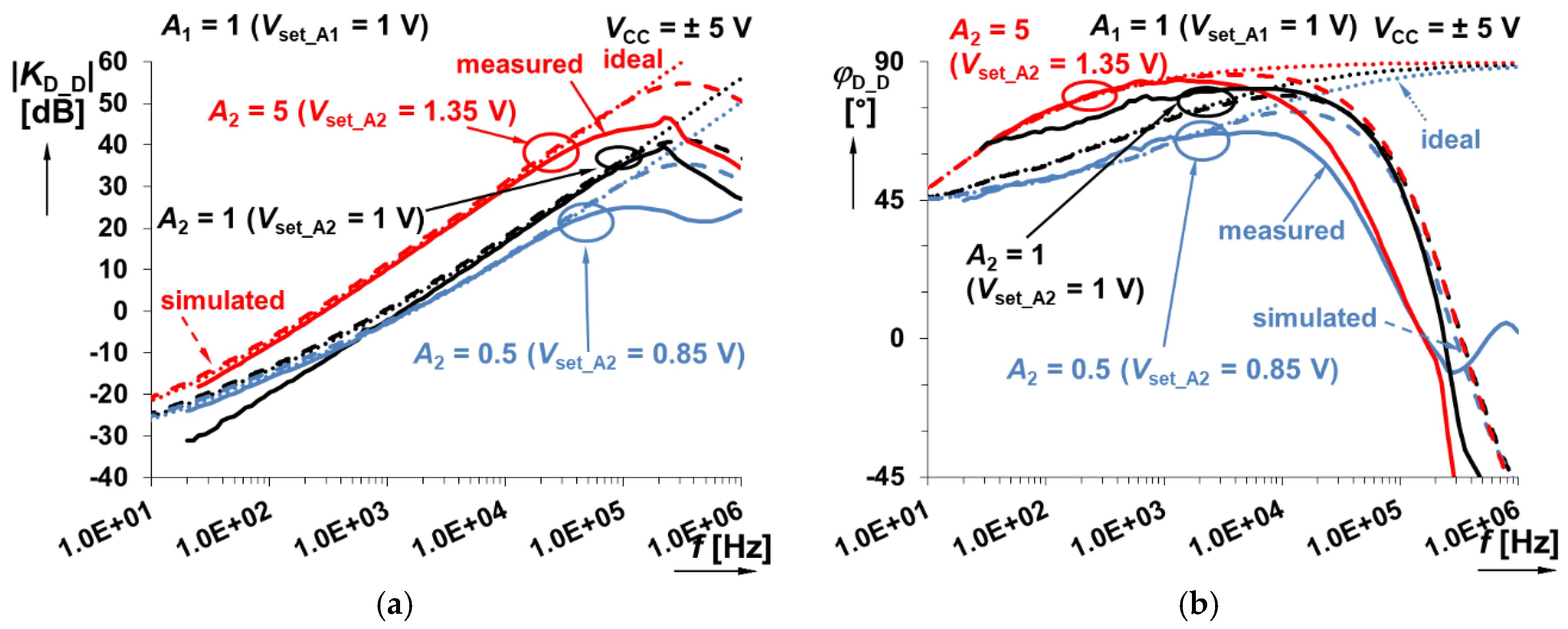

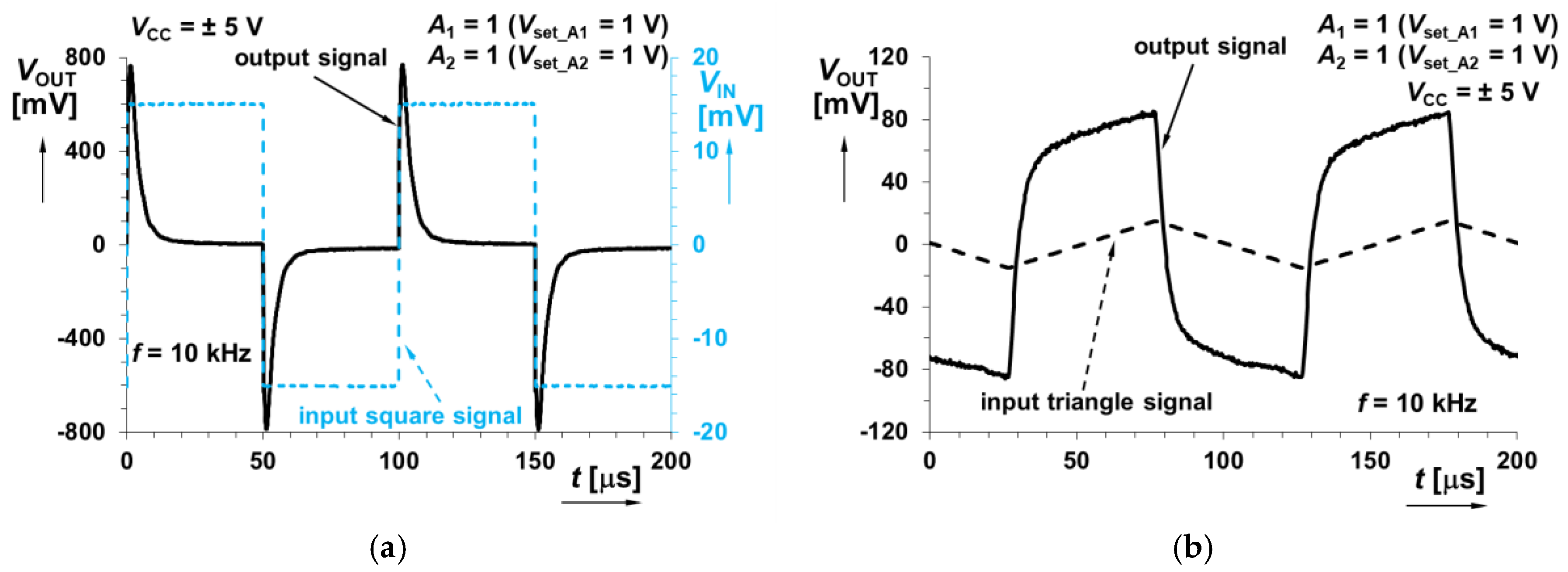

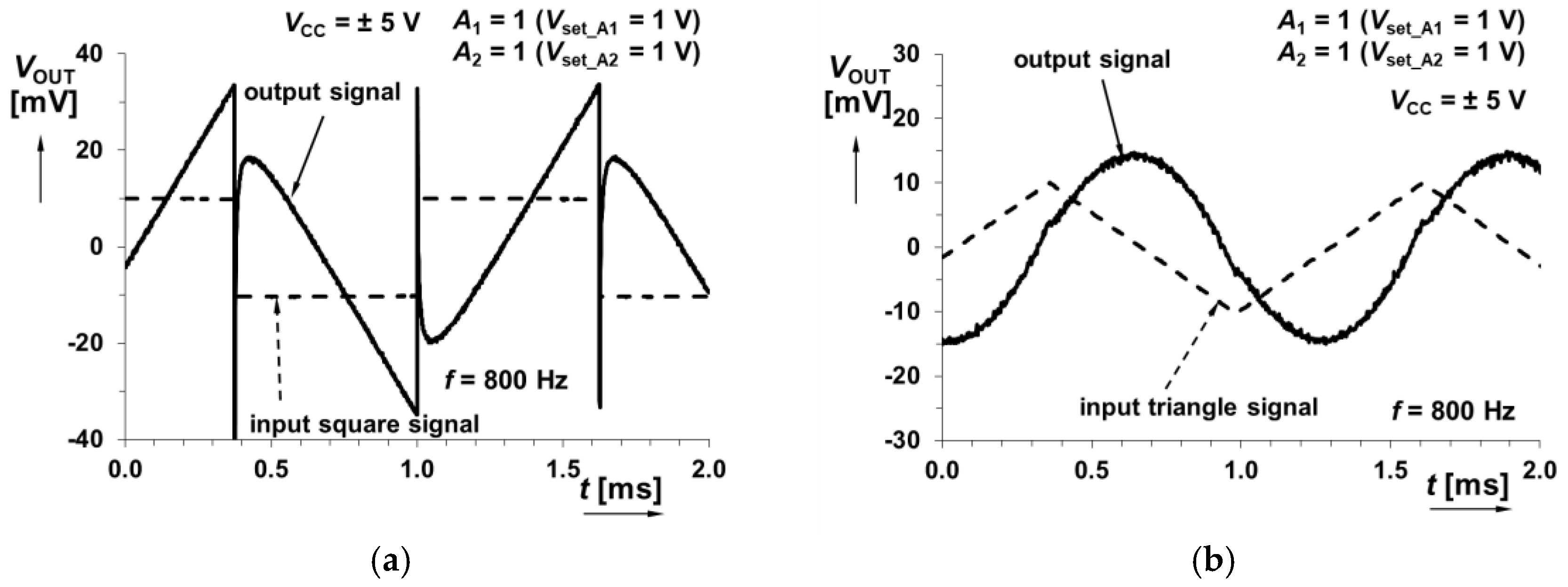

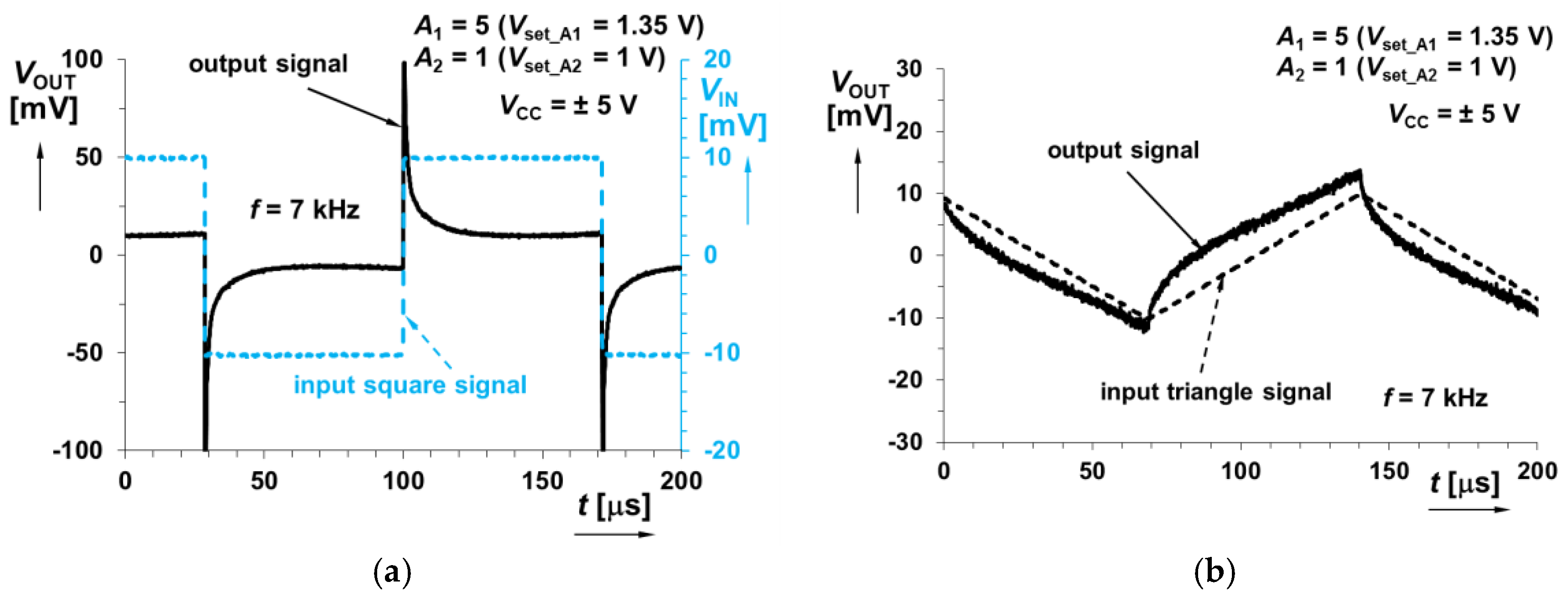

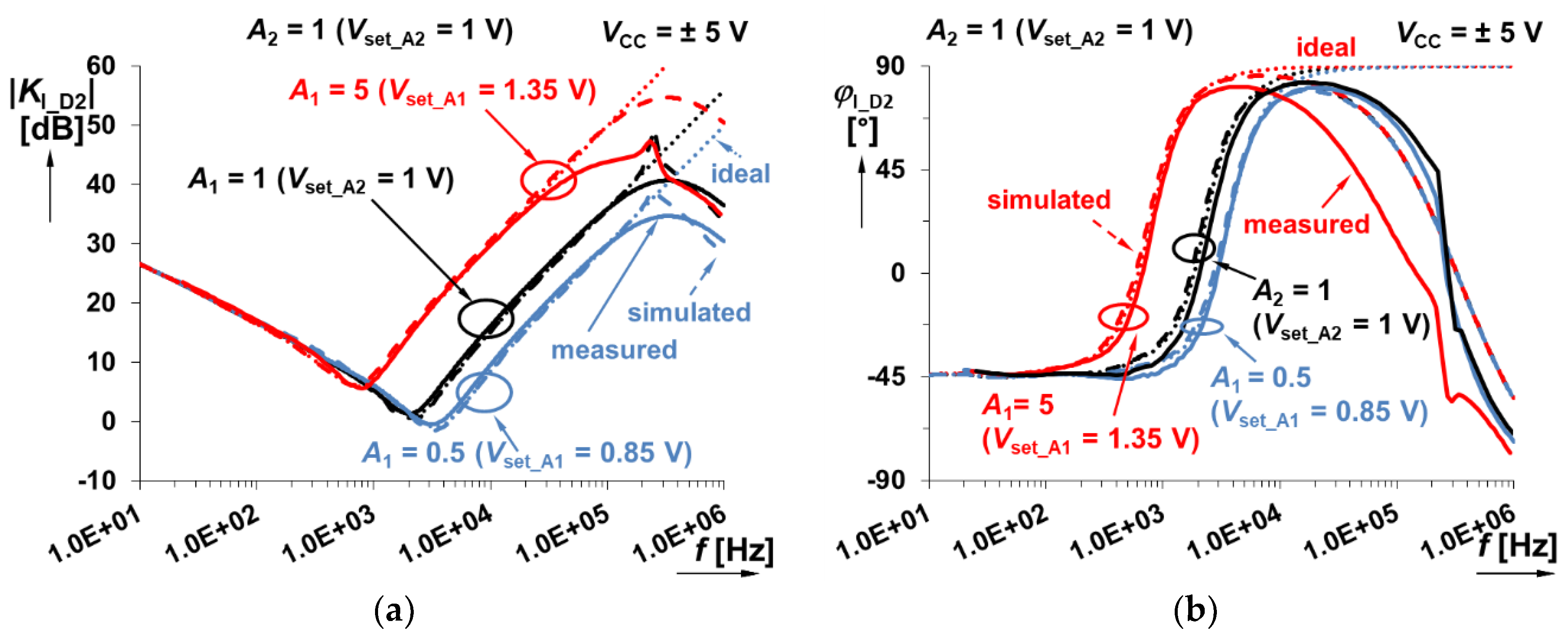

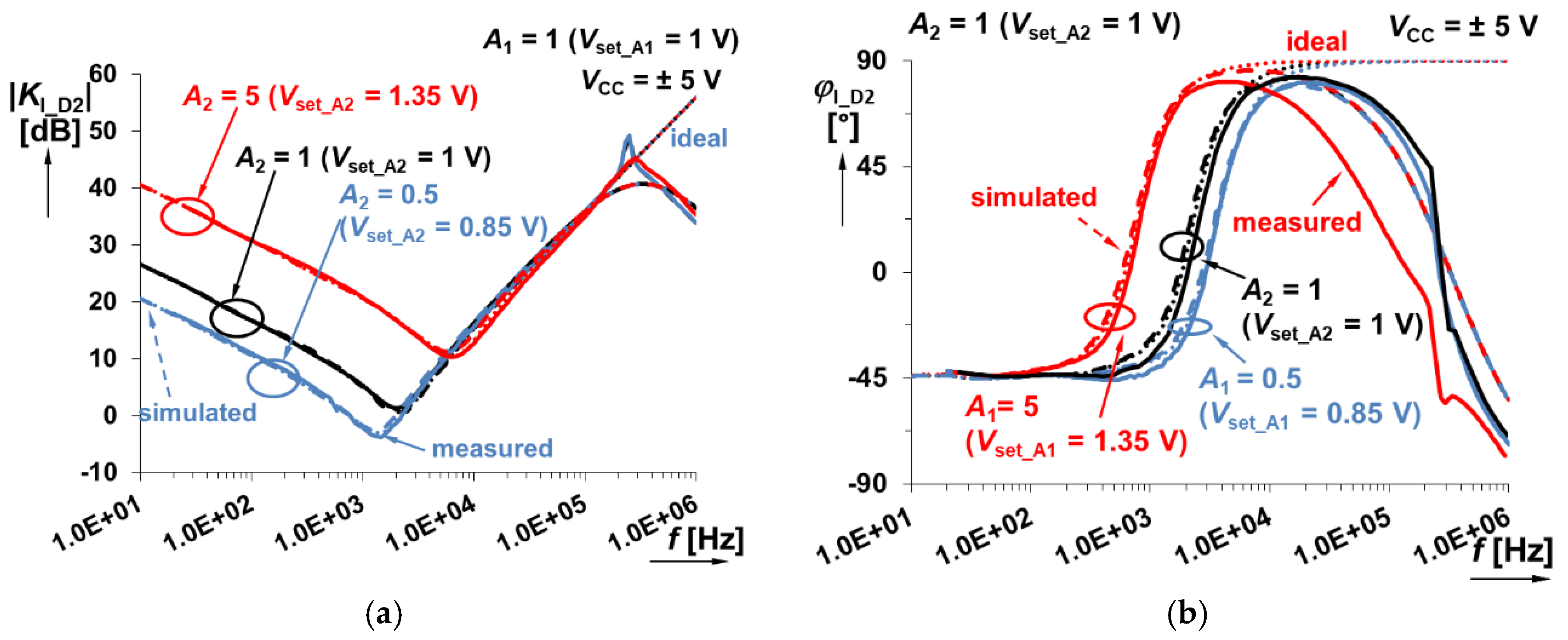

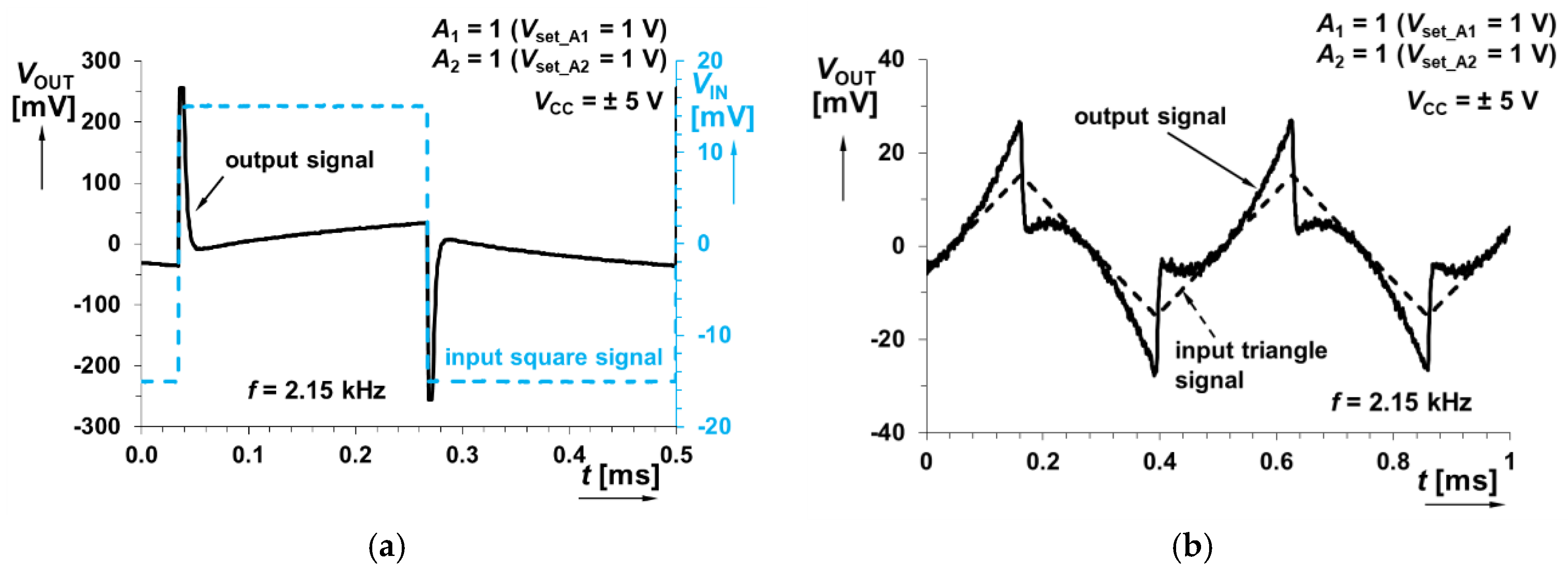

6.3. Analysis of Sum of Integer and Fractional-Order Differentiator Responses

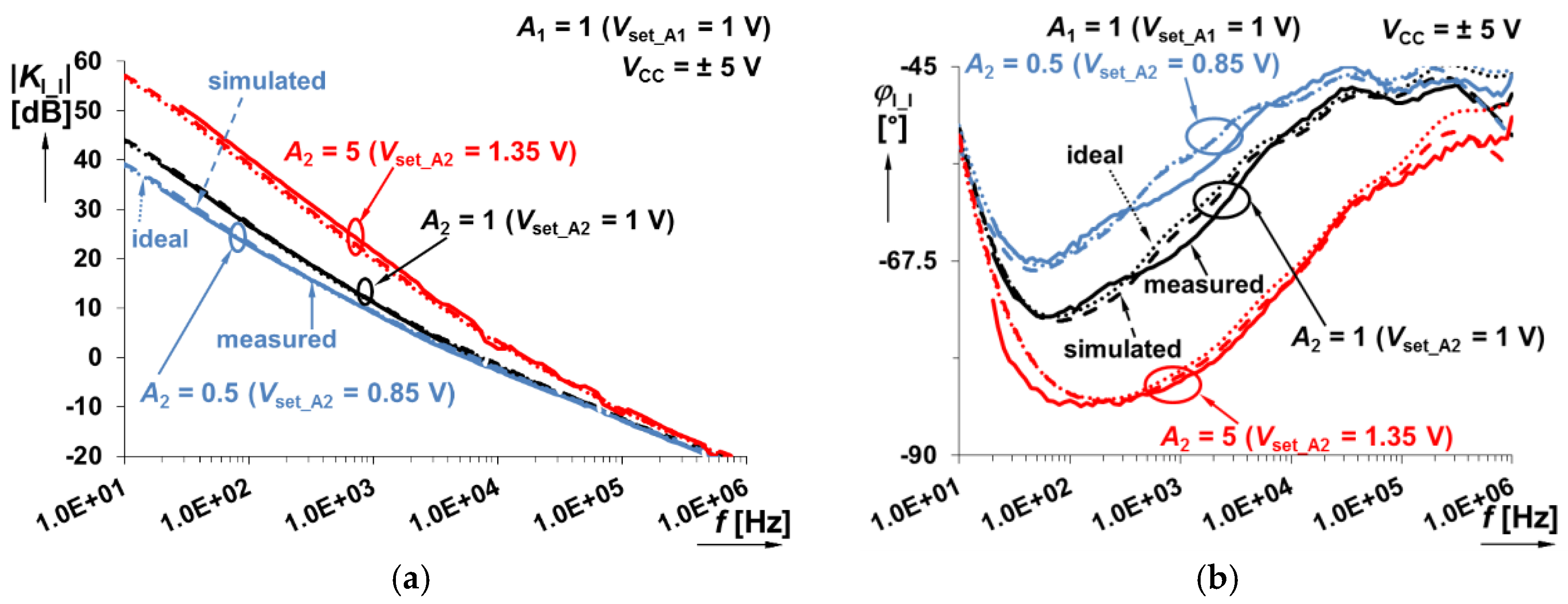

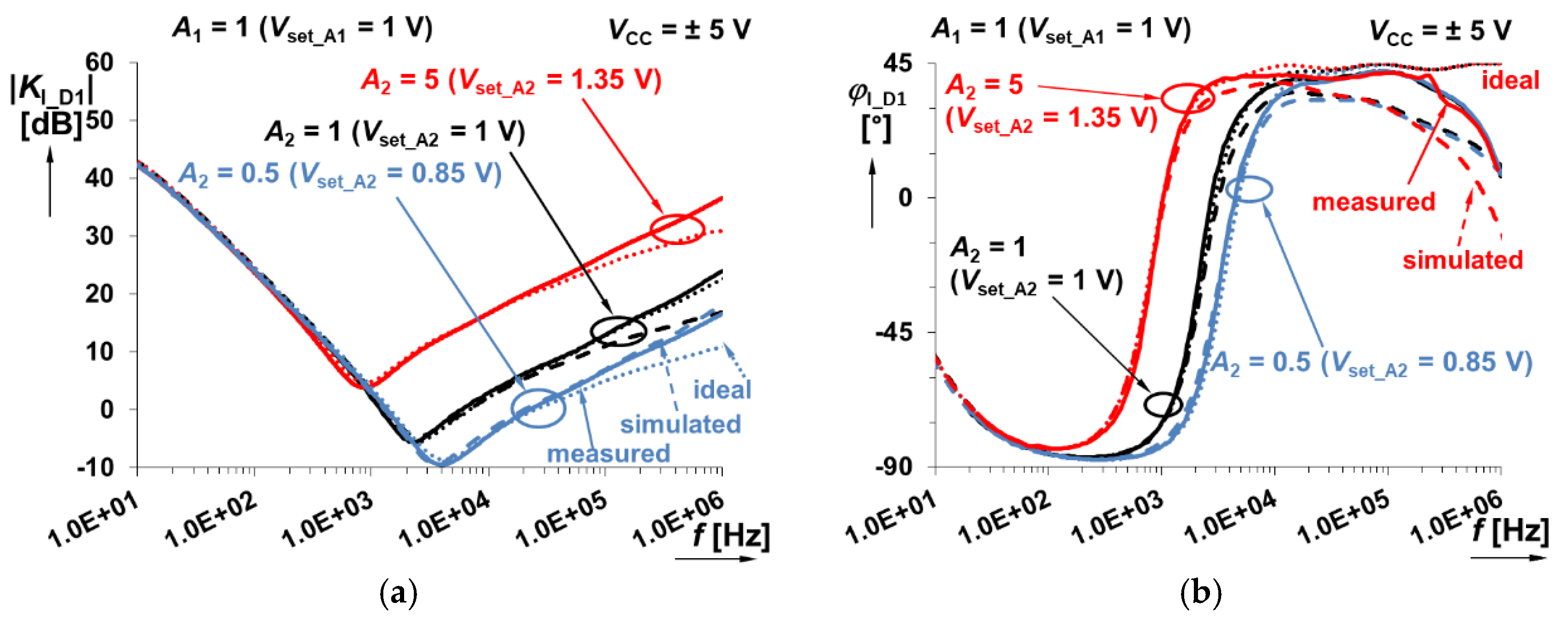

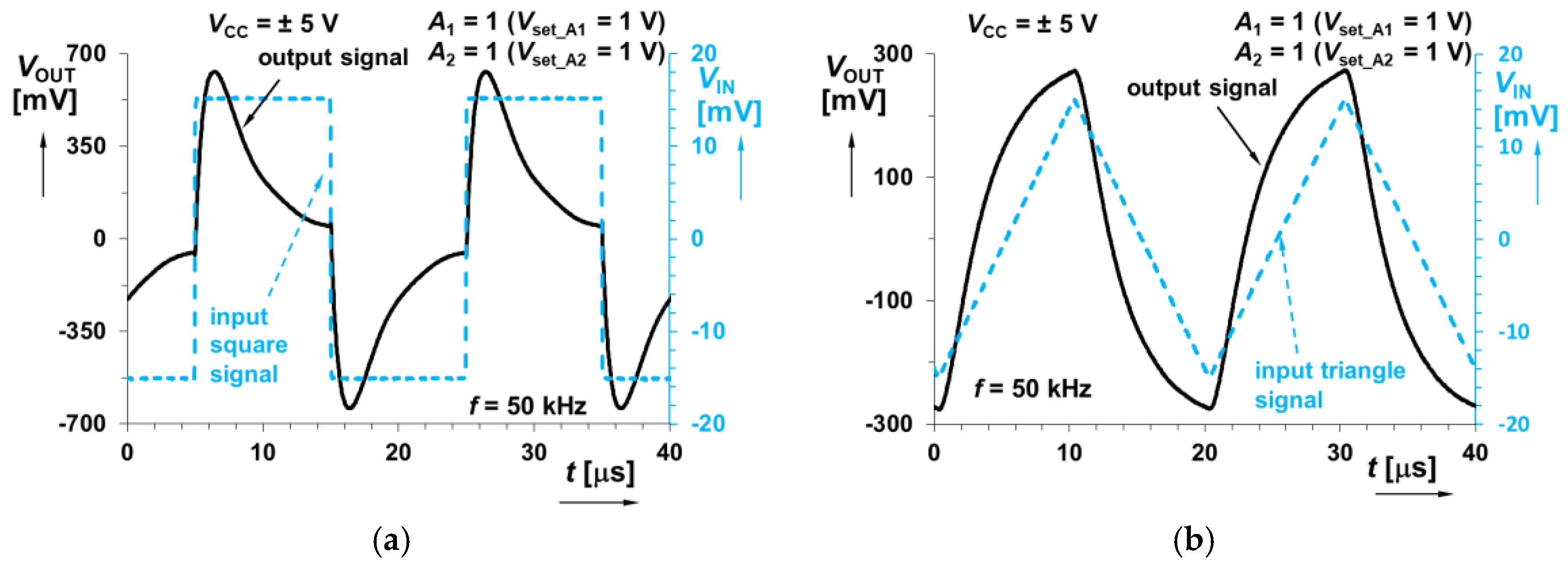

6.4. Analysis of Sum of Integer-Order Integrator and Fractional-Order Differentiator Responses

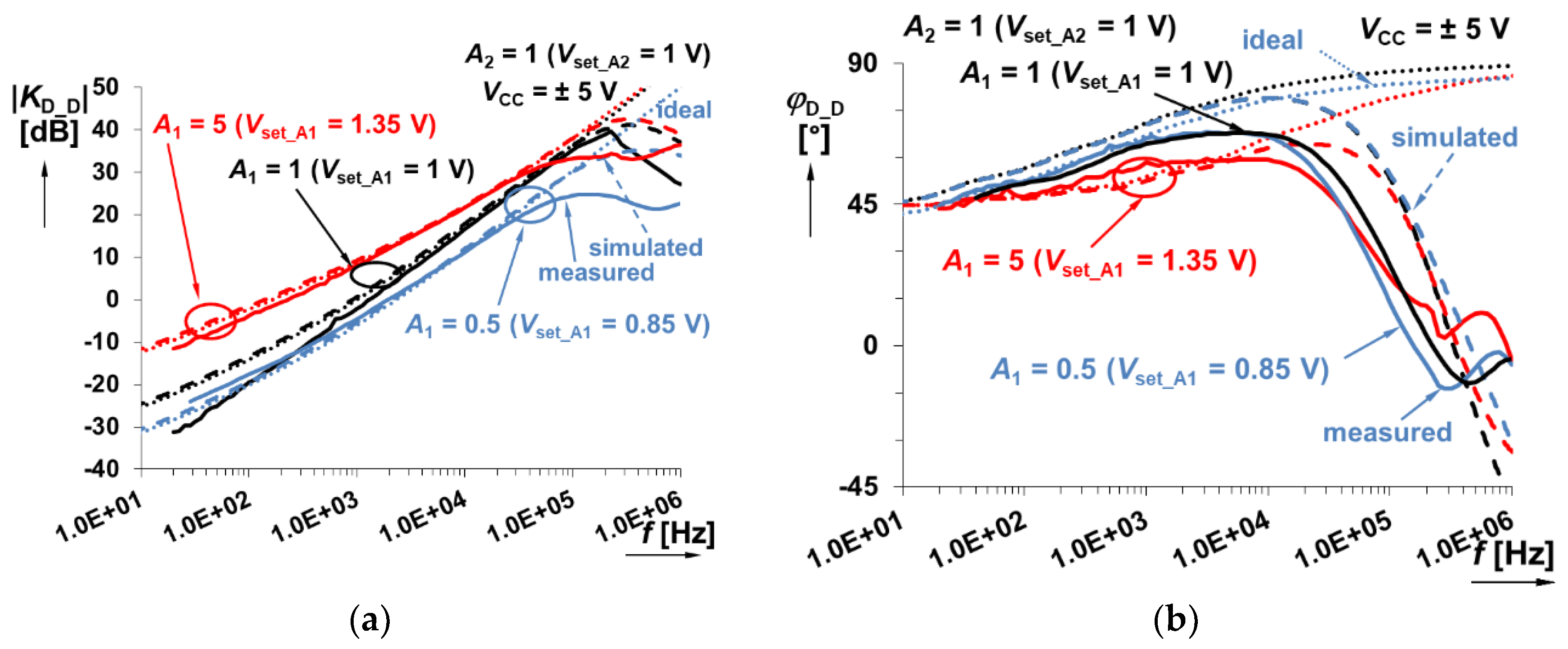

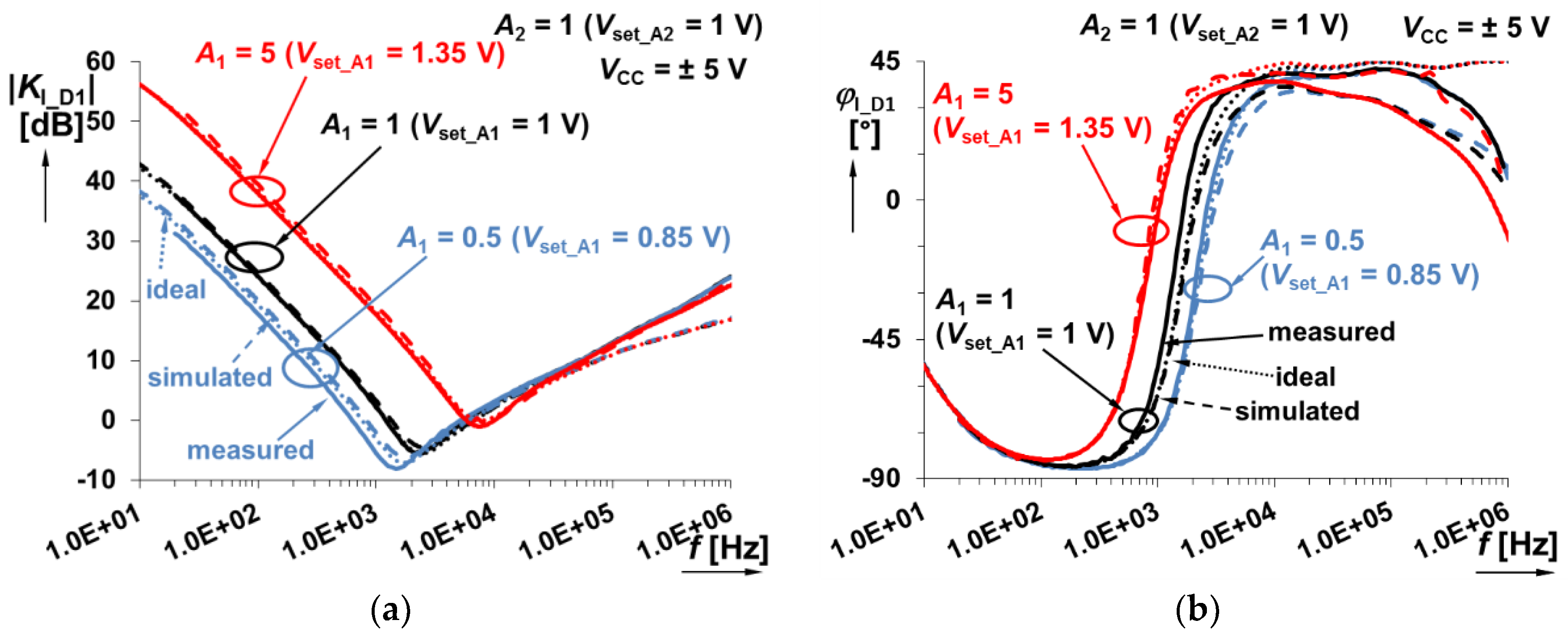

6.5. Analysis of Sum of Fractional-Order Integrator and Integer-Order Differentiator Responses

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Elwakil, A.S. Fractional-order circuits and systems: An emerging interdisciplinary research area. IEEE Circuits Syst. Mag. 2010, 10, 40–50. [Google Scholar] [CrossRef]

- Mondal, D.; Biswas, K. Performance study of fractional order integrator using single-component fractional order element. IET Circuits Devices Syst. 2011, 5, 334–342. [Google Scholar] [CrossRef]

- Goyal, D.; Varshney, P. Analog Realization of Electronically Tunable Fractional-Order Differ-Integrators. Arab. J. Sci. Eng. 2019, 44, 1933–1948. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Psychalinos, C. Ultra-low voltage fractional-order circuits using current mirrors. Int. J. Circuit Theory Appl. 2016, 44, 109–126. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Psychalinos, C.; Elwakil, A.S.; Salama, K.N. Experimental verification of on-chip CMOS fractional-order capacitor emulators. Electron. Lett. 2016, 52, 1298–1300. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Kartci, A.; Koton, K.; Herencsar, N.; Psychalinos, C. Comparative Study of Fractional-Order Differentiators and Integrators. In Proceedings of the 40th International Conference on Telecommunications and Signal Processing (TSP), Barcelona, Spain, 5–7 July 2017; pp. 714–717. [Google Scholar]

- Kapoulea, S.; Psychalinos, C.; Elwakil, A.S. Single active element implementation of fractional-order differentiators and integrators. AEU Int. J. Electron. Commun. 2018, 97, 6–15. [Google Scholar] [CrossRef]

- Bertsias, R.; Psychalinos, C.; Elwakil, A.S.; Safari, L.; Minaei, S. Design and application examples of CMOS fractional-order differentiators and integrators. Microelectron. J. 2019, 83, 155–167. [Google Scholar] [CrossRef]

- Sotner, R.; Jerabek, J.; Langhammer, L.; Polak, L.; Jaikla, W.; Prommee, P. Operational Frequency Bandwidth Rescalable Implementations of Constant Phase Devices. In Proceedings of the 29th International Conference Radioelektronika, Pardubice, Czech Republic, 16–18 April 2019; pp. 1–6. [Google Scholar]

- Podlubny, I.; Vinagre, B.; O’leary, P.; Dorcak, L. Analogue realizations of fractional-order controllers. Nonlinear Dyn. 2002, 29, 281–296. [Google Scholar] [CrossRef]

- Charef, A. Analogue realisation of fractional-order integrator, differentiator and fractional PI/spl lambda/D/spl mu/ controller. IEE Proc. Control. Theory Appl. 2006, 153, 714–720. [Google Scholar] [CrossRef]

- Muniz-Montero, C.; Garcia-Jimenez, L.V.; Sanchez-Gaspariano, L.A.; Sanchez-Lopez, C.; Gonzalez-Diaz, V.R.; Tlelo-Cuautle, E. New alternatives for analog implementation of fractional-order integrators, differentiators and PID controllers based on integer order integrators. Nonlinear Dyn. 2017, 90, 241–256. [Google Scholar] [CrossRef]

- Dimeas, I.; Petras, I.; Psychalinos, C. New analog implementation technique for fractional-order controlled: A dc motor control. AEU Int. J. Electron. Commun. 2017, 78, 192–200. [Google Scholar] [CrossRef]

- Domansky, O.; Sotner, R.; Langhammer, L.; Jerabek, J.; Psychalinos, C.; Tsirimokou, G. Practical Design of RC Approximants of Constant Phase Elements and Their Implementation in Fractional-Order PID Regulators Using CMOS Voltage Differencing Current Conveyors. Circuits Syst. Signal Process. 2019, 38, 1520–1546. [Google Scholar] [CrossRef]

- Sotner, R.; Jerabek, J.; Kartci, A.; Domansky, O.; Herencsar, N.; Kledrowetz, V.; Alagoz, B.; Yeroglu, C. Electronically reconfigurable two-path fractional-order PI/D controller employing constant phase blocks based on bilinear segments using CMOS modified current differencing unit. Microelectron. J. 2019, 86, 114–129. [Google Scholar] [CrossRef]

- Tolba, M.F.; AboAlNaga, B.M.; Said, L.A.; Madian, A.H.; Radwan, A.G. Fractional order integrator/differentiator: FPGA implementation and FOPID controller application. AEU Int. J. Electron. Commun. 2019, 98, 220–229. [Google Scholar] [CrossRef]

- Tolba, M.F.; Said, L.A.; Madian, A.H.; Radwan, A.G. FPGA Implementation of the Fractional Order Integrator/Differentiator: Two Approaches and Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1484–1495. [Google Scholar] [CrossRef]

- Herencsar, N.; Kartci, A.; Koton, J.; Sotner, R.; Alagoz, B.B.; Yeroglu, C. Analogue Implementation of a Fractional-PIλ Controller for DC Motor Speed Control. In Proceedings of the 28th IEEE International Symposium on Industrial Electronics (ISIE), Vancouver, BC, Canada, 12–14 June 2019; pp. 467–472. [Google Scholar]

- Sotner, R.; Jerabek, J.; Herencsar, N.; Petrzela, J.; Dostal, T.; Vrba, K. First-order adjustable transfer sections for synthesis suitable for special purposes in constant phase block approximation. AEU Int. J. Electron. Commun. 2015, 69, 1334–1345. [Google Scholar] [CrossRef]

- Sotner, R.; Petrzela, J.; Domansky, O.; Dostal, T. Current feedback operational amplifier based two-port frequency equalizer. In Proceedings of the European Conference on Circuit Theory and Design (ECCTD), Catania, Italy, 4–6 September 2017; pp. 1–4. [Google Scholar]

- Sotner, R.; Polak, L.; Jerabek, J.; Petrzela, J. Simple two operational transconductance amplifiers-based electronically controllable bilinear two port for fractional-order synthesis. Electron. Lett. 2018, 54, 1164–1165. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Psychalinos, C.; Elwakil, A.S.; Salama, K.N. Experimental behavior evaluation of series and parallel connected constant phase elements. AEU Int. J. Electron. Commun. 2017, 74, 5–12. [Google Scholar] [CrossRef]

- Kartci, A.; Agambayev, A.; Herencsar, N.; Salama, K.N. Series-, Parallel-, and Inter-Connection of Solid-State Arbitrary Fractional-Order Capacitors: Theoretical Study and Experimental Verification. IEEE Access 2018, 6, 10933–10943. [Google Scholar] [CrossRef]

- Kartci, A.; Agambayev, A.; Farhat, M.; Herencsar, N.; Brancik, L.; Bagci, H.; Salama, K.N. Synthesis and Optimization of Fractional-Order Elements Using a Genetic Algorithm. IEEE Access 2019, 7, 80233–80246. [Google Scholar] [CrossRef]

- Semary, M.S.; Fouda, M.E.; Hassan, H.N.; Radwan, A.G. Realization of fractional-order capacitor based on passive symmetric network. J. Adv. Res. 2019, 18, 147–159. [Google Scholar] [CrossRef] [PubMed]

- Sotner, R.; Jerabek, J.; Petrzela, J.; Domansky, O.; Tsirimokou, G.; Psychalinos, C. Synthesis and design of constant phase elements based on the multiplication of electronically controllable bilinear immittances in practice. AEU Int. J. Electron. Commun. 2017, 78, 98–113. [Google Scholar] [CrossRef]

- Kadlcik, L.; Horsky, P. A CMOS Follower-Type Voltage Regulator with a Distributed-Element Fractional-Order Control. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2753–2763. [Google Scholar] [CrossRef]

- Sotner, R.; Petrzela, J.; Jerabek, J.; Herencsar, N.; Andriukaitis, D. Design of Fractional-Order Integrator Controlled by Single Voltage Gain. In Proceedings of the 42nd International Conference on Telecommunications and Signal Processing (TSP), Budapest, Hungary, 1–3 July 2019; pp. 360–364. [Google Scholar]

- Biolek, D.; Senani, R.; Biolkova, V.; Kolka, Z. Active elements for analog signal processing: Classification, review, and new proposal. Radioengineering 2008, 17, 15–32. [Google Scholar]

- Texas Instruments. VCA810 High Gain Adjust Range, Wideband and Variable Gain Amplifier. 2015. Available online: http://www.ti.com/lit/ds/symlink/vca810.pdf (accessed on 3 November 2019).

- Analog Devices. LT1364/LT1365 Dual and Quad 70 MHz, 1000 V/us Op Amps. 1994. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/13645fa.pdf (accessed on 3 November 2019).

- Analog Devices. AD8129/8130 Low Cost 270 MHz Differential Receiver Amplifiers. 2005. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD8129_8130.pdf (accessed on 3 November 2019).

- Valsa, J.; Dvorak, P.; Friedl, M. Network model of the CPE. Radioengineering 2011, 20, 616–626. [Google Scholar]

- Valsa, J.; Vlach, J. RC models of a constant phase element. Int. J. Circuit Theory Appl. 2013, 41, 59–67. [Google Scholar] [CrossRef]

- Keysight. Keysight InfiniiVision 3000T X-Series Oscilloscopes User’s Guide. 2017. Available online: https://www.keysight.com/main/techSupport.jspx?nid=-32541.1150349&pid=x202172&cc=CZ&lc=eng&pageMode=PL (accessed on 3 November 2019).

| Reference | Design Target (Both = Integrator and Differentiator) | Simple Single Parameter Electronic Time Constant Tuning | Active Devices | Solution of Fractional-Order Part | Topological Circuit Complexity | SW Support not Required | Tested Operational Bandwidth | Application, if Any | Response Based on Combination of Integer and Fractional-Order |

|---|---|---|---|---|---|---|---|---|---|

| Integrators/Differentiators Only | |||||||||

| [2] | integrator | No | OAs | passive | Low | Yes | <1 MHz | N/A | - |

| [3] | both | Yes | DVCCTA | passive | Low | Yes | <100 kHz | N/A | - |

| [4] | both | No | CMOS current mirrors | active | Low | Yes | <100 Hz | Sum of reconfigurable filtering responses | No |

| [5] | integrator | No | CMOS OTAs | active | Medium | Yes | <1 kHz | N/A | - |

| [6] | both | No | CFOAs | active | Medium | Yes | <100 kHz | N/A | - |

| [7] | both | No | Single EX-CCII | passive | Low | Yes | <1 kHz | PID | No |

| [8] | both | No | CMOS block | active | Low | Yes | <100 Hz | high-pass/low-pass filter | No |

| [9] | integrator | Yes | CCII+, VGA | active | High | Yes | <10 MHz | N/A | - |

| Integrators/Differentiators in Controllers | |||||||||

| [10] | integrator | No | OAs | passive | Low | Yes | <10 kHz | I controller | - |

| [11] | both | No | OAs | passive | Low | Yes | <100 Hz | PID | No |

| [12] | both | N/A | FPAA (OAs) | active | High | No | <100 Hz | PID | No |

| [13] | both | No | CMOS OTAs | active | Medium | Yes | <1 kHz | PID | No |

| [14] | both | No | CMOS VDCCs | passive | Low | Yes | <1 MHz | PID | No |

| [15] | both | No | MCDUs | active | Medium | Yes | <10 MHz | PI/D | No |

| [16] | both | N/A | FPGA/DSP * | active | High | No | <tens of MHz | PID | No |

| [17] | both | N/A | FPGA/DSP * | active | High | No | <tens of MHz | N/A | - |

| Bilinear Synthesis of Integrators/Differentiators | |||||||||

| [8] | both | No | CMOS block | active | Low | Yes | <1 MHz | Active CPE | - |

| [18] | both | No | CMOS OAs | active | High | Yes | <1 kHz | PI controller | No |

| [19] | integrator | No | CMOS OTAs | active | High | Yes | <10 MHz | N/A | - |

| [20] | both | No | CFOAs | active | Medium | Yes | <100 kHz | N/A | - |

| [21] | integrator | No | OTAs | active | Medium | Yes | <100 kHz | N/A | - |

| Proposed | |||||||||

| [3,5,7,9] | both | Yes | OAs, VGAs | passive | Low | Yes | <1 MHz | Sum of integer- and fractional-order responses | Yes |

| Theoretically Achievable Behavior for Variation of α | Tested for α = 0.5 (A1 = A2 = 1) | ||||||

|---|---|---|---|---|---|---|---|

| Solution | Magnitude Slope/Phase Shift (low Frequency Sub-Band) | Magnitude Slope/Phase Shift (High Frequency Sub-Band) | ExperimentallyEstimated Operational Range (Frequency Bandwidth) | Magnitude Slope/Phase Shift (High Frequency Sub-Band) | Magnitude Slope/Phase Shift (High Frequency Sub-Band) | Experimentally Estimated Dynamics Dependent on A1,2 Setting | Instability Compensation |

| Figure 3 | −20 dB/dec −90° | −20∙α dB/dec −α∙90° | 50 Hz–100 kHz | −17 dB/dec −78° | −10 dB/dec -49° | >50 dB | No |

| Figure 5 | 20∙α dB/dec α∙90° | 20 dB/dec 90° | 50 Hz–10 kHz | 16 dB/dec 45° | 19 dB/dec 80° | >60 dB | Integer-order integrator |

| Figure 7 | −20 dB/dec −90° | 20∙α dB/dec α∙90° | 50 Hz–10 kHz | −20 dB/dec −88° | 10 dB/dec +42° | >45 dB | Fractional-order differentiator |

| Figure 9 | −20∙α dB/dec −α∙90° | 20 dB/dec 90° | 50 Hz – 10 kHz | −10 dB/dec −45° | 21 dB/dec 85° | >45 dB | Integer-order differentiator |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sotner, R.; Domansky, O.; Jerabek, J.; Herencsar, N.; Petrzela, J.; Andriukaitis, D. Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations. Appl. Sci. 2020, 10, 54. https://doi.org/10.3390/app10010054

Sotner R, Domansky O, Jerabek J, Herencsar N, Petrzela J, Andriukaitis D. Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations. Applied Sciences. 2020; 10(1):54. https://doi.org/10.3390/app10010054

Chicago/Turabian StyleSotner, Roman, Ondrej Domansky, Jan Jerabek, Norbert Herencsar, Jiri Petrzela, and Darius Andriukaitis. 2020. "Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations" Applied Sciences 10, no. 1: 54. https://doi.org/10.3390/app10010054

APA StyleSotner, R., Domansky, O., Jerabek, J., Herencsar, N., Petrzela, J., & Andriukaitis, D. (2020). Integer-and Fractional-Order Integral and Derivative Two-Port Summations: Practical Design Considerations. Applied Sciences, 10(1), 54. https://doi.org/10.3390/app10010054