Electrical and Mechanical Analysis of Different TSV Geometries

Abstract

1. Introduction

2. Electrical Investigation of Through-Silicon Via (TSV) Structures

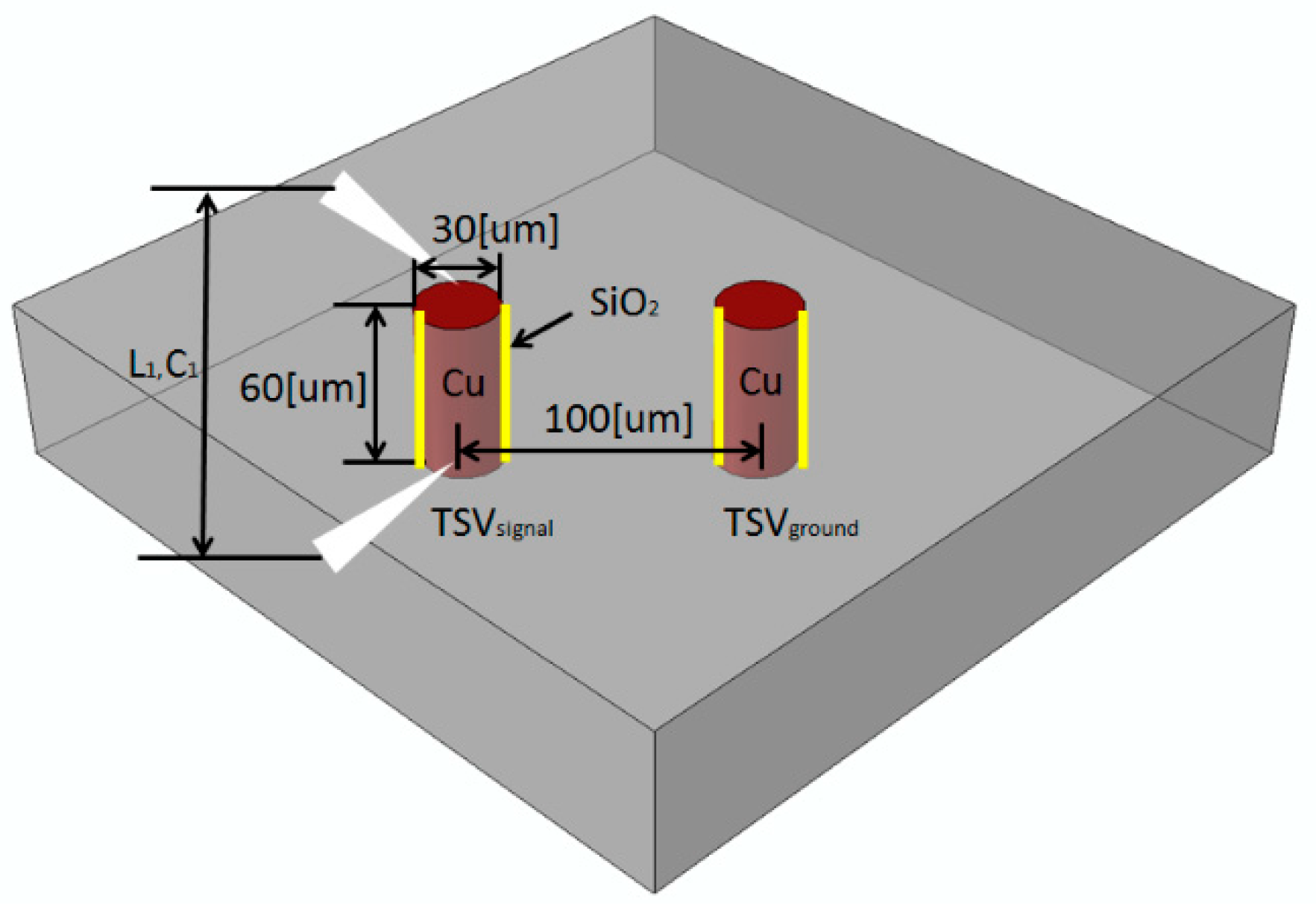

2.1. Through-Silicon Via (TSV) Structure and Manufacturing Process

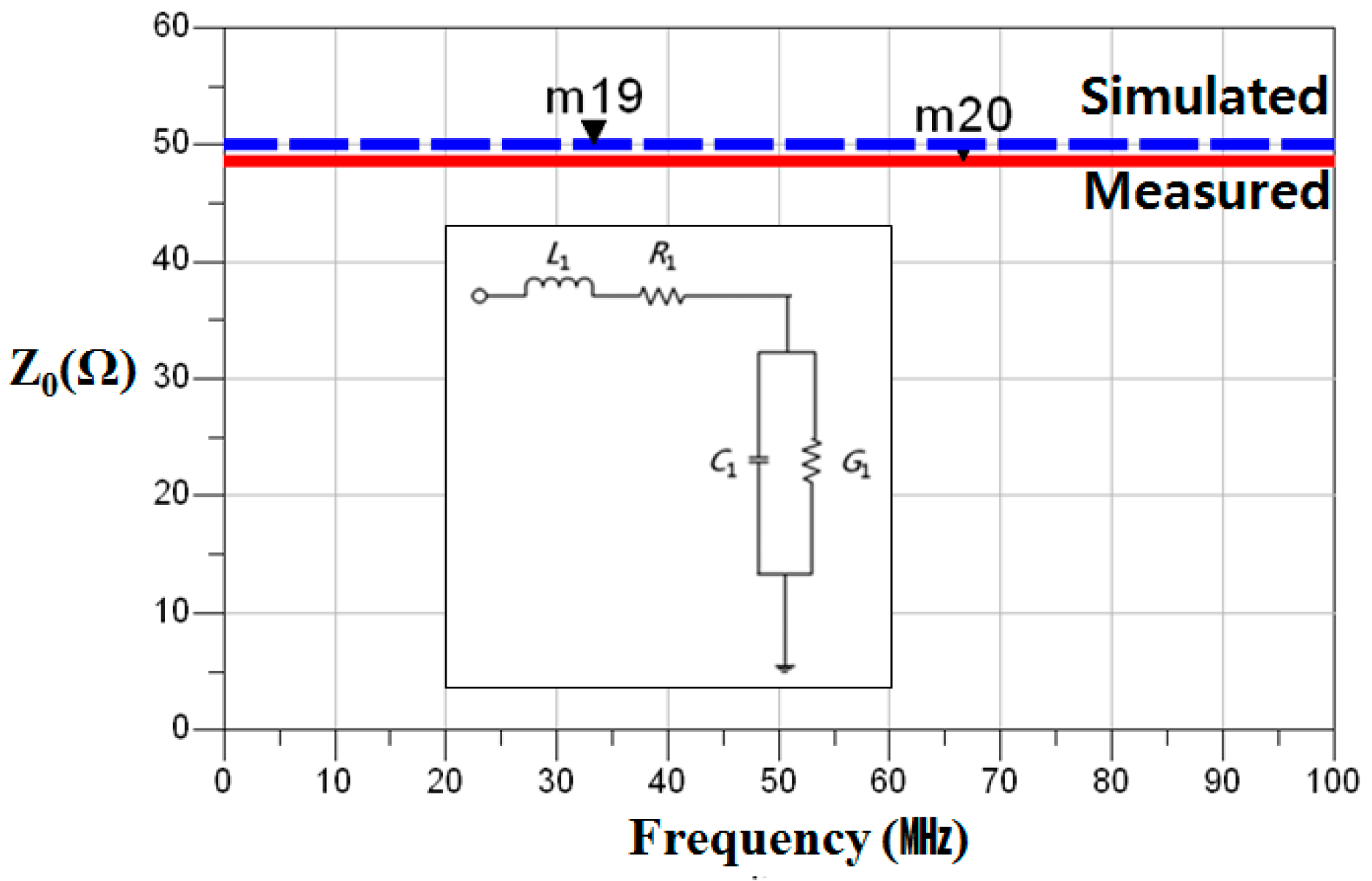

2.2. Electrical Simulation

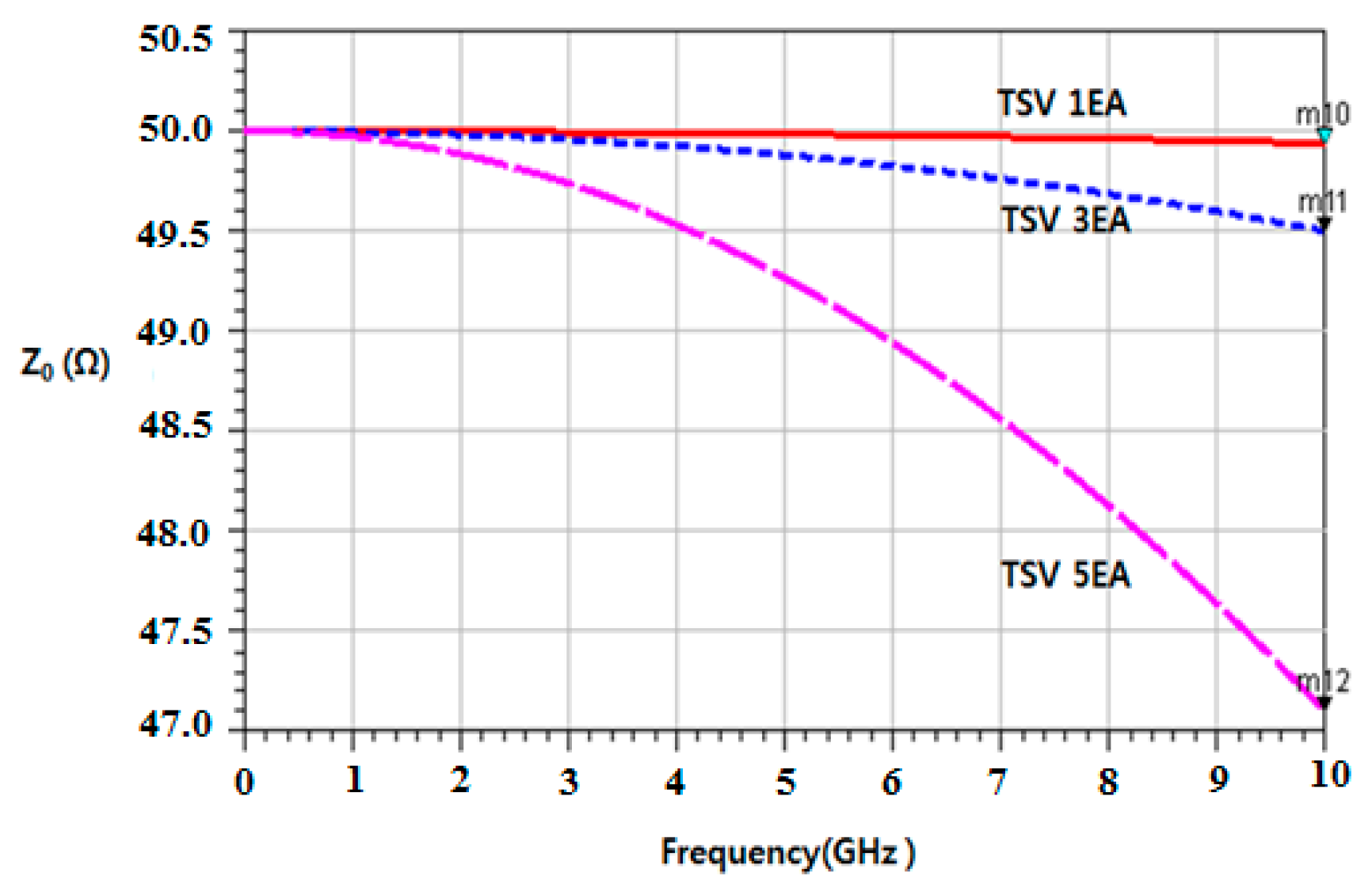

2.3. Characteristic Impedance of Multilayer TSV

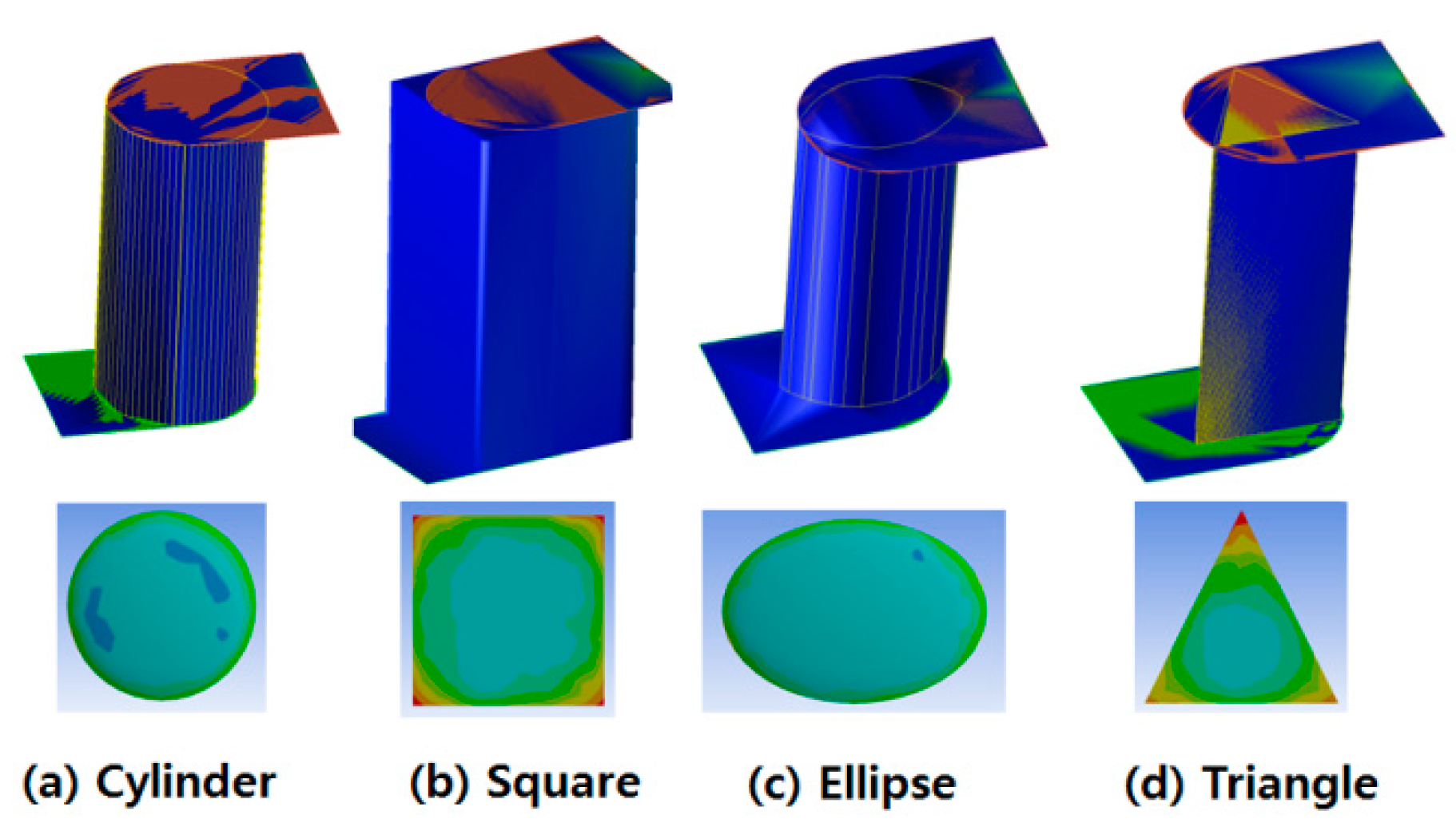

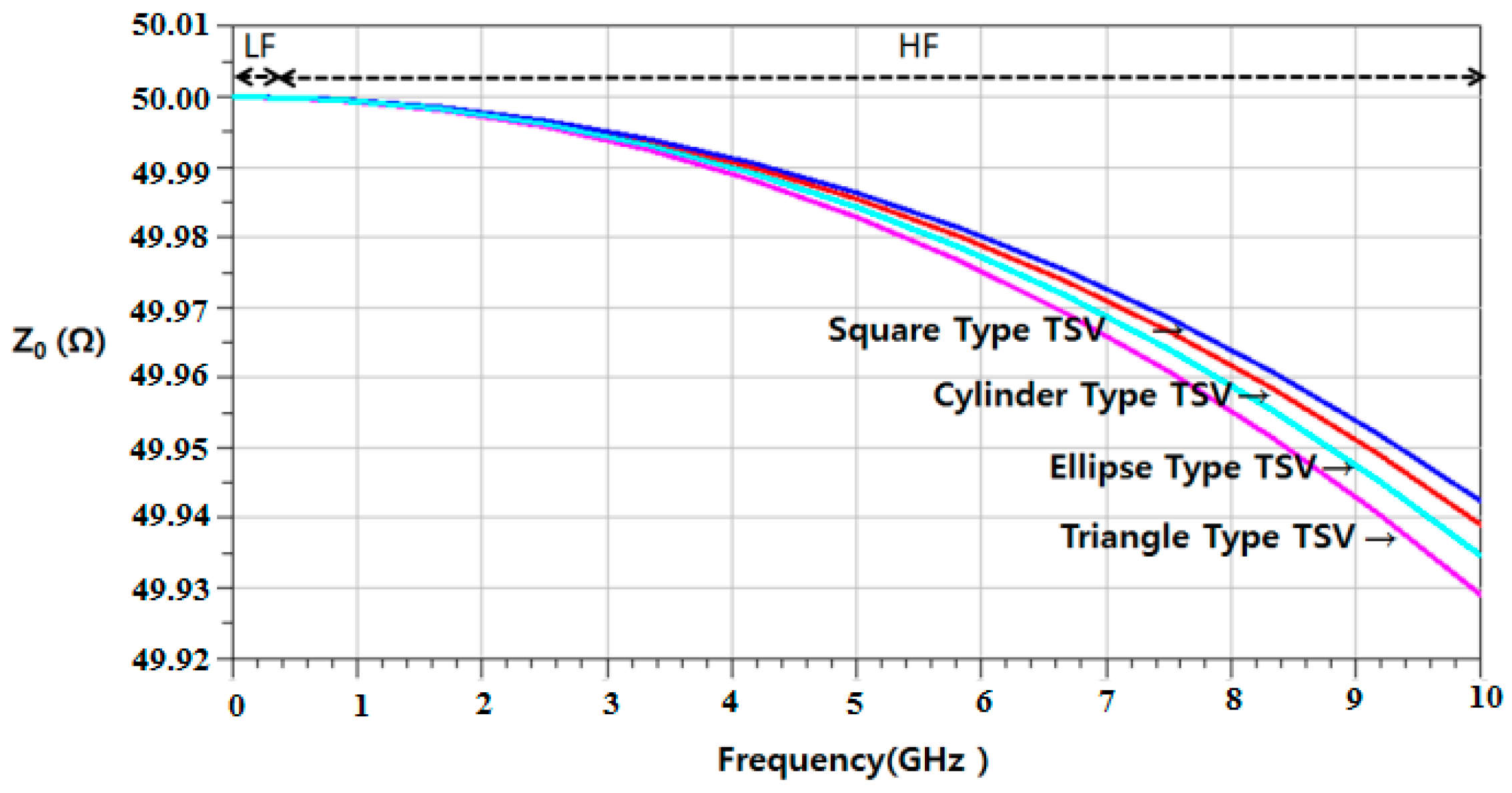

2.4. Characteristic Impedance for Different TSV Shapes

3. Mechanical Investigation of TSV Structures

3.1. Finite Element Simulation (FEM)

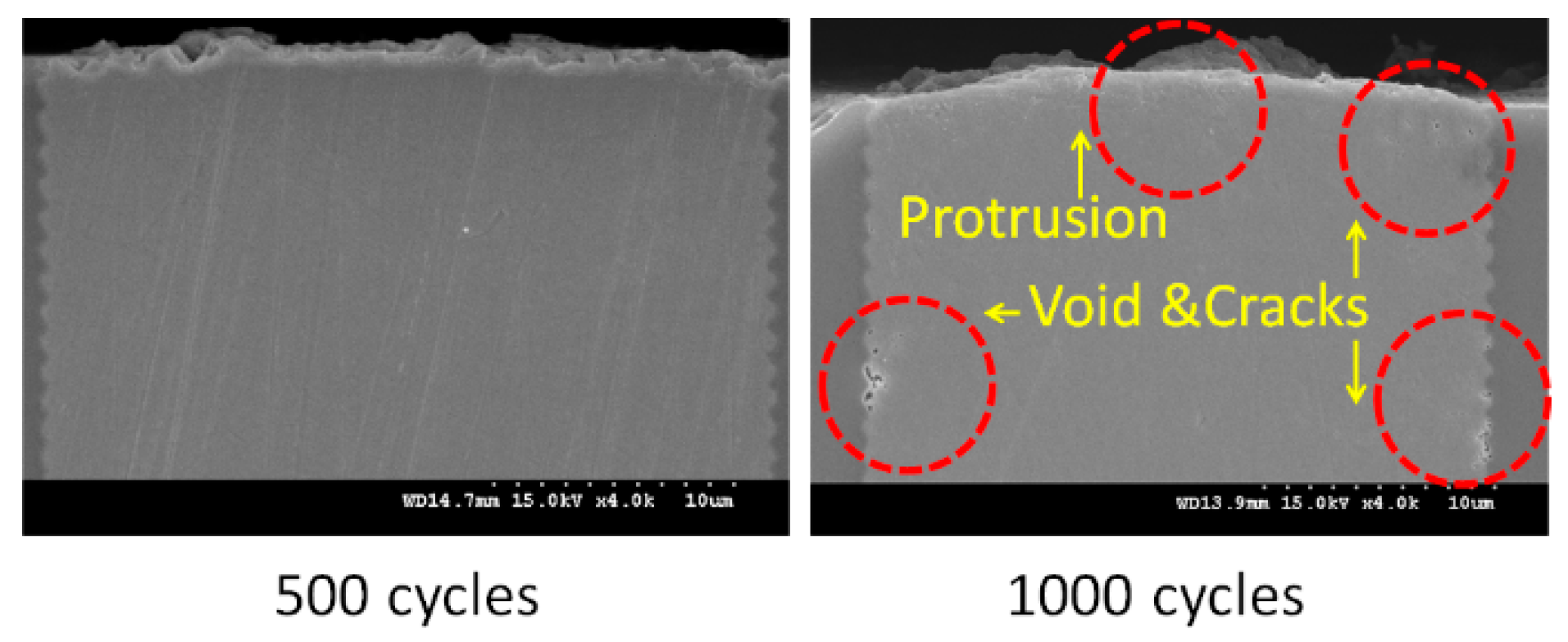

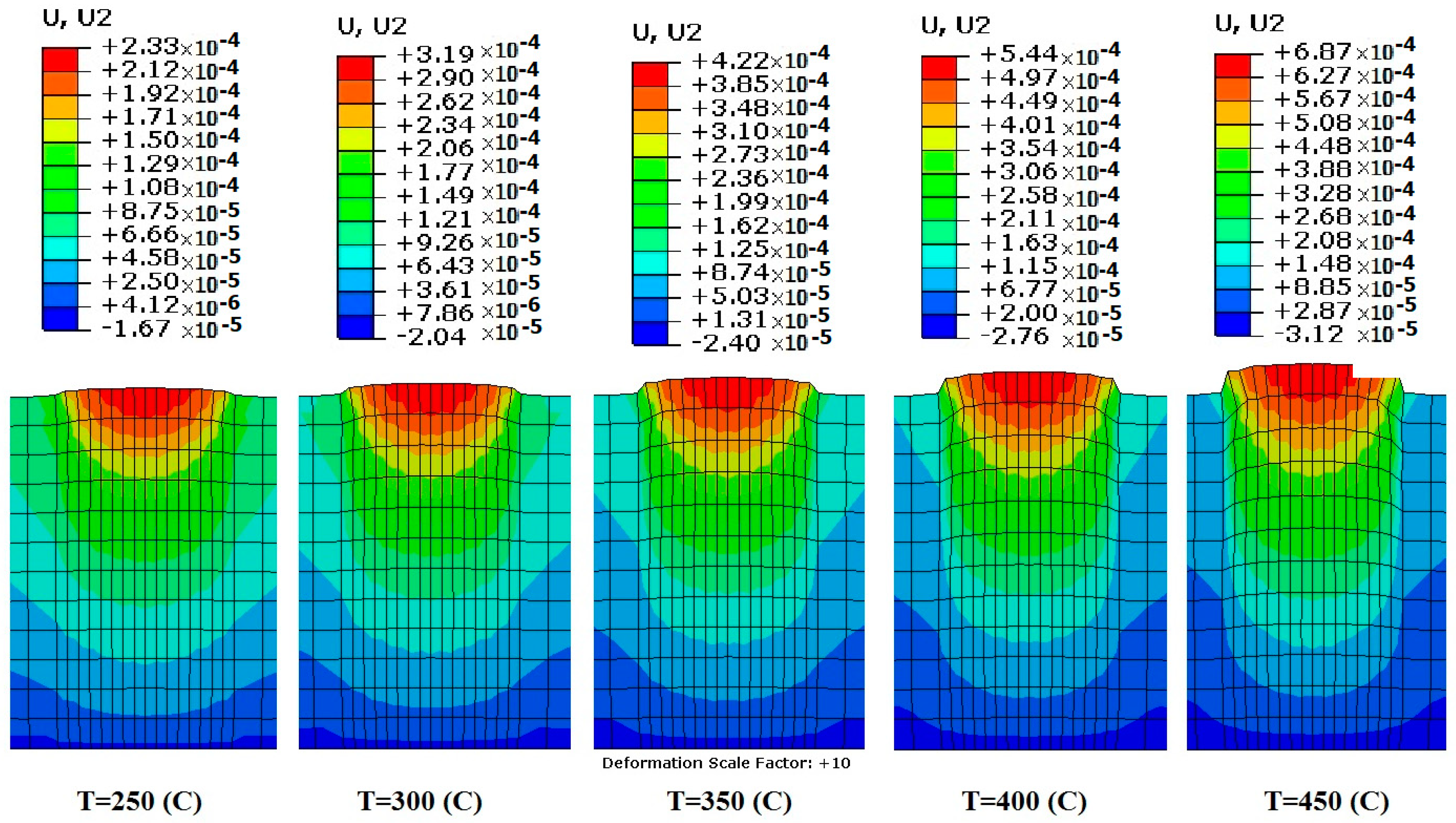

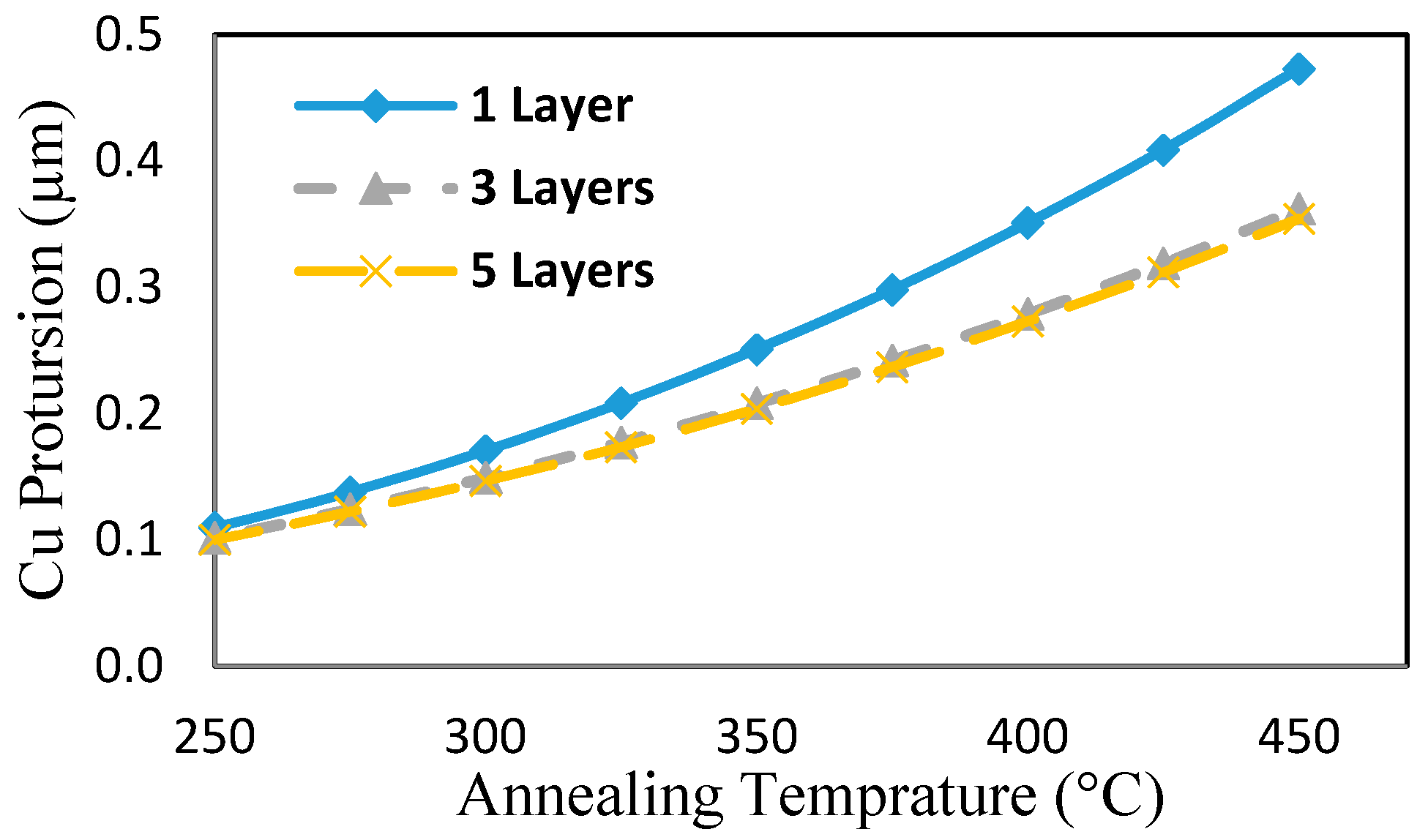

3.2. Protrusion on Single Layer TSV

3.3. Protrusion on Multilayer TSVs

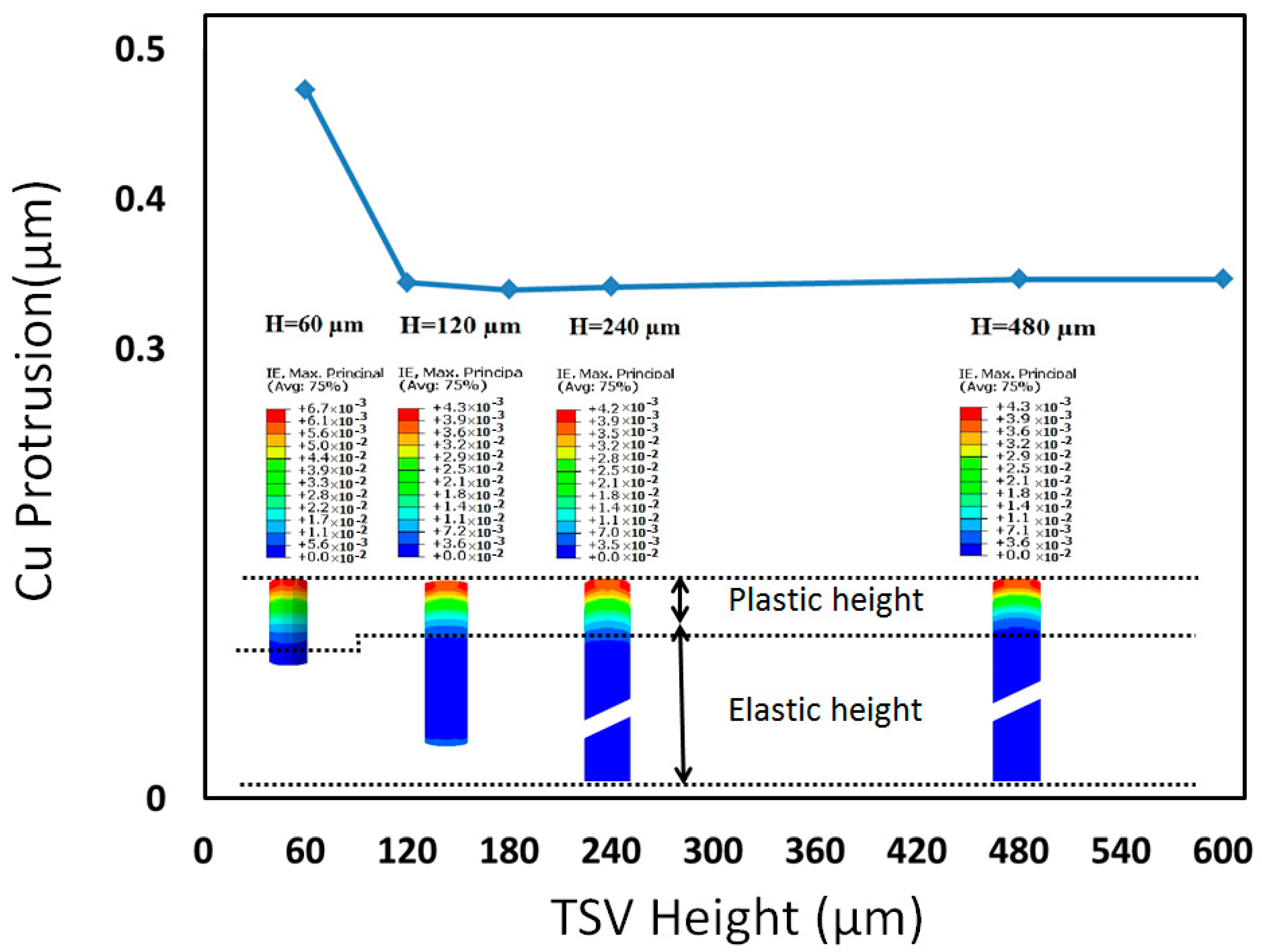

3.4. Effect of TSV Height on the Protrusion

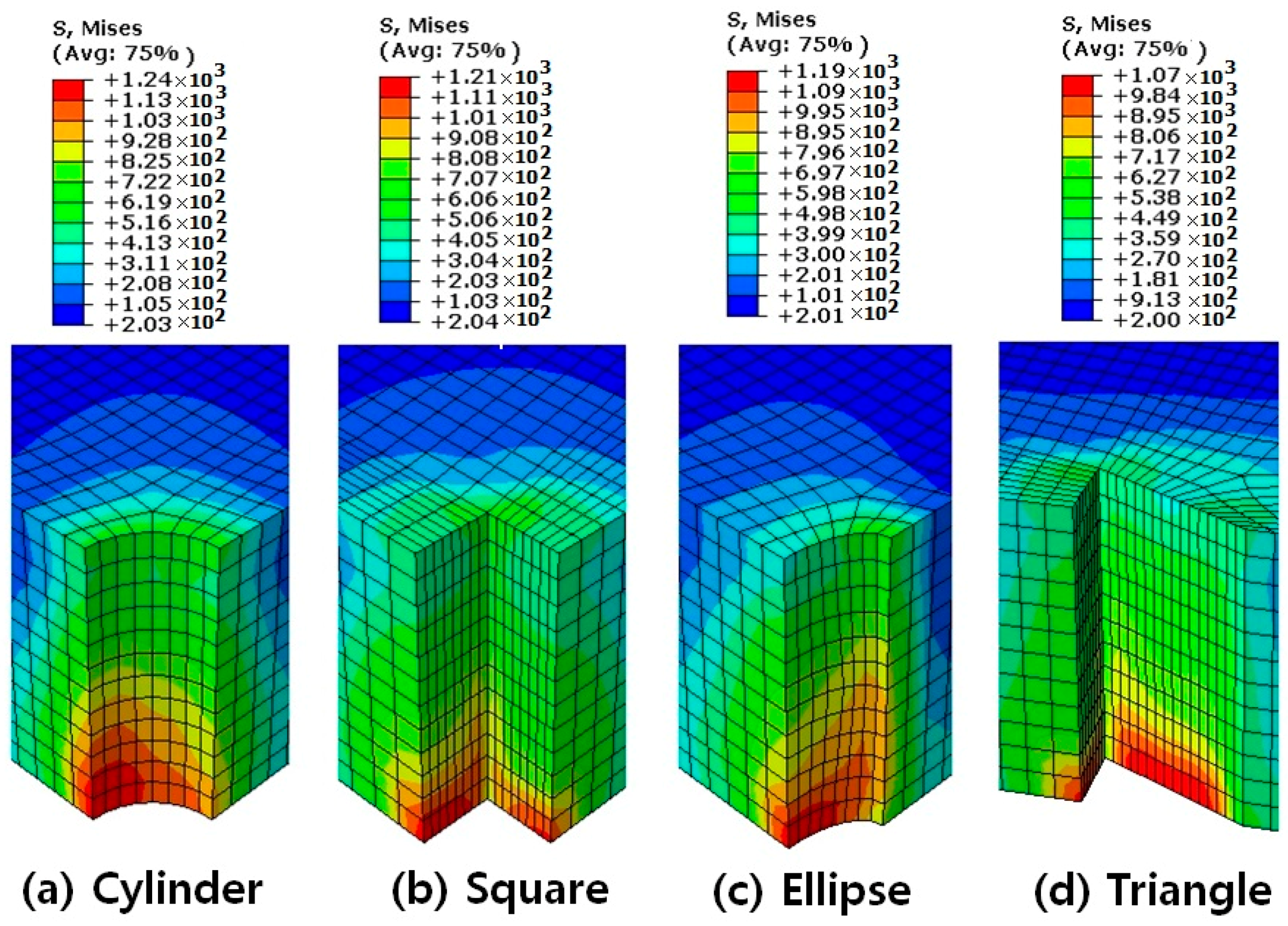

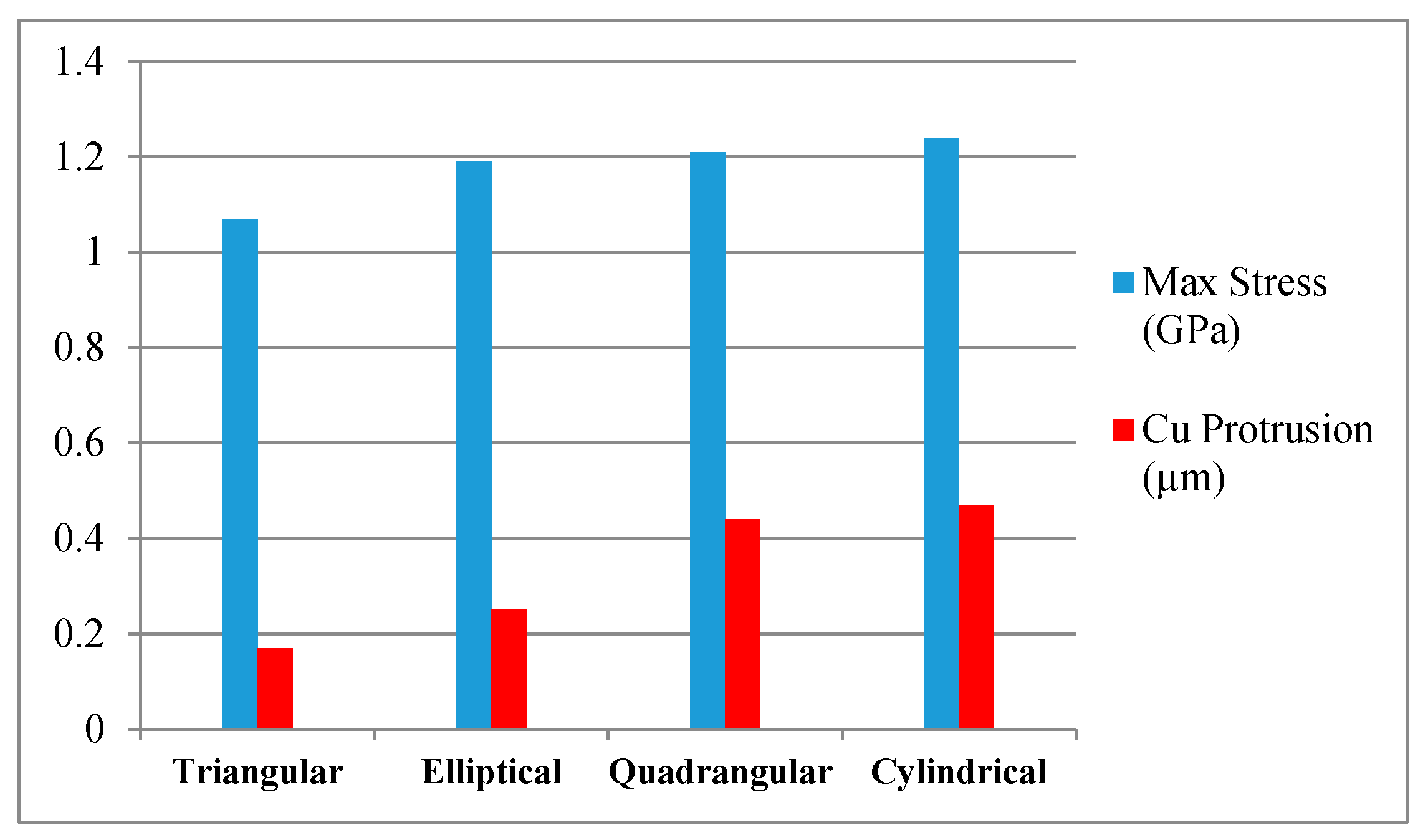

3.5. The Protrusion and Stress Analysis for Different TSV Shapes

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kong, L.W. Visualization of extrusion and voids induced in TSV. Microelectron. Reliab. 2012, 92, 24–28. [Google Scholar] [CrossRef]

- Ding, Y.; Yan, Y.; Chen, Q.; Wang, S.; Su, R.; Dang, H. Analytical solution on interfacial reliability of 3-D through-silicon-via (TSV) containing dielectric liner. Microelectron. Reliab. 2014, 54, 1384–1391. [Google Scholar] [CrossRef]

- Choi, H.S.; Seo, W.S.; Choi, D.K. Prediction of reliability on thermoelectric module through accelerated life test and Physics-of-failure. Electron. Mater. Lett. 2011, 7, 271. [Google Scholar] [CrossRef]

- Kang, U.S.; Chung, H.J.; Heo, S.M.; Park, D.H.; Lee, H.; Kim, J.H.; Ahn, A.H.; Cha, S.H.; Ahn, J.; Kwon, D.M.; et al. 8 Gb 3-D DDR3 DRAM using through-silicon-via technology. IEEE J. Solid-state Circuit Conf. 2010, 45, 111–119. [Google Scholar] [CrossRef]

- Kumar, S.; Park, J.Y.; Jung, J.P. Analysis of high speed shear characteristics of Sn-Ag-Cu solder joints. Electron. Mater. Lett. 2011, 7, 365. [Google Scholar] [CrossRef]

- Roh, M.H.; Sharma, A.; Lee, J.H.; Jung, J.P. Extrusion Suppression of TSV Filling Metal by Cu-W Electroplating for Three-Dimensional Microelectronic Packaging. Metall. Mater. Trans. A 2015, 46, 2051–2062. [Google Scholar] [CrossRef]

- Lau, J.H. Overview and Outlook of Three-Dimensional Integrated Circuit Packaging, Three-Dimensional Si Integration, and Three-Dimensional Integrated Circuit Integration. ASME J. Electron. Packag. 2014, 136, 040801. [Google Scholar] [CrossRef]

- De Messemaeker, O.; Pedreira, V.; Vandevelde, B.; Philipsen, H.; De Wolf, I.; Beyne, E.; Croes, K. Impact of post-plating anneal and throughsilicon via dimensions on Cu pumping. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2013; pp. 586–591. [Google Scholar]

- Jeong, I.H.; Jung, D.H.; Shin, K.S.; Shin, D.S.; Jung, J.P. Electrical characteristics and thermal shock properties of Cu-filled TSV prepared by laser drilling. Electron. Mater. Lett. 2013, 9, 389–392. [Google Scholar] [CrossRef]

- Seo, S.W.; Park, J.H.; Seo, M.S.; Kim, G.S. The electrical, mechanical properties of through-silicon-via insulation layer for 3D ICs. In Proceeding of the Electronics Packaging Technology & High Density Packaging International Conference, Beijing, China, 10–13 August 2009; p. 64. [Google Scholar]

- Lu, J.Q.; Xu, Z. Through-silicon-via fabrication technologies, passives extraction, and electrical modeling for 3-D integration/packaging. Semicond. Manuf. IEEE 2013, 26, 23. [Google Scholar]

- Hayt, W.H. Engineering Electromagnetics, 5th ed.; McGraw-Hill: New York, NY, USA, 1989; ISBN 0070274061. [Google Scholar]

- Vander Vorst, A.; Rosen, A.; Kotsuka, Y. RF/Microwave Interaction with Biological Tissues; John Wiley and Sons, Inc.: Hoboken, NJ, USA, 2006; ISBN 978-0-471-73277-8. [Google Scholar]

- Jordan, E.C. Electromagnetic Waves and Radiating Systems; Prentice Hall: Upper Saddle River, NJ, USA, 1968; p. 130. ISBN 978-0-13-249995-8. [Google Scholar]

- Jing, X.; Lee, U.-H.; Xu, C.; Niu, Z.; Hao, H.; Bae, J.-Y.; Won, J.; Zhang, W. Effect of pre-CMP annealing on TSV pumping in thermal budget and reliability test. In Proceedings of the 2015 IEEE 22nd International Symposium on the Physical and Failure Analysis of Integrated Circuits, Hsinchu, Taiwan, 29 June–2 July 2015. [Google Scholar]

| Mat. | Poisson’s Ratio | CTE (ppm/k) | Young Modulus (GPa) | Plastic Curve, Stress (MPa) vs. Strain |

|---|---|---|---|---|

| Cu | 0.34 | 17.3 | 121 | 121@0.001 186@0.004 217@0.01 234@0.02 248@0.04 |

| Si | νyz = 0.36 νzx = 0.28 νxy = 0.064 | 2.8 | Ex = Ey = 169 Ez = 130 Gyz = Gzx = 79.6 Gxy = 50.9 | Fully elastic |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, I.H.; Eslami Majd, A.; Jung, J.P.; Ekere, N.N. Electrical and Mechanical Analysis of Different TSV Geometries. Metals 2020, 10, 467. https://doi.org/10.3390/met10040467

Jeong IH, Eslami Majd A, Jung JP, Ekere NN. Electrical and Mechanical Analysis of Different TSV Geometries. Metals. 2020; 10(4):467. https://doi.org/10.3390/met10040467

Chicago/Turabian StyleJeong, Il Ho, Alireza Eslami Majd, Jae Pil Jung, and Nduka Nnamdi Ekere. 2020. "Electrical and Mechanical Analysis of Different TSV Geometries" Metals 10, no. 4: 467. https://doi.org/10.3390/met10040467

APA StyleJeong, I. H., Eslami Majd, A., Jung, J. P., & Ekere, N. N. (2020). Electrical and Mechanical Analysis of Different TSV Geometries. Metals, 10(4), 467. https://doi.org/10.3390/met10040467