A Voltage Parameter Adaptive Detection Method for Power Systems Under Grid Voltage Distortion Conditions

Abstract

1. Introduction

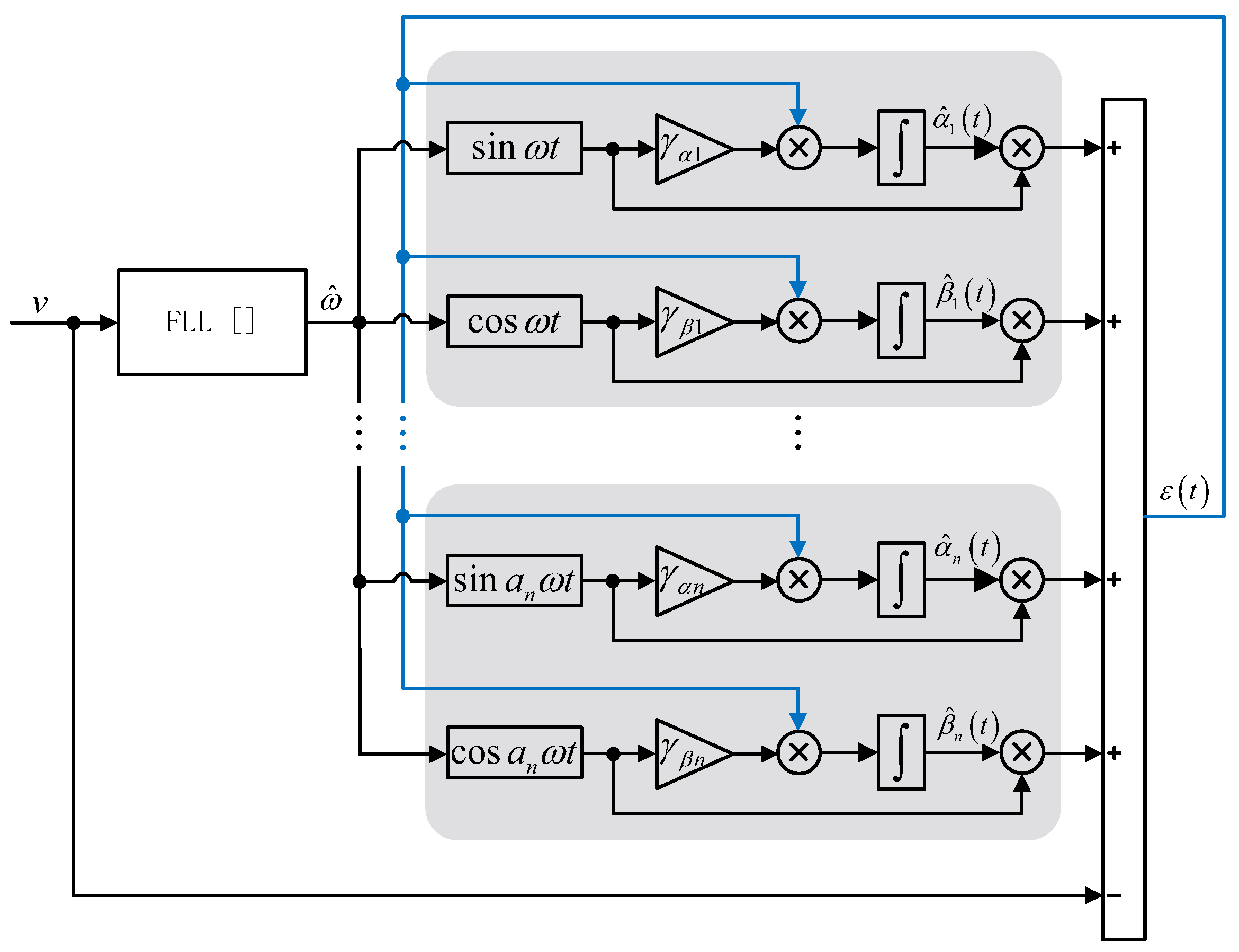

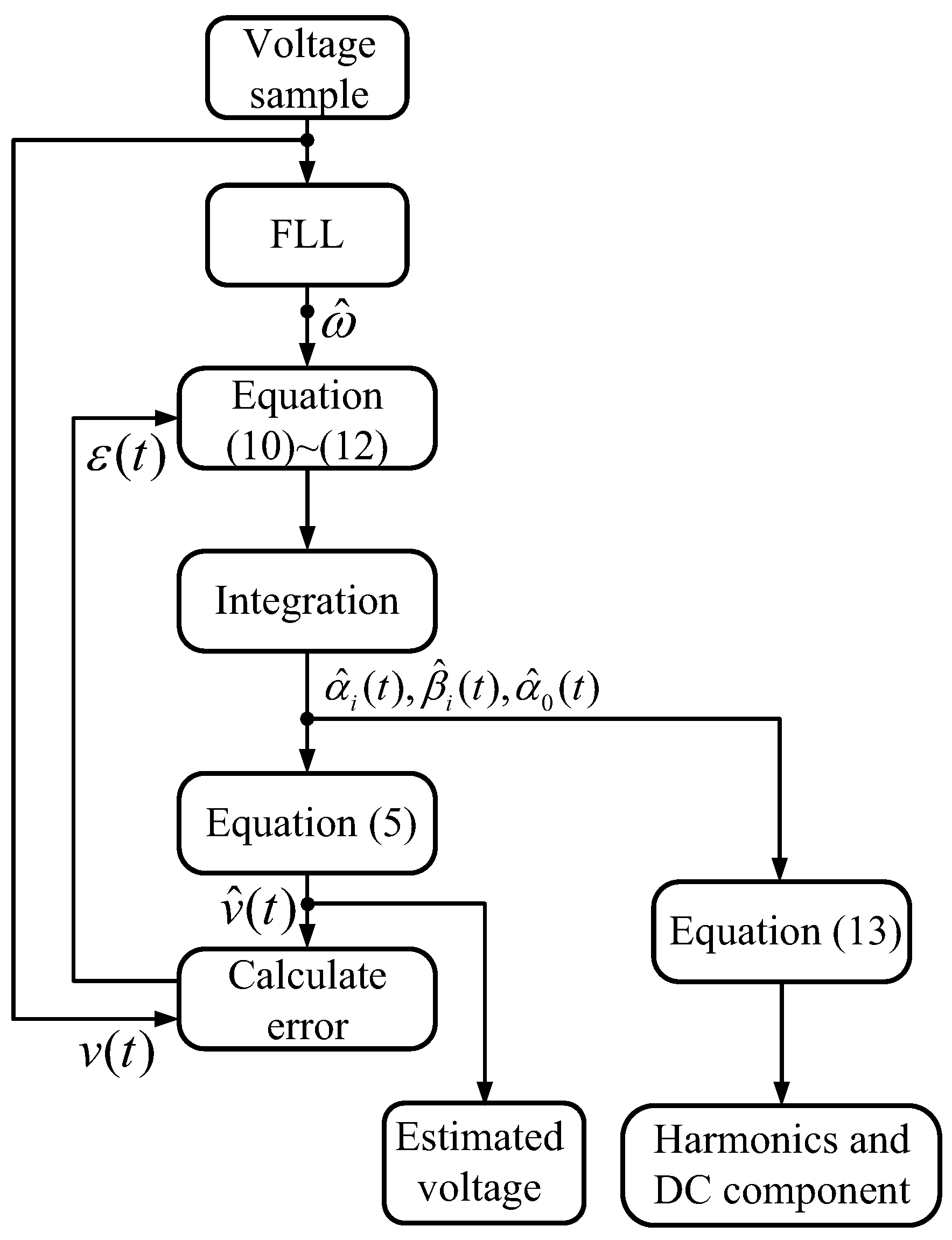

2. Voltage Parameter Detection Under Harmonically Distorted Conditions

3. Frequency-Locked Loop

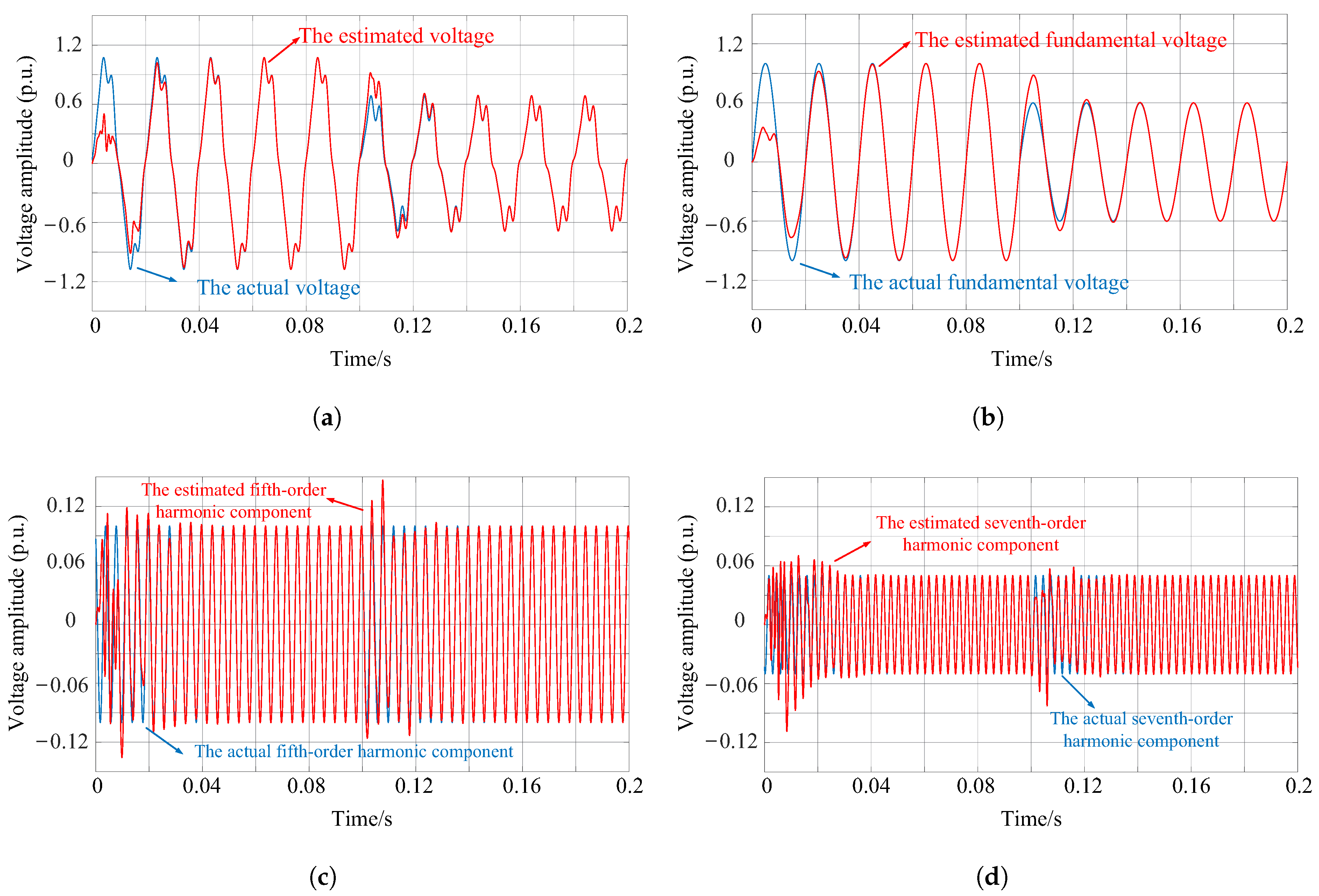

4. Simulation Results

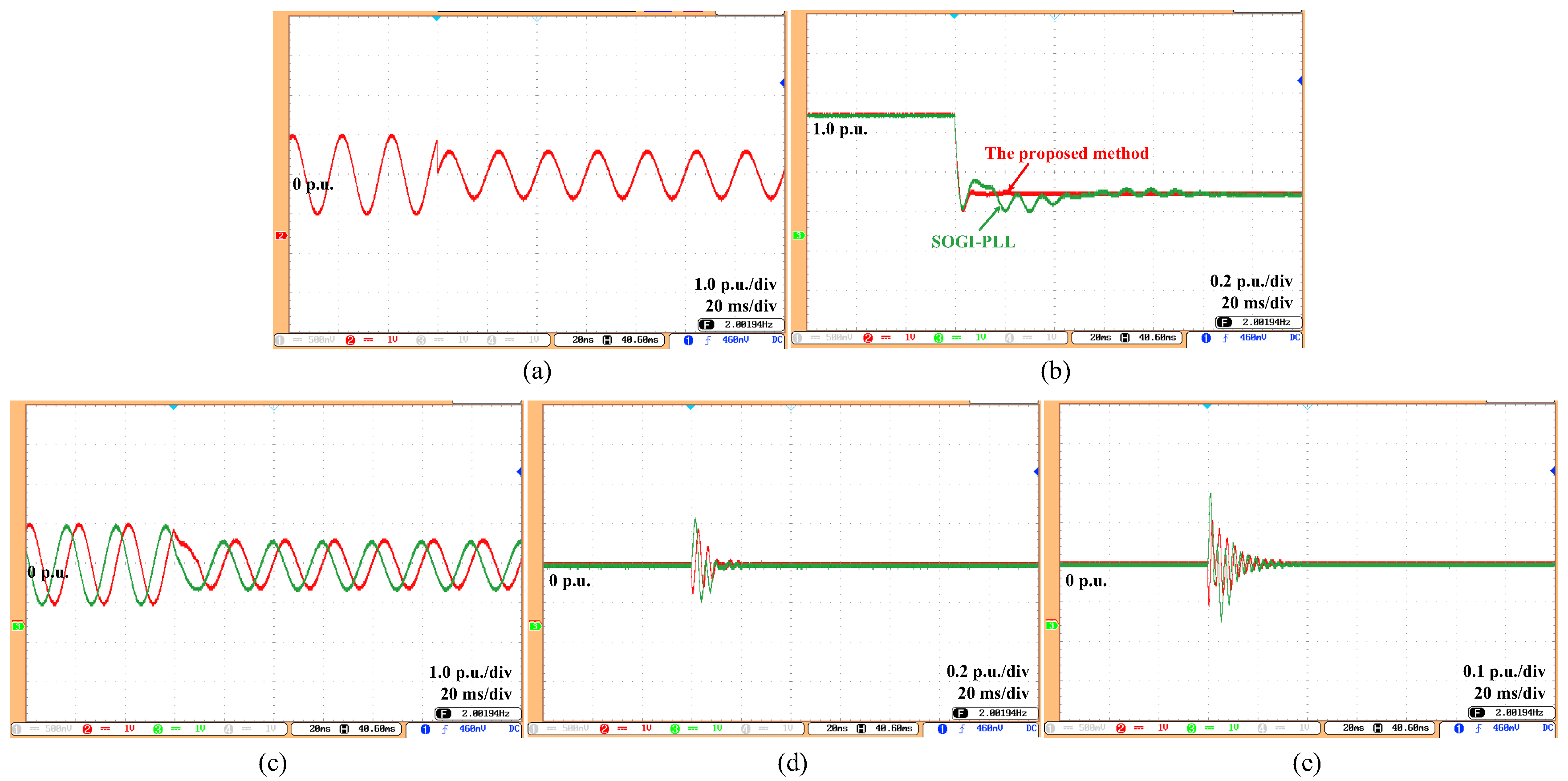

5. Experimental Results

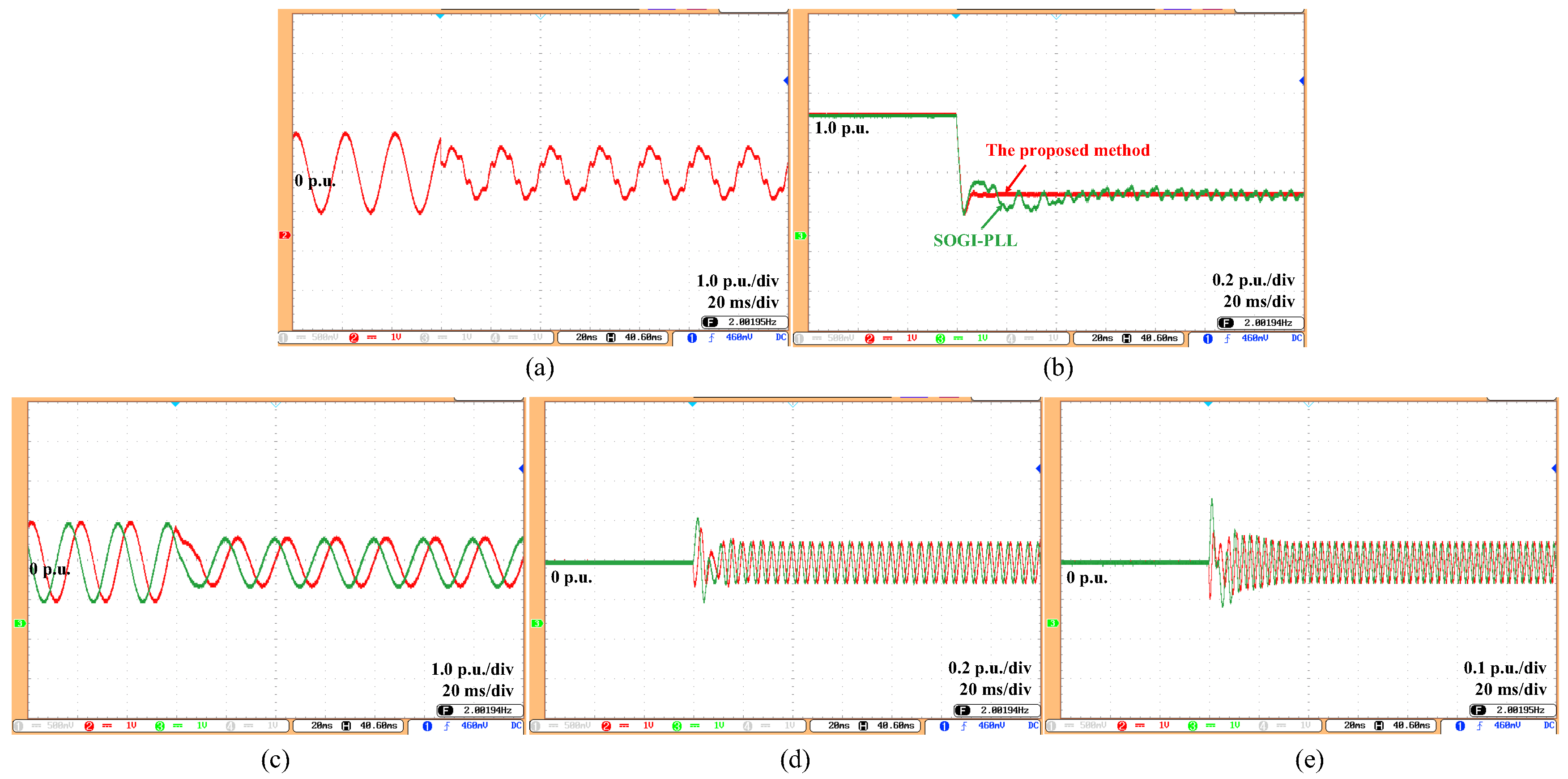

5.1. Case Without FLL

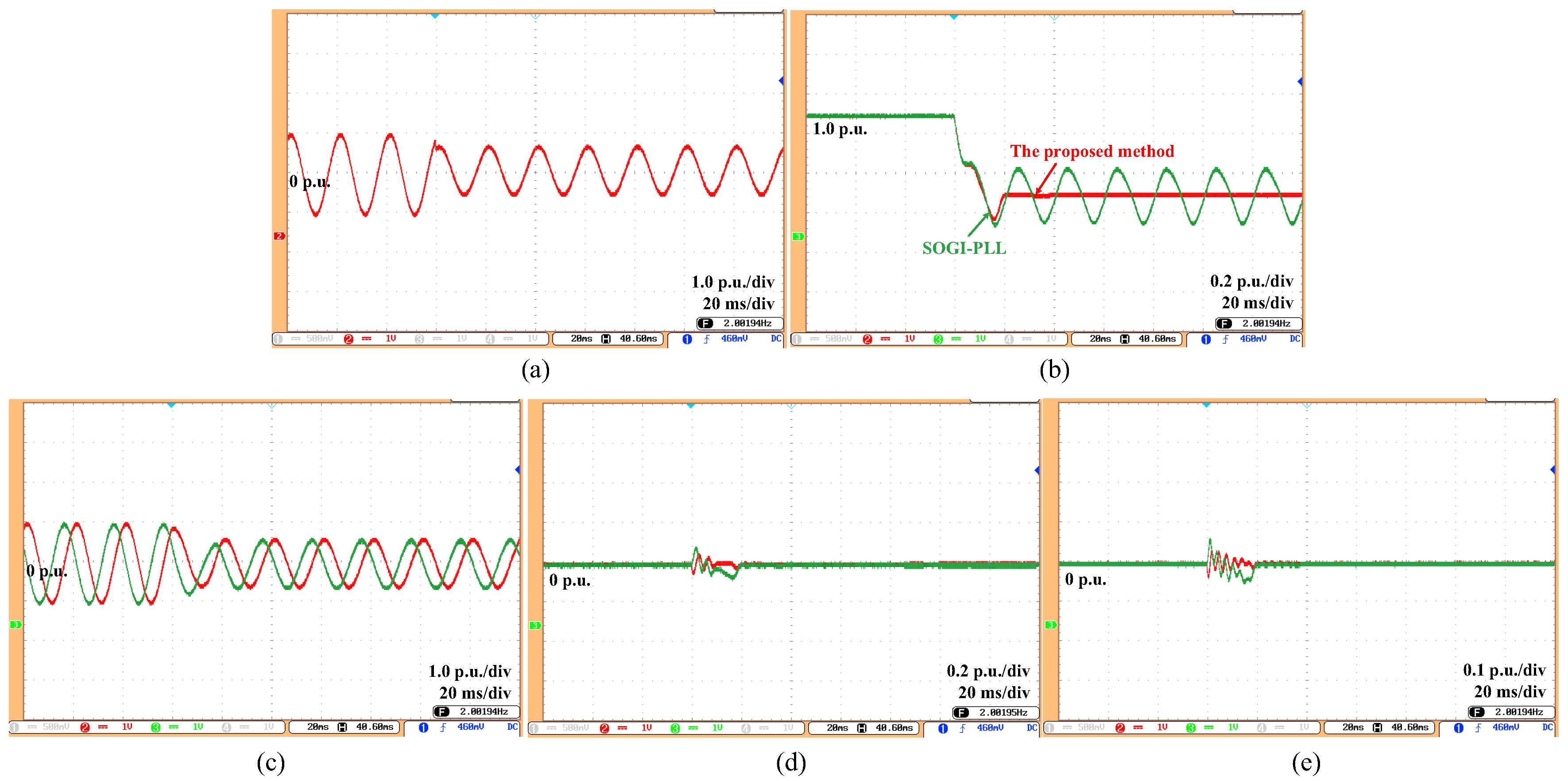

5.2. Case with FFL

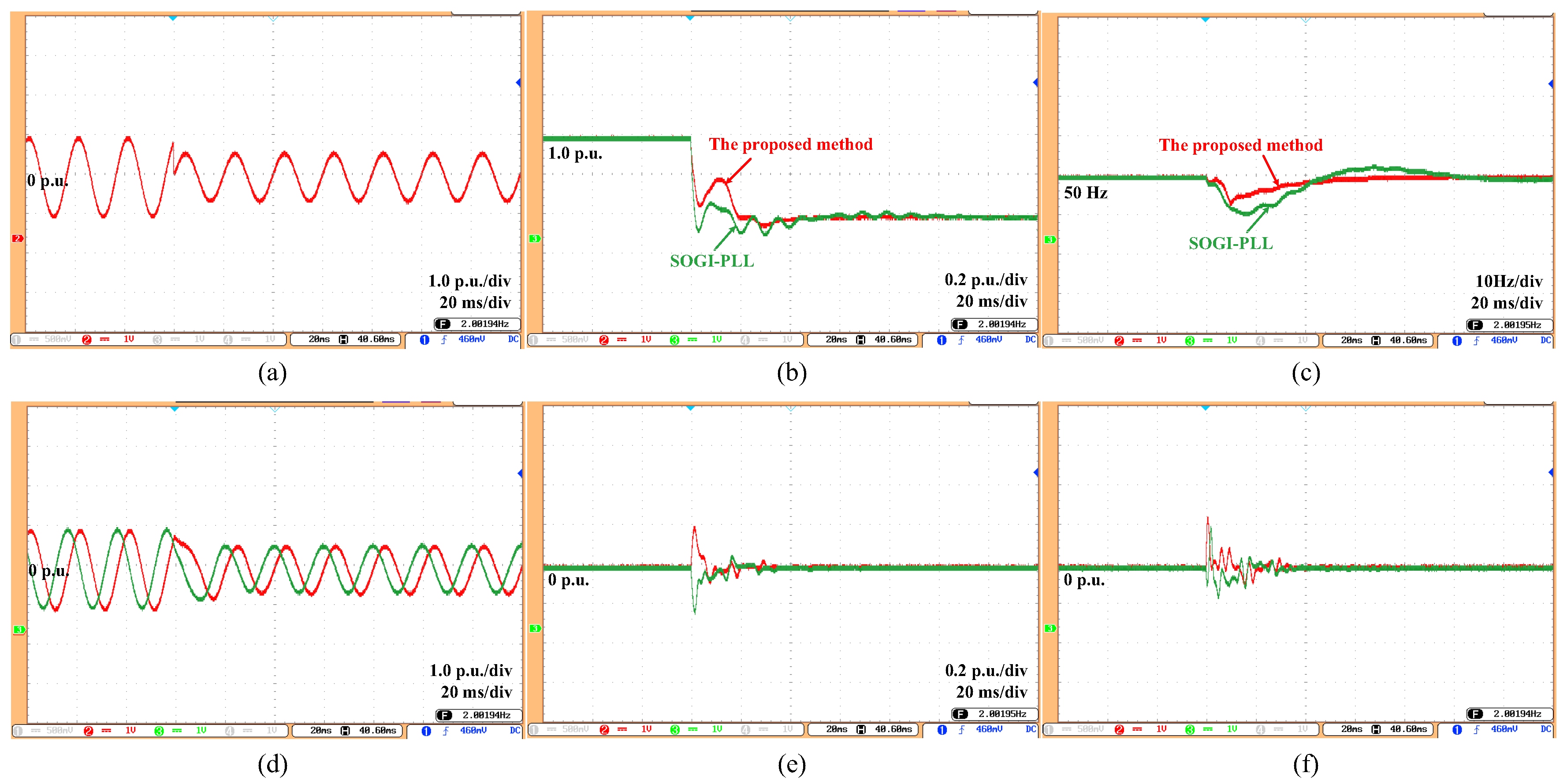

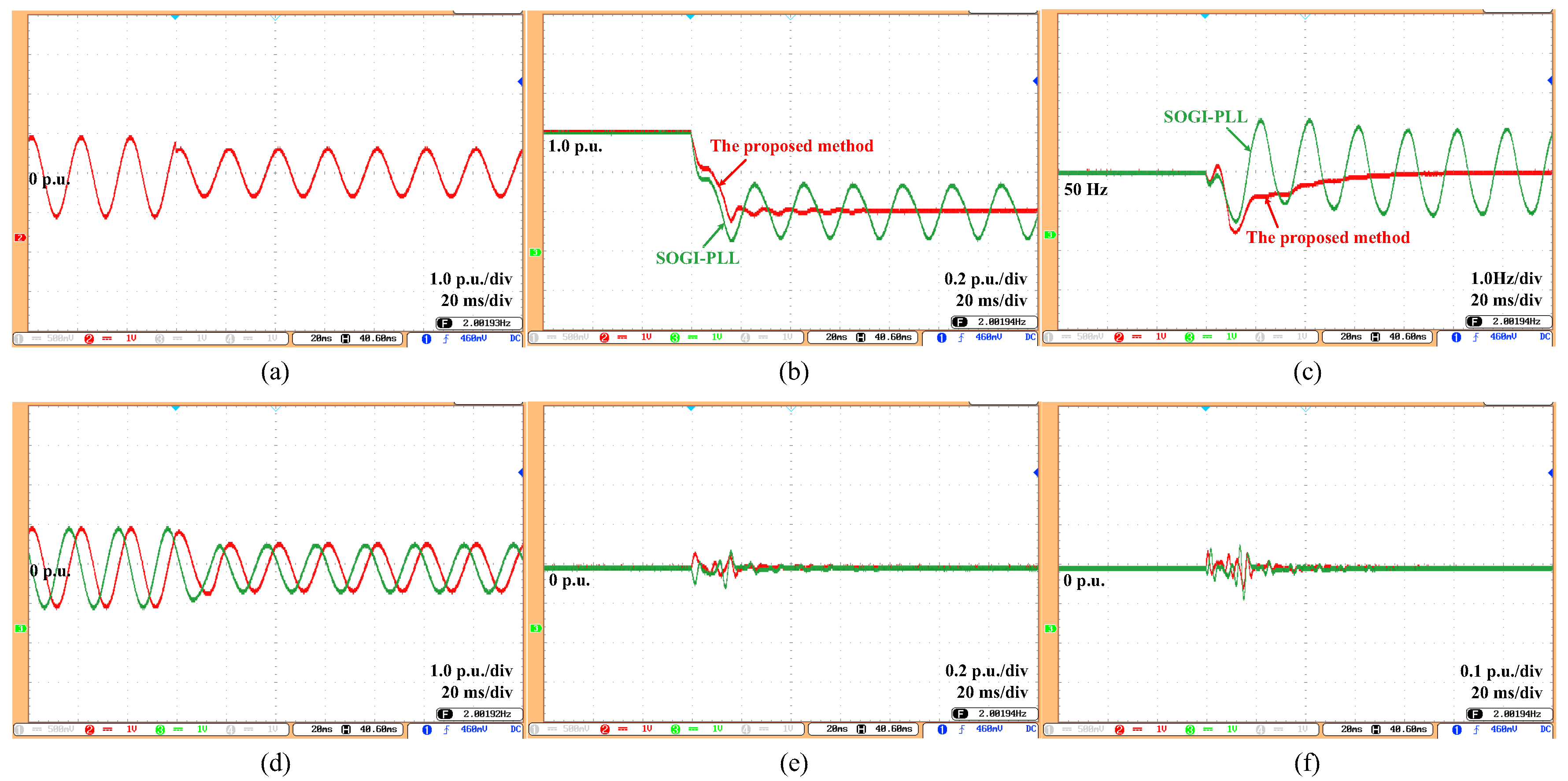

5.3. Comparison with Traditional Methods

6. Conclusions

- The novel method has great advantages in detection speed;

- The novel method achieves accurate tracking of the voltage parameters with zero steady-state error under voltage distortion conditions;

- The novel method is able to extract the harmonics and the DC component without steady-state error.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| FLL | frequency-locked loop; |

| PLL | phase-locked loop; |

| pPLLs | power-based PLLs; |

| LPF-PLL | low-pass filter-based pPLL; |

| DFAC-pPLL | double-frequency and amplitude compensation-based pPLL; |

| QSG-PLLs | quadrature signal generation-based PLLs; |

| SOGI-PLL | second-order generalized integrator-based phase-locked loop; |

| MAF-PLLs | moving average filter-based pPLLs; |

| TD-PLL | transfer delay-PLL; |

| VTD-PLL | variable-length delay-PLL; |

| ATD-PLL | adaptive transfer delay-PLL; |

| NTD-PLL | non-frequency-dependent TD-PLL; |

| QSG-FLLs | quadrature signal generation-based FLLs; |

| SOGI-FLL | second-order generalized integrator-based FLL; |

| TD-AFLL | transfer delay-based adaptive frequency locked loop; |

| DDSRF-PLL | Decoupled double synchronous reference frame PLL; |

| LSRF-PLL | low-pass filter-based synchronous reference frame PLL; |

| VSPF-PLL | variable sampling period filter phase-locked loop |

| DSOGI-PLL | dual second-order generalized integrator-based phase-locked loop; |

| MRF-PLL | multiple-reference-frame phase-locked loop; |

| LVRT | low-voltage ride through. |

References

- Khan, I.; Doolla, S. Improved fault ride-through response of grid forming inverters under symmetrical and asymmetrical faults. IEEE Trans. Energy Convers. 2025, 40, 394–408. [Google Scholar] [CrossRef]

- Feng, Y.; Huang, W.; Jin, Z.; Li, Y.; Shen, Z.J.; Shuai, Z. Voltage Support Strategy for Improving Power Transfer Capability of Grid-Connected Converter Under Unbalanced Conditions. IEEE Trans. Power Electron. 2024, 39, 7863–7875. [Google Scholar] [CrossRef]

- Xiao, F.; Dong, L.; Li, L.; Liao, X. Fast voltage detection method for grid-tied renewable energy generation systems under distorted grid voltage conditions. IET Power Electron. 2017, 10, 1487–1493. [Google Scholar] [CrossRef]

- Ma, C.; Gao, F.; He, G.; Li, G. Fast voltage detection method for the voltage ride through operation of grid-tied renewable energy generation systems. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 386–391. [Google Scholar]

- Ismail, F.; Jamaludin, J.; Abd Rahim, N. Enhanced Energy Delivery for Solar PV Distributed Generators at Voltage Sags. IEEE Access 2023, 11, 139688–139705. [Google Scholar] [CrossRef]

- Styvaktakis, E.; Bollen, M.H.; Gu, I.Y. Automatic classification of power system events using RMS voltage measurements. In Proceedings of the IEEE Power Engineering Society Summer Meeting, Chicago, IL, USA, 21–25 July 2002; Volume 2, pp. 824–829. [Google Scholar]

- Naidoo, R.; Pillay, P. A new method of voltage sag and swell detection. IEEE Trans. Power Deliv. 2007, 22, 1056–1063. [Google Scholar] [CrossRef]

- Zou, W.; Su, S. Voltage flicker detection based on wavelet fourier transform. In Proceedings of the 2011 International Conference on Electrical and Control Engineering, Yichang, China, 16–18 September 2011; pp. 4218–4220. [Google Scholar]

- Golestan, S.; Ramezani, M.; Guerrero, J.M.; Freijedo, F.D.; Monfared, M. Moving average filter based phase-locked loops: Performance analysis and design guidelines. IEEE Trans. Power Electron. 2014, 29, 2750–2763. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Design and tuning of a modified power-based PLL for single-phase grid-connected power conditioning systems. IEEE Trans. Power Electron. 2012, 27, 3639–3650. [Google Scholar] [CrossRef]

- Avudaiappan, S.K.; Joshi, S.T.; Ganesan, S.I.; Chilakapati, N. A high-speed frequency adaptive grid synchronization technique for single-phase inverter under distorted grid conditions. Sādhanā 2022, 47, 69. [Google Scholar] [CrossRef]

- Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. A new single-phase PLL structure based on second order generalized integrator. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Republic of Korea, 18–22 June 2006; pp. 1–6. [Google Scholar]

- Lubura, S.; Šoja, M.; Lale, S.; Ikić, M. Single-phase phase locked loop with DC offset and noise rejection for photovoltaic inverters. IET Power Electron. 2014, 7, 2288–2299. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A.; Mojiri, M. Addressing DC component in PLL and notch filter algorithms. IEEE Trans. Power Electron. 2011, 27, 78–86. [Google Scholar] [CrossRef]

- Akhtar, M.A.; Choudhury, S.; Saha, S. LQR based PI controller tuning for transport delay-phase locked loop (TD-PLL). In Proceedings of the 2018 3rd International Innovative Applications of Computational Intelligence on Power, Energy and Controls with their Impact on Humanity (CIPECH), Ghaziabad, India, 1–2 November 2018; pp. 34–38. [Google Scholar]

- Akhtar, M.A.; Saha, S. A Systematic Approach of Loop Filter Tuning of TD-Based PLLs Using LQR-Based Approach Considering Time Delay. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 2424–2434. [Google Scholar] [CrossRef]

- Akhtar, M.A.; Saha, S.; Pal, D.; Verma, A.K.; Tir, Z. A Systematic Approach to Design Amplitude Estimators for NTD-PLL: Performance Improvement Under Abnormal Grid Disturbances. IEEE Trans. Power Electron. 2023, 38, 5456–5468. [Google Scholar] [CrossRef]

- Pompodakis, E.E.; Boubaris, A.; Voglitsis, D.; Papanikolaou, N.; Yiannis, K.; Karapidakis, E.S. Variable-Length Transfer Delay-Based Synchronization Approach for Improved Dynamic Performance in Single-Phase Inverters. IEEE Access 2024, 12, 151331–151347. [Google Scholar] [CrossRef]

- Golestan, S.; Guerrero, J.M.; Abusorrah, A.; Al-Hindawi, M.M.; Al-Turki, Y. An adaptive quadrature signal generation-based single-phase phase-locked loop for grid-connected applications. IEEE Trans. Ind. Electron. 2016, 64, 2848–2854. [Google Scholar] [CrossRef]

- Pin, G.; Chen, B.; Fedele, G.; Parisini, T. Robust Frequency-Adaptive PLL with Lyapunov Stability Guarantees. In Proceedings of the 2020 IEEE Conference on Control Technology and Applications (CCTA), Montreal, QC, Canada, 24–26 August 2020; pp. 498–503. [Google Scholar]

- Pin, G.; Chen, B.; Fedele, G.; Parisini, T. Robust Frequency-Adaptive Quadrature Phase-Locked-Loops with Lyapunov-Certified Global Stability. IEEE Trans. Control Syst. Technol. 2023, 31, 467–474. [Google Scholar] [CrossRef]

- Prakash, S.V.; Behera, S.; N, V.R.N.; Karthik, M. SOGI-PLL Based Control Technique for the Single-Phase Single-Stage Grid Connected PV System. In Proceedings of the 2023 First International Conference on Cyber Physical Systems, Power Electronics and Electric Vehicles (ICPEEV), Hyderabad, India, 28–30 September 2023; pp. 1–5. [Google Scholar]

- Dai, Z.; Zhang, Z.; Yang, Y.; Blaabjerg, F.; Huangfu, Y.; Zhang, J. A fixed-length transfer delay based adaptive frequency-locked loop for single-phase systems. IEEE Trans. Power Electron. 2018, 34, 4000–4004. [Google Scholar] [CrossRef]

- Dai, Z.; Lin, W. Adaptive estimation of three-phase grid voltage parameters under unbalanced faults and harmonic disturbances. IEEE Trans. Power Electron. 2016, 32, 5613–5627. [Google Scholar] [CrossRef]

- Surbhi; Teja, A.V.R.; J, K. A Novel Variable Time Delay FLL Based Estimation of Positive and Negative Sequence Components of Grid. In Proceedings of the IECON 2023—49th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 16–19 October 2023; pp. 1–6. [Google Scholar]

- Tao, G. Adaptive Control Design and Analysis; John Wiley & Sons: Hoboken, NJ, USA, 2003; pp. 99–111. [Google Scholar]

- Goodwin, G.C.; Welsh, J.S. Self excited closed loop parametric estimation in the presence of noise undermodelling. In Proceedings of the 2002 American Control Conference (IEEE Cat. No. CH37301), Anchorage, AK, USA, 8–10 May 2002; Volume 4, pp. 3331–3336. [Google Scholar]

- Rodríguez, P.; Luna, A.; Candela, I.; Mujal, R.; Teodorescu, R.; Blaabjerg, F. Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions. IEEE Trans. Ind. Electron. 2010, 58, 127–138. [Google Scholar] [CrossRef]

- Wang, L.; Jiang, Q.; Hong, L.; Zhang, C.; Wei, Y. A novel phase-locked loop based on frequency detector and initial phase angle detector. IEEE Trans. Power Electron. 2012, 28, 4538–4549. [Google Scholar] [CrossRef]

- Carugati, I.; Maestri, S.; Donato, P.G.; Carrica, D.; Benedetti, M. Variable sampling period filter PLL for distorted three-phase systems. IEEE Trans. Power Electron. 2011, 27, 321–330. [Google Scholar] [CrossRef]

- Rodríguez, P.; Pou, J.; Bergas, J.; Candela, J.I.; Burgos, R.P.; Boroyevich, D. Decoupled double synchronous reference frame PLL for power converters control. IEEE Trans. Power Electron. 2007, 22, 584–592. [Google Scholar] [CrossRef]

- Pinto, J.; Carvalho, A.; Rocha, A.; Araújo, A. Comparison of DSOGI-based PLL for phase estimation in three-phase weak grids. Electricity 2021, 2, 244–270. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D. Design-oriented study of advanced synchronous reference frame phase-locked loops. IEEE Trans. Power Electron. 2012, 28, 765–778. [Google Scholar] [CrossRef]

| Method | Characteristic | Method | Characteristic |

|---|---|---|---|

| RMS-based method | A minimum delay of one cycle | Peak Voltage Detection Method | A minimum delay of a half-cycle |

| DFT-based method | A minimum delay of one cycle | LPF-PLL | Slow dynamic response |

| MAF-PLL | Slow dynamic response | DFAC-pPLL | A satisfactory dynamic response |

| TOGI-PLL | DC offset rejection capability | MSOGI-PLL | Better harmonic immunity |

| TD-PLL | Affected by frequency deviations | NTD-PLL | Steady-state error exists |

| VTD-PLL | Complex stability analysis | ATD-PLL | Good steady-state performance |

| GQPLL | Frequency adaptation | TD-AFLL | Obvious steady-state error under harmonic disturbances |

| Proposed method | Without steady-state error under voltage distortion conditions | ||

| Experiment Conditions | SOGI-PLL | Proposed Method (No FLL) |

|---|---|---|

| test (1) | settle time: last for 80 ms | settle time: 5.3 ms |

| test (2) | minor fluctuation | large fluctuation |

| test (3) | 3.2% steady-state error | zero steady-state error |

| test (4) | 25% steady-state error | zero steady-state error |

| Experiment Conditions | SOGI-PLL | Proposed Method (with FLL) |

|---|---|---|

| test (1) | settle time: last for 80 ms | settle time: about 40 ms |

| test (2) | settle time: about 56 ms | settle time: about 25 ms |

| test (3) | 3.2% steady-state error | zero steady-state error |

| test (4) | 25% steady-state error | zero steady-state error |

| Detection Method | Maximum Detection Time Without Grid Voltage Distortion (ms) | Detection Time with Low-Order Harmonic Distortion (ms) |

|---|---|---|

| DDSRF-PLL | 25 | longer than 25 |

| VSPF-PLL | 25 | 25 |

| MAF-PLL | 20 | longer than 20 |

| LSRF-PLL | 60 | longer than 60 |

| MRF-PLL | 40 | longer than 40 |

| DSOGI-PLL | 30 | longer than 30 |

| Proposed method | 4.16 | 10.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hao, W.; Dai, Z.; Li, G.; Lv, S.; Sun, Q.; Lu, N.; Ma, J. A Voltage Parameter Adaptive Detection Method for Power Systems Under Grid Voltage Distortion Conditions. Symmetry 2025, 17, 975. https://doi.org/10.3390/sym17060975

Hao W, Dai Z, Li G, Lv S, Sun Q, Lu N, Ma J. A Voltage Parameter Adaptive Detection Method for Power Systems Under Grid Voltage Distortion Conditions. Symmetry. 2025; 17(6):975. https://doi.org/10.3390/sym17060975

Chicago/Turabian StyleHao, Wenzhe, Zhiyong Dai, Guangqi Li, Shuaishuai Lv, Qitao Sun, Nana Lu, and Jinke Ma. 2025. "A Voltage Parameter Adaptive Detection Method for Power Systems Under Grid Voltage Distortion Conditions" Symmetry 17, no. 6: 975. https://doi.org/10.3390/sym17060975

APA StyleHao, W., Dai, Z., Li, G., Lv, S., Sun, Q., Lu, N., & Ma, J. (2025). A Voltage Parameter Adaptive Detection Method for Power Systems Under Grid Voltage Distortion Conditions. Symmetry, 17(6), 975. https://doi.org/10.3390/sym17060975