The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters

Abstract

1. Introduction

2. Materials and Methods

3. Results

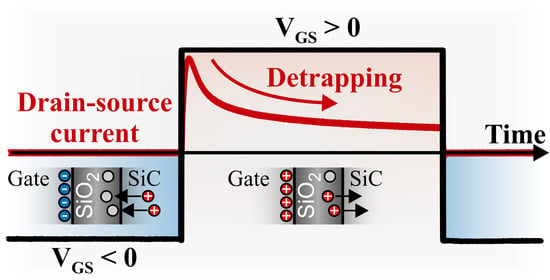

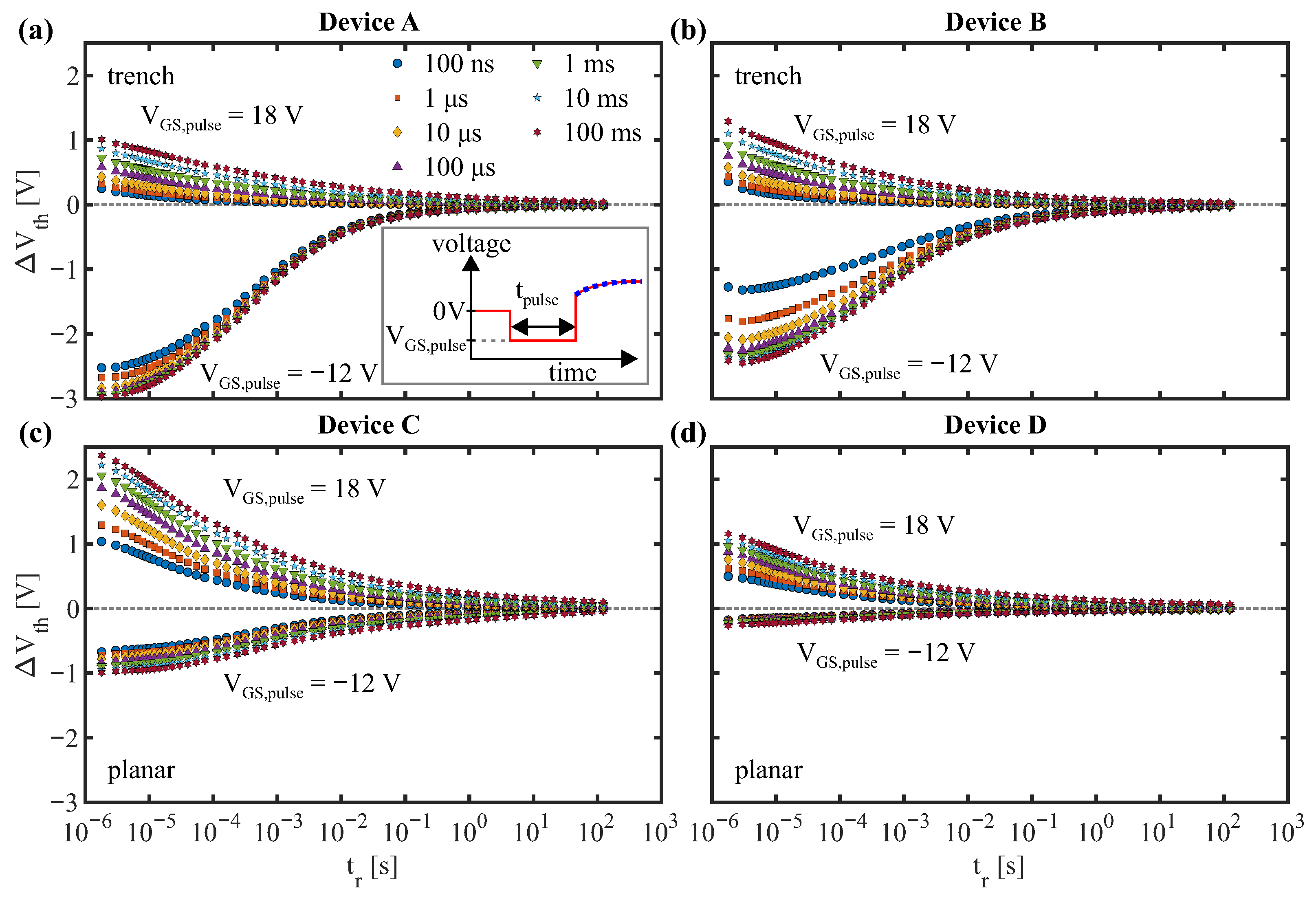

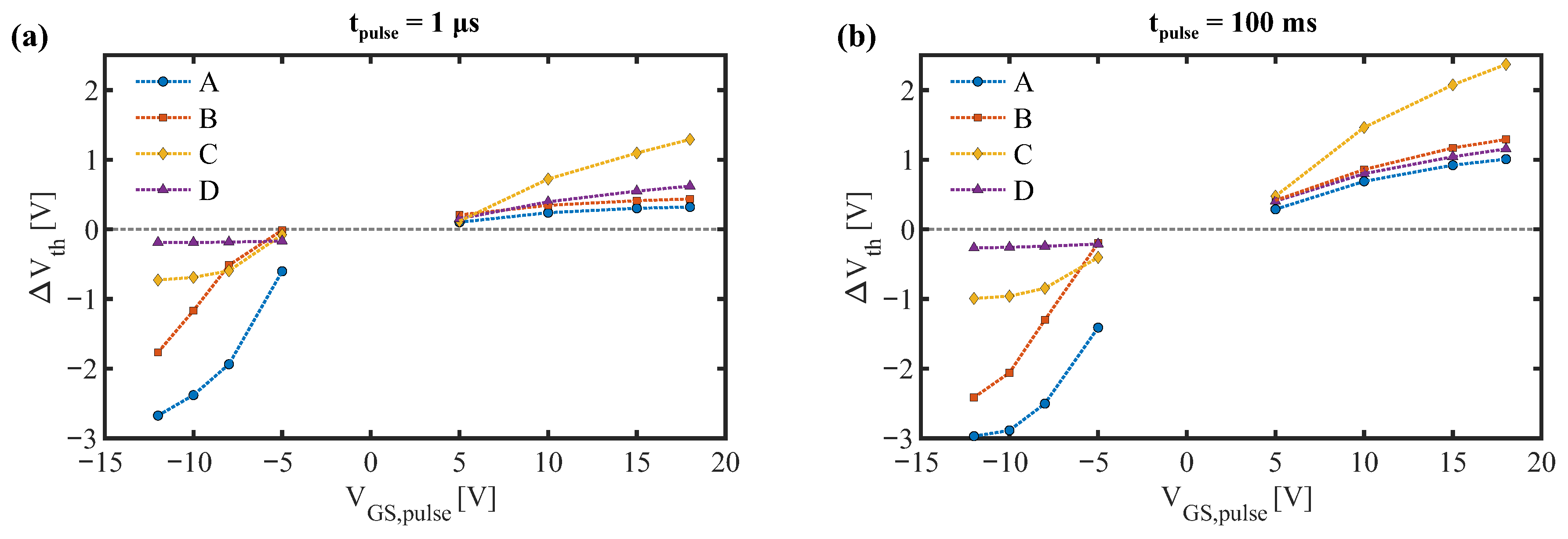

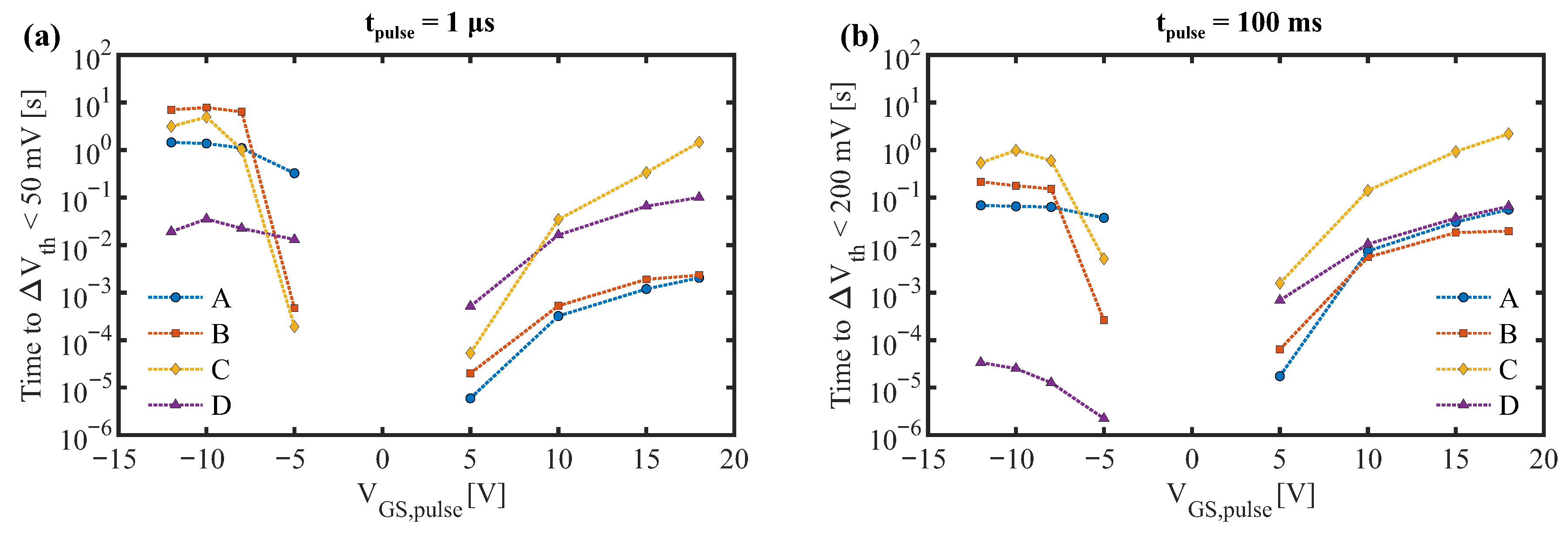

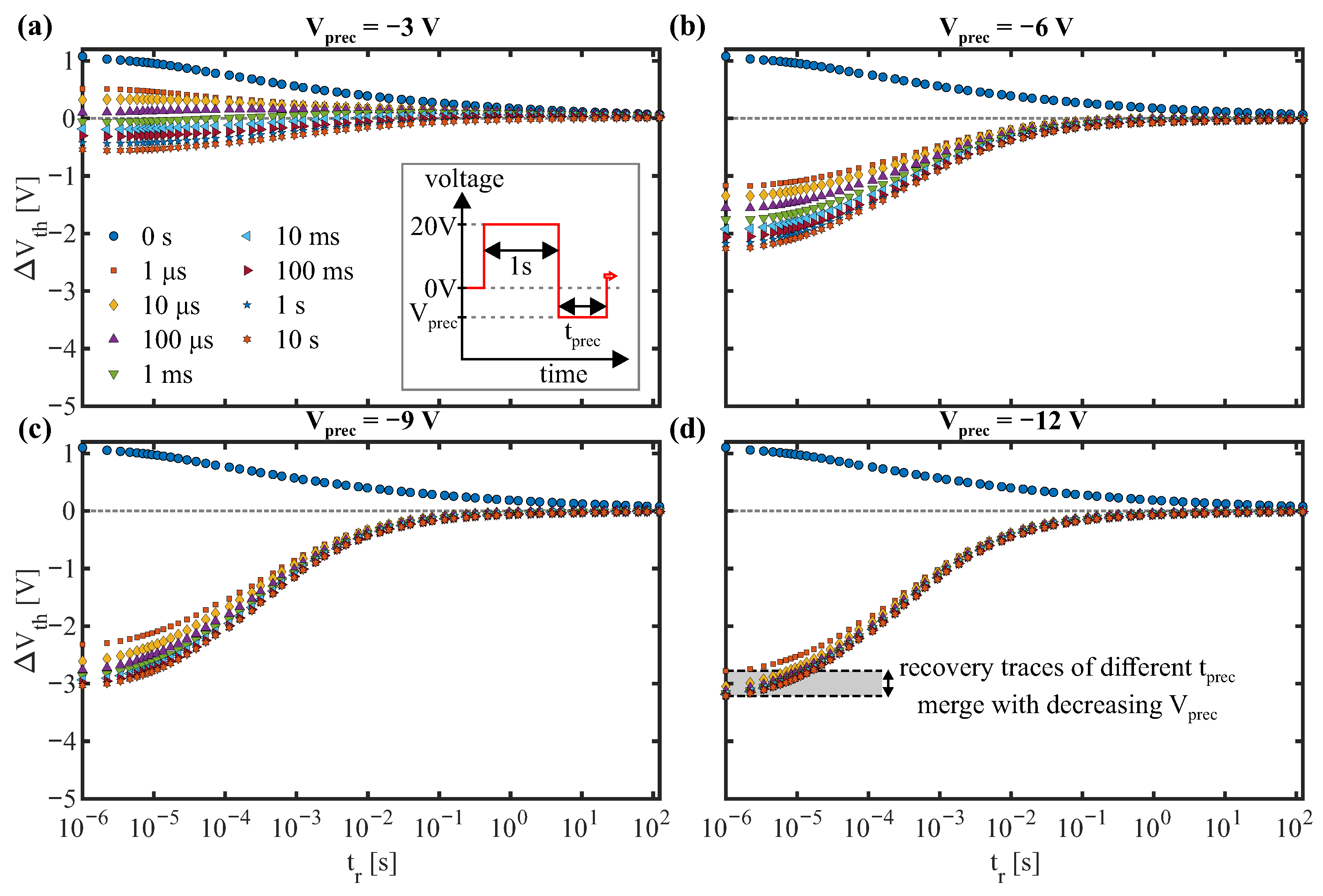

3.1. Threshold Voltage Dynamics after Short Gate Pulses

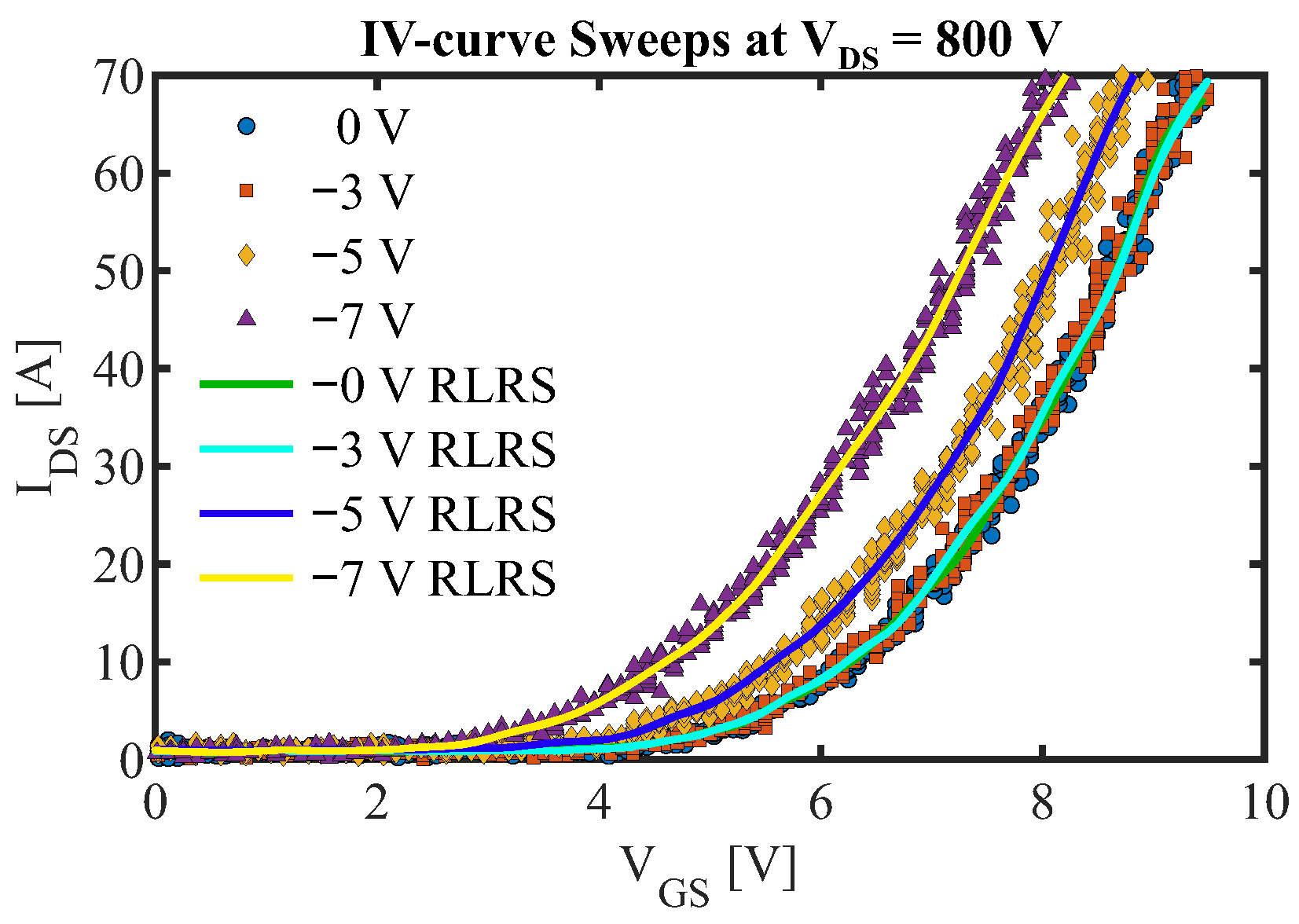

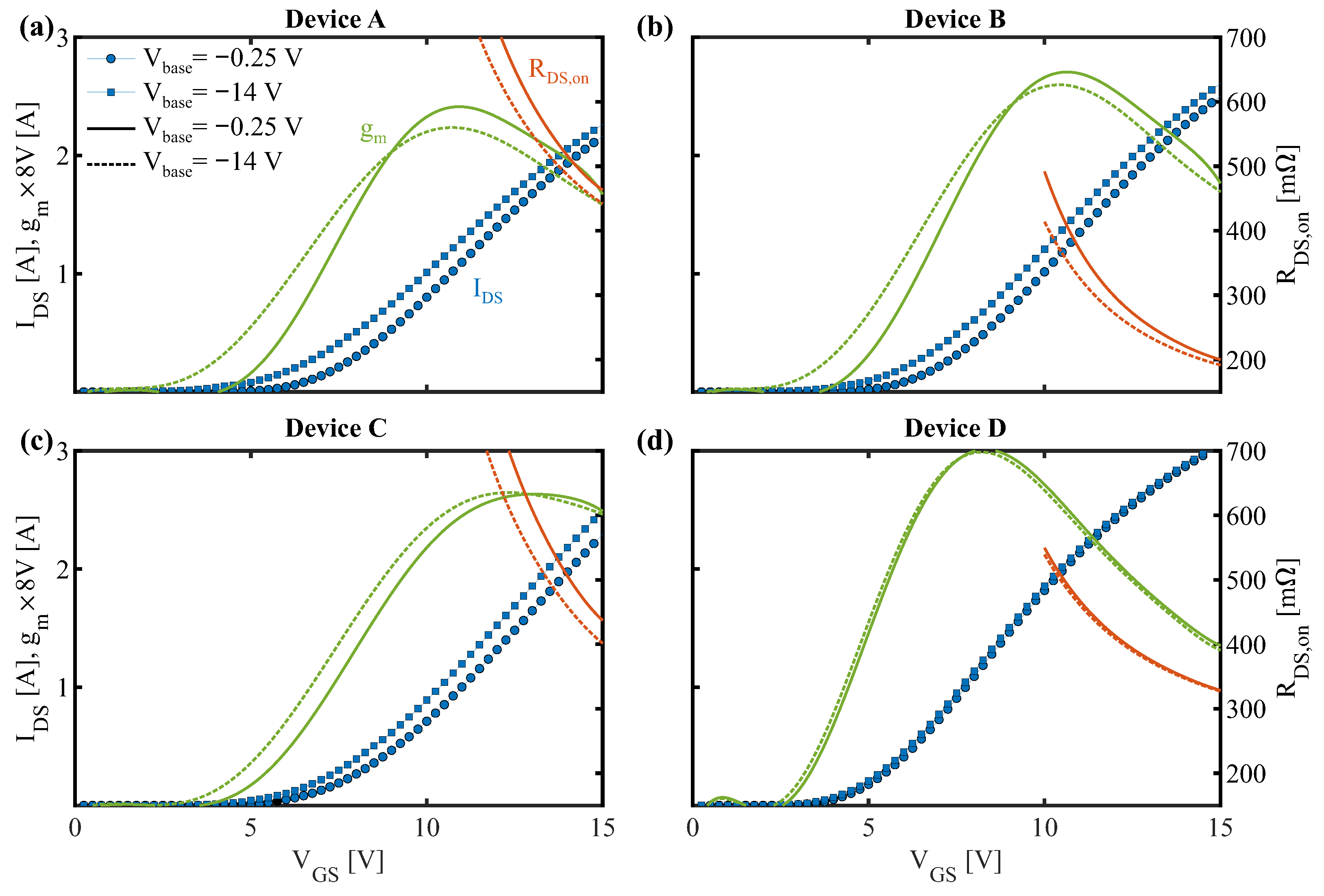

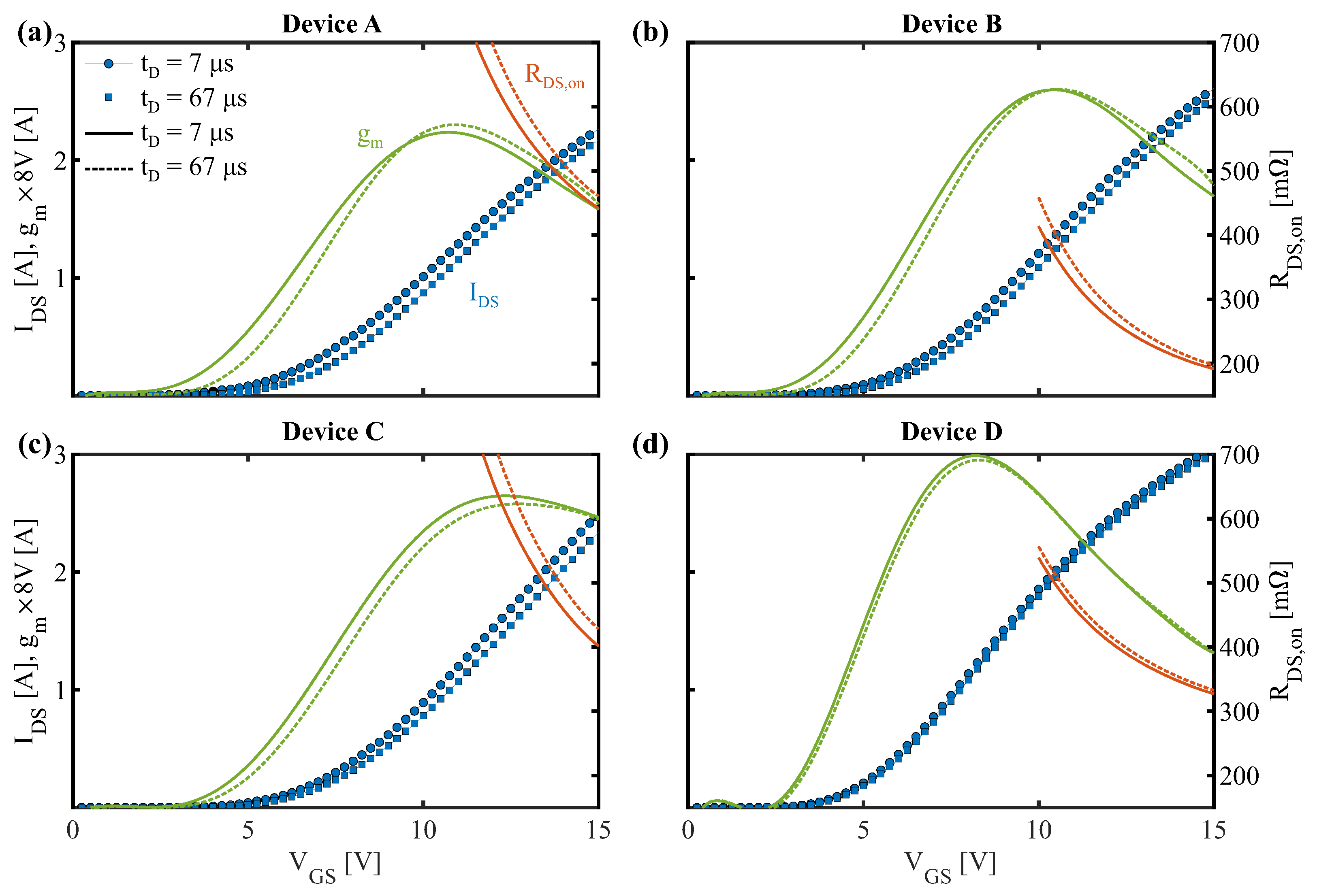

3.2. Drain-Source Current Voltage Characteristics and On-State Resistance

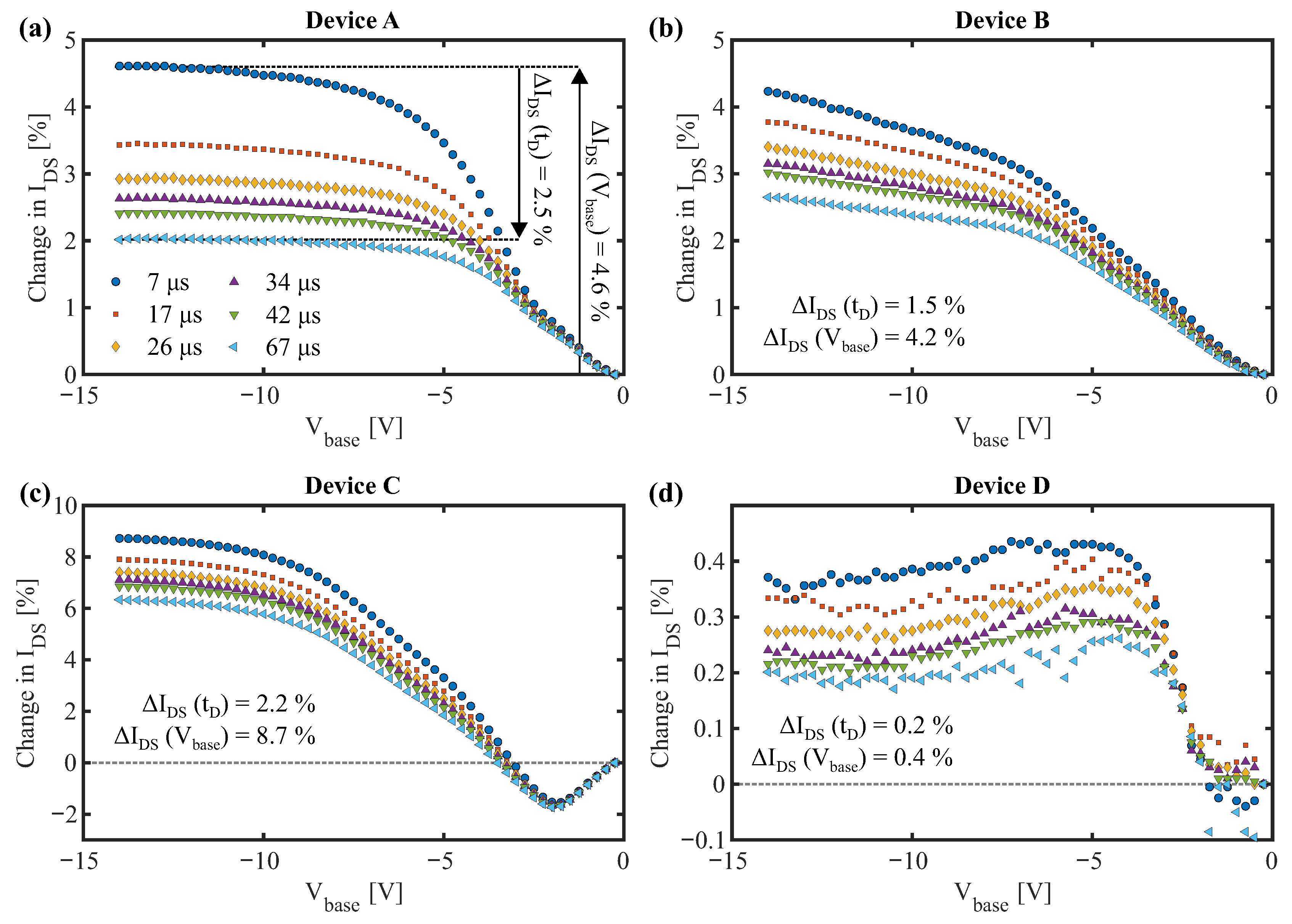

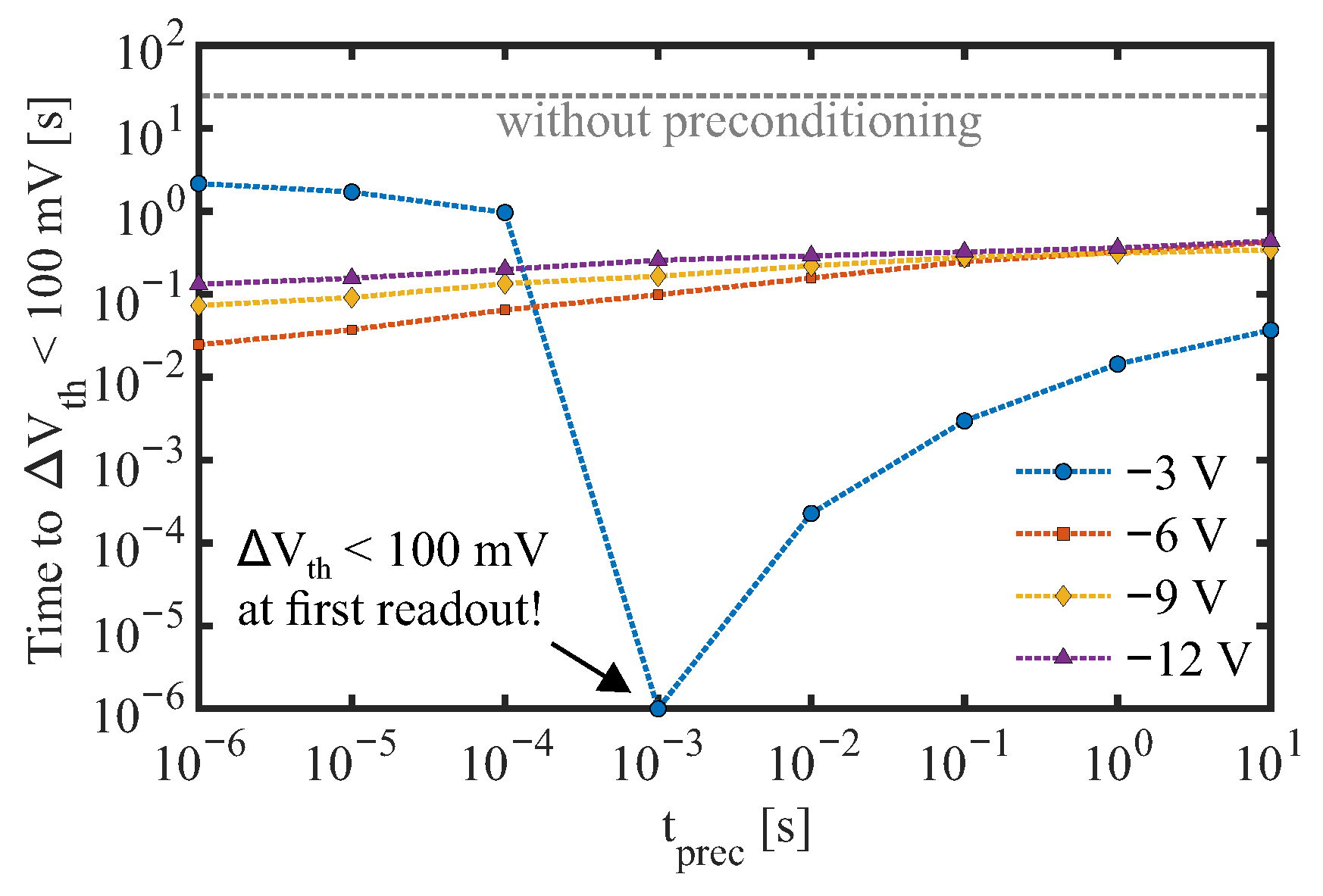

3.3. Device Preconditioning

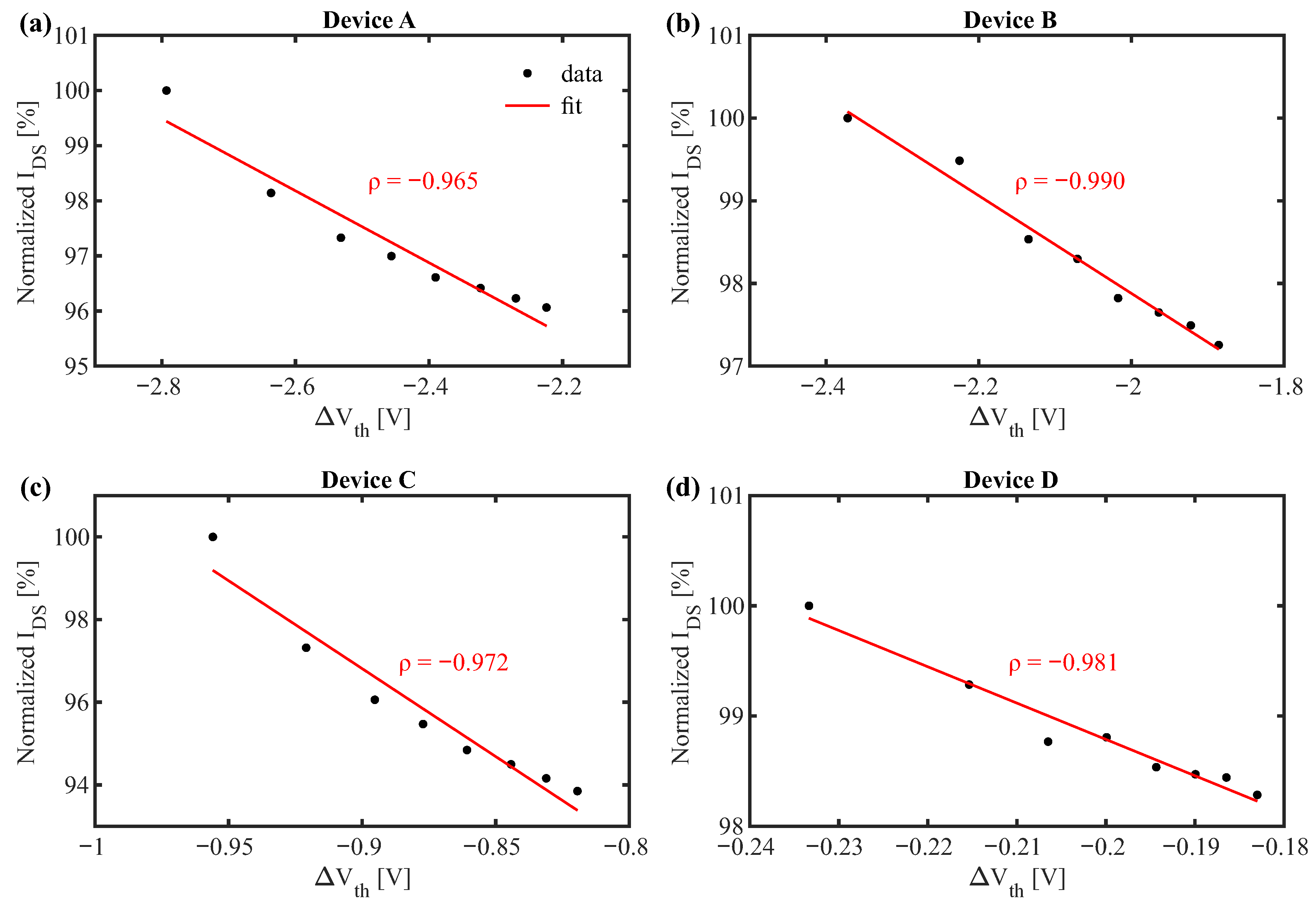

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| SiC | silicon carbide |

| Si | silicon |

| MOSFET | metal-oxide-semiconductor field-effect transistor |

| BTI | bias temperature instability |

Appendix A. Sweeped IV-Curves at High Drain-Source Voltage

Appendix B. Base Voltage Dependence of the Drain-Source Current

Appendix C. Correlation between Change in Drain-Source Current and the Threshold Voltage Shift

References

- Afanas’ev, V.V.; Bassler, M.; Pensl, G.; Schulz, M.J.; Stein von Kamienski, E. Band offsets and electronic structure of SiC/SiO2 interfaces. J. Appl. Phys. 1996, 79, 3108–3114. [Google Scholar] [CrossRef]

- Palmour, J.W. Silicon carbide power device development for industrial markets. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 1.1.1–1.1.8. [Google Scholar] [CrossRef]

- Heer, D.; Domes, D.; Peters, D. Switching performance of a 1200 V SiC-Trench-MOSFET in a low-power module. In Proceedings of the PCIM Europe 2016, Nuremberg, Germany, 10–12 May 2016; pp. 53–59. [Google Scholar]

- Guo, S.; Zhang, L.; Lei, Y.; Li, X.; Xue, F.; Yu, W.; Huang, A.Q. 3.38 Mhz operation of 1.2kV SiC MOSFET with integrated ultra-fast gate drive. In Proceedings of the 3rd IEEE Workshop on Wide Bandgap Power Devices and Applications, Blacksburg, VA, USA, 2–4 November 2015; Volume 25, pp. 390–395. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Peters, D.; Siemieniec, R.; Aichinger, T.; Basler, T.; Esteve, R.; Bergner, W.; Kueck, D. Performance and Ruggedness of 1200 V SiC-Trench-MOSFET. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s, Sapporo, Japan, 28 May–1 June 2017; pp. 239–242. [Google Scholar] [CrossRef]

- Yano, H.; Nakao, H.; Hatayama, T.; Uraoka, Y.; Fuyuki, T. Increased Channel Mobility in 4H-SiC UMOSFETs Using On-Axis Substrates. Mater. Sci. Forum 2007, 556–557, 807–810. [Google Scholar] [CrossRef]

- Anwar, S.; Wang, Z.J.; Chinthavali, M. Characterization and Comparison of Trench and Planar Silicon Carbide (SiC) MOSFET at Different Temperatures. In Proceedings of the 2018 IEEE Transportation Electrification Conference and Expo (ITEC), Long Beach, CA, USA, 13–15 June 2018; pp. 1039–1045. [Google Scholar] [CrossRef]

- Aichinger, T.; Schmidt, M. Gate-oxide reliability and failure-rate reduction of industrial SiC MOSFETs. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Puschkarsky, K.; Grasser, T.; Aichinger, T.; Gustin, W.; Reisinger, H. Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability. IEEE Trans. Electron. Devices 2019, 66, 4604–4616. [Google Scholar] [CrossRef]

- Schleich, C.; Berens, J.; Rzepa, G.; Pobegen, G.; Rescher, G.; Tyaginov, S.; Grasser, T.; Waltl, M. Physical Modeling of Bias Temperature Instabilities in SiC MOSFETs. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 486–489. [Google Scholar] [CrossRef]

- Rescher, G.; Pobegen, G.; Aichinger, T.; Grasser, T. On the subthreshold drain current sweep hysteresis of 4H-SiC nMOSFETs. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 10.8.1–10.8.4. [Google Scholar] [CrossRef]

- Puschkarsky, K.; Grasser, T.; Aichinger, T.; Gustin, W.; Reisinger, H. Understanding and Modeling Transient Threshold Voltage Instabilities in SiC MOSFETs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 3B.5-1–3B.5-10. [Google Scholar] [CrossRef]

- Puschkarsky, K.; Reisinger, H.; Aichinger, T.; Gustin, W.; Grasser, T. Threshold voltage hysteresis in SiC MOSFETs and its impact on circuit operation. In Proceedings of the 2017 IEEE International Integrated Reliability Workshop (IIRW), Fallen Leaf Lake, CA, USA, 8–12 October 2017. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B. SiC MOSFET threshold-stability issues. Mater. Sci. Semicond. Process. 2018, 78, 32–37. [Google Scholar] [CrossRef]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Rescher, G.; Pobegen, G.; Aichinger, T.; Grasser, T. Preconditioned BTI on 4H-SiC: Proposal for a Nearly Delay Time-Independent Measurement Technique. IEEE Trans. Electron Devices 2018, 65, 1419–1426. [Google Scholar] [CrossRef]

- Reisinger, H.; Blank, O.; Heinrigs, W.; Mühlhoff, A.; Gustin, W.; Schlünder, C. Analysis of NBTI Degradation- and Recovery-Behavior Based on Ultra Fast VT-Measurements. In Proceedings of the 2006 IEEE International Reliability Physics Symposium Proceedings, San Jose, CA, USA, 26–30 March 2006; pp. 448–453. [Google Scholar] [CrossRef]

- Basler, T.; Heer, D.; Peters, D.; Aichinger, T.; Schörner, R. Practical Aspects and Body Diode Robustness of a 1200 V SiC Trench MOSFET. In Proceedings of the PCIM Europe 2018, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management. VDE, Nuremberg, Germany, 5–7 June 2018; pp. 536–542. [Google Scholar]

- Gruber, G.; Cottom, J.; Meszaros, R.; Koch, M.; Pobegen, G.; Aichinger, T.; Peters, D.; Hadley, P. Electrically detected magnetic resonance of carbon dangling bonds at the Si-face 4H-SiC/SiO2 interface. J. Appl. Phys. 2018, 123, 161514. [Google Scholar] [CrossRef]

| Label | [V] | [V] | [V] | [V] | [pF] | Design | [ns] |

|---|---|---|---|---|---|---|---|

| A | 1200 | 3.5–5.7 | −7 | 23 | 182 | trench | 16 |

| B | 1200 | 2.7–5.6 | −4 | 22 | 398 | trench | 16 |

| C | 1200 | 1.8–N/A | −10 | 25 | 290 | planar | 7 |

| D | 1200 | 2.0–4.0 | −10 | 25 | 259 | planar | 14 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Feil, M.W.; Huerner, A.; Puschkarsky, K.; Schleich, C.; Aichinger, T.; Gustin, W.; Reisinger, H.; Grasser, T. The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters. Crystals 2020, 10, 1143. https://doi.org/10.3390/cryst10121143

Feil MW, Huerner A, Puschkarsky K, Schleich C, Aichinger T, Gustin W, Reisinger H, Grasser T. The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters. Crystals. 2020; 10(12):1143. https://doi.org/10.3390/cryst10121143

Chicago/Turabian StyleFeil, Maximilian W., Andreas Huerner, Katja Puschkarsky, Christian Schleich, Thomas Aichinger, Wolfgang Gustin, Hans Reisinger, and Tibor Grasser. 2020. "The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters" Crystals 10, no. 12: 1143. https://doi.org/10.3390/cryst10121143

APA StyleFeil, M. W., Huerner, A., Puschkarsky, K., Schleich, C., Aichinger, T., Gustin, W., Reisinger, H., & Grasser, T. (2020). The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters. Crystals, 10(12), 1143. https://doi.org/10.3390/cryst10121143