TCAD Simulation Study of ESD Behavior of InGaAs/InP Heterojunction Tunnel FETs

Abstract

1. Introduction

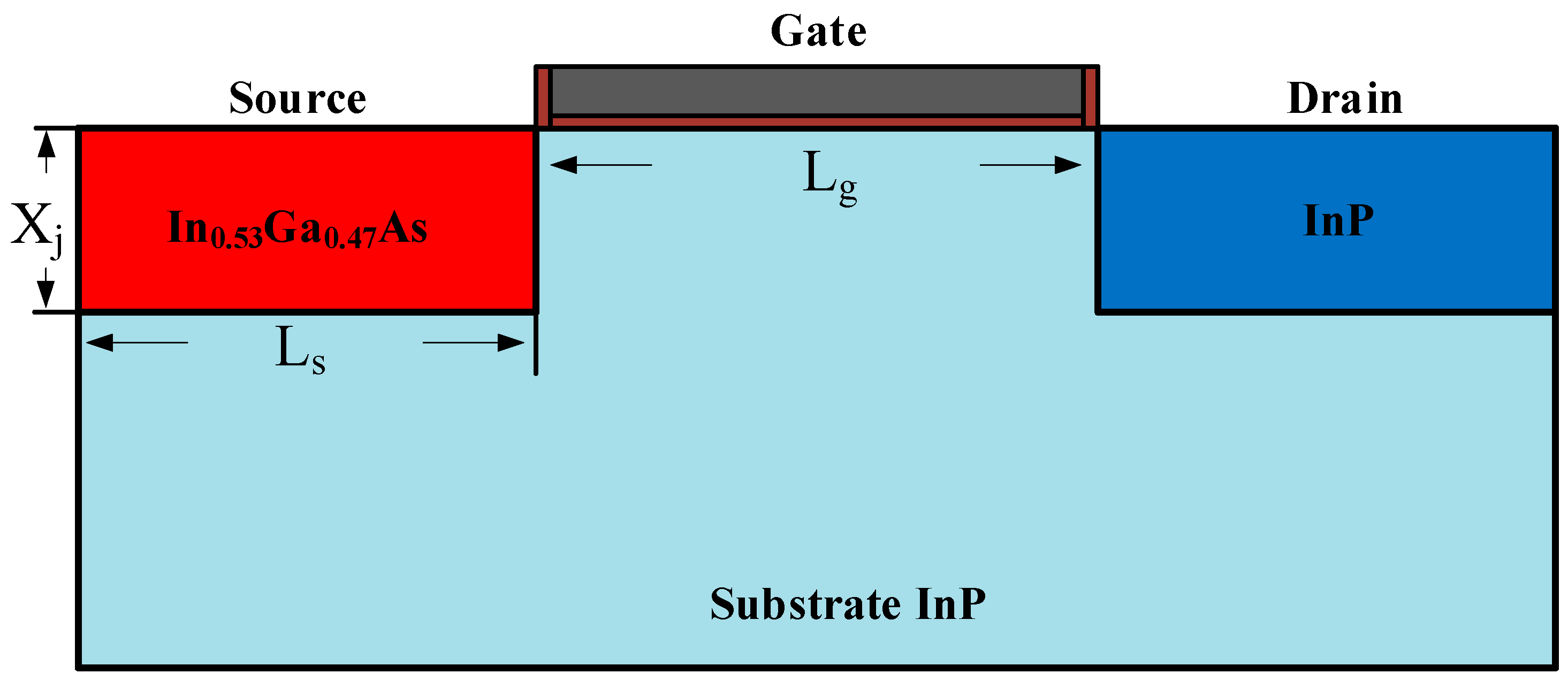

2. Model Calibration and Device Structure

3. Off- and On-State Current with Different Parameters

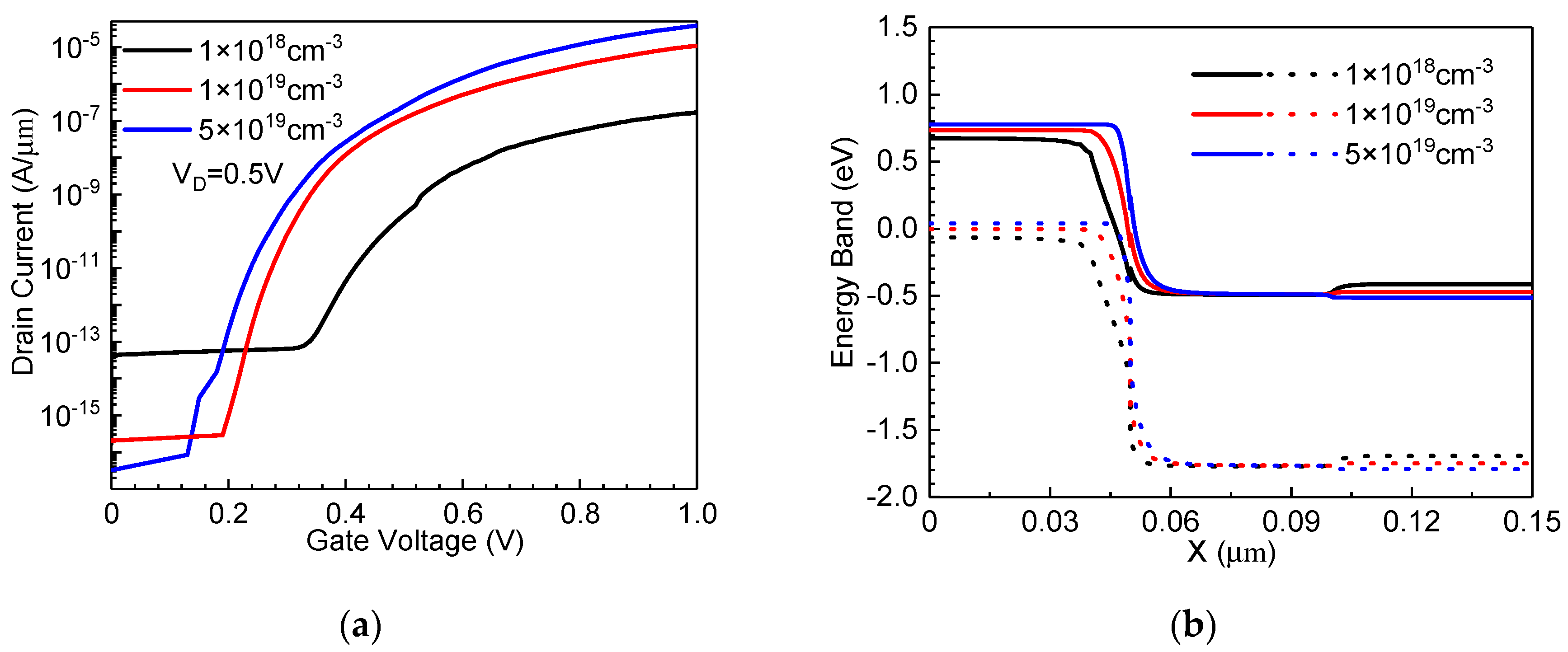

3.1. Effect of the Source Doping Concentration

3.2. Effect of Channel Length

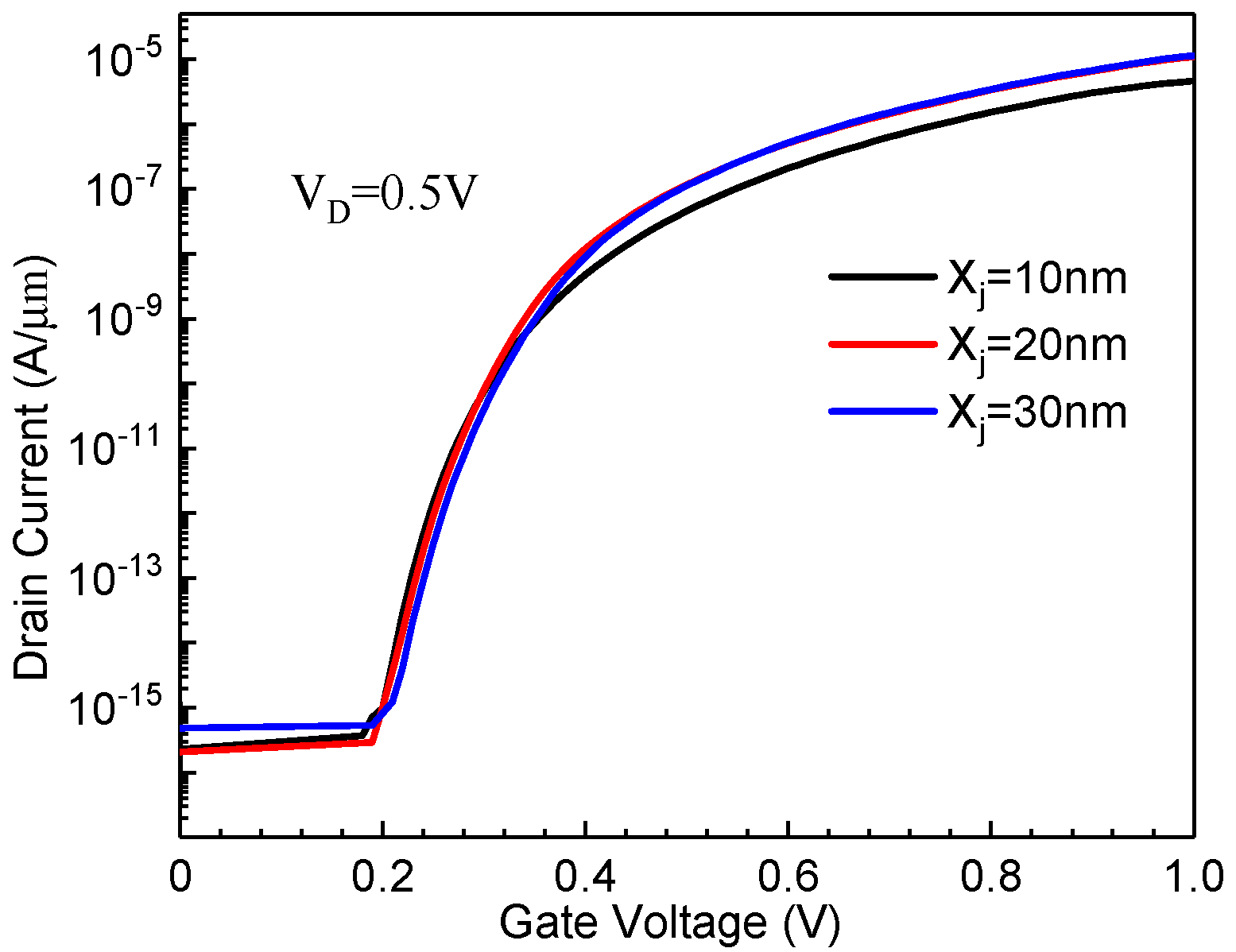

3.3. Effect of Junction Depth

3.4. Effect of the Doping Concentration of the Substrate

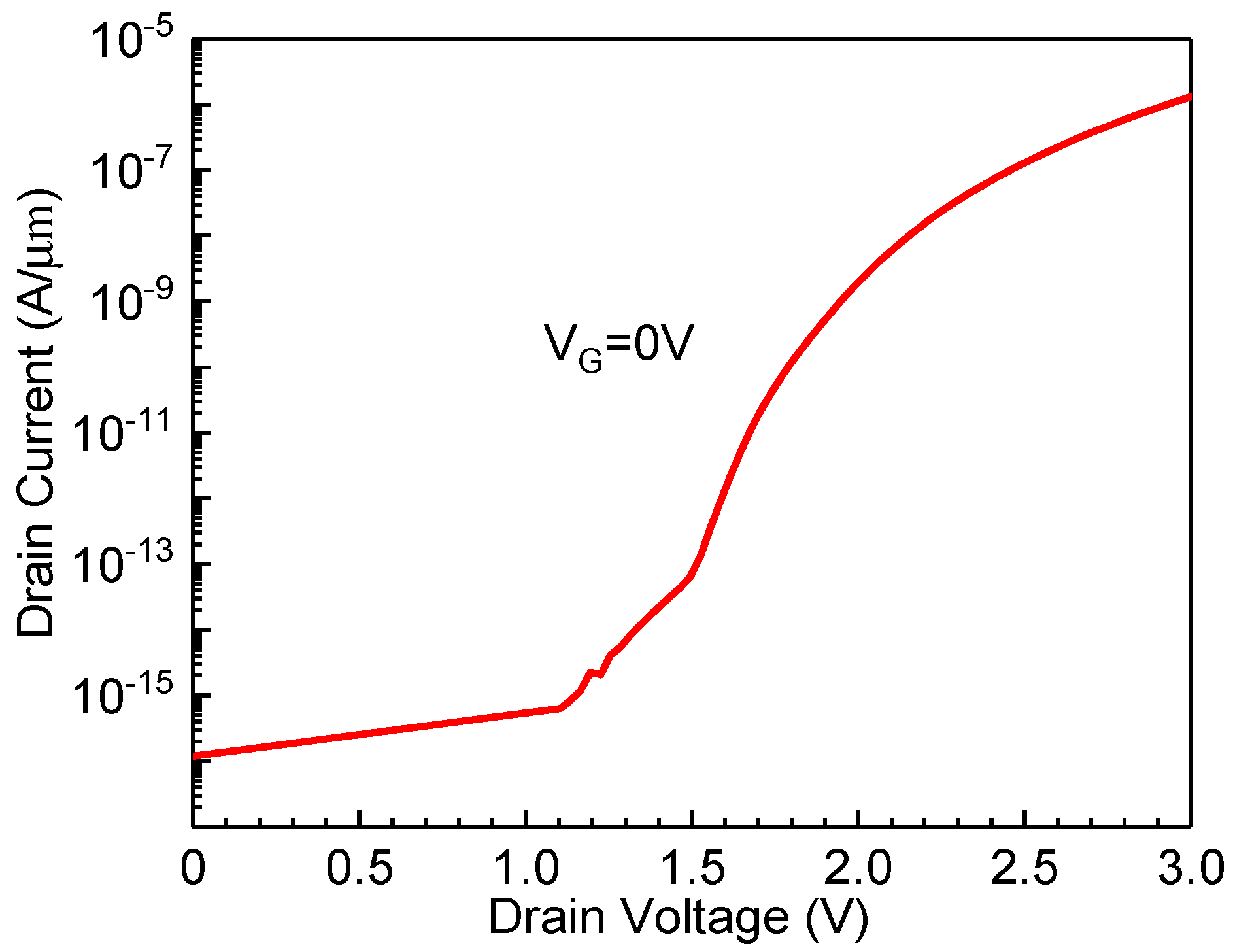

3.5. Breakdown Voltage

4. The Quasi-Static Characteristics of the HTFET under TLP Stress

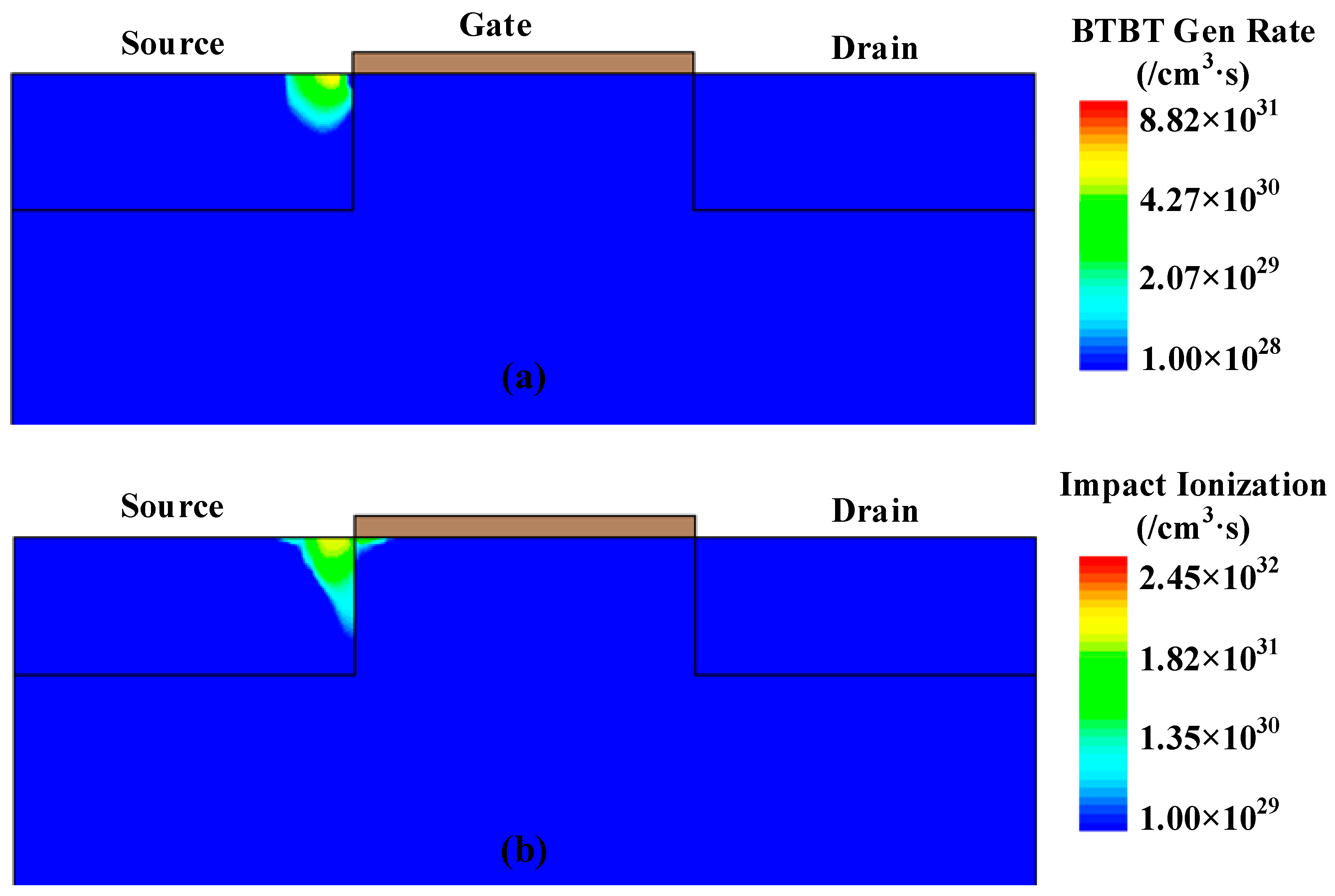

4.1. Forward Direction

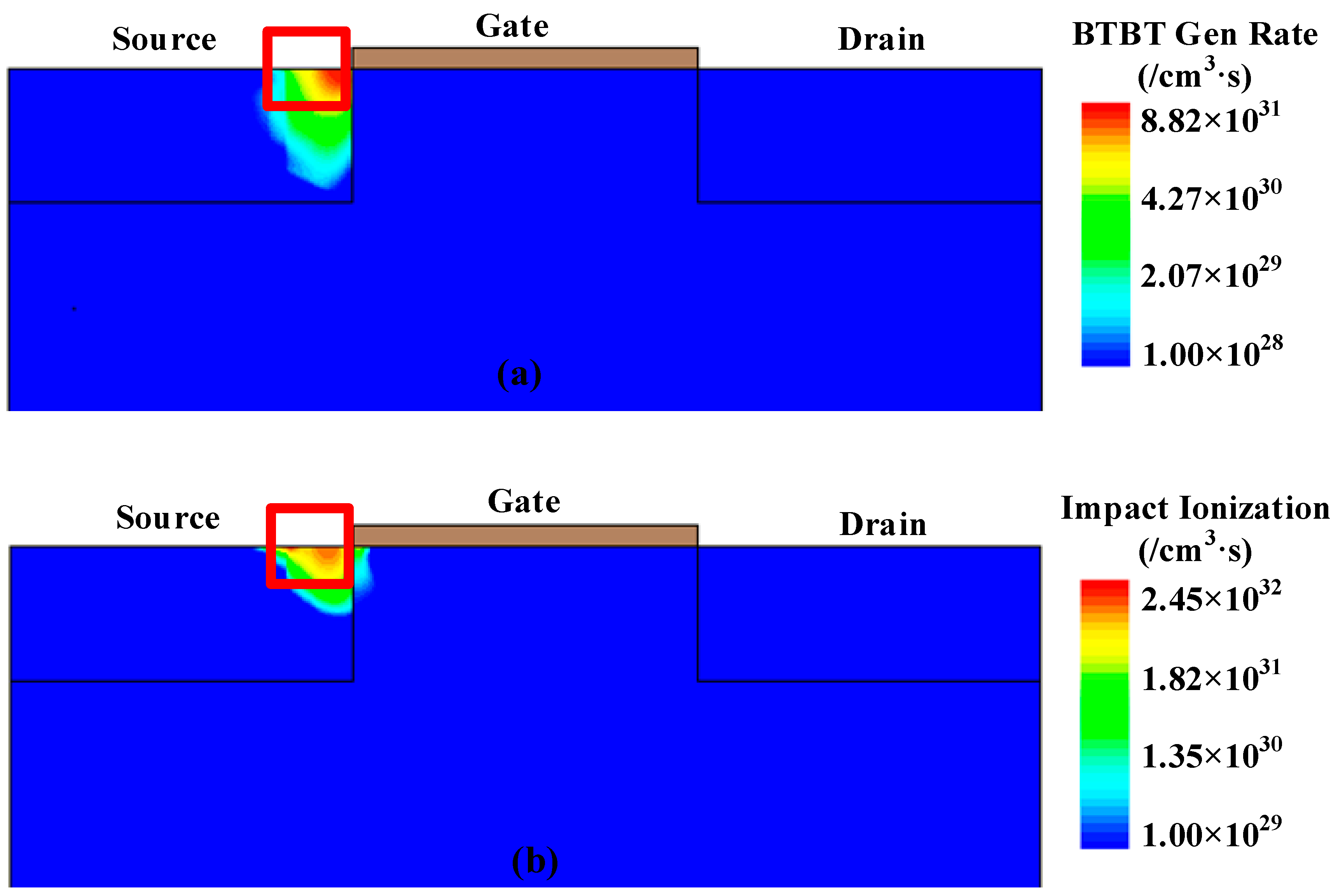

4.2. Reverse Direction

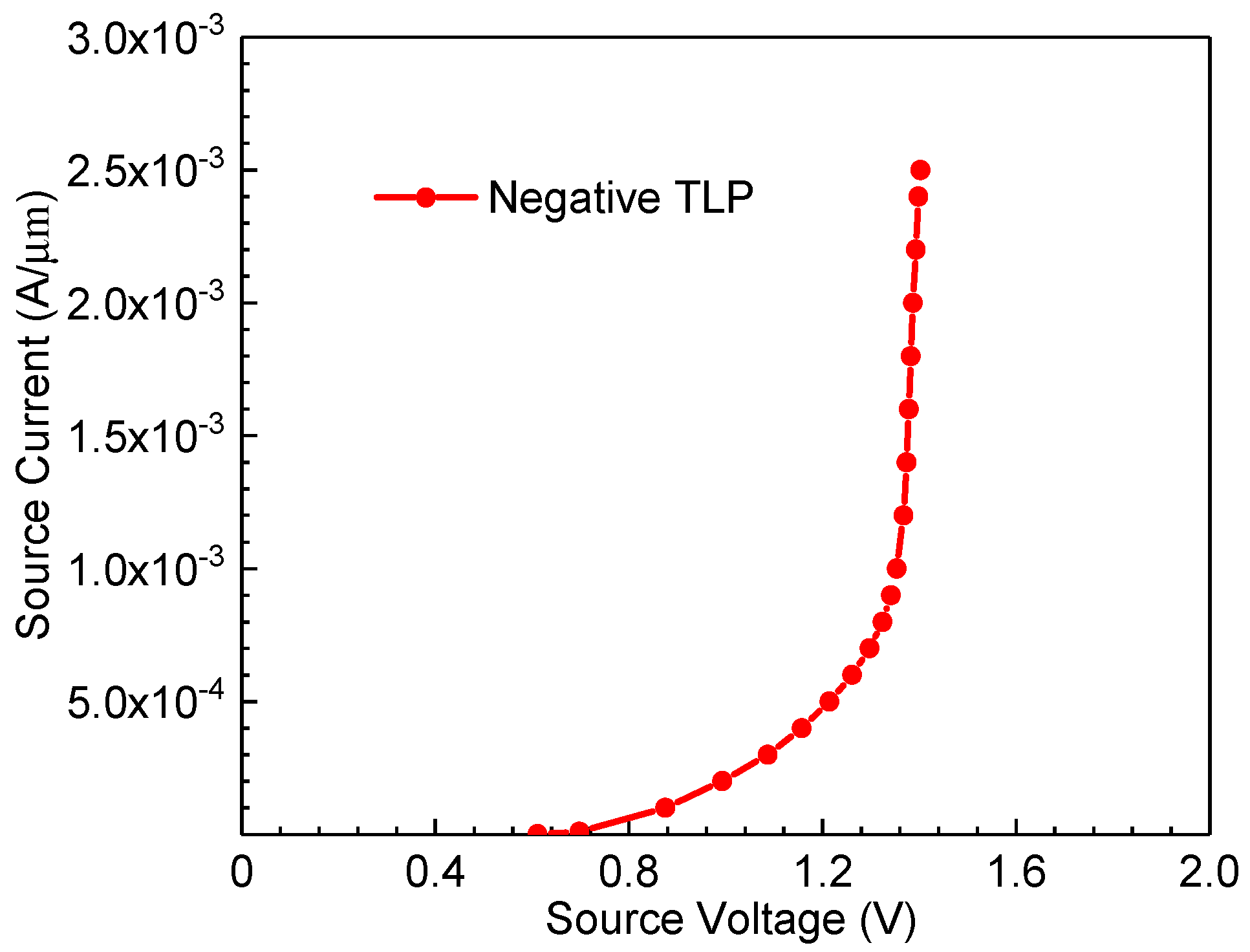

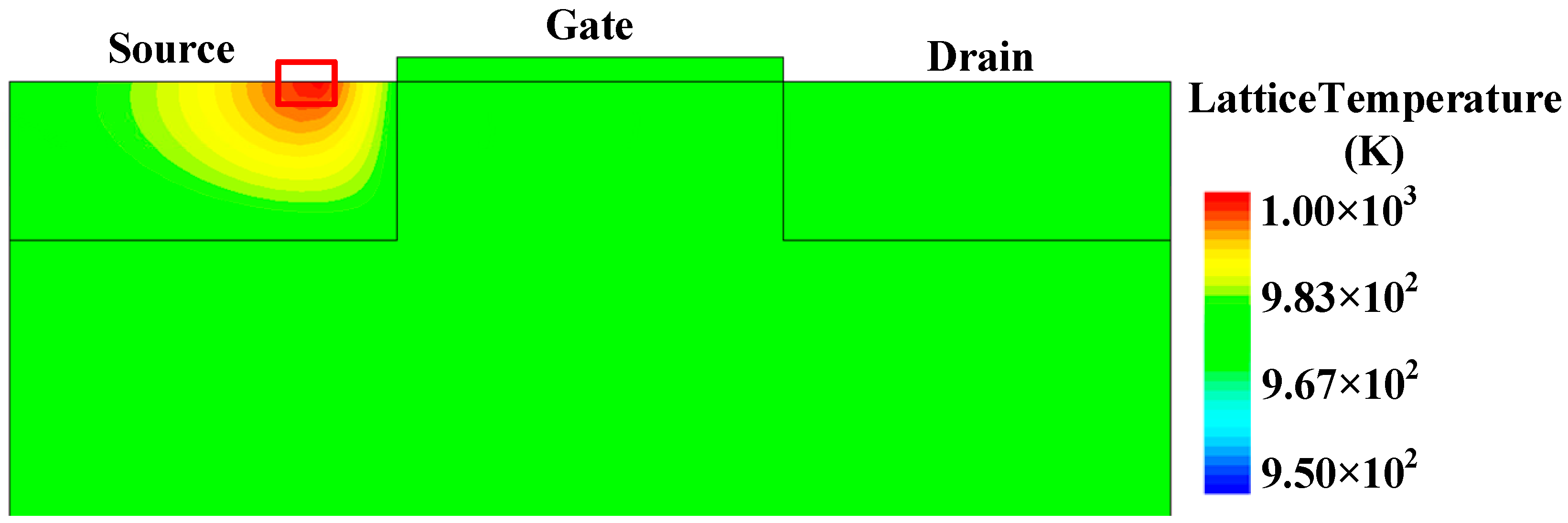

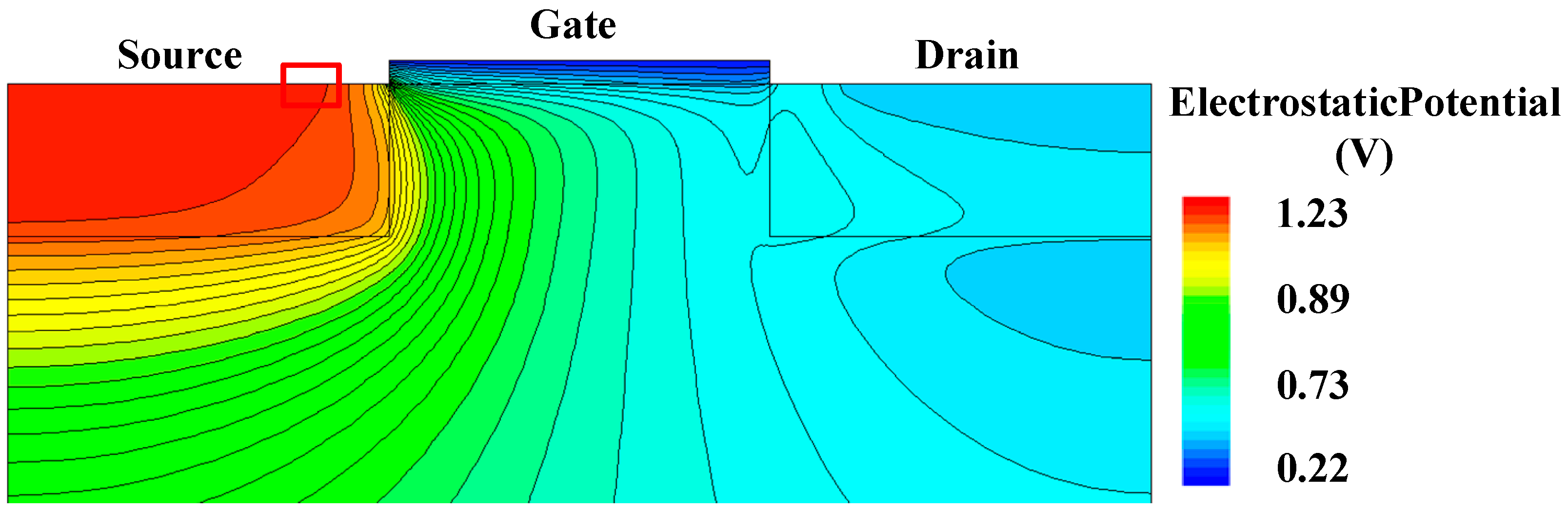

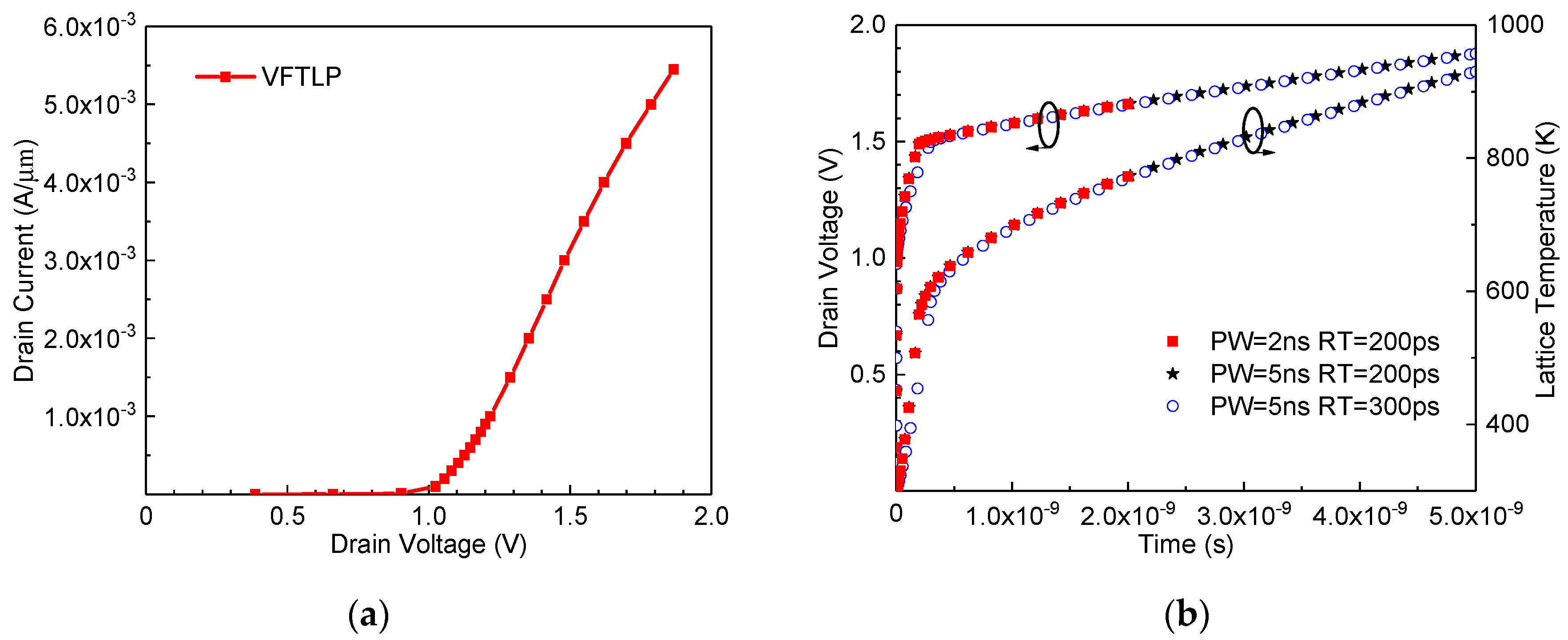

5. The Quasi-Static Characteristics of the HTFET under VFTLP Stress

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nat. Cell Biol. 2011, 479, 329–337. [Google Scholar] [CrossRef] [PubMed]

- Lu, H.; Seabaugh, A. Tunnel Field-Effect Transistors: State-of-the-Art. IEEE J. Electron Devices Soc. 2014, 2, 44–49. [Google Scholar] [CrossRef]

- Wang, X.D.; Xiong, Y.; Tang, M.-H.; Peng, L.; Xiao, Y.G.; Xu, X.Y.; Liang, S.E.; Zhong, X.H.; He, J.H. A Si tunnel field-effect transistor model with a high switching current ratio and steep sub-threshold swing. Semicond. Sci. Technol. 2014, 29, 5–9. [Google Scholar] [CrossRef]

- Kim, S.H.; Agarwal, S.; Jacobson, Z.A.; Matheu, P.; Hu, C.; Liu, T.-J.K. Tunnel Field Effect Transistor With Raised Germanium Source. IEEE Electron Device Lett. 2010, 31, 1107–1109. [Google Scholar] [CrossRef]

- Blaeser, S.; Glass, S.; Schulte-Braucks, C.; Narimani, K.; Driesch, N.V.D.; Wirths, S.; Tiedemann, A.T.; Trellenkamp, S.; Buca, D.; Zhao, Q.-T.; et al. Novel SiGe/Si line tunneling TFET with high Ion at low Vdd and constant SS. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: New York, NY, USA, 2015. [Google Scholar]

- Dubey, P.K.; Kaushik, B.K. T-Shaped III-V Heterojunction Tunneling Field-Effect Transistor. IEEE Trans. Electron Devices 2017, 64, 3120–3125. [Google Scholar] [CrossRef]

- Zhou, G.; Lu, Y.; Li, R.; Zhang, Q.; Hwang, W.S.; Liu, Q.; Vasen, T.; Chen, C.; Zhu, H.; Kuo, J.-M.; et al. Vertical InGaAs/InP Tunnel FETs With Tunneling Normal to the Gate. IEEE Electron Device Lett. 2011, 32, 1516–1518. [Google Scholar] [CrossRef]

- Sant, S.; Schenk, A. Methods to Enhance the Performance of InGaAs/InP Heterojunction Tunnel FETs. IEEE Trans. Electron Devices 2015, 63, 2169–2175. [Google Scholar] [CrossRef]

- Dong, A.; Xiong, J.; Mitra, S.; Liang, W.; Gauthier, R.; Loiseau, A. Comprehensive Study of ESD Design Window Scaling Down to 7nm Technology Node. In Proceedings of the 2018 40th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 23–28 September 2018; Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA. [Google Scholar]

- Mergens, M.P.J.; Russ, C.C.; Verhaege, K.; Armer, J.; Jozwiak, P.C.; Mohn, R.P.; Keppens, B.; Trinh, C.S. Speed optimized diode-triggered SCR (DTSCR) for RF ESD protection of ultra-sensitive IC nodes in advanced technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 532–542. [Google Scholar] [CrossRef]

- Galy, P. Electro Static Discharge (ESD) one real life event: Physical impact and protection challenges in advanced CMOS technologies. In Proceedings of the 2014 International Semiconductor Conference (CAS), Sinaia, Romania, 13–15 October 2014; Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA; pp. 31–34. [Google Scholar]

- Galy, P.; Athanasiou, S. Preliminary results on TFET—Gated diode in thin silicon film for IO design & ESD protection in 28nm UTBB FD-SOI CMOS technology. In Proceedings of the 2016 International Conference on IC Design and Technology (ICICDT), Ho Chi Minh City, Vietnam, 27–29 June 2016; Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA; pp. 1–4. [Google Scholar]

- Kranthi, N.K.; Shrivastava, M. ESD Behavior of Tunnel FET Devices. IEEE Trans. Electron Devices 2016, 64, 28–36. [Google Scholar] [CrossRef]

- Yang, Z.; Zhang, Y.; Yang, Y.; Yu, N. Investigation of the Double Current Path Phenomenon in Gate-Grounded Tunnel FET. IEEE Electron Device Lett. 2017, 39, 103–106. [Google Scholar] [CrossRef]

- Sithanandam, R.; Kumar, M.J. A New On-Chip ESD Strategy Using TFETs-TCAD Based Device and Network Simulations. IEEE J. Electron Devices Soc. 2018, 6, 298–308. [Google Scholar] [CrossRef]

- Colinge, J.-P.; Alderman, J.C.; Xiong, W.; Cleavelin, C.R. Quantum-mechanical effects in trigate SOI MOSFETs. IEEE Trans. Electron Devices 2006, 53, 1131–1136. [Google Scholar] [CrossRef]

- Sahay, S.; Kumar, M.J. Insight into Lateral Band-to-Band-Tunneling in Nanowire Junctionless FETs. IEEE Trans. Electron Devices 2016, 63, 4138–4142. [Google Scholar] [CrossRef]

- Wang Albert, Z.H. On-chip ESD Protection for Integrated Circuits: An IC Design Perspective; Springer US: Manhattan, NY, USA, 2002; p. 233. [Google Scholar]

- Yang, Z.; Yang, Y.; Yu, N.; Liou, J.J. Improving ESD Protection Robustness Using SiGe Source/Drain Regions in Tunnel FET. Micromachines 2018, 9, 657. [Google Scholar] [CrossRef] [PubMed]

- Brenchley, M.E.; Hopkinson, M.; Kelly, A.; Kidd, P.; Dunstan, D.J. Coherency Strain as an Athermal Strengthening Mechanism. Phys. Rev. Lett. 1997, 78, 3912–3914. [Google Scholar] [CrossRef]

- Lim, C.G. Thermal Modeling of Intersubband Transition-Based InGaAs/AlAsSb Ultrafast All-Optical Cross-Phase Modulators. IEEE J. Quantum Electron. 2010, 46, 610–617. [Google Scholar] [CrossRef]

| Parameter | Unit | In0.53Ga0.47As | InP |

|---|---|---|---|

| Eg | eV | 0.74 | 1.35 |

| Electron affinity | eV | 4.5 | 4.38 |

| mte | m0 | 0.043 | 0.08 |

| mth | m0 | 0.052 | 0.12 |

| Degeneracy | 1 | 2 | 2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, Z.; Yang, Z.; Zhang, Y.; Fan, X.; Liou, J.J.; Fan, W. TCAD Simulation Study of ESD Behavior of InGaAs/InP Heterojunction Tunnel FETs. Crystals 2020, 10, 1059. https://doi.org/10.3390/cryst10111059

Zhu Z, Yang Z, Zhang Y, Fan X, Liou JJ, Fan W. TCAD Simulation Study of ESD Behavior of InGaAs/InP Heterojunction Tunnel FETs. Crystals. 2020; 10(11):1059. https://doi.org/10.3390/cryst10111059

Chicago/Turabian StyleZhu, Zhihua, Zhaonian Yang, Yingtao Zhang, Xiaomei Fan, Juin Jei Liou, and Wenbing Fan. 2020. "TCAD Simulation Study of ESD Behavior of InGaAs/InP Heterojunction Tunnel FETs" Crystals 10, no. 11: 1059. https://doi.org/10.3390/cryst10111059

APA StyleZhu, Z., Yang, Z., Zhang, Y., Fan, X., Liou, J. J., & Fan, W. (2020). TCAD Simulation Study of ESD Behavior of InGaAs/InP Heterojunction Tunnel FETs. Crystals, 10(11), 1059. https://doi.org/10.3390/cryst10111059