Pre-Silicon Accurate SPICE Modeling of Trench MOSFETs via Advanced TCAD Simulations and Dynamic Validation

Abstract

1. Introduction

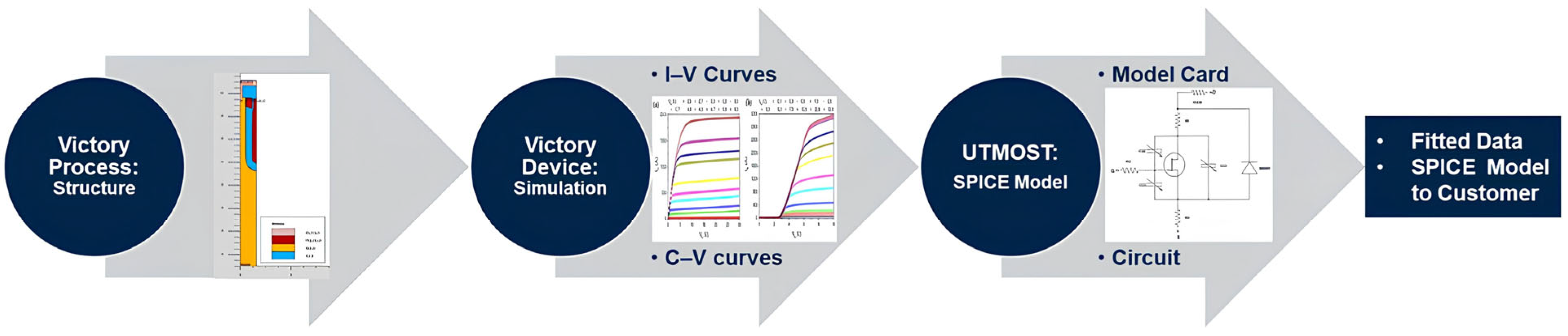

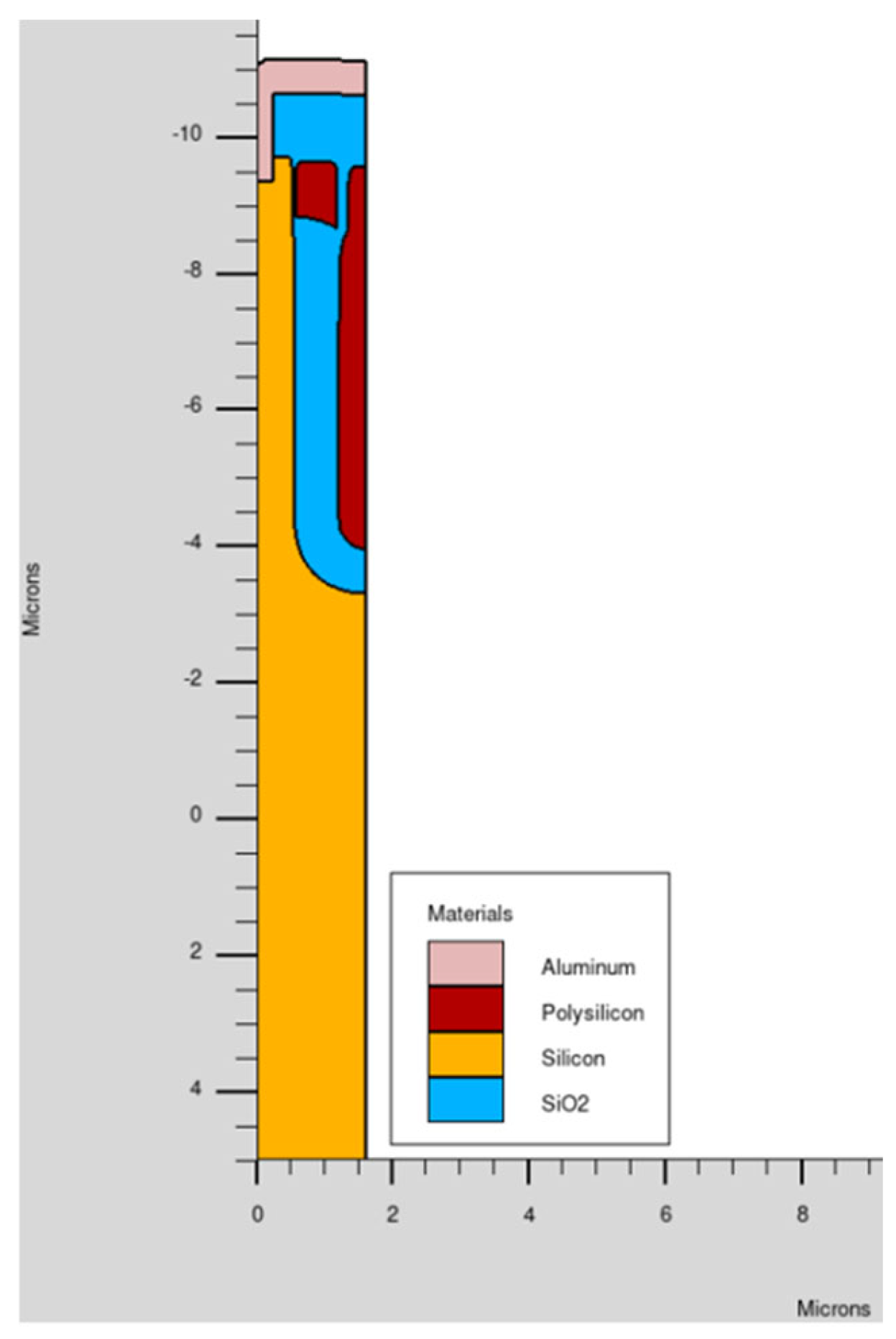

2. TCAD Simulation

2.1. Process Structure

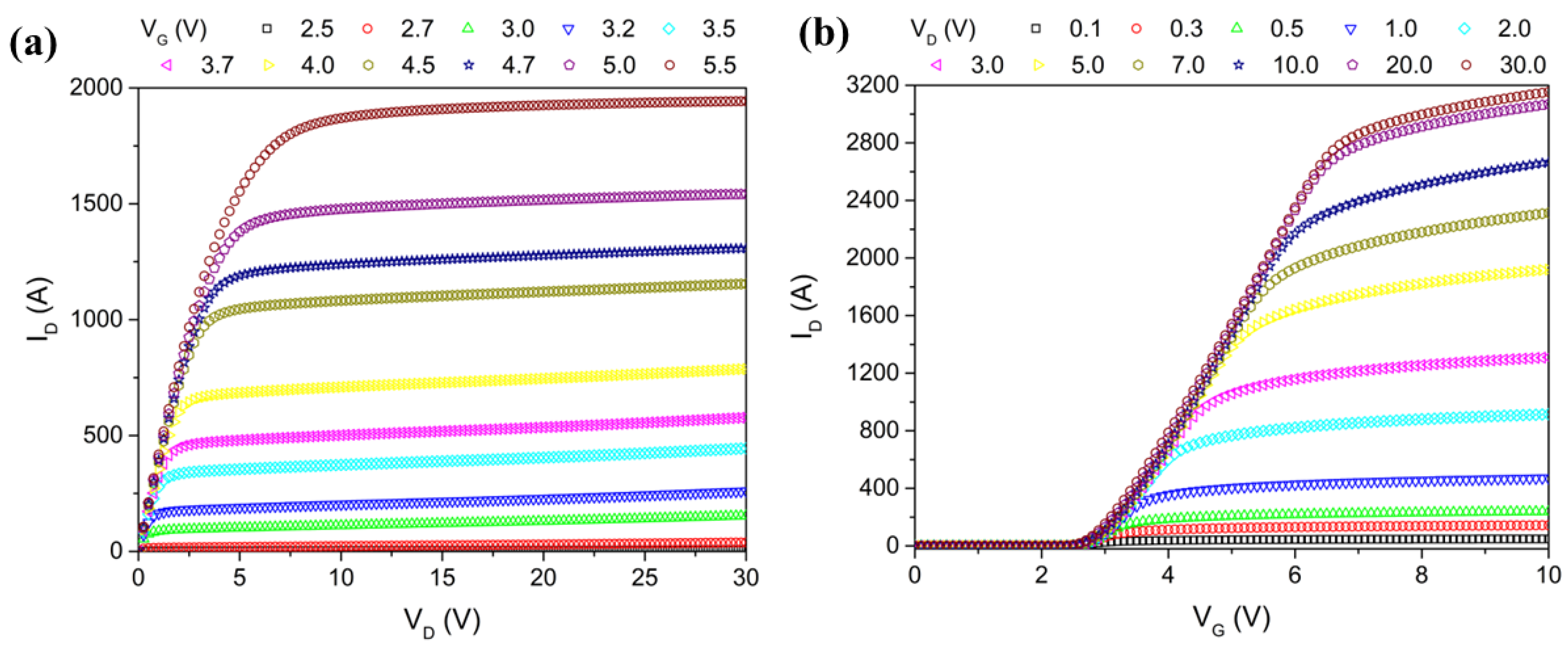

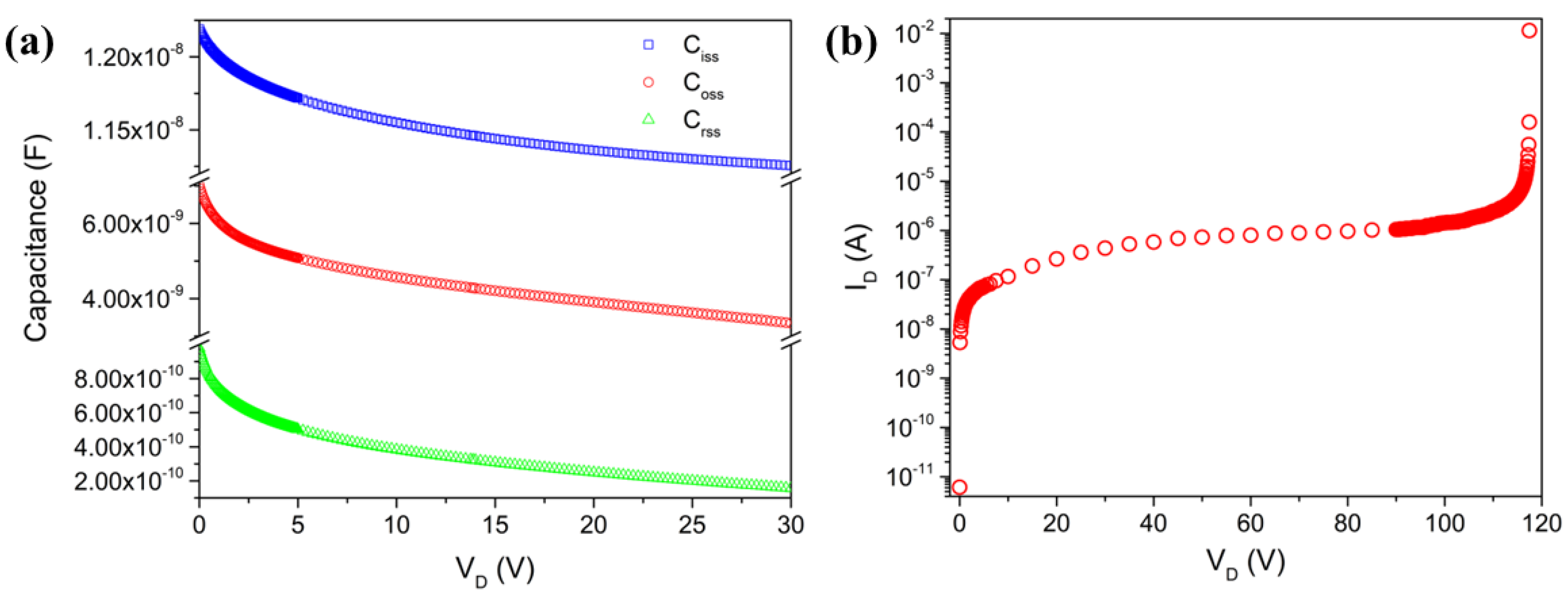

2.2. Device Simulations

3. Results

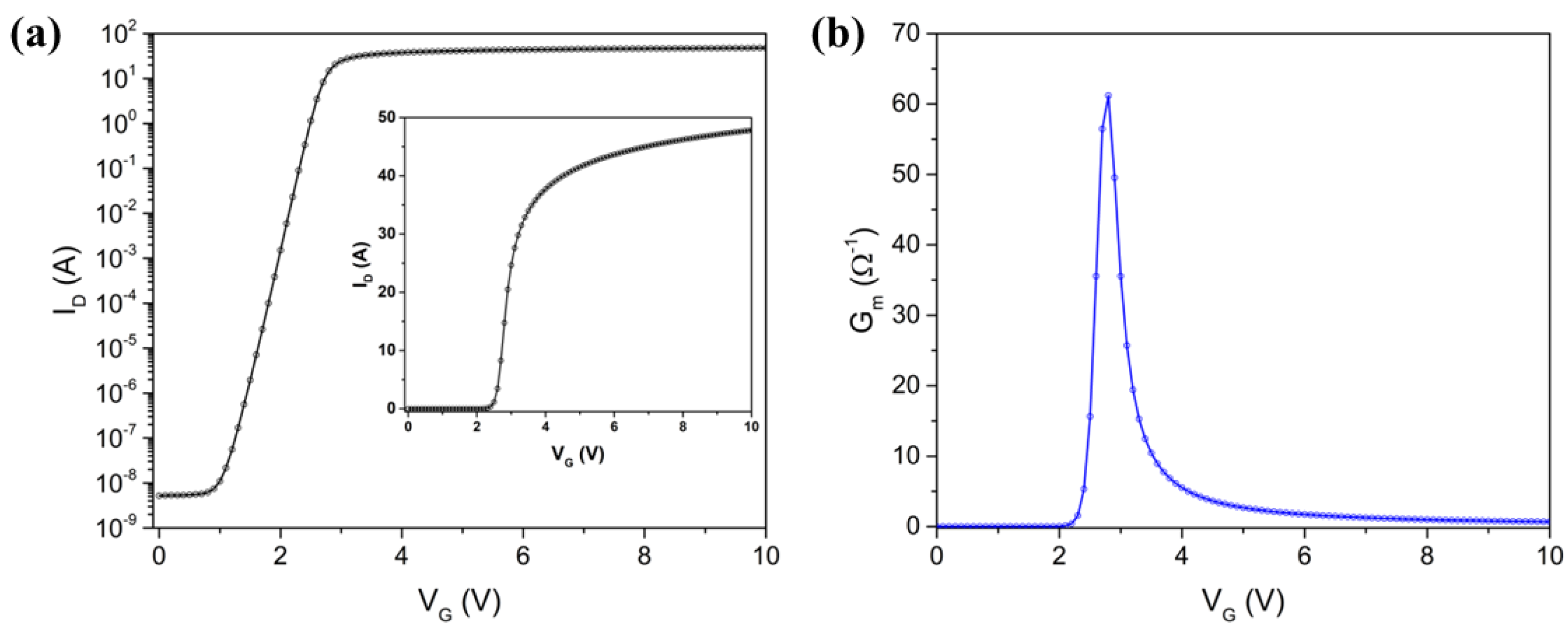

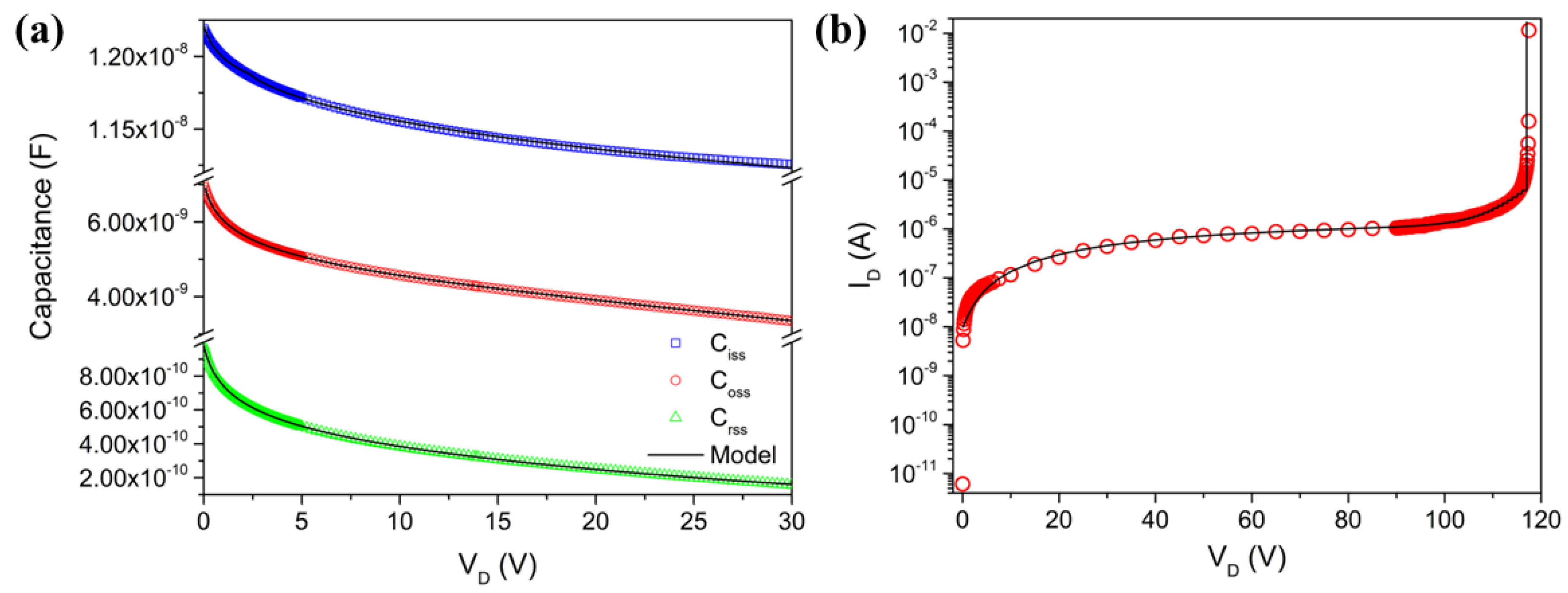

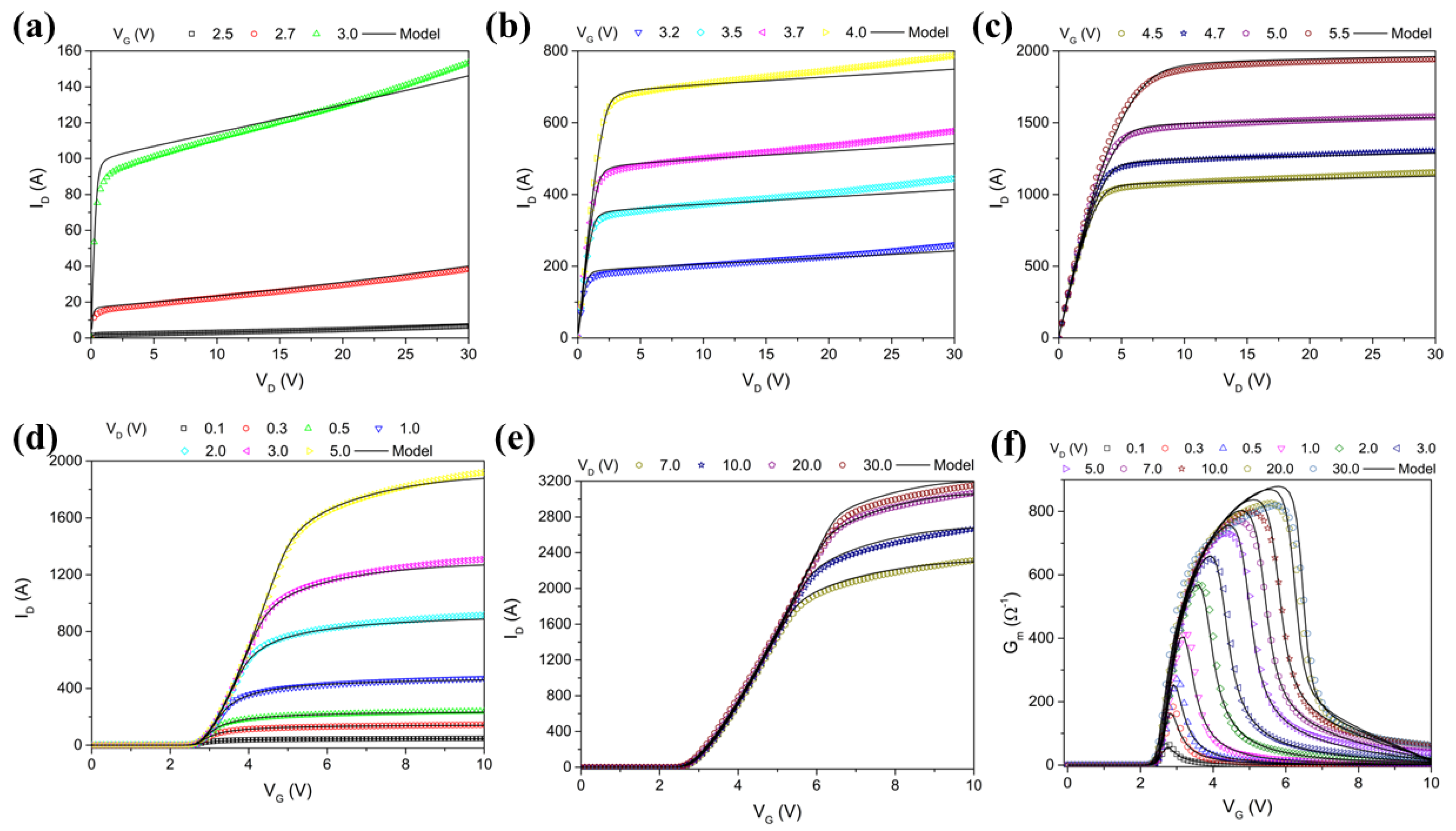

3.1. Initial Parameter Extraction

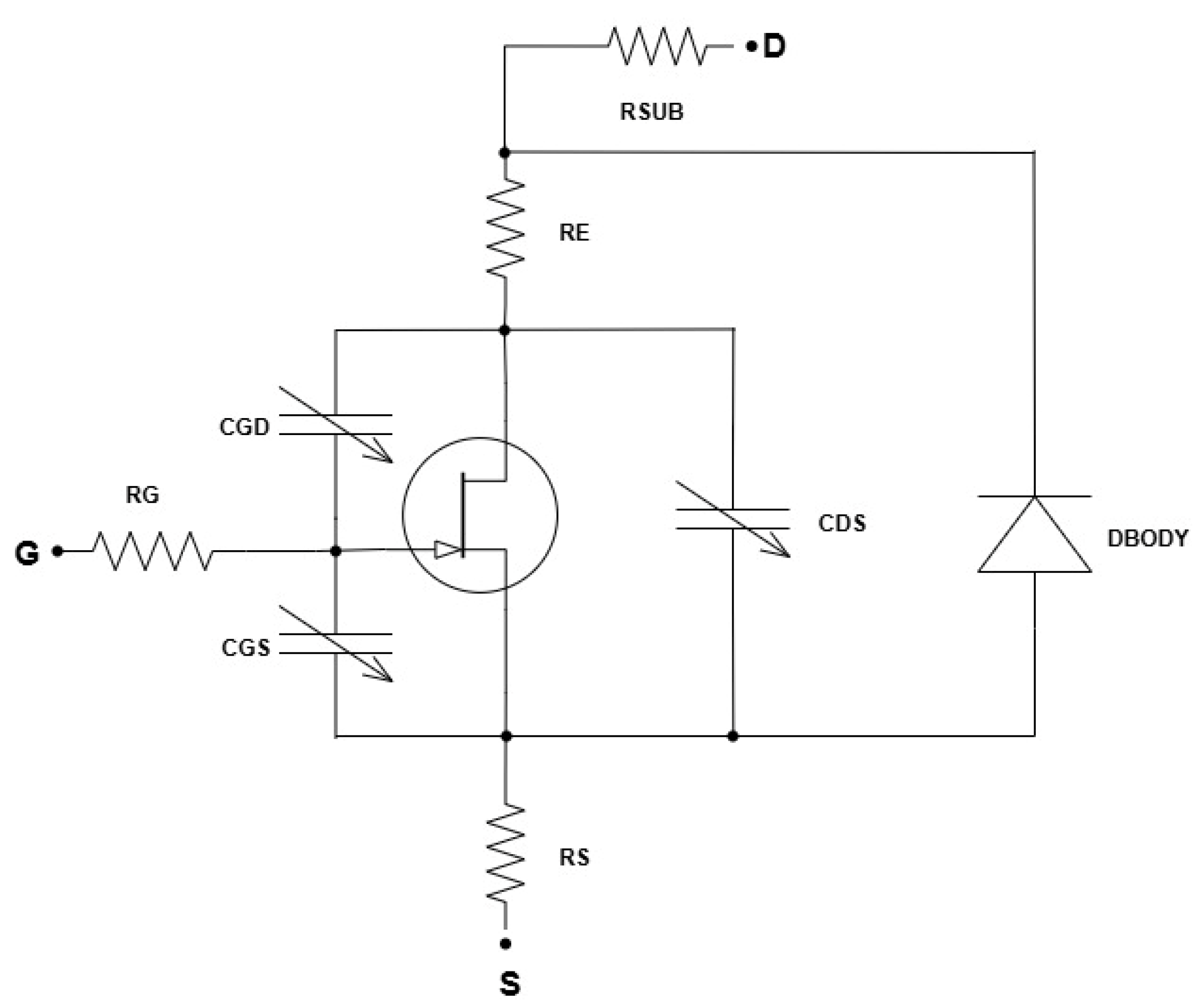

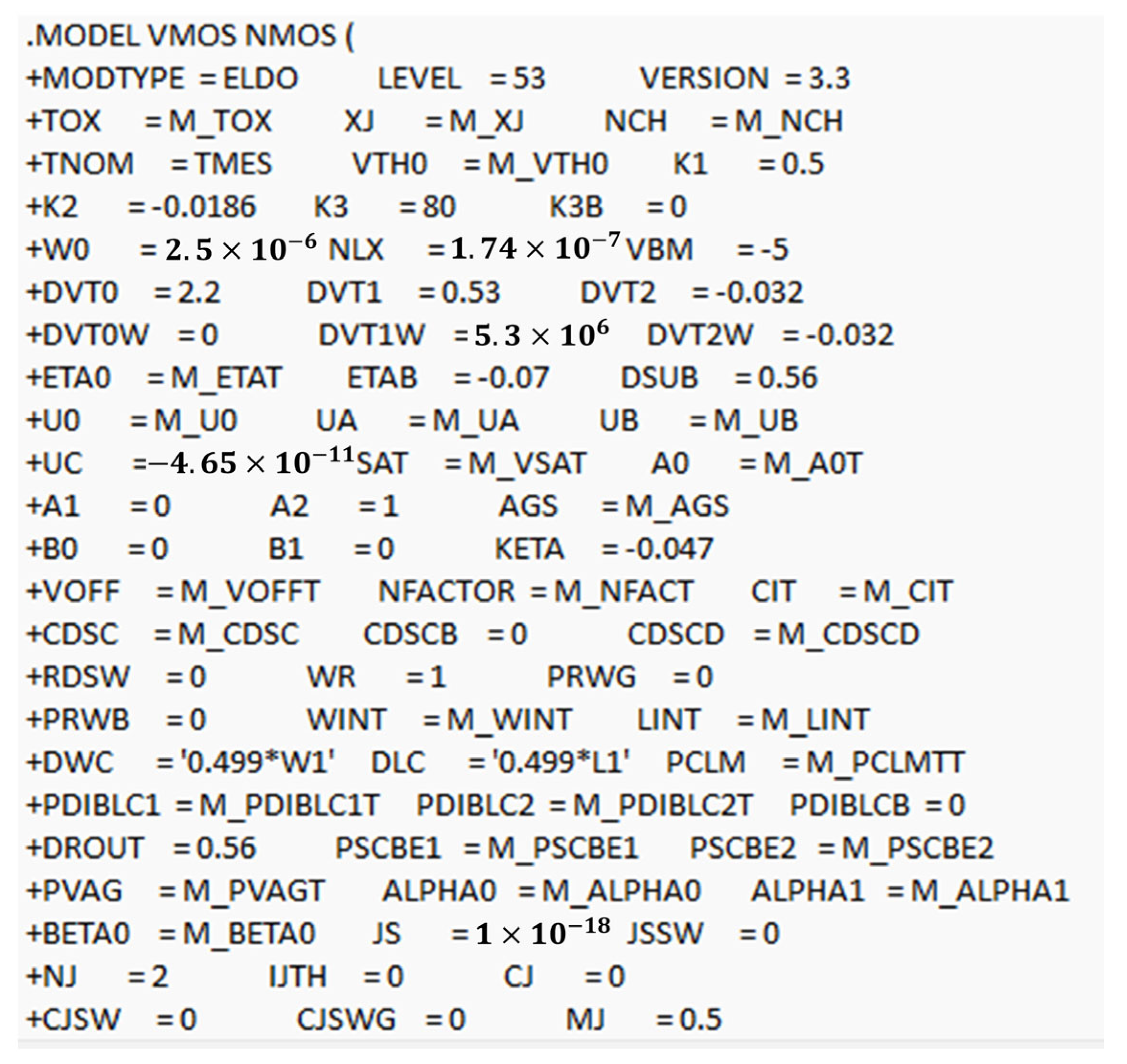

Macromodel Integration

- Gate network:

- RG: resistor representing the gate parasitic resistance.

- CGD, CGS, CDS: capacitors representing the parasitic capacitances between the gate-drain and the gate-source and drain-source.

- Transistor core:

- NMOS: the main MOSFET device modeled using BSIM3 parameters.

- Source and drain networks:

- RE: external source resistance.

- RSUB: parasitic resistances in the drain and substrate.

- DBODY: body diode and its associated resistance.

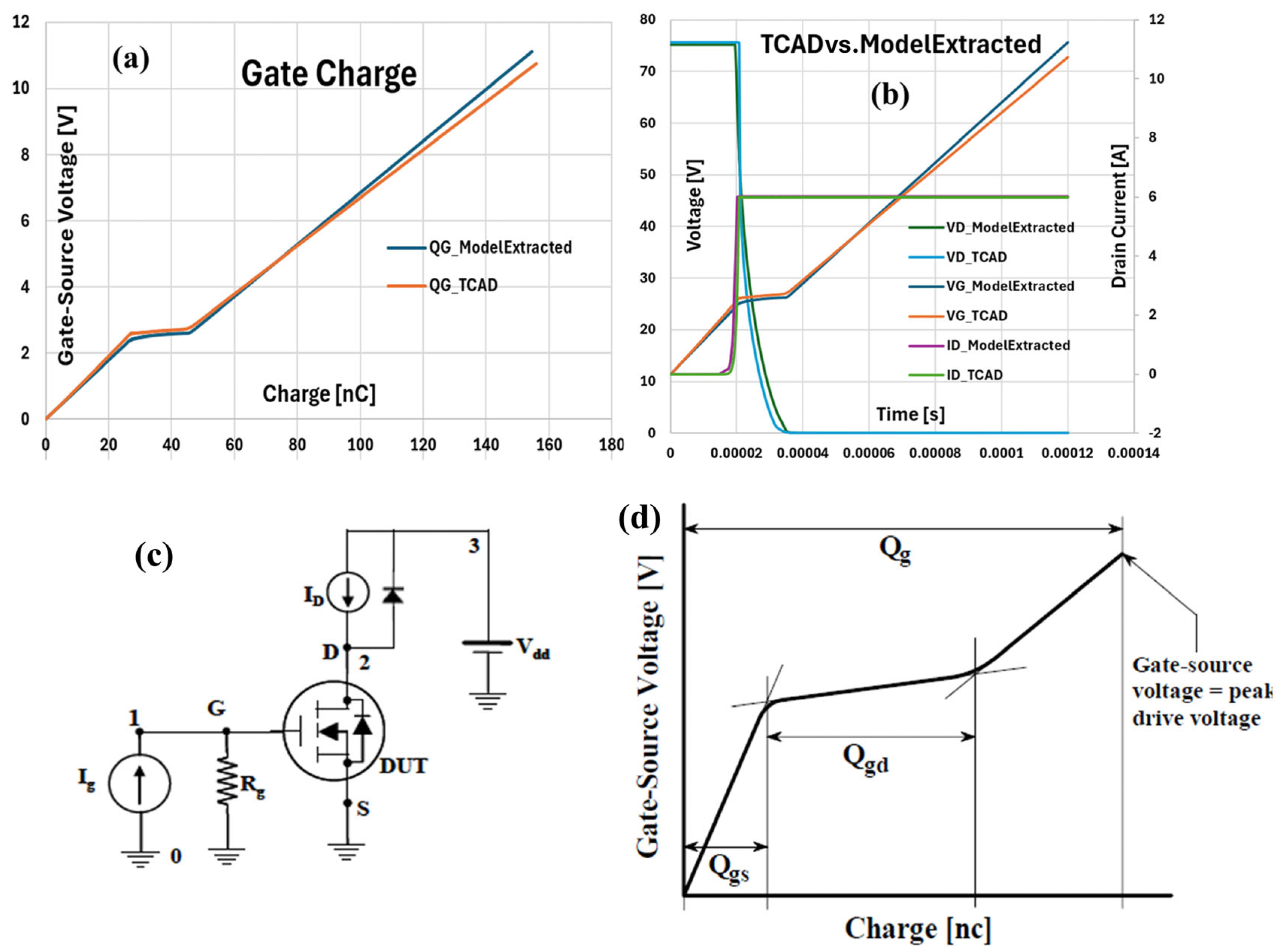

3.2. Gate-Charge Test Simulation and Model Validation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| MOSFET | Silicon metal–oxide–semiconductor field-effect transistors |

| TCAD | Technology computer-aided design |

| DIBL | Drain-induced barrier-lowering |

References

- Ratnesh, R.K.; Goel, A.; Kaushik, G.; Garg, H.; Singh, M.; Prasad, B. Advancement and challenges in MOSFET scaling. Mater. Sci. Semicond. Process 2021, 134, 106002. [Google Scholar] [CrossRef]

- Rafin, S.S.H.; Ahmed, R.; Haque, M.A.; Hossain, M.K.; Mohammed, O.A. Power electronics revolutionized: A comprehensive analysis of emerging wide and ultrawide bandgap devices. Micromachines 2023, 14, 2045. [Google Scholar] [CrossRef]

- Nandan, K.; Agarwal, A.; Bhowmick, S.; Chauhan, Y.S. Two-dimensional semiconductors based field-effect transistors: Review of major milestones and challenges. Front. Electron. 2023, 4, 1277927. [Google Scholar] [CrossRef]

- Das, R.S. A Systematic Literature Review on Advanced FinFET Technology and Beyond: Exploring Novel Transistor Architectures and Assessing their Potential for Future Semiconductor Applications. Eur. J. Adv. Eng. Technol. 2022, 9, 122–130. [Google Scholar]

- Wu, Y. Evolution, Challenges and Applications of Modern MOSFETs. Appl. Comput. Eng. 2023, 24, 294–301. [Google Scholar] [CrossRef]

- Xu, K. Integrated Silicon Directly Modulated Light Source Using p-Well in Standard CMOS Technology. IEEE Sens. J. 2016, 16, 6184–6191. [Google Scholar] [CrossRef]

- Sharafi, F. Review of nano scale MOSFET transistors in high frequency applications. IJCSNS 2017, 17, 215. [Google Scholar]

- Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The trench power MOSFET: Part I—History, technology, and prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Celler, G.K.; Cristoloveanu, S. Frontiers of silicon-on-insulator. J. Appl. Phys. 2017, 93, 4955–4978. [Google Scholar] [CrossRef]

- Chopra, S.; Subramaniam, S. A review on challenges for MOSFET scaling. Int. J. Innov. Sci. 2016, 2, 1055–1057. [Google Scholar]

- Siemieniec, R.; Hutzler, M.; Braz, C.; Naeve, T.; Pree, E.; Hofer, H.; Laforet, D. A new power MOSFET technology achieves a further milestone in efficiency. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hannover, Germany, 5–9 September 2022; pp. 1–11. [Google Scholar]

- Foty, G. Effective MOSFET modeling for SPICE circuit simulation. In Proceedings of the Northcon/98. Conference Proceedings (Cat. No. 98CH36264), Seattle, WA, USA, 21–23 October 1998; pp. 228–235. [Google Scholar]

- Petrosyants, K.O.; Ismail-zade, M.R.; Sambursky, L.M.; Dvornikov, O.V.; Lvov, B.G.; Kharitonov, I.A. Automation of parameter extraction procedure for Si JFET SPICE model in the 200+ 110 °C temperature range. In Proceedings of the 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, Russia, 14–16 March 2018; pp. 1–5. [Google Scholar]

- Dash, T.P.; Das, S.; Dey, S.; Mohapatra, E.; Jena, J.; Maiti, C.K. SPICE parameter extraction of tri-gate FinFETs—An integrated approach. In Proceedings of the 2019 Devices for Integrated Circuit (DevIC), Kalyani, India, 23–24 March 2019; pp. 291–294. [Google Scholar]

- Faruque, M.O.; Strasser, T.; Lauss, G.; Jalili-Marandi, V.; Forsyth, P.; Dufour, C.; Paolone, M. Real-time simulation technologies for power systems design, testing, and analysis. IEEE Power Energy Technol. Syst. J. 2015, 2, 63–73. [Google Scholar] [CrossRef]

- Behrendt, S.; Altenmüller, T.; May, M.C.; Kuhnle, A.; Lanza, G. Real-to-sim: Automatic simulation model generation for a digital twin in semiconductor manufacturing. J. Intell. Manuf. 2025, 1–20. [Google Scholar] [CrossRef]

- MacMillen, D.; Camposano, R.; Hill, D.; Williams, T.W. An industrial view of electronic design automation. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2000, 19, 1428–1448. [Google Scholar] [CrossRef]

- McAndrew, C.C.; Scholten, A.J.; Gullapalli, K.K.; Chauhan, Y.; Xia, K. Benchmarks for SPICE Modeling and Parameter Extraction Based on AI/ML. IEEE Trans. Electron Devices 2025, 72, 1551–1559. [Google Scholar] [CrossRef]

- Liu, X.; Hua, M.; Shafie, S.; Radzi, M.A.; Azis, N. SPICE Modelling-Assisted evaluation of dynamic on-resistance characterization in Schottky p-GaN HEMTs amid synchronous buck transient instabilities. Comput. Electr. Eng. 2024, 118, 109410. [Google Scholar] [CrossRef]

- Maiti, C.K. Introducing Technology Computer-Aided Design (TCAD): Fundamentals, Simulations, and Applications; Jenny Stanford Publishing: Singapore, 2015. [Google Scholar]

- Cheng, Y.; Hu, C. MOSFET Modeling & BSIM3 User’s Guide; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2002. [Google Scholar]

- Raut, P.; Panda, D.K.; Goyal, A.K. A Comprehensive Review on Next-Generation Modeling and Optimization for Semiconductor Devices. IEEE Access 2025, 13, 123724–123742. [Google Scholar] [CrossRef]

- Choi, N.-Y.; Kim, S.-G.; Zhang, S.-U. Enhanced Simulation Accuracy and Design Optimization in Power Semiconductors Through Individual Aluminum Metallization Layer Modeling. Energies 2025, 18, 2457. [Google Scholar] [CrossRef]

- Cai, Z.; Huang, A.; Xiong, Y.; Mu, D.; Miao, X.; Wang, X. Multi-order Differential Neural Network for TCAD Simulation of the Semiconductor Devices. In Proceedings of the 61st ACM/IEEE Design Automation Conference (DAC ‘24), San Francisco, CA, USA, 23–27 June 2024; Association for Computing Machinery: New York, NY, USA, 2024; pp. 1–6, Article 198. [Google Scholar] [CrossRef]

- Thinh, C.; Trang, H. A design TCADAS tool for semiconductor devices and case study of 65 nm conventional floating-gate MOS transistor. Heliyon 2024, 10, e26496. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Wu, Z.; Rzepa, G.; Karner, M.; Xu, H.; Wu, Z.; Wang, W.; Yang, G.; Luo, Q.; Wang, L.; et al. Overview of Emerging Semiconductor Device Model Methodologies: From Device Physics to Machine Learning Engines. Fundam. Res. 2024, in press. [Google Scholar] [CrossRef]

- Dixit, H.; Lichtenwalner, D.J.; Scholze, A.; Kim, J.; Han, K.J.; Ryu, S.H. Revised Channel Mobility Model for Predictive TCAD Simulations of 4H-SiC MOSFETs. Solid State Phenom. 2024, 358, 103–107. [Google Scholar] [CrossRef]

- Lee, J.; Kang, M. TID Circuit Simulation in Nanowire FETs and Nanosheet FETs. Electronics 2021, 10, 956. [Google Scholar] [CrossRef]

- Górecki, P.; d’Alessandro, V. A Datasheet-Driven Electrothermal Averaged Model of a Diode–MOSFET Switch for Fast Simulations of DC–DC Converters. Electronics 2024, 13, 154. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tariq, A.; Minardi, G.; Cinnera Martino, V.; Fazio, E.; Rinaudo, S.; Privitera, G.; Neri, F.; Corsaro, C. Pre-Silicon Accurate SPICE Modeling of Trench MOSFETs via Advanced TCAD Simulations and Dynamic Validation. Micromachines 2025, 16, 955. https://doi.org/10.3390/mi16080955

Tariq A, Minardi G, Cinnera Martino V, Fazio E, Rinaudo S, Privitera G, Neri F, Corsaro C. Pre-Silicon Accurate SPICE Modeling of Trench MOSFETs via Advanced TCAD Simulations and Dynamic Validation. Micromachines. 2025; 16(8):955. https://doi.org/10.3390/mi16080955

Chicago/Turabian StyleTariq, Ammar, Giovanni Minardi, Valeria Cinnera Martino, Enza Fazio, Salvatore Rinaudo, Giuseppe Privitera, Fortunato Neri, and Carmelo Corsaro. 2025. "Pre-Silicon Accurate SPICE Modeling of Trench MOSFETs via Advanced TCAD Simulations and Dynamic Validation" Micromachines 16, no. 8: 955. https://doi.org/10.3390/mi16080955

APA StyleTariq, A., Minardi, G., Cinnera Martino, V., Fazio, E., Rinaudo, S., Privitera, G., Neri, F., & Corsaro, C. (2025). Pre-Silicon Accurate SPICE Modeling of Trench MOSFETs via Advanced TCAD Simulations and Dynamic Validation. Micromachines, 16(8), 955. https://doi.org/10.3390/mi16080955