Design of a Dual-Band Low-Noise Amplifier with a Novel Matching Structure

Abstract

1. Introduction

2. Design Theory and Analysis

- First of all, the IDBT proposed for adoption in this paper will be introduced as a whole.

- Secondly, the relevant theory of parallel-coupled lines will be introduced to theoretically prove the feasibility of the design.

- Thirdly, the calculation method of the two-section series microstrip lines in Part II will be introduced.

- Finally, the implementation method of low NF in the DB-LNA will be analyzed.

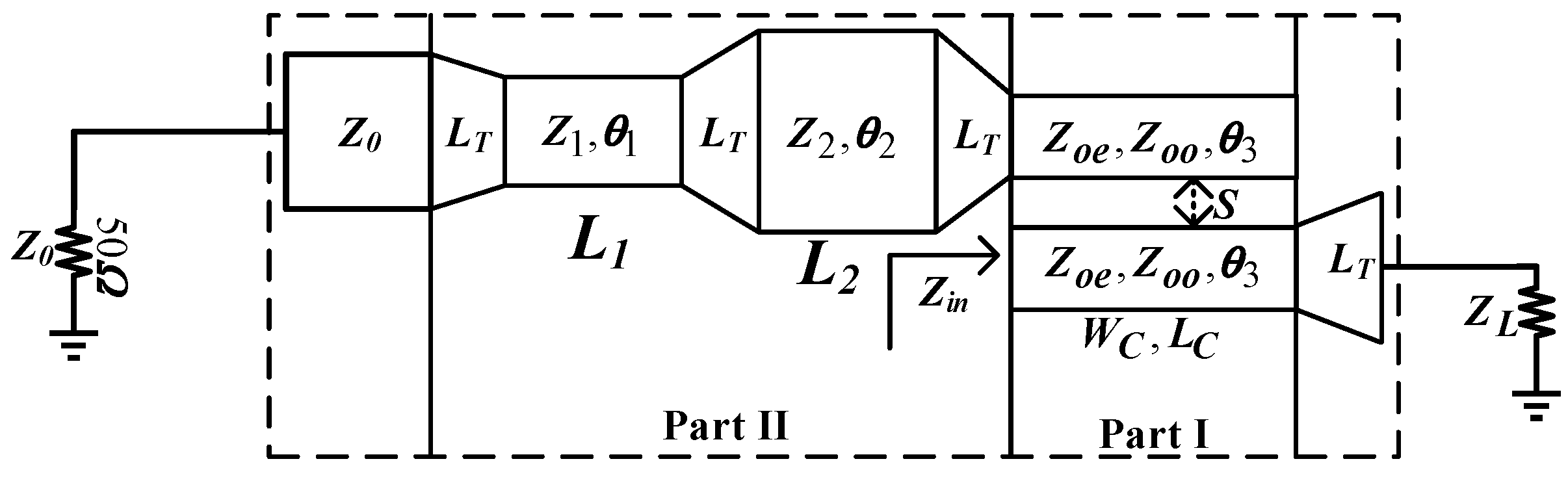

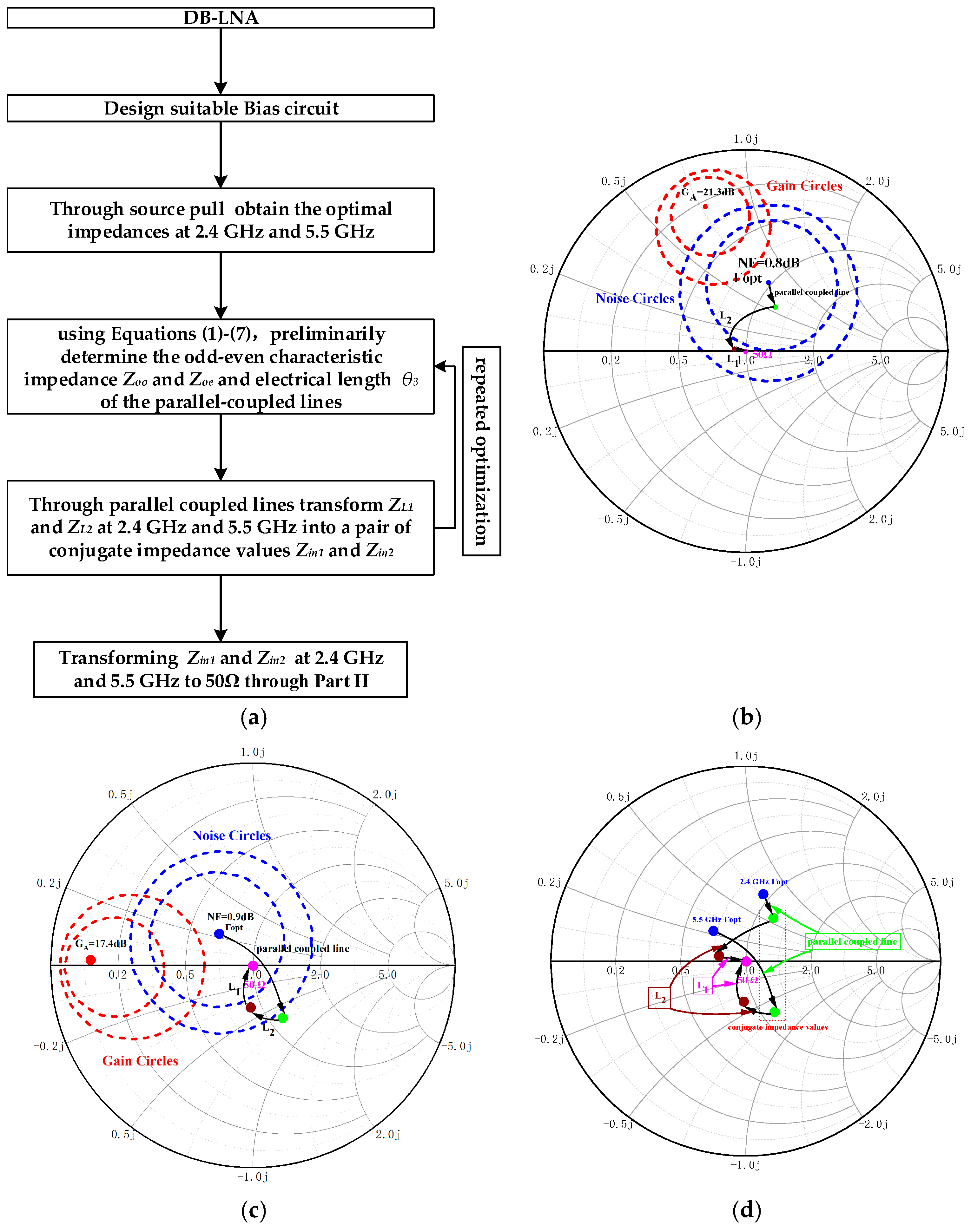

2.1. Complex IDBT

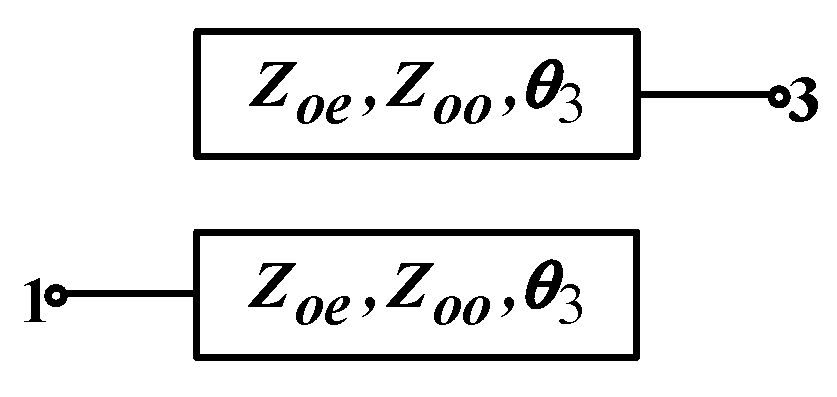

2.2. Parallel-Coupled Line Theory

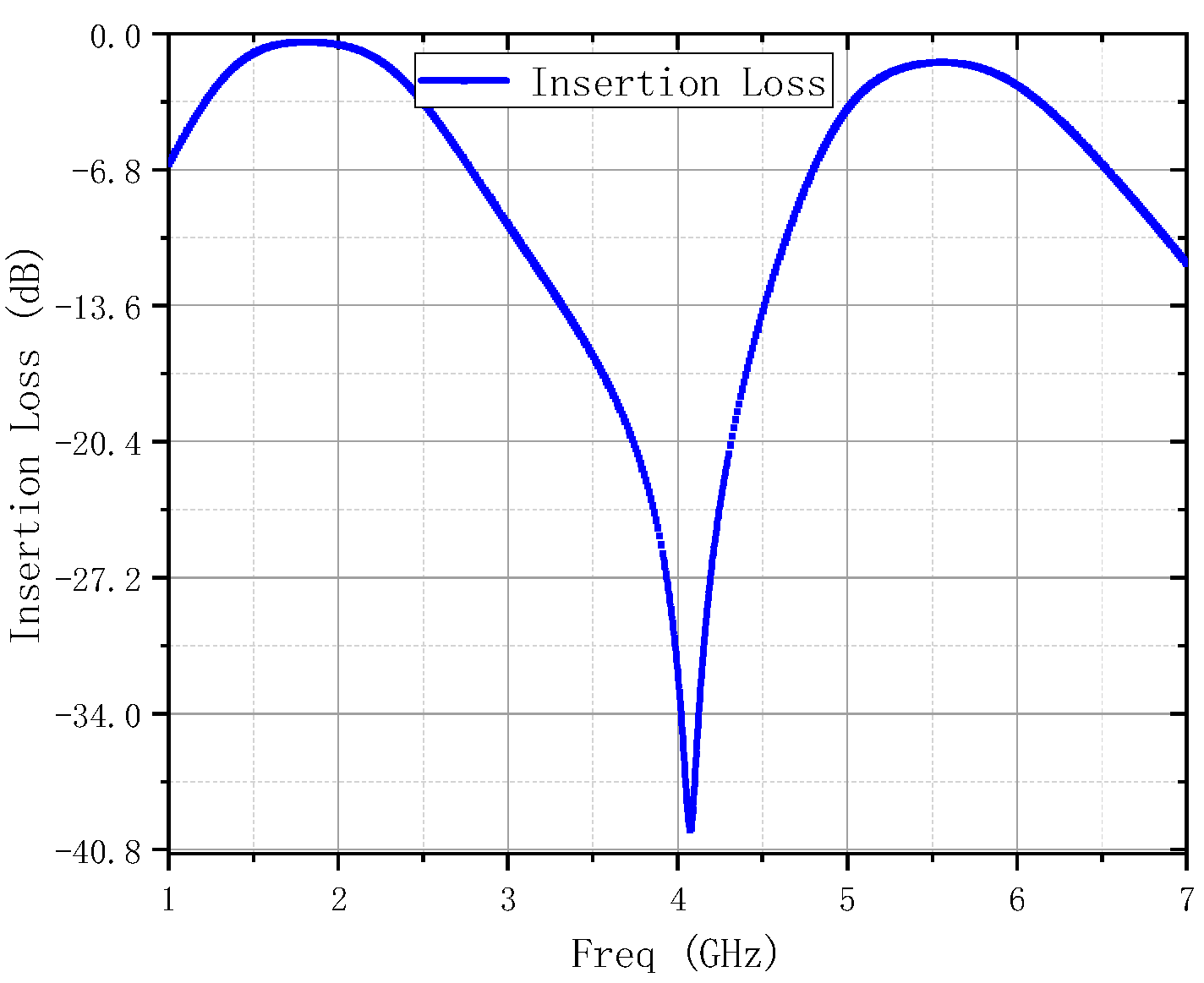

2.3. Design of Two-Section Microstrip Transmission Lines in Part II

2.4. Implementation of Low NF in the DB-LNA

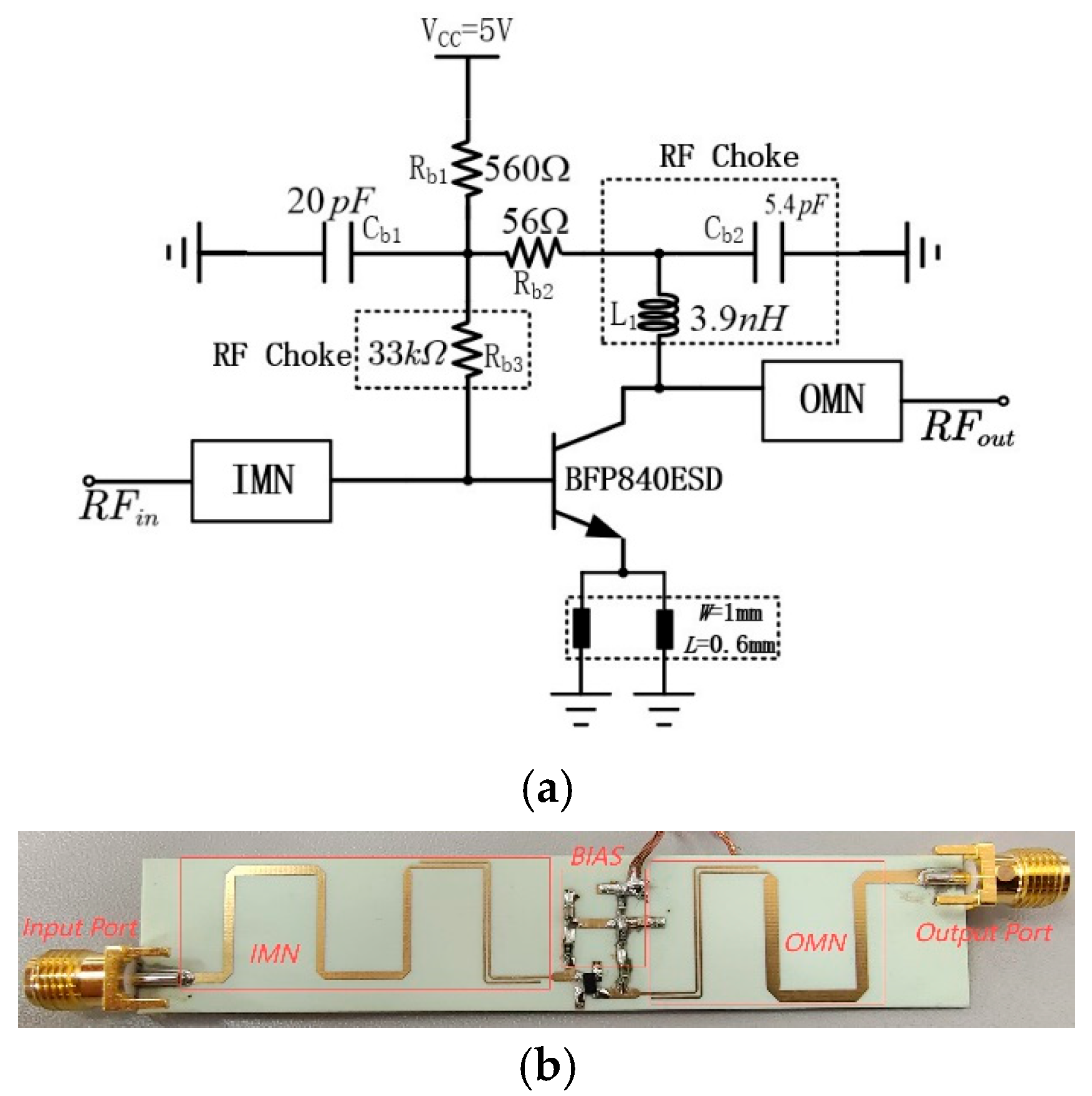

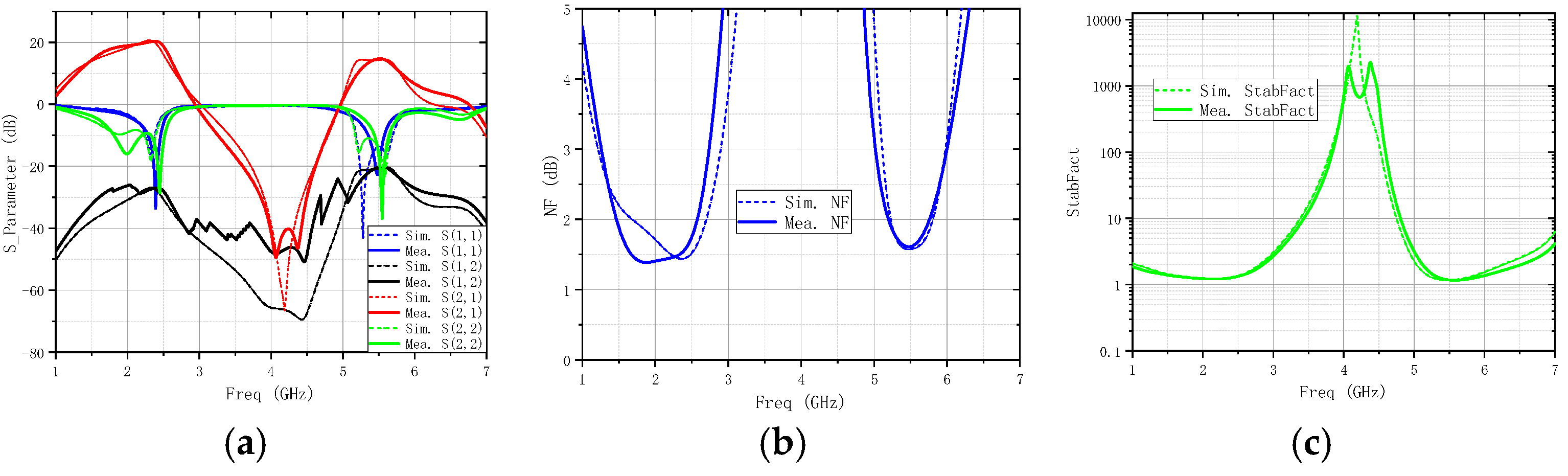

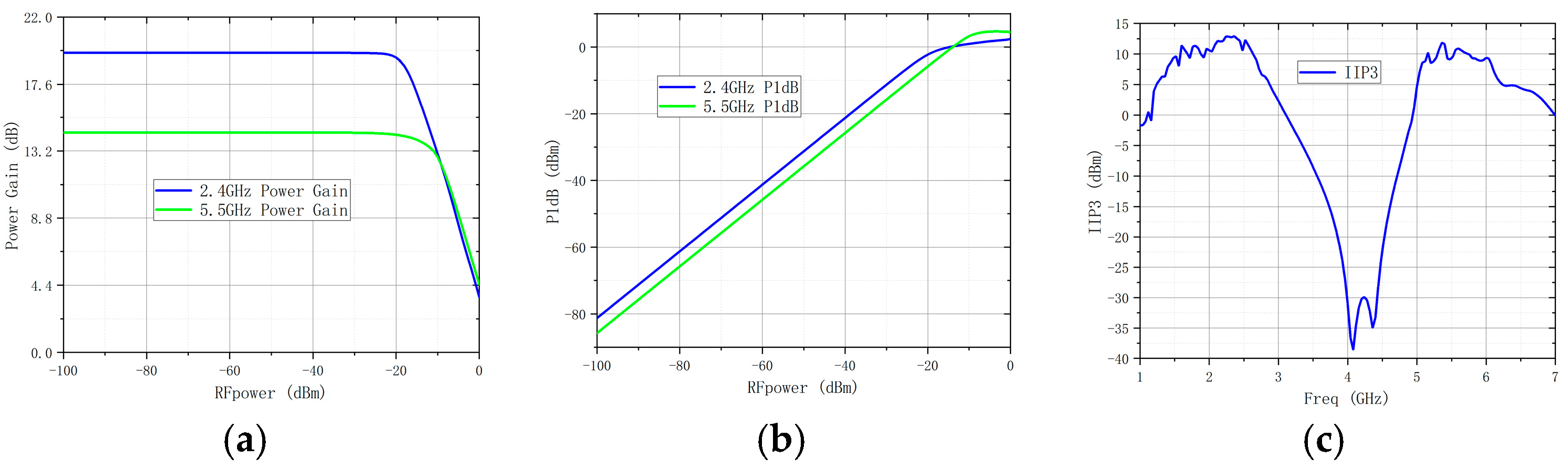

3. Implementation and Measurement

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Schmidt, A.; Catala, S. A Universal Dual Band LNA Implementation in SiGe Technology for Wireless Applications. IEEE J. Solid-State Circuits 2001, 36, 1127–1131. [Google Scholar] [CrossRef]

- Yu, X.; Neihart, N.M. Analysis and Design of a Reconfigurable Multimode Low-Noise Amplifier Utilizing a Multitap Transformer. IEEE Trans. Micro-Wave Theory Tech. 2013, 61, 1236–1246. [Google Scholar] [CrossRef]

- Hu, R. An 8–20-GHz Wide-Band LNA Design and the Analysis of Its Input Matching Mechanism. IEEE Microw. Wirel. Compon. Lett. 2004, 14, 528–530. [Google Scholar] [CrossRef]

- Ahmad, A.; Othman, A.R.; Hamidon, A.H.; Pongot, K. A Low Noise Dual-Band Cascaded LNA with Notch Filtering Network for IEEE 802.11b/g/a/n Wireless Applications. ARPN J. Eng. Appl. Sci. 2016, 11, 3407–3412. [Google Scholar]

- Hsiao, Y.-C.; Meng, C.; Yang, C. Design Optimization of Single-/Dual-Band FET LNAs Using Noise Transformation Matrix. IEEE Trans. Micro-Wave Theory Tech. 2016, 64, 519–532. [Google Scholar] [CrossRef]

- Djoumessi, E.E.; Wu, K. Dual-Band Low-Noise Amplifier Using Step-Impedance Resonator (SIR) Technique for Wireless System Applications. In Proceedings of the 39th European Microwave Conference, Rome, Italy, 29 September–1 October 2009; pp. 1307–1310. [Google Scholar]

- Kumar, A.; Pathak, N.P. Reconfigurable Concurrent Dual-Band Low Noise Amplifier for Non-invasive Vital Sign Detection Applications. In Proceedings of the 2014 International Conference on Advances in Computing, Communications and Informatics, Delhi, India, 24–27 September 2014; pp. 2496–2500. [Google Scholar]

- Iyer, B.; Pathak, N.P. A Concurrent Dual-Band LNA for Noninvasive Vital Sign Detection System. Microw. Opt. Technol. Lett. 2014, 56, 391–394. [Google Scholar] [CrossRef]

- Kumar, A.; Pathak, N.P. Coupled Stepped-Impedance Resonator (CSIR) Based Concurrent Dual Band Filtering LNA for Wireless Applications. In Proceedings of the 2015 IEEE MTT-S International Microwave and RF Conference (IMaRC), Hyderabad, India, 10–12 December 2015; pp. 262–265. [Google Scholar]

- Lee, J.; Nguyen, C. A K-/Ka band Concurrent Dual-Band Low-Noise Amplifier Employing a Feedback Notch Technique with Simultaneous Passband Gain and Stopband Rejection Control. Microw. Opt. Technol. Lett. 2018, 60, 1429–1435. [Google Scholar] [CrossRef]

- Gupta, M.P.; Kumar, S.; Caroline, B.E.; Song, H.; Kumar, V.; Gorre, P. A 0.15 μm GaN HEMT Device to Circuit Approach Towards Dual-Band Ultra-Low Noise Amplifier Using Defected Ground Bias Technique. Int. J. Electron. Commun. 2023, 168, 154742. [Google Scholar] [CrossRef]

- Nikravan, M.A.; Atlasbaf, Z. T-Section Dual-Band Impedance Transformer for Frequency-Dependent Complex Impedance Loads. Electron. Lett. 2011, 47, 1645–1646. [Google Scholar] [CrossRef]

- Manoochehri, O.; Asoodeh, A.; Forooraghi, K. II-Model Dual-Band Impedance Transformer for Unequal Complex Impedance Loads. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 238–240. [Google Scholar] [CrossRef]

- Zheng, X.; Liu, Y.; Li, S.; Yu, C.; Wang, Z.; Li, J. A Dual-Band Impedance Transformer Using PI-Section Structure for Frequency-Dependent Complex Loads. Prog. Electromagn. Res. 2012, 32, 11–26. [Google Scholar] [CrossRef]

- Chuang, M.-L. Analytical Design of Dual-Band Impedance Transformer with Additional Transmission Zero. IET Microw. Antennas Propag. 2014, 8, 1120–1126. [Google Scholar] [CrossRef]

- Chen, M.-G.; Hou, T.-B.; Tang, C.-W. Design of Planar Complex Impedance Transformers with the Modified Coupled Line. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1704–1710. [Google Scholar] [CrossRef]

- Fang, S.J.; Jia, X. Design of Compact Coupled-Line Complex Impedance Transformers with the Series Susceptance Component. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2482–2486. [Google Scholar] [CrossRef]

- Guo, Y.Q.; Liu, H.M. Modification of Susceptance Component Loaded Coupled Line Complex Impedance Transformer. In Proceedings of the 2020 Cross Strait Radio Science & Wireless Technology Conference (CSRSWTC), Fuzhou, China, 13–16 December 2020; pp. 1–3. [Google Scholar]

- Wu, Y.; Sun, W.; Leung, S.-W.; Diao, Y.; Chan, K.-H. A Novel Compact Dual-Frequency Coupled-Line Transformer with Simple Analytical Design Equations for Frequency-Dependent Complex Load Impedance. Prog. Electromagn. Res. 2013, 134, 47–62. [Google Scholar] [CrossRef]

| Ref. | Frequency (GHz) | S11 (dB) | S22 (dB) | S21 (dB) | NF (dB) | Size (mm2) | Power (mW) | Technology |

|---|---|---|---|---|---|---|---|---|

| [4] | 2.4 | −11.3 | −24.6 | 33.84 | 0.946 | - | - | GaAs MMIC |

| 5.75 | −17.4 | −11.1 | 20 | 0.493 | ||||

| [5] | 2.4 | −10 | −8 | 20 | 2.2 | 1.5 × 1 | 37.8 | GaAs MMIC |

| 5 | −7 | −6 | 15 | 2.0 | ||||

| [6] | 2.45 | −20 | - | 22 | 1.5 | 30 × 30 | 7.5 | HMIC |

| 5.2 | −21 | - | 12 | 1.6 | ||||

| [7] | 2.3–2.5 | −8.5 | - | 3–12.2 | 0.5–5 | 55 × 60 | 41.25 | HMIC |

| 4.2–4.6 | −15 | - | 9.5–12.9 | 2.5–5 | ||||

| [8] | 2.44 | −10.5 | - | 7.15 | 4.34 | - | 35.1 | HMIC |

| 5.25 | −15.9 | - | 7.8 | 4.69 | ||||

| [9] | 2.4 | −25 | - | 11.6 | 3.96 | 120 × 34 | 56 | HMIC |

| 5.7 | −12 | - | 8.9 | 2.89 | ||||

| This Work | 2.33–2.46 | −29.8 | −15.2 | 20.3 | 1.6 | 16 × 85 | 39.3 | HMIC |

| 5.43–5.58 | −20.3 | −16.4 | 14.7 | 1.6 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Cheng, Z.; Gong, T.; Zheng, B.; Zhang, Z.; Xuan, X. Design of a Dual-Band Low-Noise Amplifier with a Novel Matching Structure. Micromachines 2025, 16, 938. https://doi.org/10.3390/mi16080938

Zhang M, Cheng Z, Gong T, Zheng B, Zhang Z, Xuan X. Design of a Dual-Band Low-Noise Amplifier with a Novel Matching Structure. Micromachines. 2025; 16(8):938. https://doi.org/10.3390/mi16080938

Chicago/Turabian StyleZhang, Mingwen, Zhiqun Cheng, Tingwei Gong, Bangjie Zheng, Zhiwei Zhang, and Xuefei Xuan. 2025. "Design of a Dual-Band Low-Noise Amplifier with a Novel Matching Structure" Micromachines 16, no. 8: 938. https://doi.org/10.3390/mi16080938

APA StyleZhang, M., Cheng, Z., Gong, T., Zheng, B., Zhang, Z., & Xuan, X. (2025). Design of a Dual-Band Low-Noise Amplifier with a Novel Matching Structure. Micromachines, 16(8), 938. https://doi.org/10.3390/mi16080938