Abstract

This paper introduces a 0.5–5.8 GHz low-noise amplifier (LNA) incorporating a gyrator-C-based active inductor (AI) and an enhanced deep trench isolation (DTI) electrostatic discharge (ESD) diode. Results suggest that AIs exhibit excellent consistency under various process voltage temperatures (PVTs) as well as input powers and the improved DTI diodes reduce parasitic capacitance by an average of 8.5% compared to conventional ones. In terms of circuit design, comprehensive analyses of gain flatness and noise are conducted. Fabricated using a 0.18 μm SiGe BiCMOS technology, the LNA delivers a high S21 of 18.3 ± 0.3 dB, a minimum noise figure of 2.6 dB, and an S11 and S22 of less than −10 dB over the entire frequency band. Operating from a 3.3 V supply voltage with a core area of 0.049 mm2, it consumes 10 mA of current.

1. Introduction

With the diversified development of wireless communication standards, the demand for multi-band compatibility in radio frequency (RF) front-end systems has become increasingly prominent [1]. Traditional multi-band reception schemes employing discrete low-noise amplifier (LNA) designs result in proportional increases in chip area and static power consumption [2,3]. Hence, compared with the discrete component scheme, chip integration technology achieves performance improvement and cost optimization of RF systems through a monolithic architecture.

The wideband LNA, as the core front-end component of ultra-wideband wireless receiver systems, must address design challenges including broadband impedance matching and noise-linearity trade-offs. Typical implementations employ cascode configurations and distributed amplification architectures, achieving bandwidth extension through active inductors and zero-pole compensation techniques [4,5]. However, parasitic CESD and RESD due to the structure of electrostatic discharge (ESD) protection devices can significantly disrupt the balance between these performances. Therefore, there is a significant necessity for a low parasitic ESD protection device to assist with the LNA design.

Inductors are critical components in Radio Frequency (RF) circuits, such as Inductor Capacitor Tank-Voltage Controlled Oscillators (LC-VCOs), LNAs, and filters. However, as the feature size keeps decreasing, spiral inductors no longer meet the trend towards being miniaturized and low-cost. Meanwhile, its inherent electromagnetic interference has become another major challenge for complex systems. Active inductors (AIs) have been intensively studied for their high quality as well as compact area in several recent works [6,7,8]. However, to increase the tunability of the AI, these jobs design the control bits off the chip. This complicates the external control scheme. To overcome this limitation, we propose an envelope detector along with an adaptive bias circuit to achieve on-chip control of the AI. In the following work, the AI is applied to the design of an ultra-wideband LNA.

2. Circuit Analysis

2.1. Active Inductor Design

The shunt resistor feedback topology achieves broadband matching through resistive feedback, demonstrating superior performance advantages over other broadband structures in the 0.5–5.8 GHz frequency range. Although this structure reduces circuit gain due to feedback and introduces thermal noise from the feedback resistor, its broadband matching capability makes it the final choice. In comparison, the bandpass filter-based topology, while achieving broadband matching by incorporating a bandpass filter, requires a large chip area for its input passive filter network. Additionally, the parasitic resistance of low-Q on-chip inductors degrades noise performance. The common-gate structure, despite its good linearity, low power consumption, and process voltage temperature (PVT) stability, suffers from poor noise performance. Even with transconductance enhancement techniques for optimization, it still cannot match the overall performance of the shunt resistor feedback topology in the 0.5–5.8 GHz range. Therefore, after comprehensively considering broadband matching, noise, and gain trade-offs, the shunt resistor feedback topology is ultimately selected as the implementation scheme for this design.

In the design of broadband low-noise amplifiers, traditional passive inductors struggle to achieve good impedance matching across wide frequency ranges due to their fixed inductance characteristics. The adaptive-biased active inductor employed in this study effectively addresses this issue through a dynamic tuning mechanism. By real-time adjustment of bias conditions, this structure enables the equivalent inductance to adaptively vary with frequency: providing higher equivalent inductance at low frequencies to improve input matching, while automatically reducing inductance at high frequencies to suppress parasitic effects. Therefore, the adaptive-biased inductor effectively extends the bandwidth of shunt-feedback broadband low-noise amplifiers.

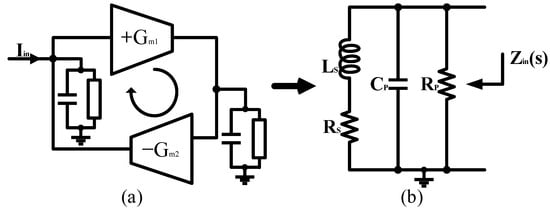

Depending on the state of the art, AIs can be configured in three ways: (1) amplifiers; (2) current conveyors; (3) gyrators [9,10,11]. The third family shows superiority in tunability, power consumption, frequency range, and circuit area. Figure 1a illustrates the gyrator–C structure. A gyrator-C consists of a positive trans-conductor and a negative trans-conductor connected head to tail. Considering the parasitics in the circuit, the gyrator-C-based AIs can be equated to the lossy model in Figure 1b. Figure 2 proposes the schematic diagram of the adopted gyrator-C based-Grounded AI. In this design, Q1 and Q2 form a cascode structure to provide high-output impedance and are used as a negative trans-conductance unit while the common-collector transistor Q3 is used as positive trans-conductance unit. MOSFETs M4 and M5 act as current sources to provide bias currents to the positive and negative trans-conductance unit, respectively. Resistor R1 biases Q3 on the feedback loop and increases the inductance of the Grounded AI. From the AC small-signal equivalent model, the port impedance can be reported as

where , are the equivalent capacitance between the base and emitter, gmx (x = 1,2,3…) is the trans-conductance, (x = 1,2,3…) is the input impedance, and rox (x = 1,2,3…) is the output impedance. The expression for inductance (L), series resistor (Rs), parallel resistor (Rp) and parallel capacitor (Cp) in Figure 1b can be obtained from (1) as

Figure 1.

(a) The gyrator–C structure. (b) The lossy equivalent model for gyrator-C-based AI.

Figure 2.

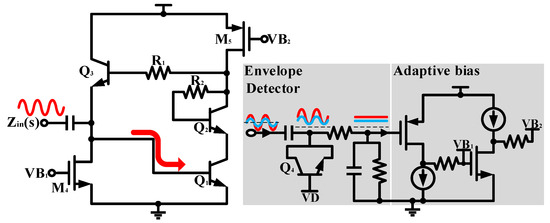

Schematic of the proposed active inductor and adaptive biasing circuit.

However, the instability of the AI at different PVT as well as input power raises risks for the circuit. The equivalent inductance (Leq) and quality factor (Q) of AIs are inherently dependent on transistor parameters such as transconductance and output impedance. PVT variations can cause significant drift in these parameters. Implementing adaptive biasing through dynamic adjustment of bias voltages/currents effectively compensates for PVT-induced variations, thereby maintaining AI stability. Furthermore, when handling large signals, the core transistors in AIs may enter nonlinear regions (cutoff or saturation), causing Leq to vary with signal amplitude and introducing harmonic distortion. Adaptive Class-AB biasing that dynamically adjusts operating points based on input signal magnitude ensures transistors remain in their quasi-linear region, preserving AI linearity.

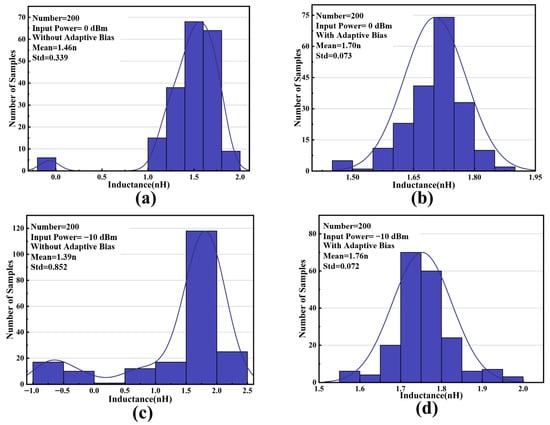

Therefore, we use an envelope detector and an adaptive biasing circuit to achieve on-chip self-bias of the non-tunable AI. The different power input signals will be shaped into varying DC voltage levels through the envelope detector. Then, the adaptive bias circuit provides a dynamic static operating point for the AI to maintain its linearity. The base bias VD of diode-connected transistor Q4 is connected to a current mirror bias circuit to ensure full PVT coverage. Monte Carlo simulation results of the AI with and without the adaptive bias circuit at different input power are given in Figure 3. Obviously, the consistency of AIs is dramatically improved.

Figure 3.

Monte Carlo simulation results for AI without adaptive bias under (a) 0 dBm and (c) −10 dBm and with adaptive bias under (b) 0 dBm and (d) −10 dBm.

2.2. ESD Protection Devices

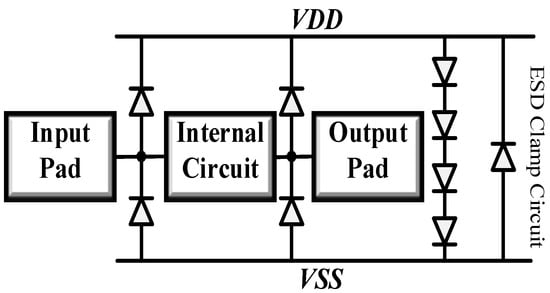

Figure 4 shows the ESD protection circuit schematic diagram. ESD diodes are widely employed in chip IO protection because of their simple structure. Nevertheless, there is a positive correlation between the robustness of the device and its parasitics. Specifically, a device with high robustness tends to generate more parasitics, while a device with fewer parasitics usually has lower robustness, as reported in references [12,13]. This issue poses a significant challenge for Radio Frequency Integrated Circuits (RFICs).

Figure 4.

ESD protection circuit schematic diagram.

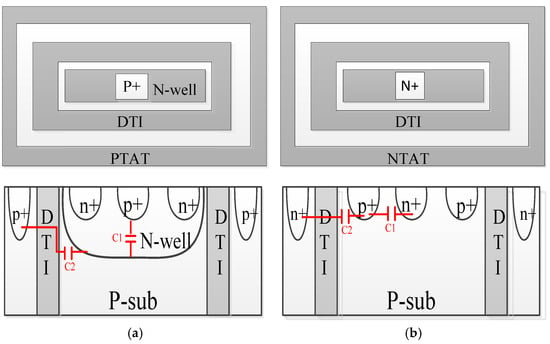

The schematic diagrams of the P+/nwell DTI diode and N+/psub DTI diode with the DTI structure are shown in Figure 5. The parasitic capacitance of each ESD diode includes the capacitance associated with the metal interconnect, the intrinsic capacitance from the ESD diode, and the parasitic pad capacitance [14,15,16]. This paper discusses only intrinsic capacitance. Take the P+/N-well diode (Dp) as an example. Parasitic capacitance consists of the capacitance C1 caused by the P+ diffusion/N-well junction and the capacitance C2 caused by the N-well/P+ guard ring junction. These capacitances can be considered as the barrier capacitance CT caused by the contact barriers between the P-type and N-type regions of the diode, which can be given by

where Aeff is the effective area of the PN junction, VD is the built-in potential. CTA0(0) represents the junction capacitance per unit area under zero bias conditions, which can be represented as

Figure 5.

(a) P+/nwell DTI diode and (b) N+/psub DTI diode with DTI structure.

This study effectively suppresses parasitic capacitance. The optimized design constructs a novel diode topology through Deep Trench Isolation (DTI) technology.

The deep trench isolation (DTI) structure penetrates beneath the N-well/P-substrate junction interface, employing oxide fillers with a reduced dielectric constant compared to silicon. This configuration significantly minimizes lateral capacitance at the N-well/P-substrate boundary through dielectric isolation. While maintaining the fundamental interdigitated electrode arrangement of standard diodes, the DTI-enhanced design achieves superior RF characteristics through improved electrical isolation and capacitive decoupling.

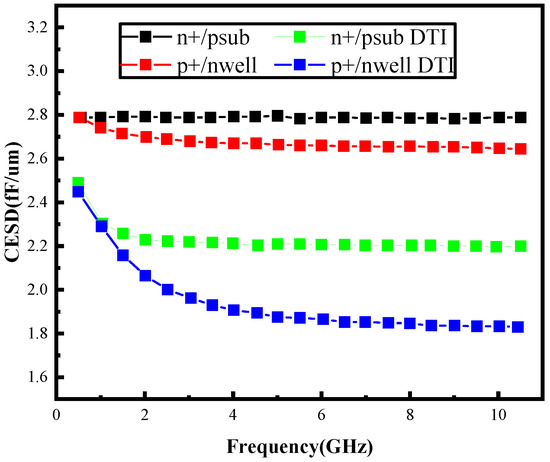

To quantitatively evaluate this enhancement, four diode configurations were analyzed through Silvaco TCAD (Silvaco Inc., Santa Clara, CA, USA, https://silvaco.com/tcad/) simulations under identical dimensional parameters for comparative capacitance assessment. Figure 6 demonstrates a notable 8.5% average reduction in parasitic capacitance for DTI-incorporated ESD protection devices relative to conventional counterparts. This performance improvement primarily stems from the trench isolation’s effectiveness in suppressing stray capacitance between active components and peripheral guard ring structures. The experimental data confirms DTI technology’s capability to optimize high-frequency circuit performance while maintaining essential ESD protection functionality.

Figure 6.

Simulation curve of parasitic capacitance.

When optimizing the trade-off between parasitic capacitance and ESD protection capability, simulation results indicate that the maximum failure current of the DTI diode used in this design is 0.23 A/μm. Under the JEDEC (JEDEC Solid State Technology Association, Arlington, VA, USA) 2 kV HBM standard, the peak current reaches 1.35 A. Therefore, a minimum diode length of 5.87 μm is required to meet the 2 kV HBM ESD protection requirement. While increasing the ESD diode area can further enhance ESD robustness, it also introduces additional parasitic capacitance, which degrades circuit performance. Thus, a trade-off must be made between ESD protection capability and parasitic effects. Ultimately, this design adopts a 7 μm length, providing sufficient ESD protection margin while avoiding excessive parasitic capacitance.

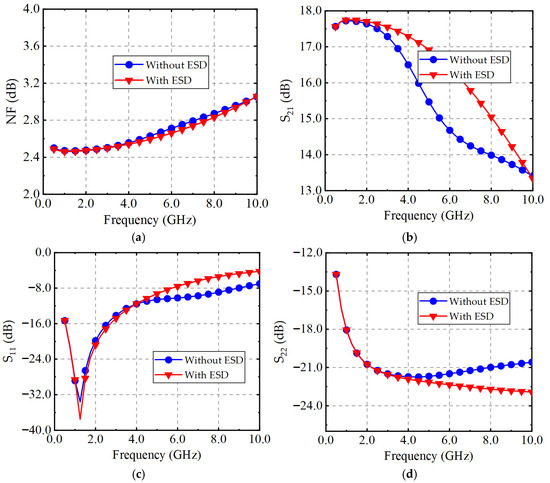

To evaluate the impact of the ESD protection circuit on LNA performance, simulations were conducted for LNA circuits with and without ESD. The simulation results are shown in Figure 7. Figure 7a,b present the simulation results for S11 and S22. The results indicate that the input and output matching of the overall circuit changes after integrating ESD devices. This is because the introduced diodes introduce parasitic capacitance, which acts in parallel with the input and output of the circuit, causing a shift in S11 and S22. To mitigate this shift, the parasitic capacitance should be reduced without compromising the ESD protection performance. Figure 7c shows the S21 simulation results. It can be observed that, since the matching design accounts for the influence of ESD, the LNA with ESD exhibits an advantage in gain, with a slower gain degradation at higher frequencies. However, at frequencies above 10 GHz, the gain of the LNA without ESD may exceed that of the proposed ESD-integrated LNA. This is due to the parasitic capacitance shifting the pole frequency downward, leading to a gain roll-off in the proposed LNA. Figure 7d displays the NF simulation results. After adding ESD protection devices, the noise figure of the circuit remains almost unchanged. Although the parasitic resistance of the diodes in the ESD protection circuit slightly degrades NFmin, the ESD-integrated LNA achieves a lower NF due to adjustments in the input and output matching networks.

Figure 7.

Simulation of (a) NF, (b) S21, (c) S11 and (d) NF for LNA with/without ESD protection circuit.

Since this design has not been fabricated yet, we acknowledge that actual silicon measurements for ESD performance (HBM 1 kV/2 kV or CDM 1 kV) are not available at this stage. Instead, we have estimated the ESD robustness based on the well-characterized protection levels of the original PDK ESD structures.

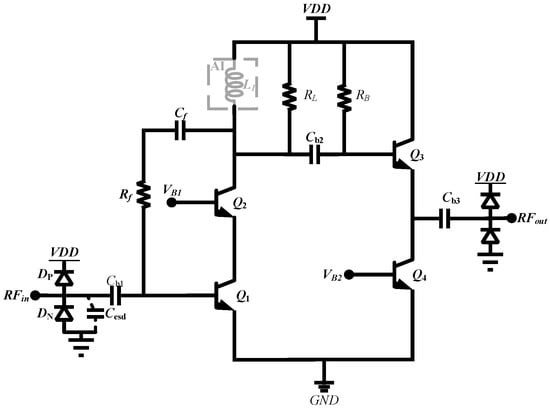

3. Circuit Design

Figure 8 shows the schematic diagram of the presented inductor-less wideband LNA. The load resistor RL, inductor L1 and the feedback resistor Rf extend the amplifier’s bandwidth. The transistors Q1 and Q2 provide sufficiently gain for the circuit, and Q3 and Q4 offer suitable output impedance. The capacitor CESD shows the parasitic capacitance of the ESD diodes, and Cb1 is the blocking capacitor for coupling the RF signal to the base of Q1. Dp and N+/P-sub diode (Dn) are DTI diodes that provide a current discharge path for the circuit when ESD event occurs.

Figure 8.

Schematic of the broadband cascode LNA with active inductor and low capacitive ESD protection.

The electrostatic discharge (ESD) protection structure incorporates a cascode amplifier configuration to achieve optimal LNA performance while preserving enhanced ESD robustness. This design implementation employs DTI Dp and DTI Dn components featuring octagonal finger arrangements (8 fingers), with physical dimensions standardized at 31 mm × 16 mm. The respective parasitic capacitance measurements for these components are quantified as 62 fF and 78 fF, demonstrating controlled capacitive characteristics essential for high-frequency operation.

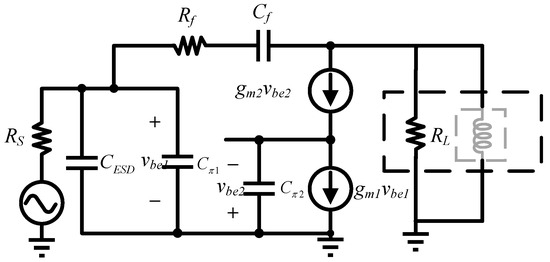

A parallel resistive feedback network is implemented from Q2’s collector to Q1’s base to establish appropriate real impedance characteristics across broad frequency spectra. The analysis presented in Figure 9’s simplified small-signal model comprehensively evaluates input impedance behavior through circuit equivalent derivation; in particular, considering parasitic capacitance effects originating from ESD protection diodes and BJT device physics, the detailed input impedance can be derived as

Figure 9.

Schematic of the broadband cascode LNA with shunt resistive feedback.

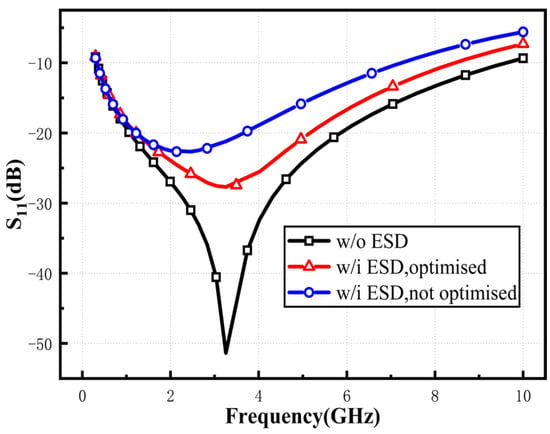

Mismatch due to capacitance at high frequencies requires reducing the ratio of (Rf + ZL)/(1 + gm1ZL) to satisfy constant impedance. Since gm1 and ZL are set for the static operating point, the mitigation effect of Rf on the ESD parasitic capacitance is emphasized. Notably, there are tradeoffs to consider. Too large an Rf will worsen bandwidth, while too small a value will degrade noise and gain. With a carefully chosen value of Rf, the gain degradation will be within acceptable limits, and the bandwidth will be widened. In Figure 10, the impact of ESD circuitry on RF performance is significantly mitigated. If the same ESD is simply added without further circuit modification, a more prominent performance degradation occurs.

Figure 10.

Simulated S11 with and without ESD.

In RC networks where capacitors and resistors create a frequency pole, the signal gain decreases at a rate of −20 dB/decade. This characteristic necessitates maintaining frequency-independent gain stability across operational bandwidths to achieve optimal performance in broadband LNA. Numerous studies have extensively explored methodologies for broadband circuit implementations, as documented in prior research [17,18].

Taking into account the small signal circuit diagram shown in Figure 8, the voltage gain can be computed as

Here, δ = Rf/ZL. To analyze the impact of gain flatness, we derive Equation (10). Ignoring the active inductor L1, we can obtain

In Equation (11), the imaginary part is neglected, we can obtain

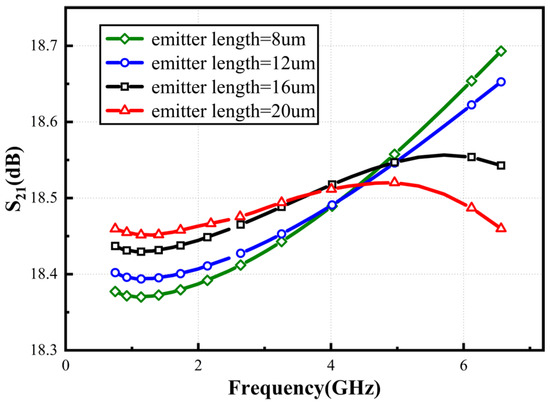

Equation (12) reveals that when the derivative of the small-signal gain with respect to frequency becomes 0. Under ideal conditions, with a transconductance gm2 = 125 mS and an input capacitance Cπ2 = 153 fF, theoretical calculations show that the gain derivative becomes zero at f = 130 GHz, achieving a flat gain response. However, in practical circuits, parasitic capacitances and resistances significantly reduce this characteristic frequency. Therefore, the actual frequency response must be evaluated through S21 parameter simulations. Without compromising other performance metrics, the flatness characteristic of the circuit gain can be enhanced by increasing the length of the Q2 emitter. Figure 11 shows the simulation curve of flatness as a function of emitter length. Specifically, increasing the upper transistor’s size optimizes the circuit’s flatness performance over the entire frequency band of interest.

Figure 11.

Simulated S21 with varied emitter length.

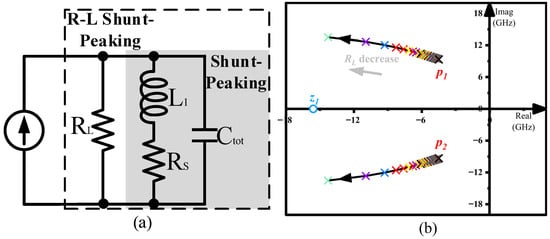

The flat gain performance of the circuit is achieved by adjusting the length of the emitter of Q2 in the absence of an inductor, and the bandwidth is further expanded by implementing the shunt-peaking technique with active inductors. Where the transistor is equated to a constant current source to explore the conditions for a load to achieve maximum bandwidth. The shunt-peaking technique has been proved to achieve up to 185% bandwidth expansion and 120% gain-peaking [19,20]. To solve the trade-off between bandwidth expansion and gain peaking, we connect a resistor RL in parallel with the original structure, resulting in the R-L shunt-peaking technique (Figure 12a), whose trans-impedance can be calculated as

where Ctot represents the parasitic capacitance of the output node. It can be found in Figure 12b that the impedance has a zero (z1) and a complex conjugate pair of poles (p1 and p2). Upon adding RL, z1 remains unchanged compared to the shunt-peaking technique, while p1 and p2 move away from the imaginary axis as RL decreases. Hence the magnitude of the frequency response decreases, while the position of the peak value of the frequency response (f = Im(p1)) is pushed back. The broadband characteristic of the load network is thus enhanced.

Figure 12.

(a) A equivalent model of the R-L shunt-peaking technique. (b) Locus of poles and zeros as RL decrease.

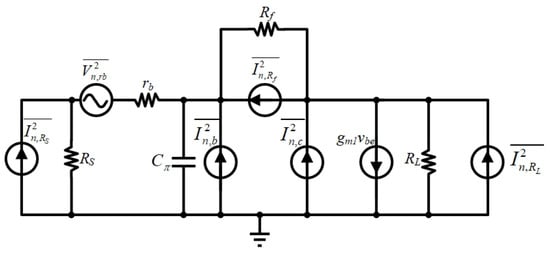

For cascaded amplifiers, when the gain of the first stage is large enough, the noise figure is mainly related to the first stage. Due to the large output impedance of Q1, the noise of Q2 can be ignored. Figure 13 shows a simplified LNA equivalent noise model considering all significant noise sources.

where , , g′m1 = gm1 − Rf−1, and Frb, FRf, FRL, FrL1 and Fnb+nc represent the noise factors due to thermal noise generated by the base parasitic resistor rb, the feedback resistor Rf, the load resistance RL, the parasitic resistance rL1 and base and collector shot noise, respectively. The total noise figure can be calculated as

Figure 13.

Small-signal noise model circuit.

The noise generated by the base parasitic resistance rb1 of Q1 accounts for the most significant proportion, followed by the collector-emitter shot noise. As frequency increases, the influence of the collector-emitter shot noise gradually emerges, mainly thanks to the effect of the emitter junction capacitance Cπ1. By extending the emitter length and tuning the base bias voltage, the parasitic resistance at the base is diminished. Through co-optimization of emitter geometry scaling and bias conditioning, rb1 is simulated to reach 15 Ω and Cπ1 is simulated to be 153 fF, achieving an optimal trade-off between input return loss and voltage gain across the 0.5–5.8 GHz operational bandwidth.

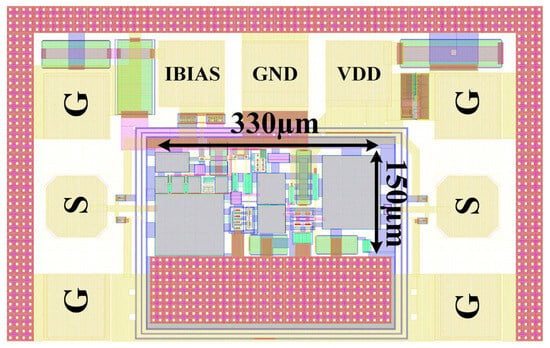

4. Simulation Results

The inductor-less wideband LNA described in this paper is fabricated using Tower-JAZZ’s 0.18 μm SiGe BiCMOS technology (Tower Semiconductor Ltd., Migdal Haemek, Israel). As shown in Figure 14, the core layout design of the LNA is highly compact, occupying a minimal chip area of only 0.049 mm2. Under a 3.3 V supply voltage, it exhibits an average current consumption of 10 mA, demonstrating efficient area utilization and optimized power consumption performance.

Figure 14.

Layout of the proposed LNA.

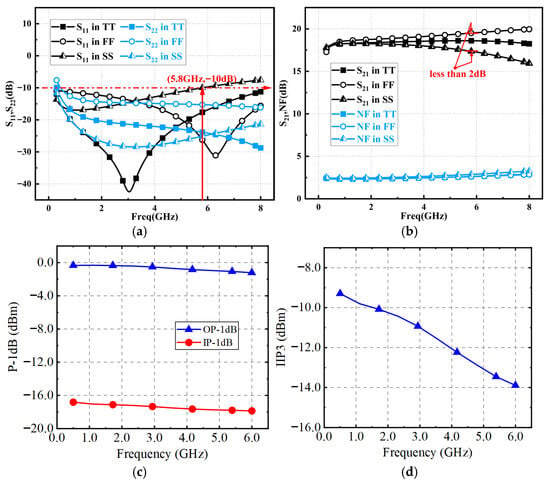

Figure 15 gives the post simulation of LNA under different process corners. This paper simulates the circuit performance under different process corners of the transistor, including Typical N Typical P (TT), Fast N Fast P (FF), and Slow N Slow P (SS) corners. Figure 15a shows a good input and output matching is achieved. Figure 15b illustrates that the LNA achieves a peak S21 of 18.6 dB with a gain ripple below 0.6 dB. Meanwhile, the simulated NF spans from 2.6 to 2.78 dB across the operating bandwidth. Figure 15c,d shows the IP-1dB of −17 dBm, OP-1dB of −1 dBm and IIP3 from −14 dBm to −7 dBm. Table 1 summarizes the proposed LNA with some previously published LNAs. By applying the AI with adaptive bias circuit to the LNA, this circuit is competitive in terms of bandwidth as well as chip-area performance. While the layout has successfully passed DRC/LVS verification, minor discrepancies between actual measurements and simulation results may occur during practical implementation.

Figure 15.

Simulated results of (a) S11 and S22 and (b) S21 and NF under different process corners and (c) P-1dB (d) IIP3 at TT corner.

Table 1.

Comparison between references and this work.

Table 1 compares the performance of the LNA proposed in this study with existing LNAs reported in the literature. The research findings demonstrate that this design achieves both excellent gain flatness and a low-noise figure. By eliminating the use of inductive components, the implementation has successfully minimized the chip area, thereby demonstrating significant competitive advantages in terms of area efficiency.

5. Conclusions

This paper explores the design and implementation of a broadband inductor-free LNA based on the Jazz 0.18 μm SiGe BiCMOS process, utilizing self-biased AI and enhanced DTI ESD diodes. The study analyzes the trade-offs and limitations in circuit design, proposes a resistive-inductive shunt-peaking technique, and conducts zero-pole analysis. Through the co-design of ESD diodes’ parasitic capacitance with the LNA circuit to optimize port matching, outstanding broadband performance is attained. The LNA core occupies a compact area of 0.049 mm2 and provides a flat high gain ranging from 18.0 to 18.6 dB across the 0.5–5.8 GHz frequency band.

Author Contributions

Conceptualization, D.D. and Z.L.; methodology, D.D.; software, Z.L.; validation, D.D.; formal analysis, D.D.; investigation, D.D.; resources, Z.L.; data curation, Y.Q.; writing—original draft preparation, Y.Q. and C.L.; writing—review and editing, X.H. and J.Z.; visualization, X.H. and J.Z.; supervision, L.Y.; project administration, L.Y.; funding acquisition, L.Y. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Im, D.; Nam, L. A 0.1 to 5 GHz ultra-wide band single-to-differential CMOS LNA with output balancing for SDRs. IEICE Electron. Express. 2013, 10, 20130789. [Google Scholar] [CrossRef]

- Amiri, N.S.; Gholami, M. Design of 3.1 to 10.6 GHz ultra-wideband flat gain LNA. Int. J. Circuit Theory Appl. 2017, 45, 2034–2045. [Google Scholar] [CrossRef]

- Jang, J.; Kim, H.; Lee, G.; Kim, T.W. Two-Stage Compact Wideband Flat Gain Low-Noise Amplifier Using High-Frequency Feedforward Active Inductor. IEEE Trans. Microw. Theory Tech. 2019, 67, 4803–4811. [Google Scholar] [CrossRef]

- Belmas, F.; Hameau, F.; Fournier, J.M. A Low Power Inductorless LNA With Double Gm Enhancement in 130 nm CMOS. IEEE J. Solid-State Circuits. 2012, 47, 1094–1103. [Google Scholar] [CrossRef]

- De Souza, M.; Mariano, A.; Taris, T. Reconfigurable Inductorless Wideband CMOS LNA for Wireless Communications. IEEE Trans. Circuits Syst. Regul. Pap. 2017, 64, 675–685. [Google Scholar] [CrossRef]

- Nediyara Suresh, L.; Manickam, B. Design of Active Inductor-Based VCO with Wide Tuning Range for RF Front End. Circuits Syst. Signal Process. 2022, 41, 2486–2502. [Google Scholar] [CrossRef]

- Majeed, H.; Singh, V. A Common-Gate, gm-boosting LNA Using Active Inductor-Based Input Matching for 3.1–10.6 GHz UWB Applications. Electrica 2022, 22, 173–187. [Google Scholar] [CrossRef]

- Behera, P.; Siddique, A.; Delwar, T.S.; Biswal, M.R.; Choi, Y.; Ryu, J.Y. A Novel 65 nm Active-Inductor-Based VCO with Improved Q-Factor for 24 GHz Automotive Radar Applications. Sensors 2022, 22, 4701. [Google Scholar] [CrossRef]

- Sachan, D.; Goswami, M.; Misra, P.K. A high-Q floating active inductor using 130 nm BiCMOS technology and its application in IF band pass filter. Analog. Integr. Circuits Signal Process. 2018, 96, 385–393. [Google Scholar] [CrossRef]

- Meister, T.; Ishida, K.; Knobelspies, S.; Cantarella, G.; Münzenrieder, N.; Tröster, G.; Carta, C.; Ellinger, F. 5–31-Hz 188-$\mu $ W Light-Sensing Oscillator with Two Active Inductors Fully Integrated on Plastic. IEEE J. Solid-State Circuits 2019, 54, 2195–2206. [Google Scholar] [CrossRef]

- Mhiri, M.; Besbes, K. Gyrator-C-Based CMOS Active Inductors: Analysis of Performance Optimization Techniques. IEEE Microw. Mag. 2021, 22, 65–82. [Google Scholar] [CrossRef]

- Wang, H.; Zhang, L.; Yu, Z. A Wideband Inductorless LNA with Local Feedback and Noise Cancelling for Low-Power Low-Voltage Applications. IEEE Trans. Circuits Syst. Regul. Pap. 2010, 57, 1993–2005. [Google Scholar] [CrossRef]

- Chang, T.; Chen, J.; Rigge, L.A.; Lin, J. ESD-Protected Wideband CMOS LNAs Using Modified Resistive Feedback Techniques with Chip-on-Board Packaging. IEEE Trans. Microw. Theory Tech. 2008, 56, 1817–1826. [Google Scholar] [CrossRef]

- Guan, X.; Wang, X.; Lin, L.; Chen, G.; Wang, A.; Liu, H.; Zhou, Y.; Chen, H.; Yang, L.; Zhao, B. (Invited) ESD-RFIC Co-design methodology. In Proceedings of the 2008 IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 15–17 June 2008; pp. 467–470. [Google Scholar] [CrossRef]

- Wu, C.Y.; Lo, Y.K.; Chen, M.C. A 3–10 GHz CMOS UWB Low-Noise Amplifier with ESD Protection Circuits. IEEE Microw. Wirel. Compon. Lett. 2009, 19, 737–739. [Google Scholar] [CrossRef]

- Bhatia, K.; Hyvonen, S.; Rosenbaum, E. A Compact, ESD-Protected, SiGe BiCMOS LNA for Ultra-Wideband Applications. IEEE J. Solid-State Circuits 2007, 42, 1121–1130. [Google Scholar] [CrossRef]

- Tiwari, S.; Mukherjee, J. An inductorless wideband gm-boosted balun LNA with nMOS-pMOS configuration and capacitively coupled loads for sub-GHz IoT applications. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 3204–3208. [Google Scholar] [CrossRef]

- Yu, Y.H.; Yang, Y.S.; Chen, Y.J.E. A compact wideband CMOS low noise amplifier with gain flatness enhancement. IEEE J. Solid-State Circuits 2010, 45, 502–509. [Google Scholar] [CrossRef]

- Wang, Z.; Cheng, G.; Kang, W.; Wu, W.; Li, Z. A 2˜ 10 GHz Ultra-Wideband LNA in 0.13 μm SiGe BiCMOS Technology. In Proceedings of the 2021 IEEE 3rd International Conference on Circuits and Systems (ICCS), Chengdu, China, 29–31 October 2021; pp. 161–164. [Google Scholar]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth extension techniques for CMOS amplifiers. IEEE J. Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Han, T.; Li, Z.; Tian, M. An inductor-less CMOS broadband balun gm-boosting LNA exploiting noise cancellation techniques. Analog. Integr. Circuits Signal Process. 2020, 104, 121–129. [Google Scholar] [CrossRef]

- Guo, B.; Chen, J.; Li, L.; Jin, H.; Yang, G. A Wideband Noise-Canceling CMOS LNA With Enhanced Linearity by Using Complementary nMOS and pMOS Configurations. IEEE J. Solid-State Circuits 2017, 52, 1331–1344. [Google Scholar] [CrossRef]

- Ebrahimi, A.; Shaterian, M. A 4-bit active-inductor-based digitally programmable low noise amplifier (AI-DPLNA) with a tunable and reconfigurable structure. Microelectron. J. 2024, 151, 106316. [Google Scholar] [CrossRef]

- Farahani, M.M.; Mazloum, J.; Fouladian, M. An ultra-wideband low noise amplifier with cascaded flipped-active inductor for cognitive radio applications. Integration 2023, 93, 102046. [Google Scholar] [CrossRef]

- Çaışkan, C.; Kalyoncu, I.; Yazici, M.; Gurbuz, Y. Sub-1-dB and Wideband SiGe BiCMOS Low-Noise Amplifiers for $X$ -Band Applic-tions. IEEE Trans. Circuits Syst. Regul. Pap. 2019, 66, 1419–1430. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).