Silicon-on-Insulator (SOI) Lateral Power-Reduced Surface Field FinFET with High-Power Figure of Merit of 239.3 MW/cm2

Abstract

1. Introduction

2. Materials and Methods

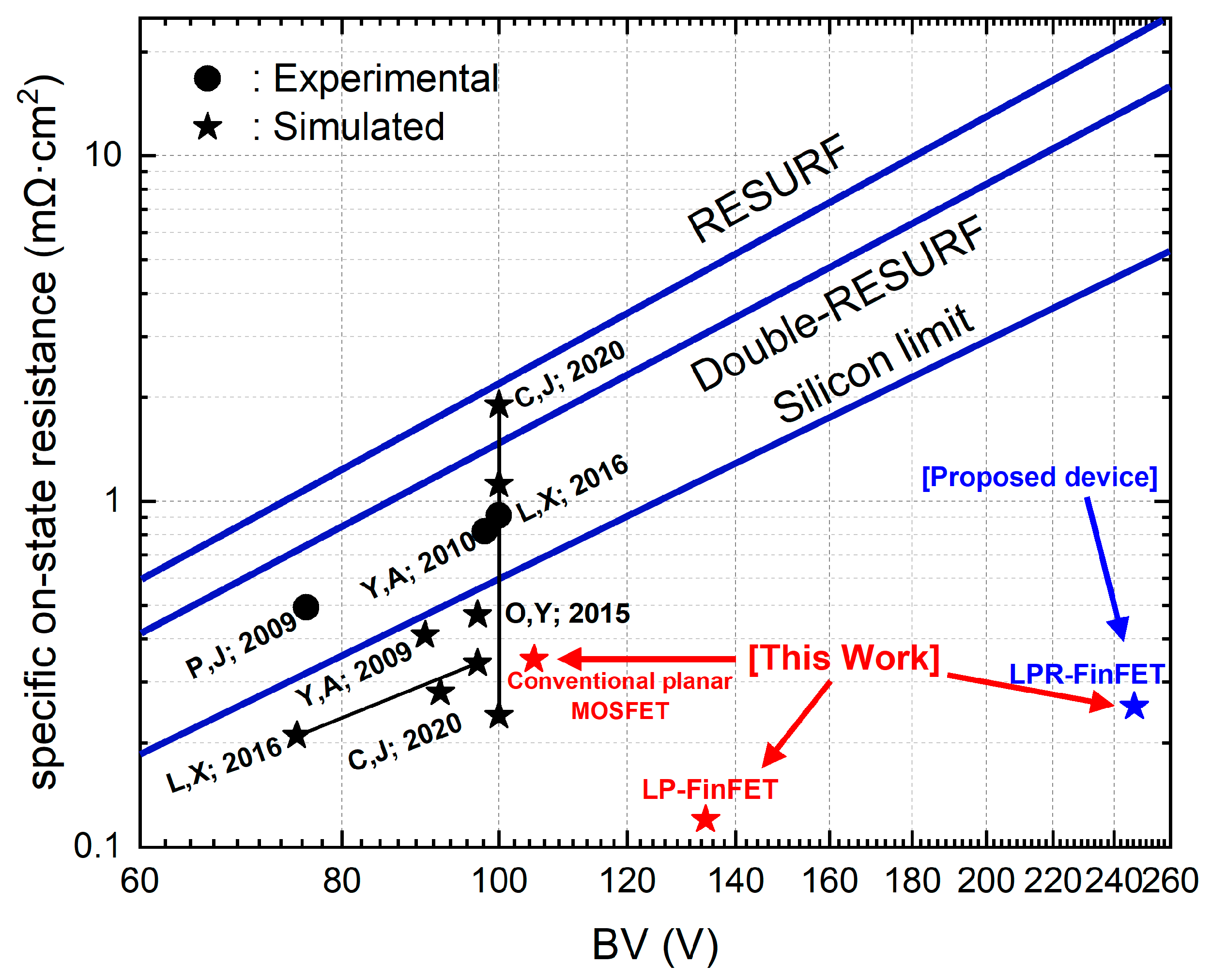

3. Results and Discussion

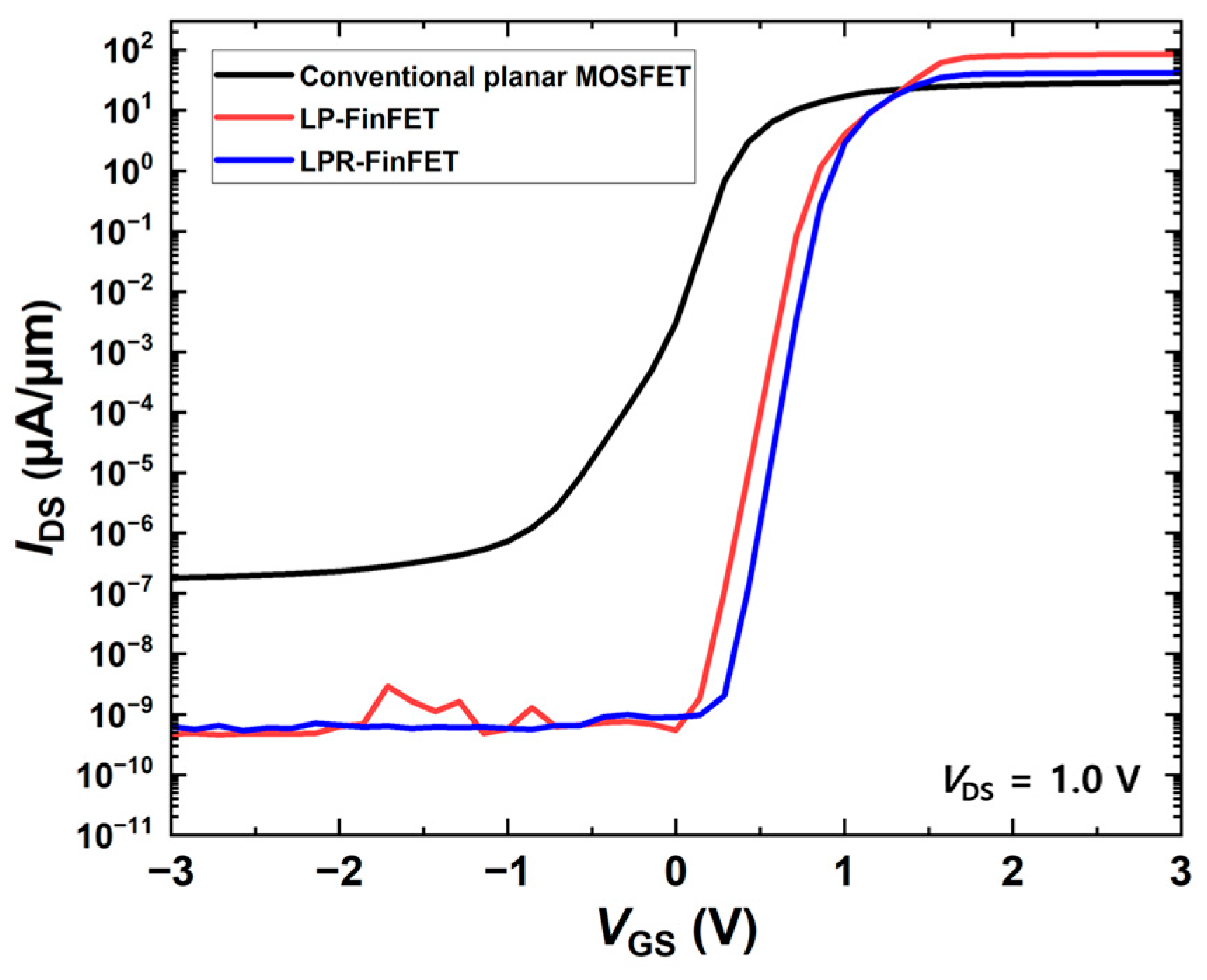

3.1. Forward Characteristics

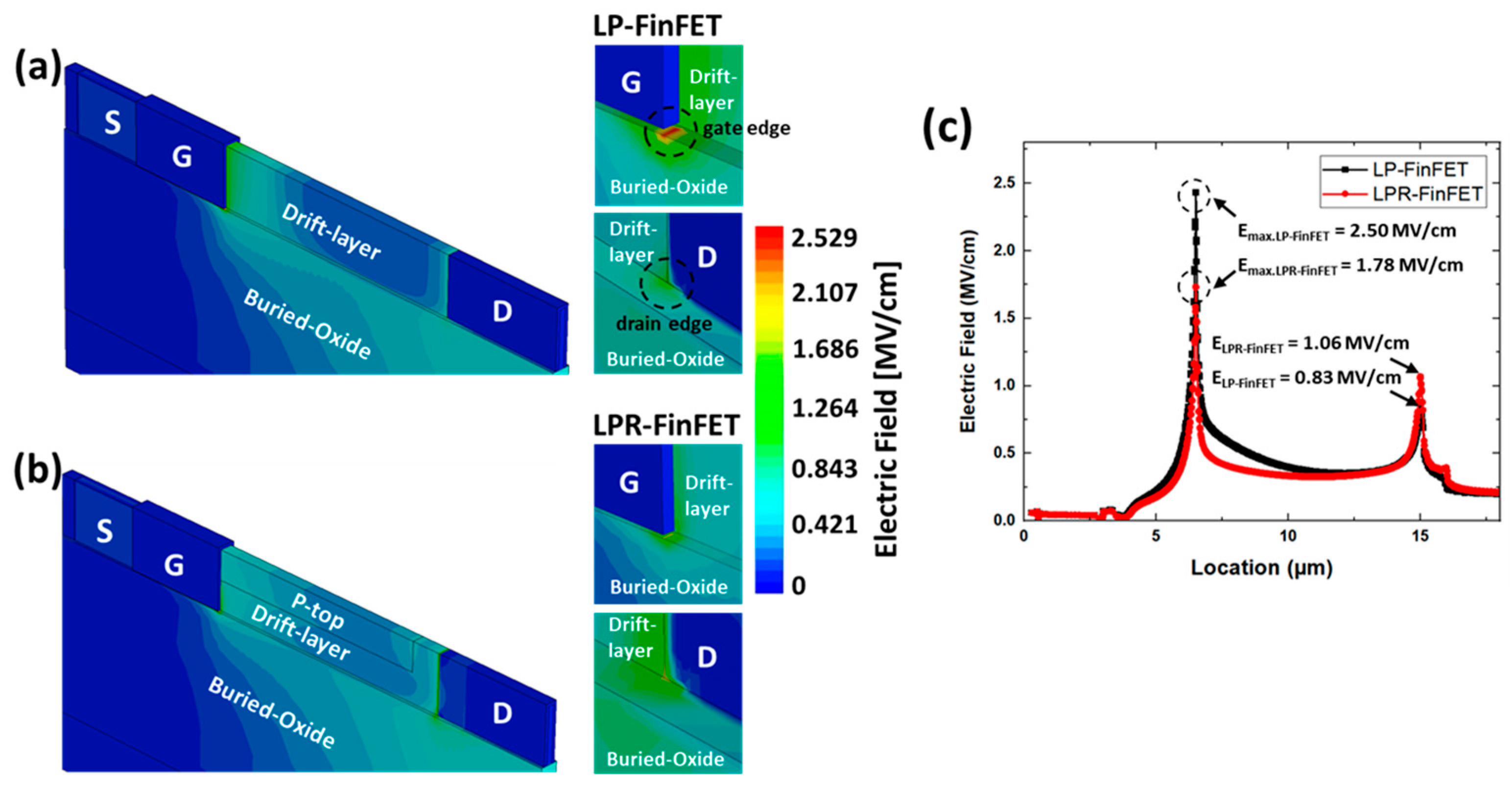

3.2. Electric Field Distributions

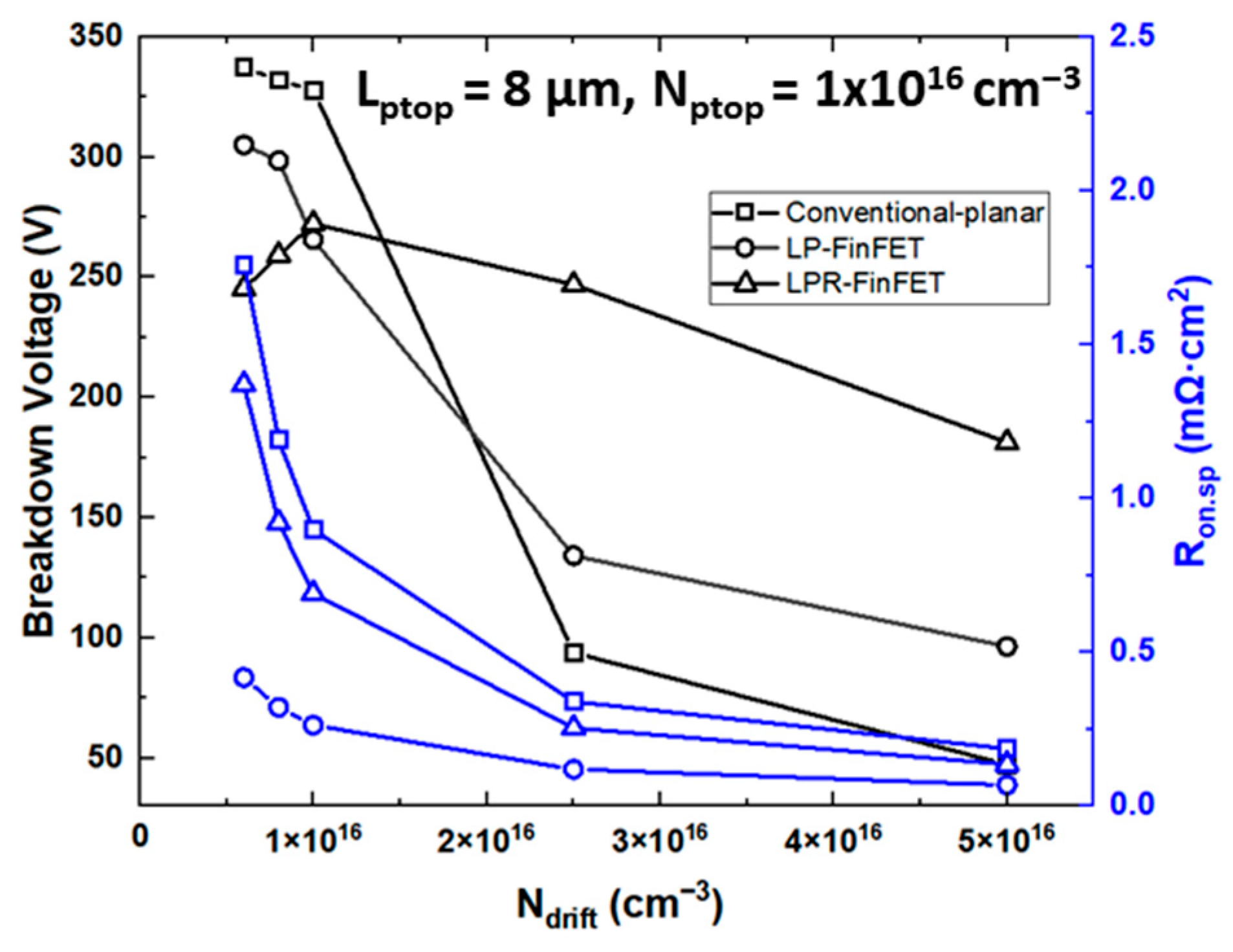

3.3. Breakdown Voltage Characteristics

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, G.; Li, K.; Wang, Y.; Luo, H.; Luo, H. Recent advances and trend of HEV/EV-oriented power semiconductors–an overview. IET Power Electron. 2020, 13, 394–404. [Google Scholar] [CrossRef]

- Tang, Z.; Yang, Y.; Blaabjerg, F. Power electronics-the enabling technology for renewable energy integration. CSEE J. Power Energy Syst. 2022, 8, 39–52. [Google Scholar] [CrossRef]

- Nguyen, M.H.; Kwak, S. Enhance Reliability of Semiconductor Devices in Power Converters. Electronics 2020, 9, 2068. [Google Scholar] [CrossRef]

- Armstrong, K.O.; Das, S.; Cresko, J. Wide bandgap semiconductor opportunities in power electronics. In Proceedings of the 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 259–264. [Google Scholar] [CrossRef]

- Hara, K.; Wada, S.; Sakano, J.; Oda, T. 600V single chip inverter IC with new SOI technology. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; IEEE: New York, NY, USA, 2014; pp. 418–421. [Google Scholar] [CrossRef]

- Udrea, F. SOI-based devices and technologies for High Voltage ICs. In Proceedings of the 2007 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Boston, MA, USA, 30 September–2 October 2007; IEEE: New York, NY, USA, 2007; pp. 74–81. [Google Scholar] [CrossRef]

- Luo, X.; Lv, M.; Yin, C.; Wei, J.; Zhou, K.; Zhao, Z. Ultralow ON-Resistance SOI LDMOS With Three Separated Gates and High-k Dielectric. IEEE Trans. Electron Devices 2016, 63, 3804–3807. [Google Scholar] [CrossRef]

- Hu, S.; Luo, J.; Jiang, Y.; Cheng, K.; Chen, Y.; Jin, J.; Wang, J.; Zhou, J.; Tang, F.; Zhou, X.; et al. Improving breakdown, conductive, and thermal performances for SOI high voltage LDMOS using a partial compound buried layer. Solid-State Electron. 2016, 117, 146–151. [Google Scholar] [CrossRef]

- Son, W.-S.; Sohn, Y.-H.; Choi, S. RESURF LDMOSFET with a trench for SOI power integrated circuits. Microelectron. J. 2016, 35, 393–400. [Google Scholar] [CrossRef]

- Yun, N.; Lynch, J.; Sung, W. Demonstration and analysis of a 600 V, 10 A, 4H-SiC lateral single RESURF MOSFET for power ICs applications. Appl. Phys. Lett. 2019, 114, 192104. [Google Scholar] [CrossRef]

- Cheng, J.; Lin, J.; Chen, W.; Wu, S.; Huang, H.; Yi, B. Lateral Power Fin MOSFET with a High-k Passivation for Ultra-Low On-Resistance. IEEE Access 2020, 8, 48991–48999. [Google Scholar] [CrossRef]

- Lv, Y.; Liu, H.; Zhou, X.; Wang, Y.; Song, X.; Cai, Y.; Yan, Q.; Wang, C.; Liang, S.; Zhang, J.; et al. Lateral β-Ga2O3 MOSFETs with High Power Figure of Merit of 277 MW/cm2. IEEE Electron Device Lett. 2020, 41, 537–540. [Google Scholar] [CrossRef]

- Lv, Y.; Zhou, X.; Long, S.; Song, X.; Wang, Y.; Liang, S.; He, Z.; Han, T.; Tan, X.; Feng, Z.; et al. Source-Field-Plated β-Ga2O3 MOSFET with Record Power Figure of Merit of 50.4 MW/cm2. IEEE Electron Device Lett. 2018, 40, 83–86. [Google Scholar] [CrossRef]

- Tetzner, K.; Treidel, E.B.; Hilt, O.; Popp, A.; Anooz, S.B.; Wagner, G.; Thies, A.; Ickert, K.; Gargouri, H.; Würfl, J.; et al. Lateral 1.8 kV β-Ga2O3 MOSFET with 155 MW/cm2 Power Figure of Merit. IEEE Electron Device Lett. 2019, 40, 1503–1506. [Google Scholar] [CrossRef]

- Iqbal, M.M.-H.; Udrea, F.; Napoli, E. On the static performance of the RESURF LDMOSFETS for power ICs. In Proceedings of the 2009 21st International Symposium on Power Semiconductor Devices & IC’s, Barcelona, Spain, 14–18 June 2009; IEEE: New York, NY, USA, 2009; pp. 247–250. [Google Scholar] [CrossRef]

- Cha, H.; Lee, K.; Lee, J.; Lee, T. 0.18 μm 100 V-rated BCD with large area power LDMOS with ultra-low effective specific resistance. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; IEEE: New York, NY, USA, 2016; pp. 423–426. [Google Scholar] [CrossRef]

- Yoo, A.; Onish, Y.; Xu, E.; Ng, W.T. A Low-Voltage Lateral SJ-FINFET With Deep-Trench p-Drift Region. IEEE Electron Device Lett. 2009, 30, 858–860. [Google Scholar] [CrossRef]

- Yoo, A.; Ng, J.C.W.; Sin, J.K.O.; Ng, W.T. High performance CMOS-compatible super-junction FINFETs for Sub-100V applications. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; IEEE: New York, NY, USA, 2010; pp. 20.7.1–20.7.4. [Google Scholar] [CrossRef]

- Onishi, Y.; Hashimoto, Y. Trench-gate-integrated superjunction lateral double-diffused MOSFET with low specific on-resistance. Jpn. J. Appl. Phys. 2015, 54, 084101. [Google Scholar] [CrossRef]

- Singh, Y.; Rawat, R.S. High figure-of-merit SOI power LDMOS for power integrated circuits. Eng. Sci. Technol. Int. J. 2015, 18, 141–149. [Google Scholar] [CrossRef][Green Version]

- Langpoklakpam, C.; Liu, A.C.; Hsiao, Y.K.; Lin, C.H.; Kuo, H.C. Vertical GaN MOSFET power devices. Micromachines 2023, 14, 1937. [Google Scholar] [CrossRef] [PubMed]

- Dudley, M.; Bakowski, M.; Shenai, K.; Ohtani, N.; Raghothamachar, B. (Eds.) Gallium Nitride and Silicon Carbide Power Technologies 8; The Electrochemical Society: Philadelphia, PA, USA, 2018. [Google Scholar]

- Brusaterra, E.; Treidel, E.B.; Brunner, F.; Wolf, M.; Thies, A.; Würfl, J.; Hilt, O. Optimization of vertical GaN drift region layers for avalanche and punch-through pn-diodes. IEEE Electron Device Lett. 2023, 44, 388–391. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, M.; Perozek, J.; Liu, Z.; Zubair, A.; Piedra, D.; Chowdhury, N.; Gao, X.; Shepard, K.; Palacios, T. Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit. IEEE Electron Device Lett. 2019, 40, 75–78. [Google Scholar] [CrossRef]

- Zhou, Q.; Chen, B.; Jin, Y.; Huang, S.; Wei, K.; Liu, X.; Bao, X.; Mou, J.; Zhang, B. High-Performance Enhancement-Mode Al2O3/AlGaN/GaN-on-Si MISFETs with 626 MWcm2 Figure of Merit. IEEE Trans. Electron Devices 2015, 62, 776–781. [Google Scholar] [CrossRef]

- Park, J.; Ko, K.; Eum, J.; Lee, K.; Jin, J.; Kim, Y.; Jeong, S.; Lee, S.; Lee, J.; Cho, I.; et al. A proposal of LDMOS using Deep Trench poly field plate. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; IEEE: New York, NY, USA, 2015; pp. 149–152. [Google Scholar] [CrossRef]

- Cheng, J.; Huang, H.; Yi, B.; Zhang, W.; Ng, W.T. A TCAD Study on Lateral Power MOSFET with Dual Conduction Paths and High-k Passivation. IEEE Electron Device Lett. 2020, 41, 260–263. [Google Scholar] [CrossRef]

| Symbol | Meaning | Value |

|---|---|---|

| Ldrift | Drift length | 12.0 μm |

| LD | Drain length | 4.0 μm |

| LS | Source length | 3.0 μm |

| Lptop | p-top length | 2.0~8.0 μm |

| WJFET | JFET region length | 2.0 μm |

| tp | Fin Plate thickness | 0.1 μm |

| w1 | Fin n-drift width | 0.4 μm |

| w2 | N+ width | 0.1 μm |

| TOX | Gate oxide thickness | 20 nm |

| Tsub | Substrate thickness | 2.0 μm |

| Tburied | Buried oxide thickness | 6.0 μm |

| Tdrift | Drift layer thickness | 2.0 μm |

| Device | BV (V) | Ron,sp (mΩ·cm2) | P-FOM (MW/cm2) |

|---|---|---|---|

| Conventional-planar | 105.1 | 0.340 | 32.5 |

| LP-FinFET | 134.2 | 0.120 | 150.0 |

| LPR-FinFET | 247 | 0.255 | 239.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Song, C.W.; Lee, T.; Kim, D.; Kyoung, S.; Woo, S. Silicon-on-Insulator (SOI) Lateral Power-Reduced Surface Field FinFET with High-Power Figure of Merit of 239.3 MW/cm2. Micromachines 2025, 16, 1080. https://doi.org/10.3390/mi16101080

Song CW, Lee T, Kim D, Kyoung S, Woo S. Silicon-on-Insulator (SOI) Lateral Power-Reduced Surface Field FinFET with High-Power Figure of Merit of 239.3 MW/cm2. Micromachines. 2025; 16(10):1080. https://doi.org/10.3390/mi16101080

Chicago/Turabian StyleSong, Chang Woo, Taeeun Lee, Dongyeon Kim, Sinsu Kyoung, and Sola Woo. 2025. "Silicon-on-Insulator (SOI) Lateral Power-Reduced Surface Field FinFET with High-Power Figure of Merit of 239.3 MW/cm2" Micromachines 16, no. 10: 1080. https://doi.org/10.3390/mi16101080

APA StyleSong, C. W., Lee, T., Kim, D., Kyoung, S., & Woo, S. (2025). Silicon-on-Insulator (SOI) Lateral Power-Reduced Surface Field FinFET with High-Power Figure of Merit of 239.3 MW/cm2. Micromachines, 16(10), 1080. https://doi.org/10.3390/mi16101080