A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications

Abstract

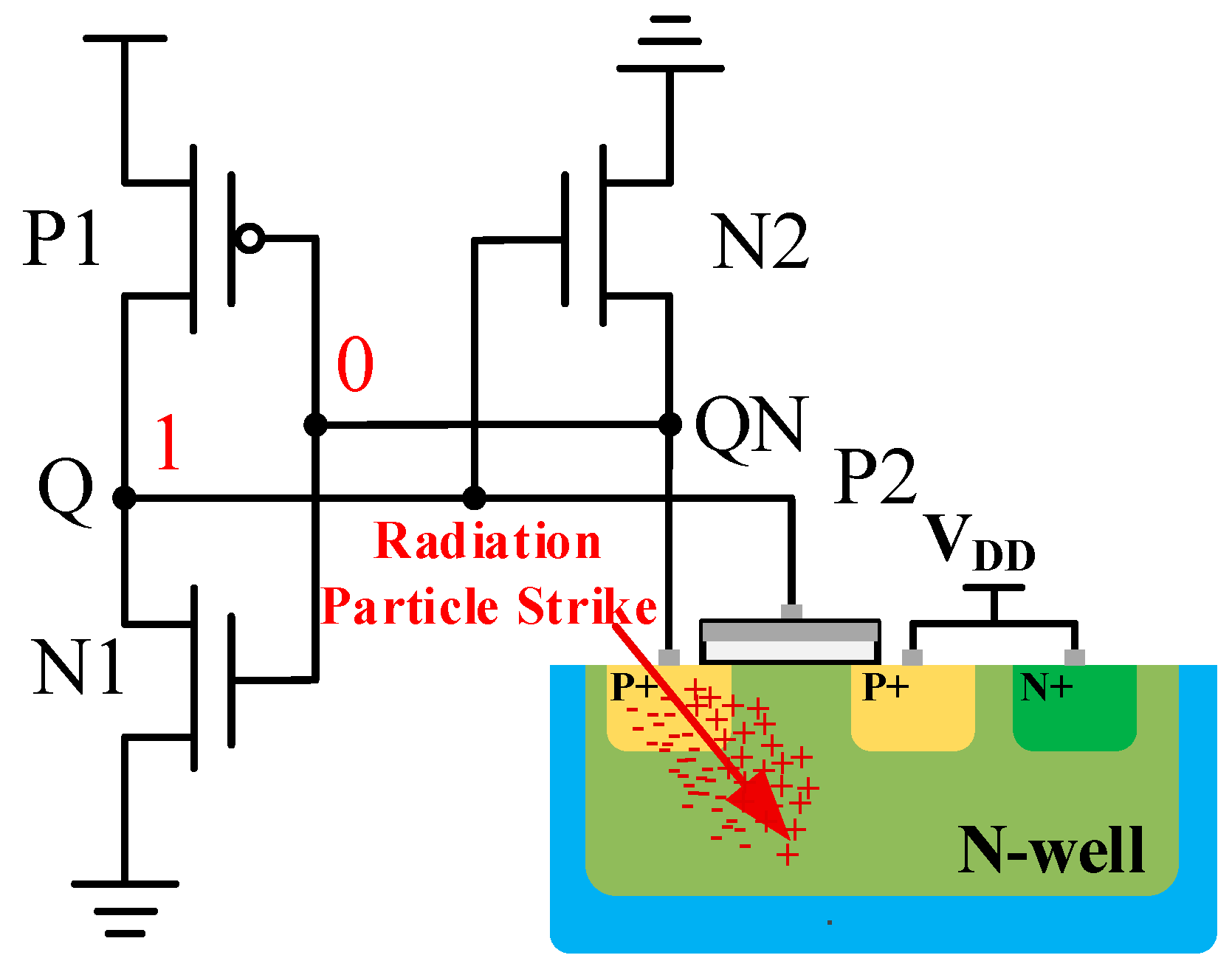

:1. Introduction

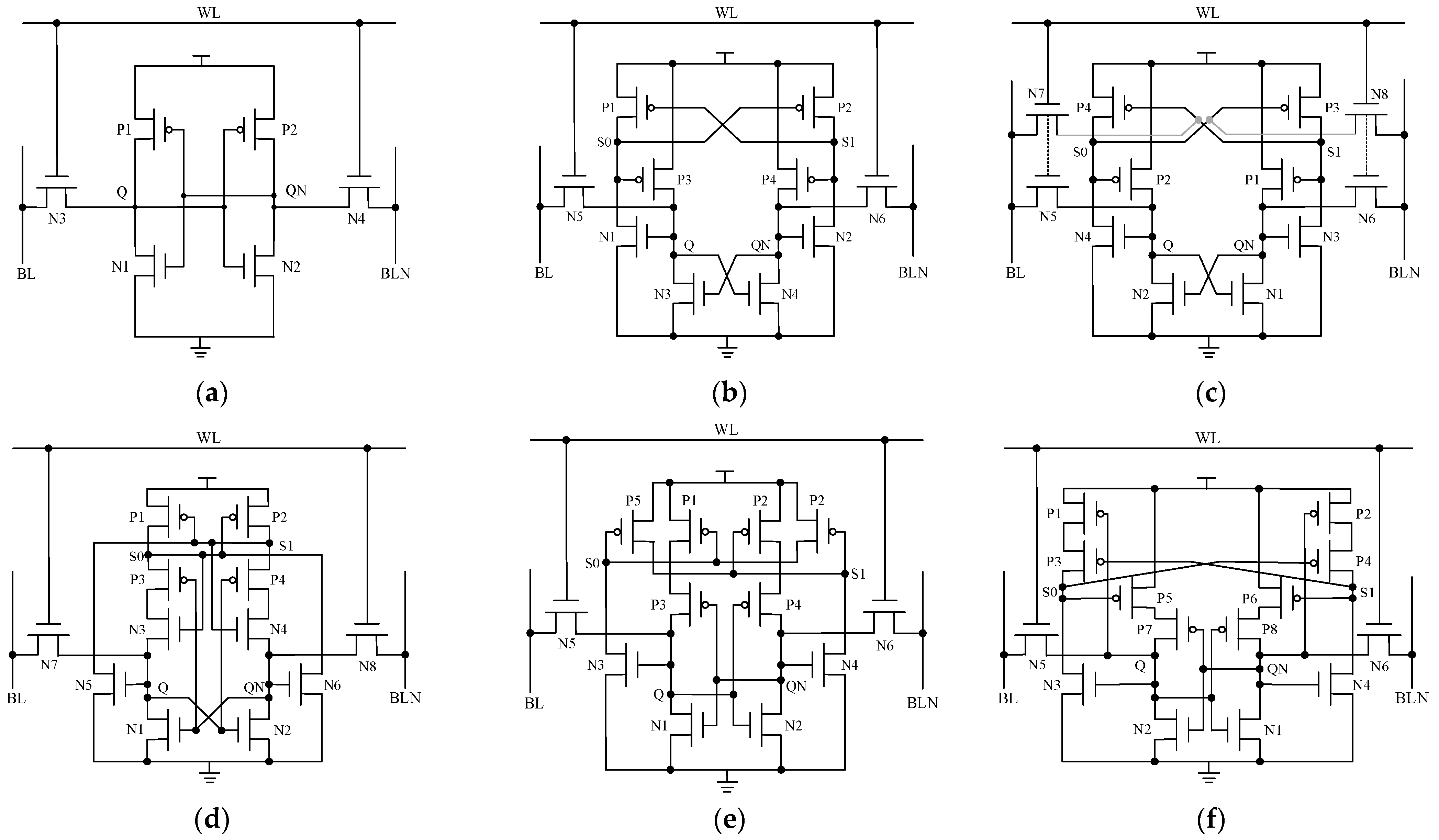

2. Previous Hardened Memory Cells

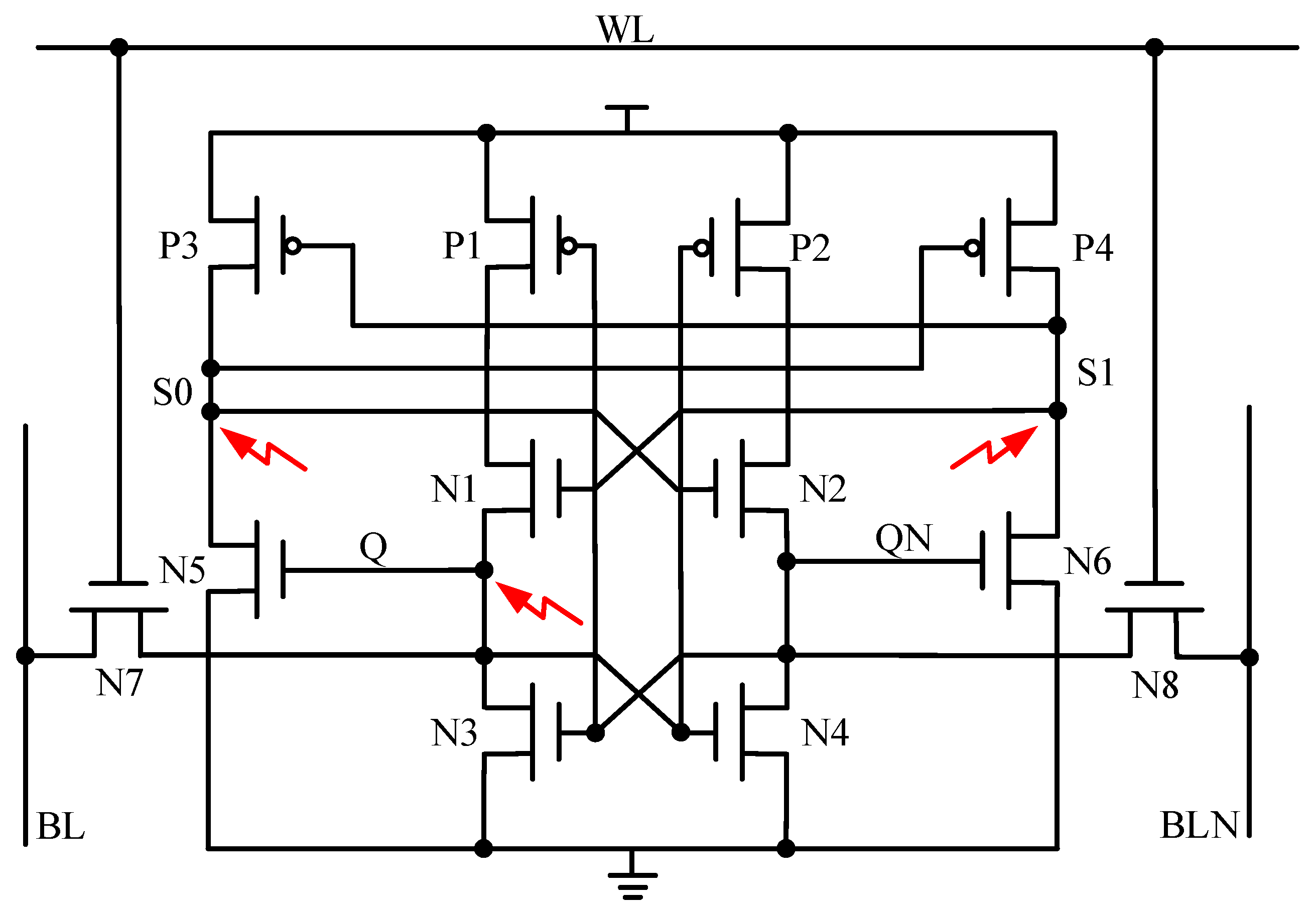

3. The Proposed RHB-12T Cell and Its Operation

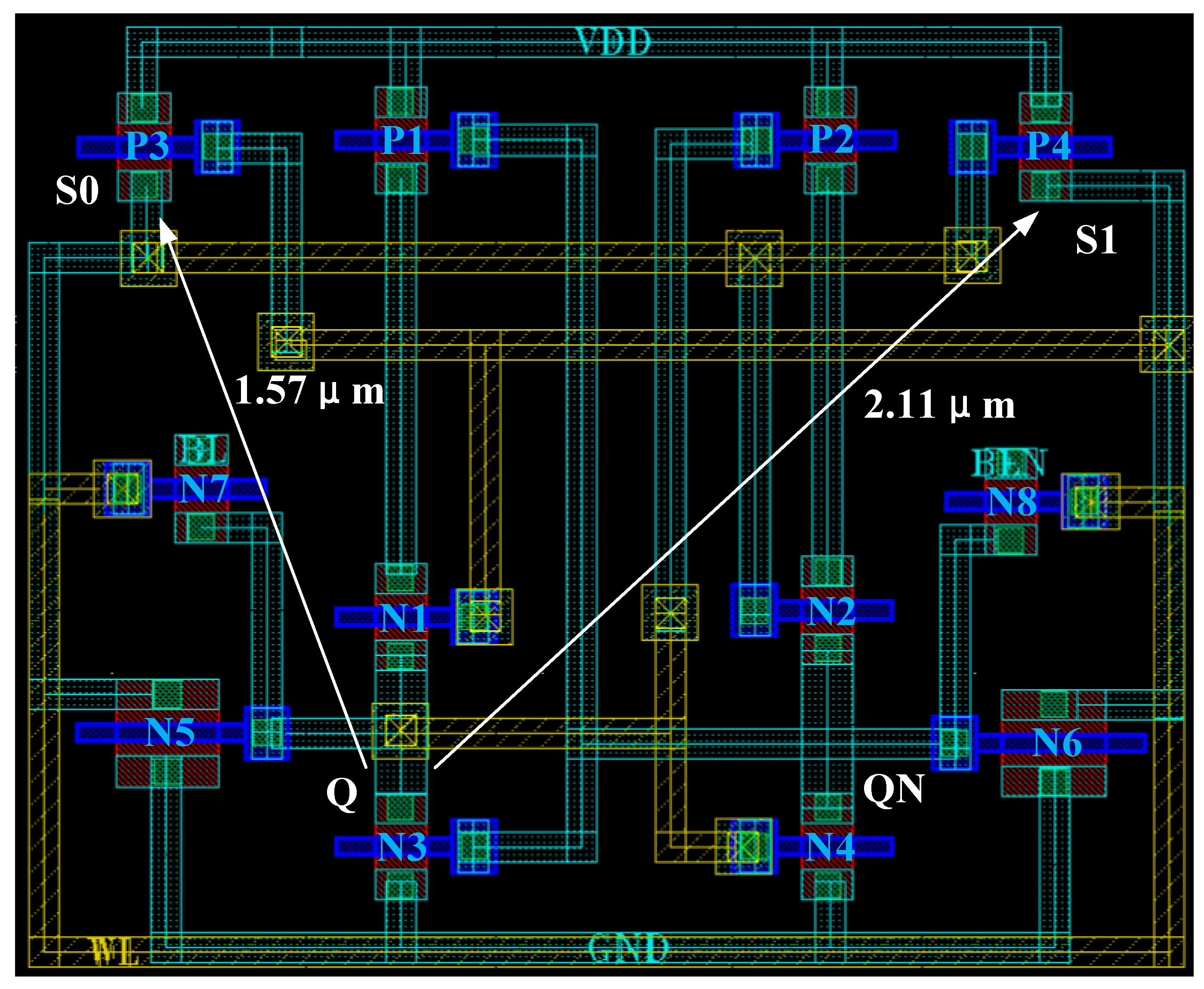

3.1. Cell Design and Its Operation

3.2. SEU Recovery Analysis

4. Simulation and Analysis

4.1. Access Time Simulation

4.2. Stability Simulation

4.3. Cell Power Consumption Simulation

4.4. Simulation of Radiation Tolerance

- (1)

- Pulse current model

- (2)

- Node-injection verification

- (3)

- Critical charge simulation

4.5. Cell Performance Summary

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Casey, M.C.; Stansberry, S.D.; Seidleck, C.M.; Maharrey, J.A.; Gamboa, D.; Pellish, J.A.; Label, K.A. Single-Event Response of 22nm Fully Depleted Silicon-on-Insulator Static Random Access Memory. IEEE Trans. Nucl. Sci. 2021, 68, 402–409. [Google Scholar] [CrossRef]

- Dohar, S.S.; Siddharth, R.K.; Vasantha, M.H.; Nithin Kumar, Y.B. A 1.2 V Highly Reliable RHBD 10T SRAM Cell for Aerospace Application. IEEE Trans. Electron. Devices 2021, 68, 2265–2270. [Google Scholar] [CrossRef]

- Dodd, P.E.; Shaneyfelt, M.R.; Schwank, J.R.; Felix, J.A. Current and Future Challenges in Radiation Effects on CMOS Electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- CH, N.R.; Gupta, B.; Kaushal, G. Single-Event Multiple Effect Tolerant RHBD14T SRAM Cell Design for Space Applications. IEEE Trans. Device Mater. Reliab. 2021, 21, 48–56. [Google Scholar] [CrossRef]

- Kahng, A.B. The ITRS Design Technology and System Drivers Roadmap: Process and Status. In Proceedings of the 2013 50th ACM/EDAC/IEEE Design Auto-mation Conference (DAC), Austin, TX, USA, 29 May 2013; pp. 1–6. [Google Scholar]

- Pal, S.; Bose, S.; Ki, W.H.; Islam, A. Characterization of Half-Select Free Write Assist 9T SRAM Cell. IEEE Trans. Electron. Devices 2019, 66, 4745–4752. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.H.; Islam, A. Design of Soft-Error-Aware SRAM With Multi-Node Upset Recovery for Aerospace Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2470–2480. [Google Scholar] [CrossRef]

- Atias, L.; Teman, A.; Giterman, R.; Meinerzhagen, P.; Fish, A. A Low-Voltage Radiation-Hardened 13T SRAM Bitcell for Ultralow Power Space Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2622–2633. [Google Scholar] [CrossRef]

- Pal, S.; Chowdary, G.; Ki, W.H.; Tsui, C. Energy-Efficient Dual-Node-Upset-Recoverable 12T SRAM for Low-Power Aerospace Applications. IEEE Access 2023, 11, 20184–20195. [Google Scholar] [CrossRef]

- Jun, I.; Kim, Y.; Lombardi, F. A novel sort error hardened 10T SRAM cells for low voltage operation. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012; pp. 714–717. [Google Scholar]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset Hardened Memory Design for Submicron CMOS Technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Jiang, J.; Xu, X.; Zhu, W.; Xiao, J.; Zou, S. Quadruple Cross-Coupled Latch-Based 10T and 12T SRAM Bit-Cell Designs for Highly Reliable Terrestrial Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 967–977. [Google Scholar] [CrossRef]

- Seyedi, A.; Aunet, S.; Kjeldsberg, P.G. Nwise and Pwise: 10T Radiation Hardened SRAM Cells for Space Applications With High Reliability Requirements. IEEE Access 2022, 10, 30624–30642. [Google Scholar] [CrossRef]

- Pal, S.; Ki, W.H.; Tsui, C. Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability for Aerospace Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 63, 1560–1570. [Google Scholar] [CrossRef]

- Yan, A.; Xiang, J.; Cao, A.; He, Z.; Cui, J.; Ni, T. Quadruple and Sextuple Cross-Coupled SRAM Cell Designs With Optimized Overhead for Reliable Applications. IEEE Trans. Device Mater. Reliab. 2022, 22, 282–295. [Google Scholar] [CrossRef]

- Dohar, S.; Siddharth, R.K.; Vasantha, M.H.; Nithin Kumar, Y.B. A Novel Single Event Upset Tolerant 12T Memory Cell for Aerospace Applications. In Proceedings of the 2020 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Limassol, Cyprus, 6–8 July 2020; pp. 48–53. [Google Scholar]

- Li, H.; Xiao, L.; Qi, C.; Li, J. Design of High-Reliability Memory Cell to Mitigate Single Event Multiple Node Upsets. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 4170–4181. [Google Scholar] [CrossRef]

- Kumar, M.P.; Lorenzo, R. A 1.2V, Radiation Hardened 14T SRAM Memory Cell for Aerospace Applications. In Proceedings of the 2022 IEEE Silchar Subsection Conference (SILCON), Silchar, India, 4–6 November 2022; pp. 1–7. [Google Scholar]

- Pal, S.; Sir, D.D.; Ki, W.H.; Islam, A. Soft-Error Resilient Read Decoupled SRAM With Multi-Node Upset Recovery for Space Applications. IEEE Trans. Electron. Devices 2021, 68, 2246–2254. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.H.; Islam, A. Soft-Error-Immune Read-Stability-Improved SRAM for Multi-Node Upset Tolerance in Space Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 3317–3327. [Google Scholar] [CrossRef]

- D’Alessio, M.; Ottavi, M.; Lombardi, F. Design of a Nanometric CMOS Memory Cell for Hardening to a Single Event With a Multiple-Node Upse. IEEE Trans. Device Mater. Reliab. 2012, 14, 127–132. [Google Scholar] [CrossRef]

- Jahinuzzaman, S.M.; Rennie, D.J.; Sachdev, M. A Soft Error Tolerant 10T SRAM Bit-Cell With Differential Read Capability. IEEE Trans. Nucl. Sci. 2009, 56, 3768–3773. [Google Scholar] [CrossRef]

- Dang, L.D.T.; Seo, D.; Han, J.W.; Kim, J.; Chang, I. A 28nm FD-SOI4KB Radiation-hardened 12T SRAM Macro with 0.6IV Wide Dynamic Voltage Scaling for Space Applications. In Proceedings of the 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), Tainan, Taiwan, 5–7 November 2018; pp. 133–134. [Google Scholar]

- Guo, J.; Xiao, L.; Mao, Z. Novel Low-power and Highly Reliable Radiation Hardened Memory Cell for 65nm CMOS Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1994–2001. [Google Scholar] [CrossRef]

- Qi, C.; Xiao, L.; Wang, T.; Li, J.; Li, L. A Highly Reliable Memory Cell Design Combined With Layout-Level Approach to Tolerant Single-Event Upsets. IEEE Trans. Device Mater. Reliab. 2016, 16, 388–395. [Google Scholar] [CrossRef]

- Peng, C.; Huang, J.; Liu, C.; Zhao, Q.; Xiao, S. Radiation-hardened 14T SRAM Bitcell with Speed and Power Optimized for Space Application. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 407–415. [Google Scholar] [CrossRef]

- Su, Z.X.; Li, B.; Su, X.H.; Liu, F.Y.; Han, Z.S.; Liu, X.Y.; Pctrosyants, K.O.; Kharitonov, I.A. An SEU (Single-event Upset) Mitigation Strategy on Read-Write Separation SRAM Cell for Low Power Consumption. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- Ding, L.; Cai, C.; Chen, G.; Wu, Z.; Zhang, J.; Wu, C.; Yu, J. Characterization of Single Event Upsets of Nanoscale FDSOI Circuits Based on the Simulation and Irradiation Results. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May 2022; pp. 2281–2285. [Google Scholar]

- Pal, S.; Sri, D.D.; Ki, W.H.; Islam, A. Highly Stable Low Power Radiation Hardened Memory-by-Design SRAM for Space Applications. IEEE Trans. Circuits Syst. II Express Briefs 2021, 58, 2147–2151. [Google Scholar] [CrossRef]

- Messenger, G.C. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

| RSNM/mV | WSNM/mV | HSNM/mV |

|---|---|---|

| 175.72 | 315.42 | 286.87 |

| Structure Name | Number of Sensitive Nodes | Tolerance SEU? | Tolerance Type | Tolerance DNU? | Critical Charge/fC |

|---|---|---|---|---|---|

| STD-6T | 2 | No | - | No | - |

| Quatro-10T [22] | 4 | No | 1→0 | No | 25.30 |

| WE-Quatro-12T [23] | 4 | No | 1→0 | No | 35.47 |

| RHM-12T [24] | 3 | Yes | 1→0, 0→1 | Yes | 87.65 |

| RHD-12T [25] | 4 | No | 1→0 | Yes | 112.37 |

| RSP-14T [26] | 4 | Yes | 1→0, 0→1 | Yes | 140.45 |

| This Work | 3 | Yes | 1→0, 0→1 | Yes | >200 |

| Structure Name | Static Power /nW | Dynamic Power /μW | Area /μm2 | Write Time /ps | Read Time /ps | RSNW /mV | WSNW /mV | HSNW /mV |

|---|---|---|---|---|---|---|---|---|

| STD-6T | 5.83 | 22.42 | 0.58 | 10.32 | 90.68 | 100.4 | 215.92 | 178.39 |

| Quatro-10T [22] | 8.29 | 38.45 | 0.94 | 32.87 | 130.52 | 135.29 | 363.01 | 310.32 |

| WE-Quatro-12T [23] | 10.97 | 23.56 | 1.08 | 21.56 | 140.77 | 209.30 | 346.37 | 293.41 |

| RHM-12T [24] | 5.69 | 27.14 | 1.02 | 18.21 | 115.69 | 158.61 | 281.45 | 246.42 |

| RHD-12T [25] | 6.19 | 24.35 | 0.98 | 19.35 | 117.74 | 169.54 | 303.43 | 301.47 |

| RSP-14T [26] | 5.05 | 23.25 | 1.22 | 22.54 | 121.63 | 177.11 | 290.09 | 250.13 |

| This work | 5.89 | 24.09 | 0.96 | 16.45 | 114.77 | 175.72 | 315.42 | 286.87 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yao, R.; Lv, H.; Zhang, Y.; Chen, X.; Zhang, Y.; Liu, X.; Bai, G. A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications. Micromachines 2023, 14, 1305. https://doi.org/10.3390/mi14071305

Yao R, Lv H, Zhang Y, Chen X, Zhang Y, Liu X, Bai G. A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications. Micromachines. 2023; 14(7):1305. https://doi.org/10.3390/mi14071305

Chicago/Turabian StyleYao, Ruxue, Hongliang Lv, Yuming Zhang, Xu Chen, Yutao Zhang, Xingming Liu, and Geng Bai. 2023. "A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications" Micromachines 14, no. 7: 1305. https://doi.org/10.3390/mi14071305

APA StyleYao, R., Lv, H., Zhang, Y., Chen, X., Zhang, Y., Liu, X., & Bai, G. (2023). A High-Reliability 12T SRAM Radiation-Hardened Cell for Aerospace Applications. Micromachines, 14(7), 1305. https://doi.org/10.3390/mi14071305