Improving Performance of Al2O3/AlN/GaN MIS HEMTs via In Situ N2 Plasma Annealing

Abstract

1. Introduction

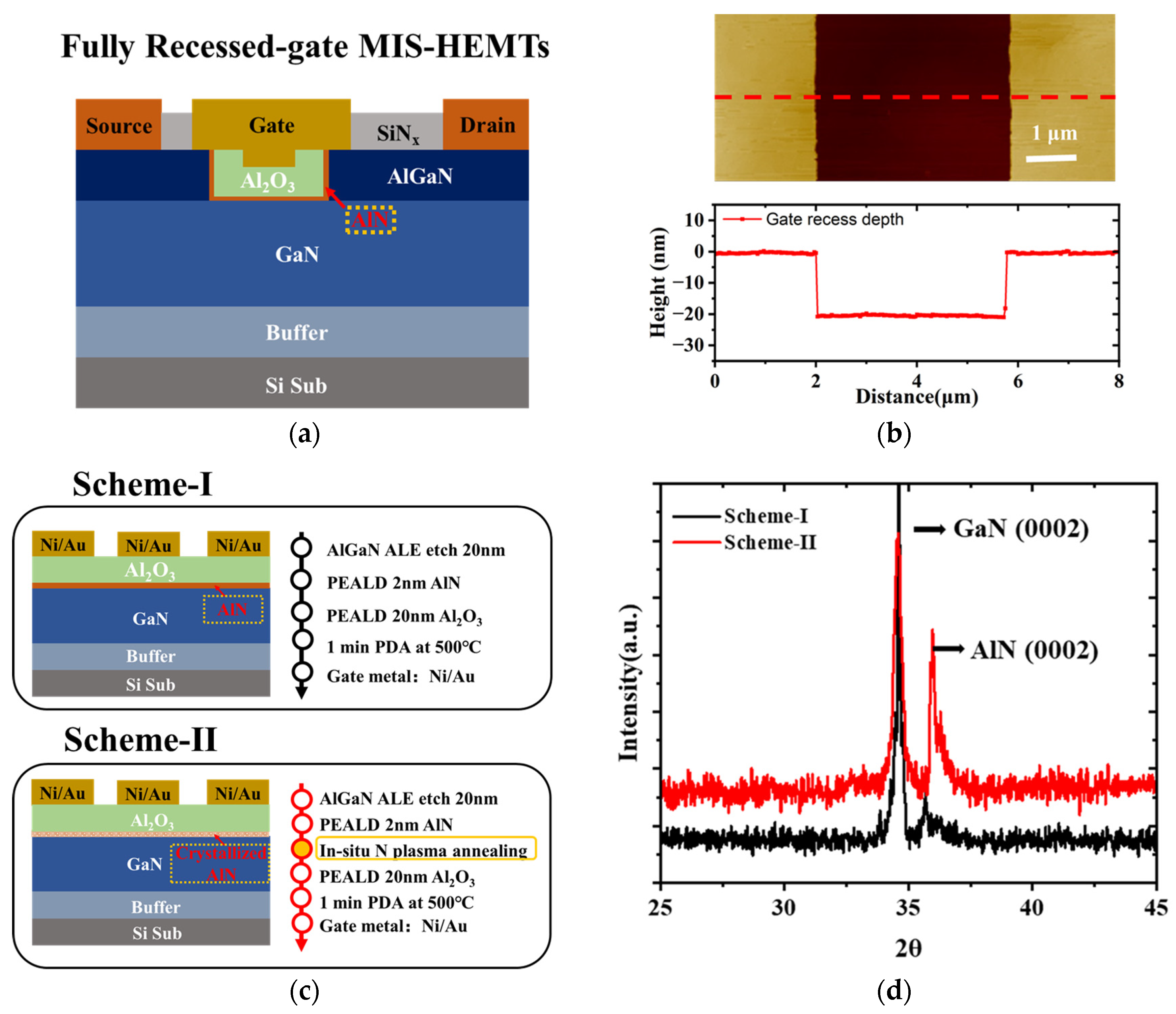

2. Device Structure and Fabrication

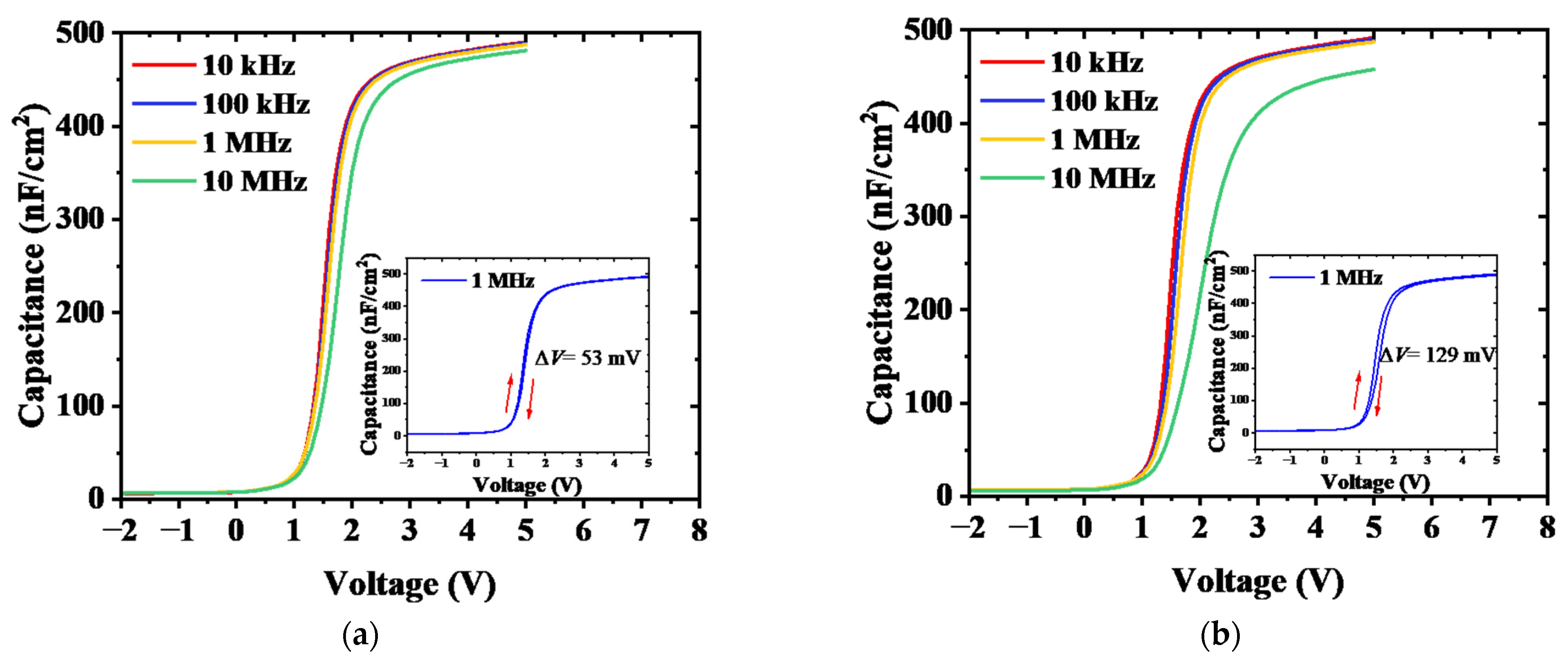

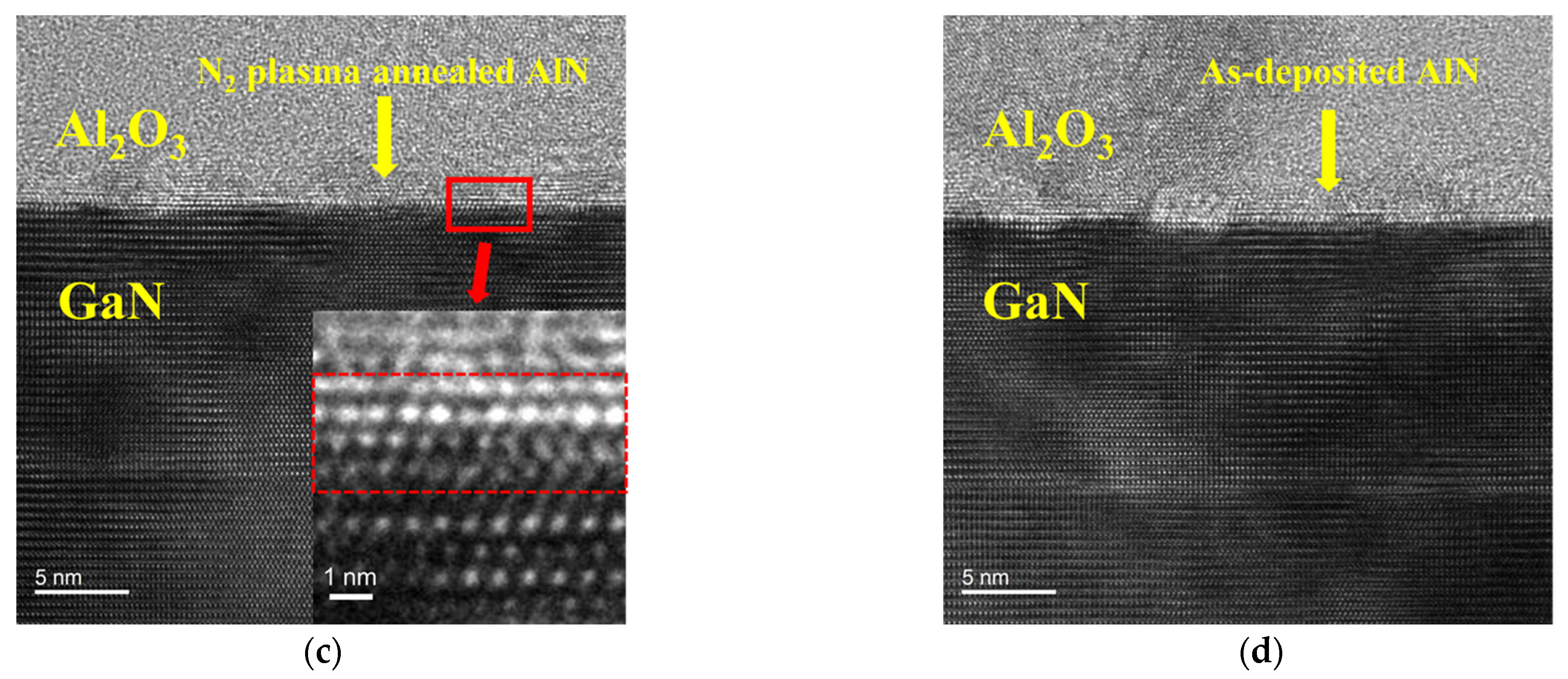

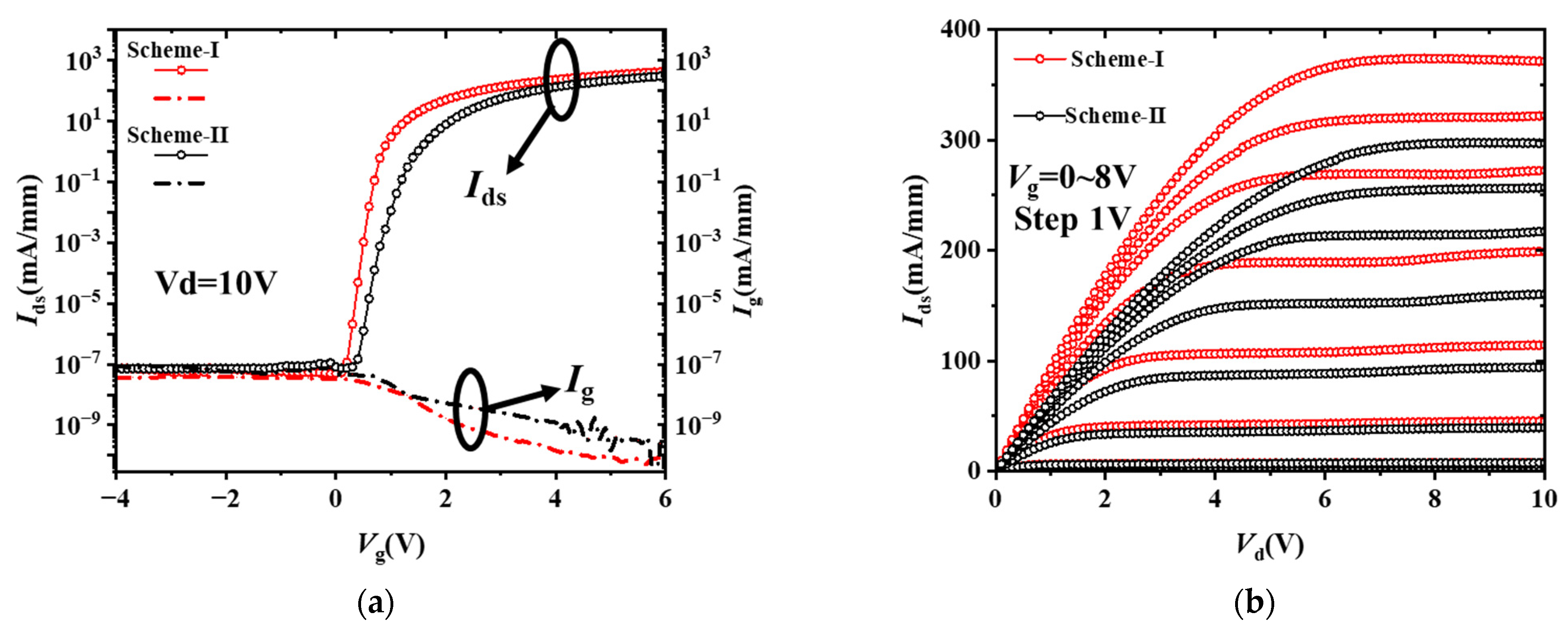

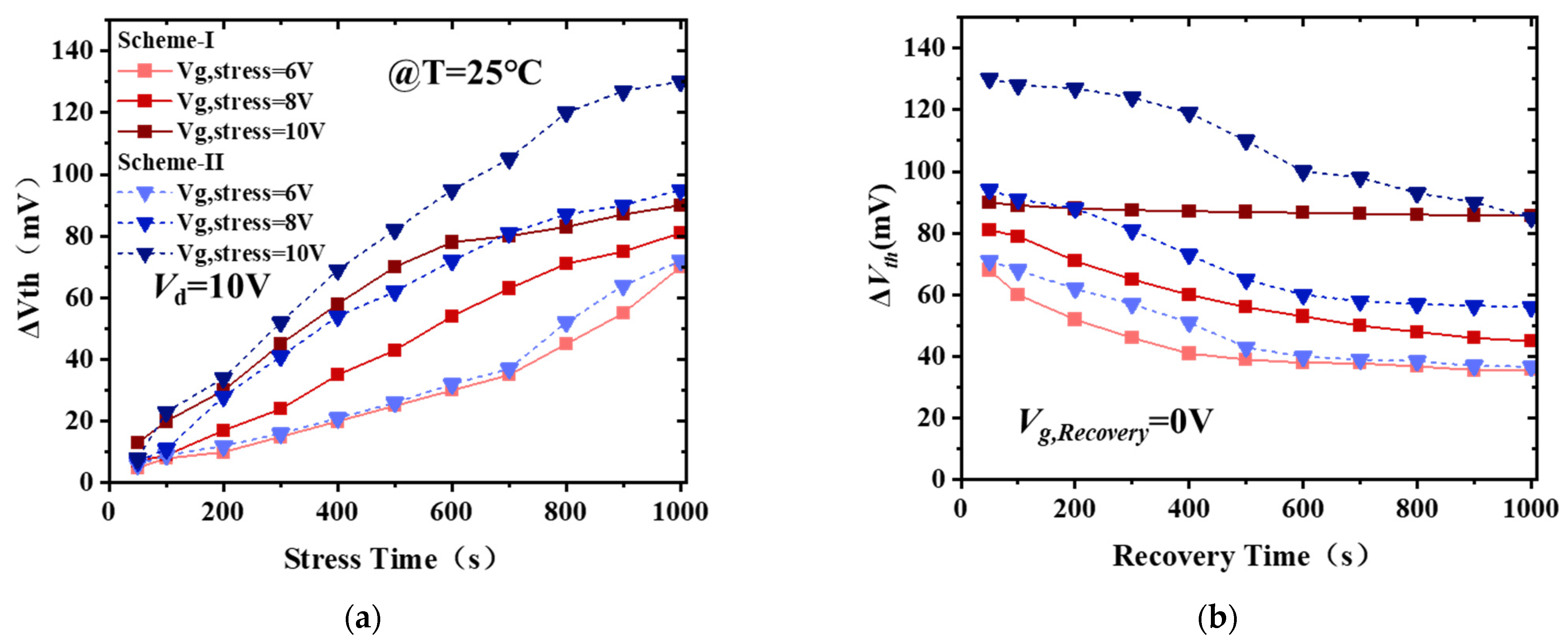

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Saito, Y.; Tsurumaki, R.; Noda, N.; Horio, K. Analysis of Reduction in Lag Phenomena and Current Collapse in Field-Plate AlGaN/GaN HEMTs with High Acceptor Density in a Buffer Layer. IEEE Trans. Device Mater. Reliab. 2017, 18, 46–53. [Google Scholar] [CrossRef]

- Sun, R.; Lai, J.; Chen, W.; Zhang, B. GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review. IEEE Access 2020, 8, 15529–15542. [Google Scholar] [CrossRef]

- Ajayan, J.; Nirmal, D.; Mohankumar, P.; Mounika, B.; Bhattacharya, S.; Tayal, S.; Fletcher, A.S. Challenges in material processing and reliability issues in AlGaN/GaN HEMTs on silicon wafers for future RF power electronics & switching applications: A critical review. Mater. Sci. Semicond. Process. 2022, 151, 106982. [Google Scholar] [CrossRef]

- Li, W.; Romanczyk, B.; Guidry, M.; Akso, E.; Hatui, N.; Wurm, C.; Liu, W.; Shrestha, P.; Collins, H.; Clymore, C.; et al. Record RF Power Performance at 94 GHz From Millimeter-Wave N-Polar GaN-on-Sapphire Deep-Recess HEMTs. IEEE Trans. Electron Devices 2023, 70, 2075–2080. [Google Scholar] [CrossRef]

- Mounika, B.; Ajayan, J.; Bhattacharya, S.; Nirmal, D. Recent developments in materials, architectures and processing of AlGaN/GaN HEMTs for future RF and power electronic applications: A critical review. Micro Nanostruct. 2022, 168, 207317. [Google Scholar] [CrossRef]

- Pu, T.; Younis, U.; Chiu, H.C.; Xu, K.; Kuo, H.C.; Liu, X. Review of Recent Progress on Vertical GaN-Based PN Diodes. Nanoscale Res. Lett. 2021, 16, 101. [Google Scholar] [CrossRef]

- Meneghini, M.; De Santi, C.; Abid, I.; Buffolo, M.; Cioni, M.; Khadar, R.A.; Nela, L.; Zagni, N.; Chini, A.; Medjdoub, F.; et al. GaN-based power devices: Physics, reliability, and perspectives. J. Appl. Phys. 2021, 130, 181101. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Lau, K.M.; Chen, K.J. Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode. IEEE Trans. Electron Devices 2006, 53, 2207–2215. [Google Scholar] [CrossRef]

- Zhou, K.; Shan, L.; Zhang, Y.; Lu, D.; Ma, Y.; Chen, X.; Luo, L.; Wu, C. Fluorine Plasma Treatment for AlGaN/GaN HEMT-Based Ultraviolet Photodetector with High Responsivity and High Detectivity. IEEE Electron Device Lett. 2023, 44, 781–784. [Google Scholar] [CrossRef]

- Hwang, I.; Kim, J.; Choi, H.S.; Choi, H.; Lee, J.; Kim, K.Y.; Park, J.B.; Lee, J.C.; Ha, J.; Oh, J.; et al. p-GaN Gate HEMTs With Tungsten Gate Metal for High Threshold Voltage and Low Gate Current. IEEE Electron Device Lett. 2013, 34, 202–204. [Google Scholar] [CrossRef]

- Huang, S.; Liu, X.; Wang, X.; Kang, X.; Zhang, J.; Fan, J.; Shi, J.; Wei, K.; Zheng, Y.; Gao, H.; et al. Ultrathin-Barrier AlGaN/GaN Heterostructure: A Recess-Free Technology for Manufacturing High-Performance GaN-on-Si Power Devices. IEEE Trans. Electron Devices 2017, 65, 207–214. [Google Scholar] [CrossRef]

- Hsieh, T.E.; Chang, E.Y.; Song, Y.Z.; Lin, Y.C.; Wang, H.C.; Liu, S.C.; Salahuddin, S.; Hu, C.C. Gate Recessed Quasi-Normally OFF Al2O3/AlGaN/GaN MIS-HEMT With Low Threshold Voltage Hysteresis Using PEALD AlN Interfacial Passivation Layer. IEEE Electron Device Lett. 2014, 35, 732–734. [Google Scholar] [CrossRef]

- He, Y.; Gao, H.; Wang, C.; Zhao, Y.; Lu, X.; Zhang, C.; Zheng, X.; Guo, L.; Ma, X.; Hao, Y. Comparative Study Between Partially and Fully Recessed-Gate Enhancement-Mode AlGaN/GaN MIS HEMT on the Breakdown Mechanism. Phys. Status Solidi (A) 2019, 216, 1900115. [Google Scholar] [CrossRef]

- Buttari, D.; Chini, A.; Chakraborty, A.; Mccarthy, L.; Xing, H.; Palacios, T.; Shen, L.; Keller, S.; Mishra, U.K. Selective dry etching of GaN over AlGaN in BCl3/SF6 mixtures. In Proceedings of the IEEE Lester Eastman Conference on High Performance Devices, Troy, NY, USA, 4–6 August 2004. [Google Scholar]

- Chen, K.J.; Yang, S.; Tang, Z.; Huang, S.; Lu, Y.; Jiang, Q.; Liu, S.; Liu, C.; Li, B. Surface nitridation for improved dielectric/III-nitride interfaces in GaN MIS-HEMTs. Phys. Status Solidi (A) 2015, 212, 1059–1065. [Google Scholar] [CrossRef]

- Kanamura, M.; Ohki, T.; Kikkawa, T.; Imanishi, K.; Hara, N. Enhancement-mode GaN MIS-HEMTs with n-GaN/i-AlN/n-GaN triple cap layer and high-κ gate dielectrics. IEEE Electron Device Lett. 2010, 31, 189–191. [Google Scholar] [CrossRef]

- Liu, S.; Yang, S.; Tang, Z.; Jiang, Q.; Liu, C.; Wang, M.; Shen, B.; Chen, K.J. Interface/border trap characterization of Al2O3/AlN/GaN metal-oxide-semiconductor structures with an AlN interfacial layer. Appl. Phys. Lett. 2015, 106, 295–298. [Google Scholar] [CrossRef]

- Hinkle, C.L.; Milojević, M.; Brennan, B.; Sonnet, A.M.; Aguirre-Tostado, F.S.; Hughes, G.; Vogel, E.M.; Wallace, R.M. Detection of Ga suboxides and their impact on III-V passivation and Fermi-level pinning. Appl. Phys. Lett. 2009, 94, 162101. [Google Scholar] [CrossRef]

- Robertson, J. Model of interface states at III-V oxide interfaces. Appl. Phys. Lett. 2009, 94, 152104. [Google Scholar] [CrossRef]

- Gao, F.; Lee, S.J.; Li, R.; Whang, S.J.; Balakumar, S.; Chi, D.Z.; Kean, C.C.; Vicknesh, S.; Tung, C.H.; Kwong, D.L. GaAs p- and n-MOS devices integrated with novel passivation (plasma nitridation and AlN-surface passivation) techniques and ALD-HfO2/TaN gate stack. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Losurdo, M.; Capezzuto, P.; Bruno, G.; Perna, G.; Capozzi, V. N2–H2N2–H2 remote plasma nitridation for GaAs surface passivation. Appl. Phys. Lett. 2002, 81, 16–18. [Google Scholar] [CrossRef]

- Romero, M.F.; JimÉnezJimenez, A.; Miguel-SÁnchezMiguel-Sanchez, J.; BraÑaBrana, A.F.; GonzÁlez-PosadaGonzalez-Posada, F.; Cuerdo, R.; Calle, F.; MuÑozMunoz, E. Effects of Plasma Pretreatment on the SiN Passivation of AlGaN/GaN HEMT. Electron Device Lett. 2008, 29, 209–211. [Google Scholar] [CrossRef]

- Romero, A.; Jiménez, F.; González-Posada, S.; Martín-Horcajo, F.C.; Muñoz, E. Impact of N2 Plasma Power Discharge on AlGaN/GaN HEMT Performance. IEEE Trans. Electron Devices 2012, 59, 374–379. [Google Scholar] [CrossRef]

- Chen, K.J.; Huang, S. AlN passivation by plasma-enhanced atomic layer deposition for GaN-based power switches and power amplifiers. Semicond. Sci. Technol. 2013, 28, 074015. [Google Scholar] [CrossRef]

- Liu, S.; Yang, S.; Tang, Z.; Jiang, Q.; Liu, C.; Wang, M.; Chen, K.J. Al2O3/AlN/GaN MOS-Channel-HEMTs With an AlN Interfacial Layer. IEEE Electron Device Lett. 2014, 35, 723–725. [Google Scholar] [CrossRef]

- Koshelev, O.A.; Nechaev, D.V.; Brunkov, P.N.; Ivanov, S.V.; Jmerik, V.N. Stress control in thick AlN/c-Al2O3 templates grown by plasma-assisted molecular beam epitaxy. Semicond. Sci. Technol. 2021, 36, 035007. [Google Scholar] [CrossRef]

- Kakanakova-Georgieva, A.; Ivanov, I.G.; Suwannaharn, N.; Hsu, C.W.; Cora, I.; Pécz, B.; Giannazzo, F.; Sangiovanni, D.G.; Gueorguiev, G.K. MOCVD of AlN on epitaxial graphene at extreme temperatures. CrystEngComm 2021, 23, 385–390. [Google Scholar] [CrossRef]

- Xie, H.; Liu, Z.; Hu, W.; Zhong, Z.; Lee, K.; Guo, Y.X.; Ng, G.I. GaN-on-Si HEMTs Fabricated With Si CMOS-Compatible Metallization for Power Amplifiers in Low-Power Mobile SoCs. IEEE Microw. Wirel. Compon. Lett. A Publ. IEEE Microw. Theory Tech. Soc. 2021, 31, 141–144. [Google Scholar] [CrossRef]

- Liu, S.; Peng, M.; Hou, C.; He, Y.; Li, M.; Zheng, X. PEALD-Grown Crystalline AlN Films on Si (100) with Sharp Interface and Good Uniformity. Nanoscale Res. Lett. 2017, 12, 279. [Google Scholar] [CrossRef]

- Marcon, D.; Hove, M.V.; Jaeger, B.D.; Posthuma, N.; Decoutere, S. Direct comparison of GaN-based e-mode architectures (recessed MISHEMT and p-GaN HEMTs) processed on 200mm GaN-on-Si with Au-free technology. Proc. SPIE-Int. Soc. Opt. Eng. 2015, 9363, 117–128. [Google Scholar] [CrossRef]

- Ramanan, N.; Lee, B.; Misra, V. Comparison of Methods for Accurate Characterization of Interface Traps in GaN MOS-HFET Devices. IEEE Trans. Electron Devices 2015, 62, 546–553. [Google Scholar] [CrossRef]

- Lagger, P.; Reiner, M.; Pogany, D.; Ostermaier, C. Comprehensive Study of the Complex Dynamics of Forward Bias-Induced Threshold Voltage Drifts in GaN Based MIS-HEMTs by Stress/Recovery Experiments. IEEE Trans. Electron Devices 2014, 61, 1022–1030. [Google Scholar] [CrossRef]

- Wu, T.L.; Marcon, D.; Bakeroot, B.; De Jaeger, B.; Lin, H.C.; Franco, J.; Stoffels, S.; Van Hove, M.; Roelofs, R.; Groeseneken, G.; et al. Correlation of interface states/border traps and threshold voltage shift on AlGaN/GaN metal-insulator-semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2015, 107, 93507. [Google Scholar] [CrossRef]

- Kuo, H.M.; Chang, T.C.; Chang, K.C.; Lin, H.N.; Kuo, T.T.; Yeh, C.H.; Lee, Y.H.; Lin, J.H.; Tsai, X.Y.; Huang, J.W.; et al. Investigation of Threshold Voltage and Drain Current Degradations in Si3N4/AlGaN/GaN MIS-HEMTs Under X-Ray Irradiation. IEEE Trans. Electron Devices 2023, 70, 2216–2221. [Google Scholar] [CrossRef]

- Wu, T.L.; Marcon, D.; Jaeger, B.D.; Hove, M.V.; Decoutere, S. The impact of the gate dielectric quality in developing Au-free D-mode and E-mode recessed gate AlGaN/GaN transistors on a 200mm Si substrate. In Proceedings of the 27th International Symposium on Power Semiconductor Devices and ICs, Hong Kong, China, 10–14 May 2015. [Google Scholar] [CrossRef]

| Power/W | Time/s | AlN Property |

|---|---|---|

| 100 | 100 | amorphous |

| 100 | 300 | amorphous |

| 100 | 500 | amorphous |

| 200 | 100 | Weak signal in AlN (0002) |

| 200 | 300 | monocrystalline |

| 200 | 500 | monocrystalline |

| 300 | 100 | monocrystalline |

| 300 | 300 | monocrystalline |

| 300 | 500 | Weak signal in AlN (0002) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, M.; Wang, L.; Zhang, P.; Chen, K. Improving Performance of Al2O3/AlN/GaN MIS HEMTs via In Situ N2 Plasma Annealing. Micromachines 2023, 14, 1100. https://doi.org/10.3390/mi14061100

Sun M, Wang L, Zhang P, Chen K. Improving Performance of Al2O3/AlN/GaN MIS HEMTs via In Situ N2 Plasma Annealing. Micromachines. 2023; 14(6):1100. https://doi.org/10.3390/mi14061100

Chicago/Turabian StyleSun, Mengyuan, Luyu Wang, Penghao Zhang, and Kun Chen. 2023. "Improving Performance of Al2O3/AlN/GaN MIS HEMTs via In Situ N2 Plasma Annealing" Micromachines 14, no. 6: 1100. https://doi.org/10.3390/mi14061100

APA StyleSun, M., Wang, L., Zhang, P., & Chen, K. (2023). Improving Performance of Al2O3/AlN/GaN MIS HEMTs via In Situ N2 Plasma Annealing. Micromachines, 14(6), 1100. https://doi.org/10.3390/mi14061100