PCCNoC: Packet Connected Circuit as Network on Chip for High Throughput and Low Latency SoCs

Abstract

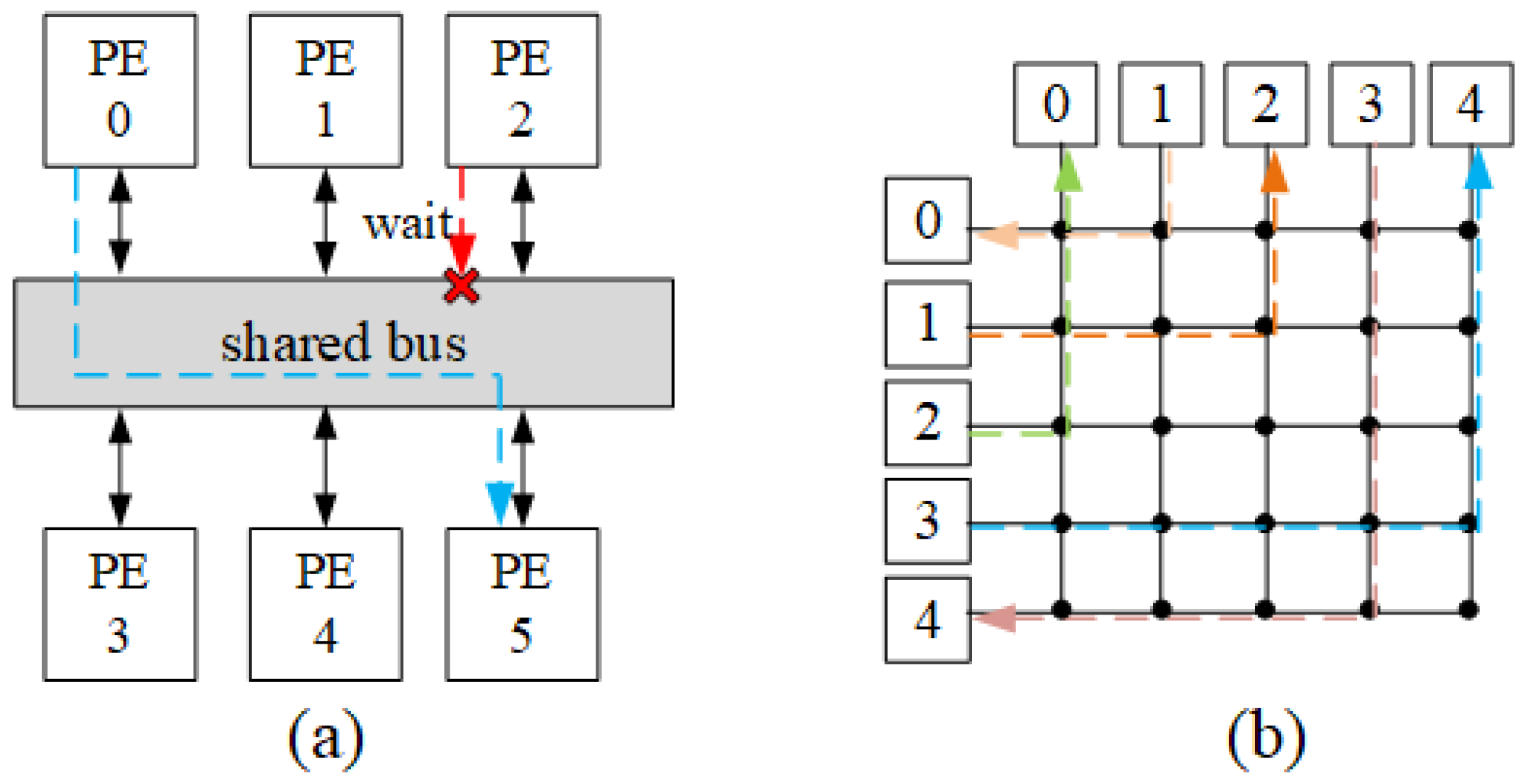

1. Introduction

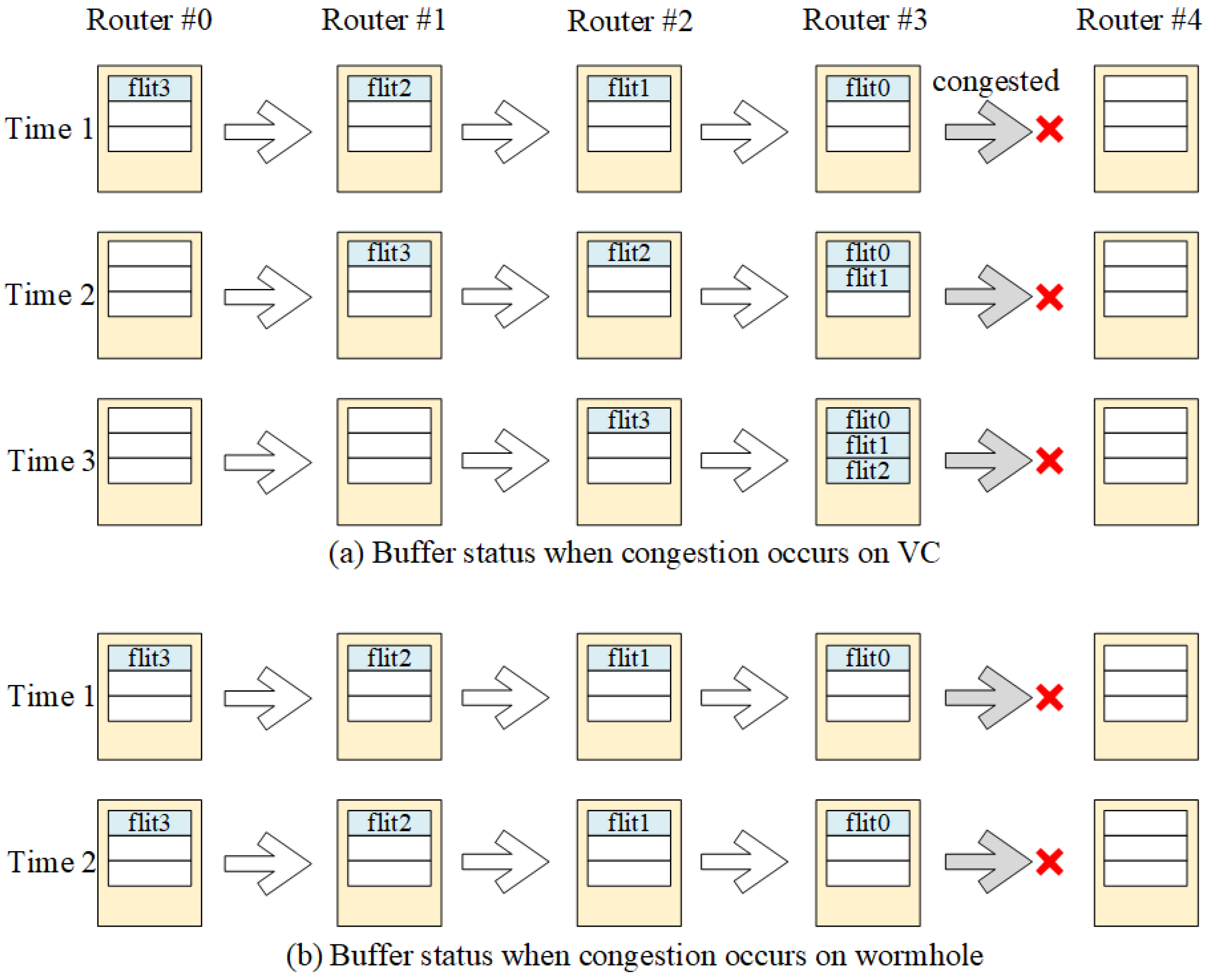

2. Related Work

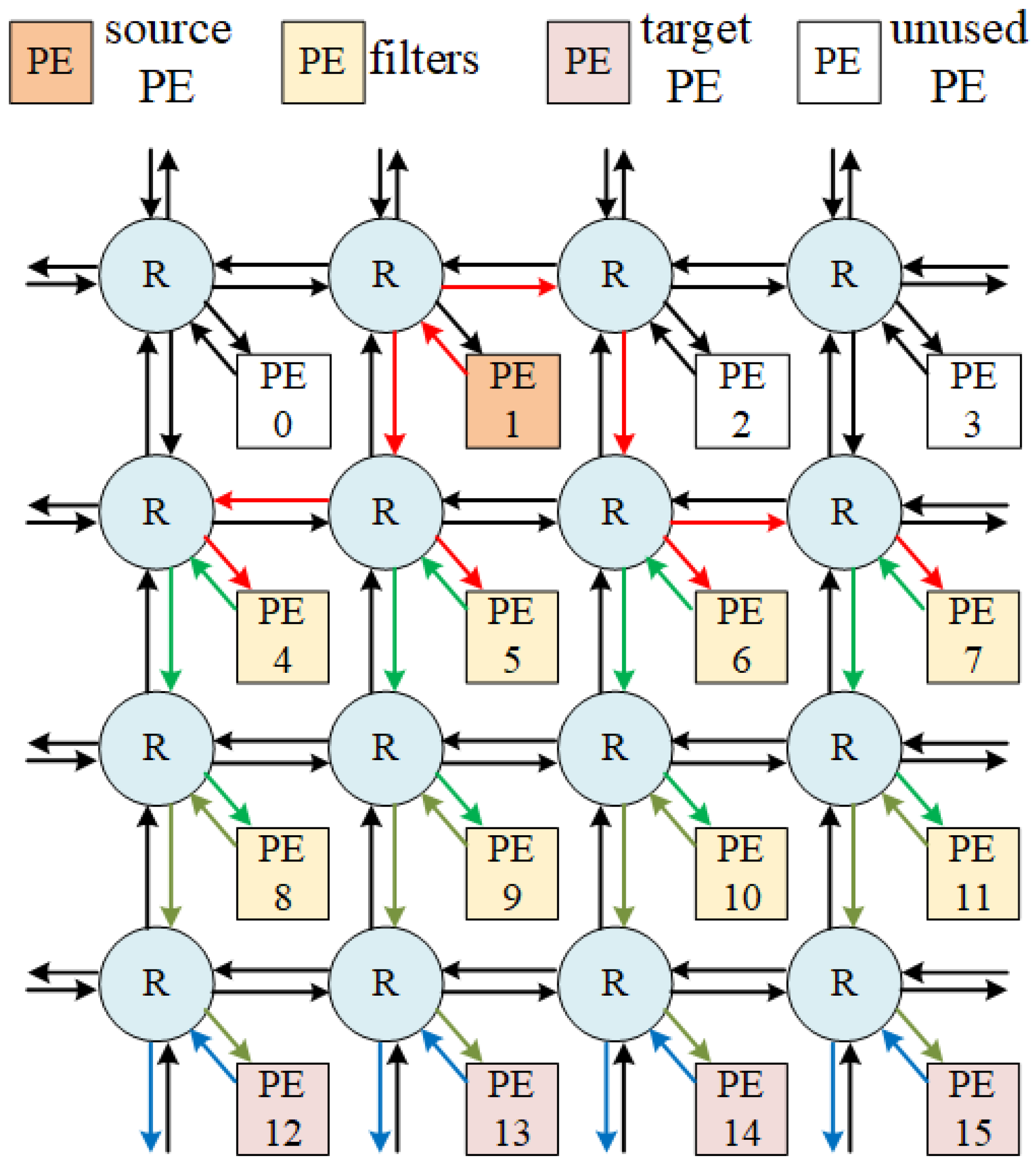

3. Proposed Architecture

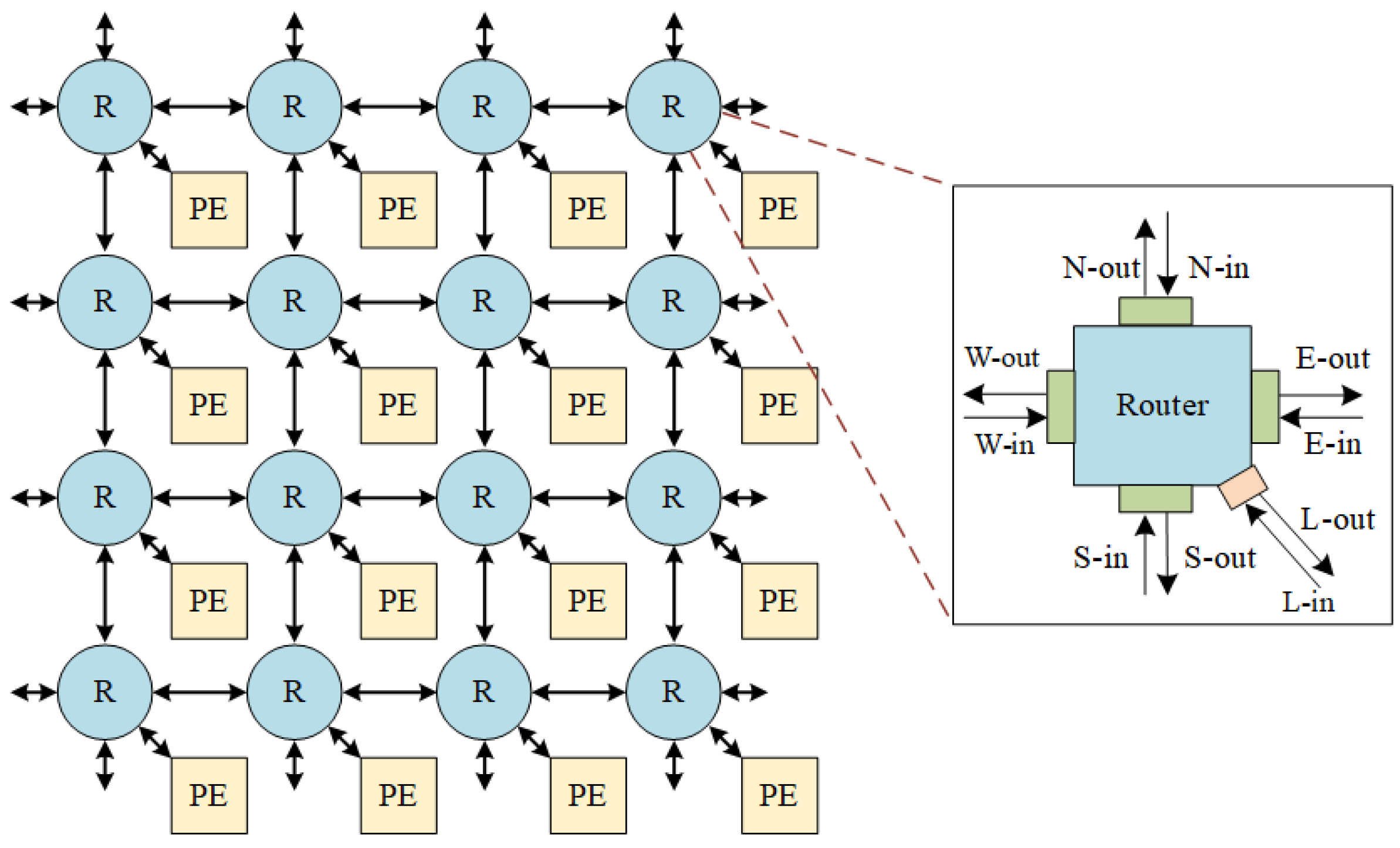

3.1. PCCNoC Design

- Processor. The writing bus of data storage (Lin) or program memory or configuration memory (Lin) are connected; the reading bus of data storage (Lout) is connected.

- Function module. The writing bus of data storage (Lin) and configuration register (Lin) are connected; the reading bus of data storage (Lout) is connected.

- Memory. The write port input to the data memory (Lin) is connected to the router; the read port of the data memory (Lout) is connected to the router.

- Interface (I/O). The router connects the interface (I/O), and the DMA inside the node provides subsequent data transmission.

3.2. Router Design

- Routing source (RS): the node that initiates the transmission request;

- Routing target (RT): the node that accepts the transmission request;

- Data sender (DS): the node that sends data, which can be RS or RT;

- Data receiver (DR): the node that receives data, which can be RS or RT.

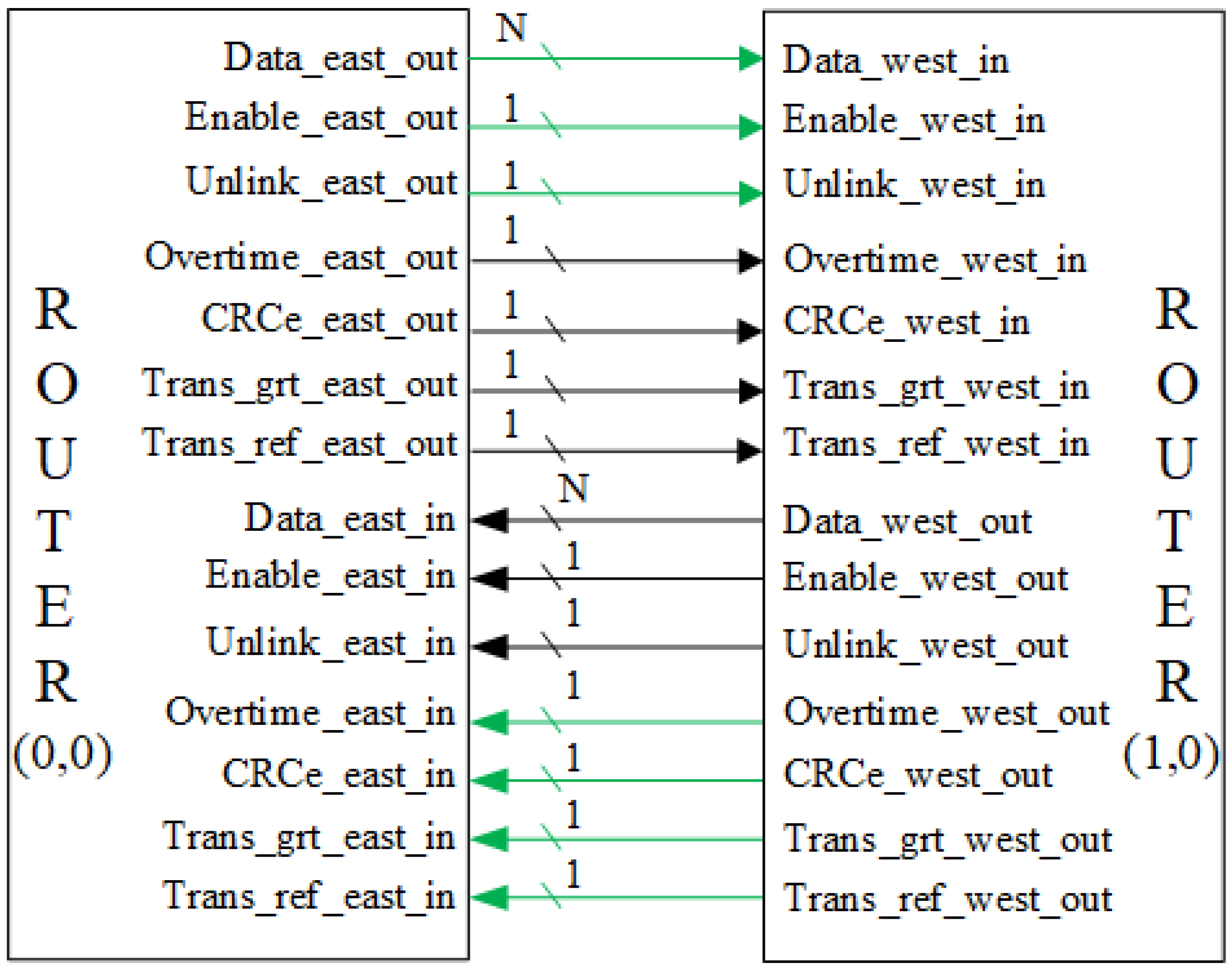

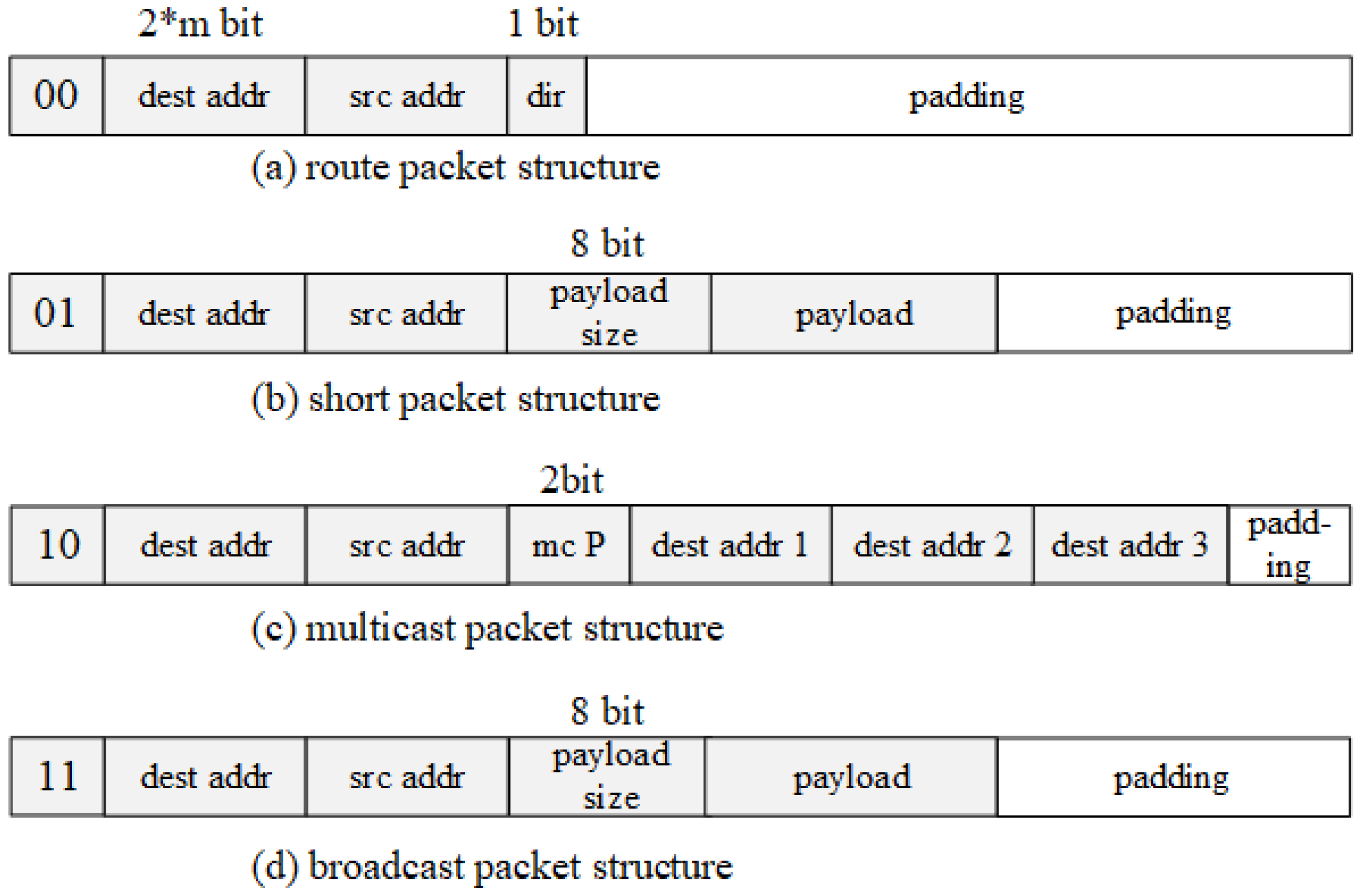

3.3. Interface Structure

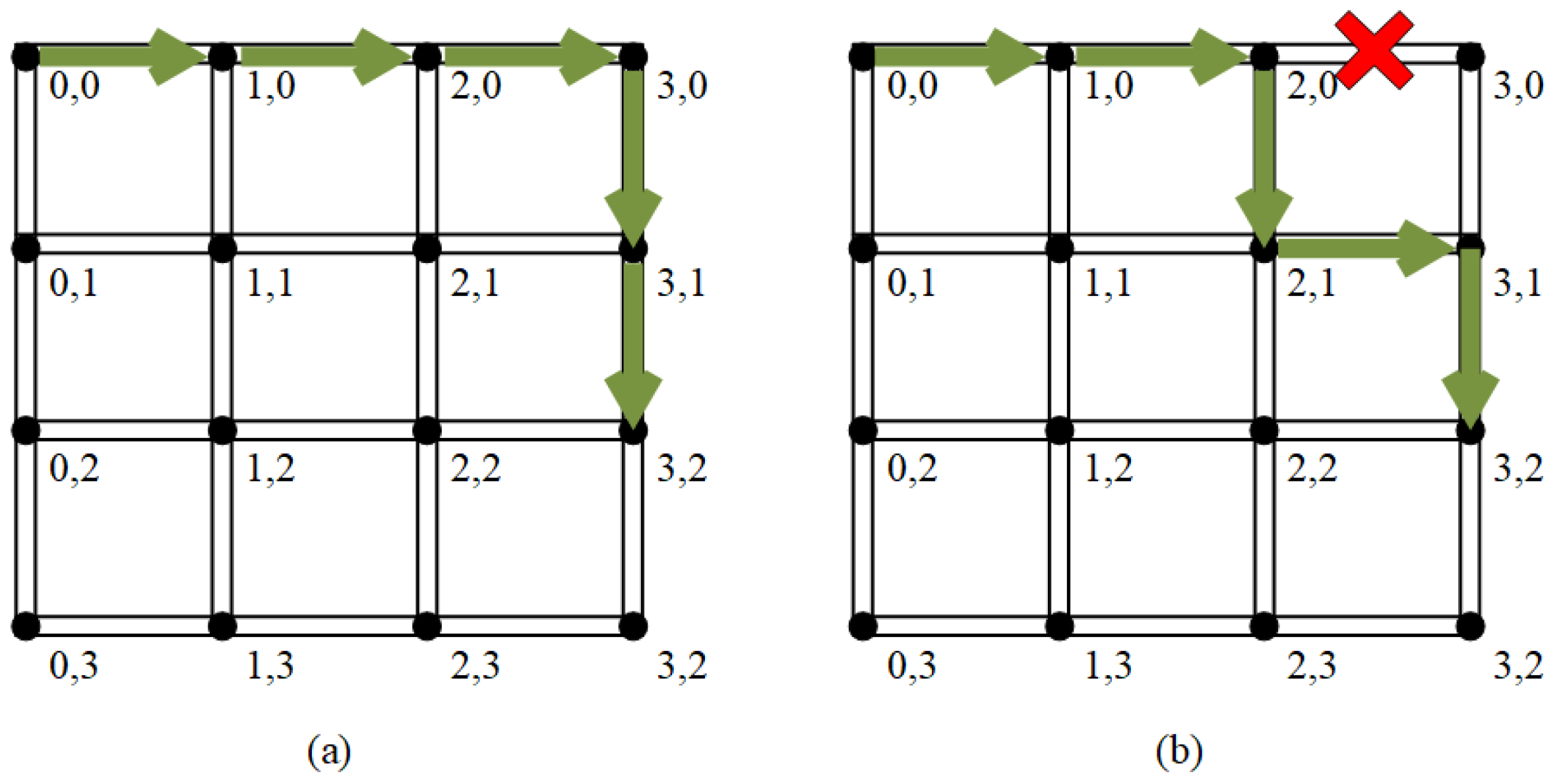

3.4. Routing Algorithm

- The address codes of the two sections are X for east–west (the east is bigger) and Y for south–north (the north is bigger).

- When routing, the address of target node is compared with the local node address. When the X address of target node is bigger, they move eastward, and vice versa; when the Y address of target node is bigger, they move northward, and vice versa;

- The routing decision of each routing node needs to take the congestion of the surrounding routing nodes into account. The X direction has higher priority.

4. The NoC Workflow

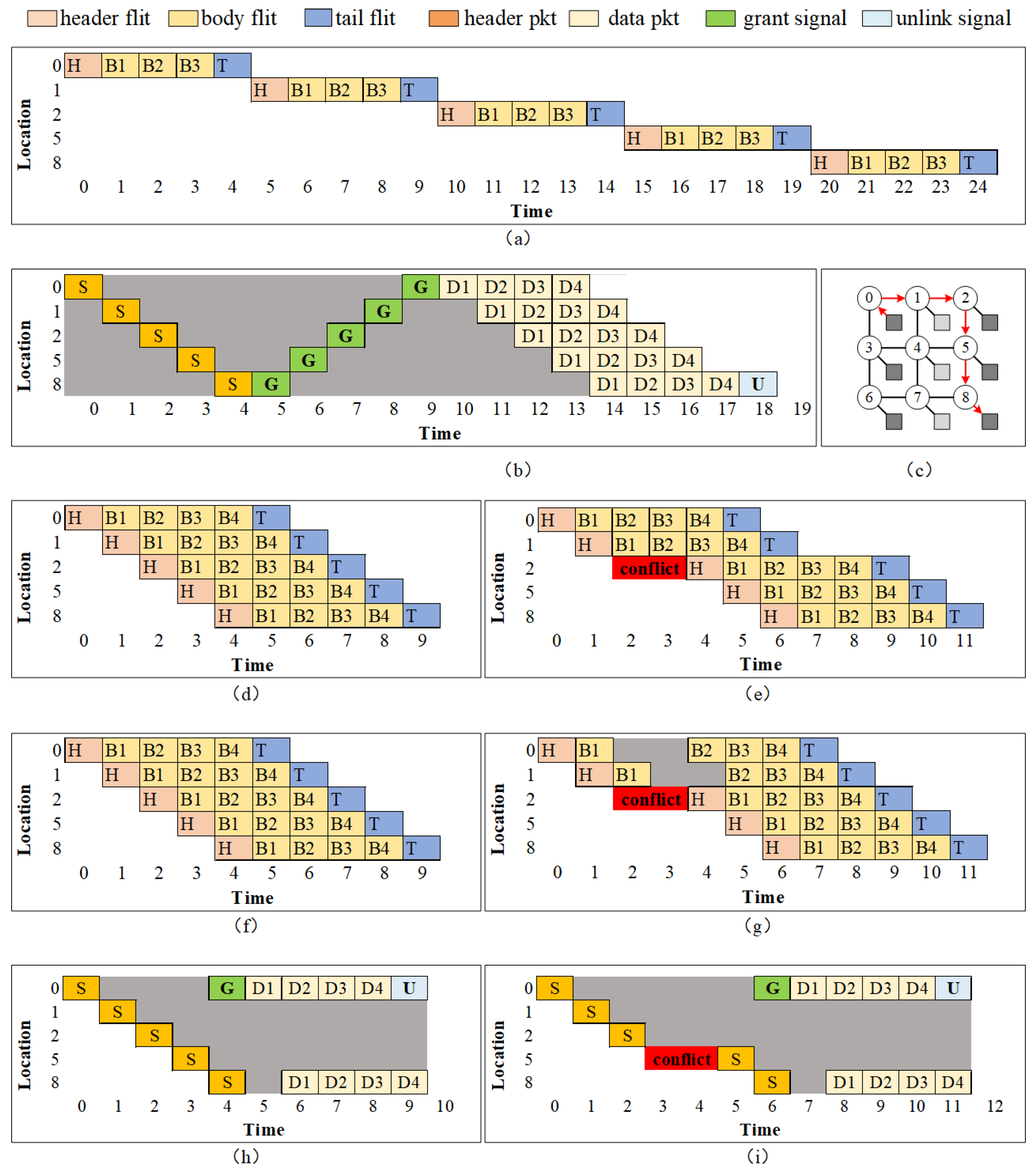

4.1. Transmission Mechanism

- The router keeps a record of the occupancy of adjacent nodes.

- According to the destination address of the route and the occupancy status of adjacent nodes, temporarily lock the inport and outport paths of the node according to data transfer direction, and send routing packets to the determined direction.

- The routers along the transmitting path lock circuit to establish a directional locked data path.

- The routing target node confirms the transmission request.

- The routers along the transmitting path keep to support payload transmission.

- The routing source node is equipped with timeout control, and the transmission with abnormal timeout will be terminated and reported to the system.

4.2. Multicast and Broadcast

4.3. Short Packet

4.4. Pipelines

- Routing pipelines are used by the router to perform the routing function and other control information calculation. The routing packet consumes one clock at each node.

- Data transmission pipelines are the pipelines used by router for the data transmission circuit. The data transmission circuit of each node can be set as a combination circuit or a pipeline register. Along the locked data path, most nodes are set as combination logic while few intermediate nodes are set to pipeline register according to the length of the whole path. The information about which nodes are set as pipeline registers is calculated by routing source.

- If CRC is acquired, extra clock cycles are needed by the data sender and data receiver according to the port bandwidth. However, when parallel CRC is designed using Galois matrix, the extra cycle cost can be negligible.

5. Implementation and Evaluation

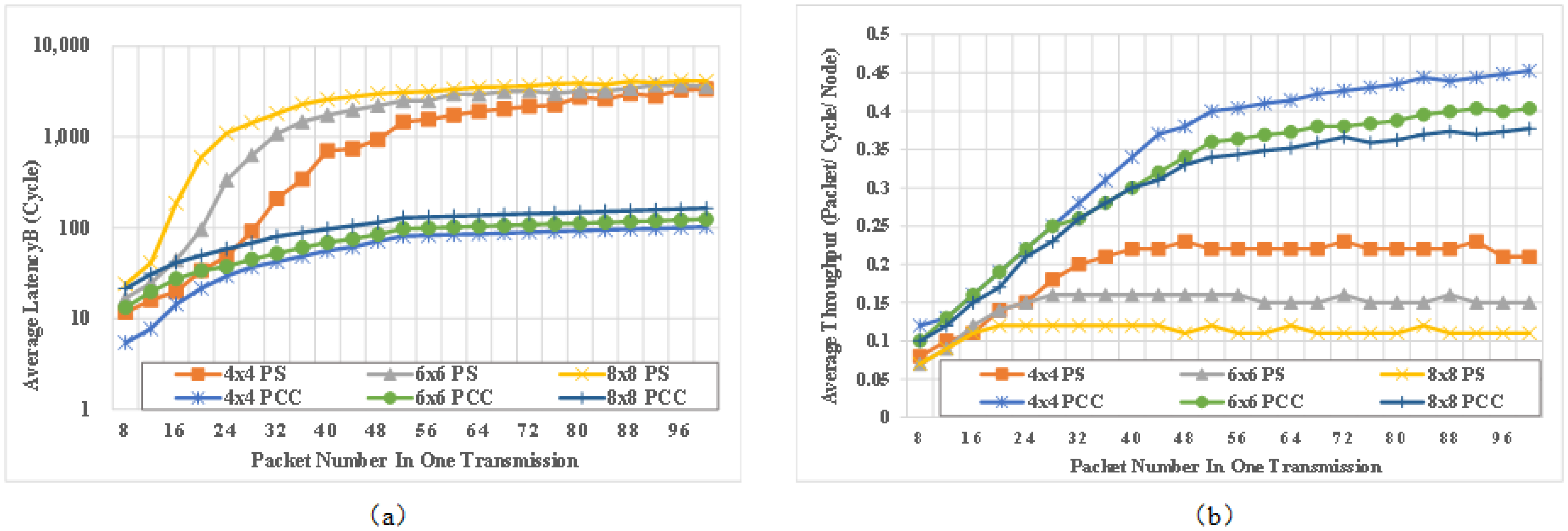

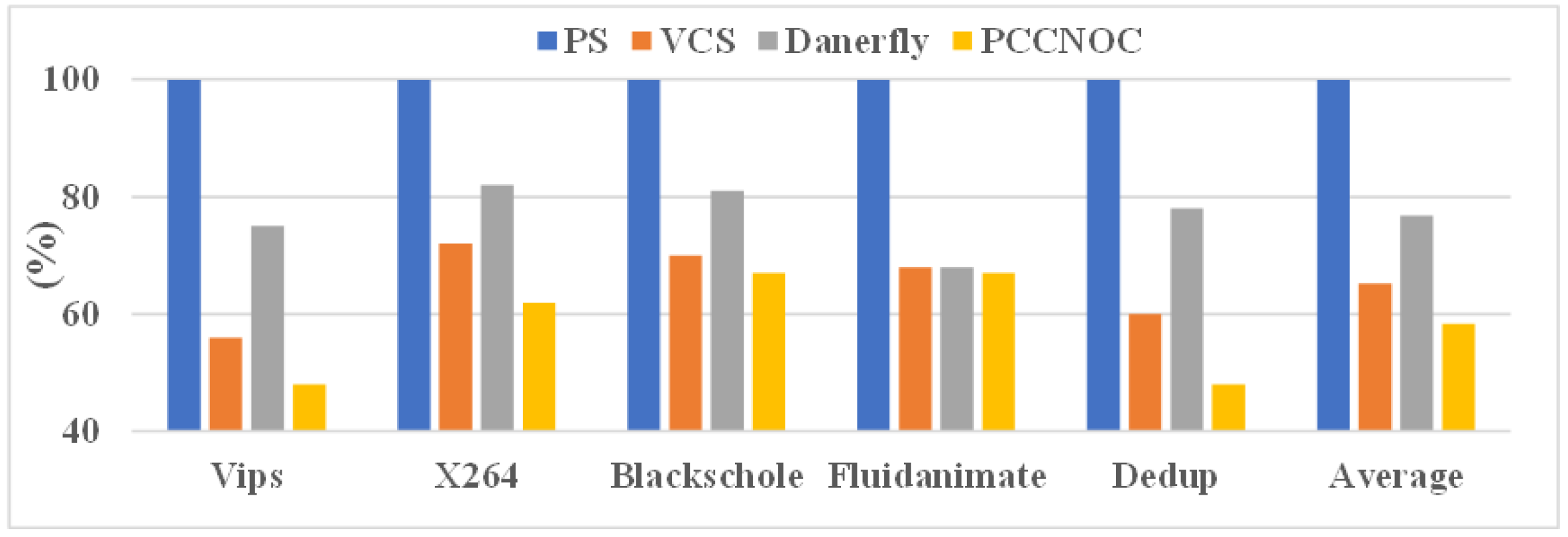

5.1. Latency and Throughput

5.2. Configuration Time

5.3. Synthesis Result

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bennett, H. International Technology Roadmap for Semiconductors 2015 Edition Outside System Connectivity. 2015. Available online: https://www.nist.gov/publications/international-technology-roadmap-semiconductors-2015-edition-outside-system (accessed on 12 February 2023).

- Wang, C.; Bagherzadeh, N. Design and evaluation of a high throughput QoS-aware and congestion-aware router architecture for Network-on-Chip. Microprocess. Microsyst. 2014, 38, 304–315. [Google Scholar] [CrossRef]

- Balasubramonian, R.; Pinkston, T.M. Buses and Crossbars; Springer: Berlin/Heidelberg, Germany, 2011. [Google Scholar]

- Jantsch, A.; Tenhunen, H. Networks on chip. IEEE Trans. Comput. 2010, 57, 1216–1229. [Google Scholar]

- Dally, W.J.; Towles, B.P. Principles and Practices of Interconnection Networks; Elsevier: Amsterdam, The Netherlands, 2004. [Google Scholar]

- Liu, S.; Jantsch, A.; Lu, Z. Analysis and Evaluation of Circuit Switched NoC and Packet Switched NoC. In Proceedings of the 2013 Euromicro Conference on Digital System Design, Los Alamitos, CA, USA, 4–6 September 2013. [Google Scholar]

- Das, T.S.; Ghosal, P.; Chatterjee, N. VCS: A Method of In-order Packet Delivery for Adaptive NoC Routing. Nano Commun. Netw. 2020, 28, 100333. [Google Scholar] [CrossRef]

- Lee, Y.S.; Kim, Y.W.; Han, T.H. MRCN: Throughput-Oriented Multicast Routing for Customized Network-on-Chips. IEEE Trans. Parallel Distrib. Syst. 2022, 34, 163–179. [Google Scholar] [CrossRef]

- Yang, M.C.; Lee, Y.S.; Han, T.H. MRBS: An Area-Efficient Multicast Router for Network-on-Chip Using Buffer Sharing. IEEE Access 2021, 9, 168783–168793. [Google Scholar] [CrossRef]

- Anjali, N.; Somasundaram, K. Design and evaluation of virtual channel router for mesh-of-grid based NoC. In Proceedings of the 2014 International Conference on Electronics and Communication Systems (ICECS), Coimbatore, India, 13–14 February 2014; pp. 1–5. [Google Scholar]

- Monemi, A.; Tang, J.W.; Palesi, M.; Marsono, M.N. ProNoC: A low latency network-on-chip based many-core system-on-chip prototyping platform. Microprocess. Microsyst. 2017, 54, 60–74. [Google Scholar] [CrossRef]

- González, Y.R.; Nelissen, G.; Tovar, E. IPDeN: Real-Time deflection-based NoC with in-order flits delivery. In Proceedings of the 2022 IEEE 28th International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), Taipei, Taiwan, 23–25 August 2022; pp. 160–169. [Google Scholar]

- Tobuschat, S.; Axer, P.; Ernst, R.; Diemer, J. IDAMC: A NoC for mixed criticality systems. In Proceedings of the 2013 IEEE 19th International Conference on Embedded and Real-Time Computing Systems and Applications, Taipei, Taiwan, 19–21 August 2013; pp. 149–156. [Google Scholar]

- Konstantinou, D.; Nicopoulos, C.; Lee, J.; Sirakoulis, G.C.; Dimitrakopoulos, G. SmartFork: Partitioned multicast allocation and switching in network-on-chip routers. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar]

- Jin, K.; Dong, D.; Li, C.; Huang, L.; Ma, S.; Fu, B. DancerFly: An Order-Aware Network-on-Chip Router On-the-Fly Mitigating Multi-path Packet Reordering. Int. J. Parallel Program. 2020, 48, 730–749. [Google Scholar] [CrossRef]

- Bahrebar, P.; Stroobandt, D. The Hamiltonian-based odd-even turn model for maximally adaptive routing in 2D mesh networks-on-chip. Comput. Electr. Eng. 2015, 45, 386–401. [Google Scholar] [CrossRef]

- Liu, D. Embedded DSP Processor Design: Application Specific Instruction Set Processors; Elsevier: Amsterdam, The Netherlands, 2008. [Google Scholar]

- Das, T.S.; Ghosal, P.; Chatterjee, N. Virtual circuit switch based orderly delivery of packets in adaptive noc routing. In Proceedings of the 12th International Workshop on Network on Chip Architectures, Columbus, OH, USA, 13 October 2019; pp. 1–6. [Google Scholar]

- Asgarieh, Y.; Lin, B. Smart-hop arbitration request propagation: Avoiding quadratic arbitration complexity and false negatives in SMART NoCs. ACM Trans. Des. Autom. Electron. Syst. (TODAES) 2019, 24, 1–25. [Google Scholar] [CrossRef]

- Zheng, H.; Wang, K.; Louri, A. Adapt-noc: A flexible network-on-chip design for heterogeneous manycore architectures. In Proceedings of the 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Seoul, Republic of Korea, 27 February–3 March 2021; pp. 723–735. [Google Scholar]

- Kwon, H.; Krishna, T. OpenSMART: Single-cycle multi-hop NoC generator in BSV and Chisel. In Proceedings of the 2017 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Santa Rosa, CA, USA, 24–25 April 2017; pp. 195–204. [Google Scholar]

- Farrokhbakht, H.; Gratz, P.V.; Krishna, T.; San Miguel, J.; Jerger, N.E. Stay in your Lane: A NoC with Low-overhead Multi-packet Bypassing. In Proceedings of the 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Seoul, Republic of Korea, 2–6 April 2022; pp. 957–970. [Google Scholar]

- Ejaz, A.; Sourdis, I. FastTrackNoC: A NoC with FastTrack Router Datapaths. In Proceedings of the 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Seoul, Republic of Korea, 2–6 April 2022; pp. 971–985. [Google Scholar]

- Stensgaard, M.B.; Sparsø, J. Renoc: A network-on-chip architecture with reconfigurable topology. In Proceedings of the Second ACM/IEEE International Symposium on Networks-on-Chip (nocs 2008), Newcastle upon Tyne, UK, 7–10 April 2008; pp. 55–64. [Google Scholar]

- Stefan, R.A.; Molnos, A.; Goossens, K. daelite: A tdm noc supporting qos, multicast, and fast connection set-up. IEEE Trans. Comput. 2012, 63, 583–594. [Google Scholar]

- Goossens, K.; Dielissen, J.; Radulescu, A. Æthereal network on chip: Concepts, architectures, and implementations. IEEE Des. Test Comput. 2005, 22, 414–421. [Google Scholar] [CrossRef]

- Modarressi, M.; Tavakkol, A.; Sarbazi-Azad, H. Application-aware topology reconfiguration for on-chip networks. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2010, 19, 2010–2022. [Google Scholar] [CrossRef]

- Kim, M.M.; Davis, J.D.; Oskin, M.; Austin, T. Polymorphic on-chip networks. In Proceedings of the 2008 International Symposium on Computer Architecture, Beijing, China, 21–25 June 2008; pp. 101–112. [Google Scholar]

- Papamichael, M.K.; Hoe, J.C. CONNECT: Re-examining conventional wisdom for designing NoCs in the context of FPGAs. In Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2012; pp. 37–46. [Google Scholar]

- Ma, N.; Lu, Z.; Zheng, L. System design of full HD MVC decoding on mesh-based multicore NoCs. Microprocess. Microsyst. 2011, 35, 217–229. [Google Scholar] [CrossRef]

- Lusala, A.K.; Legat, J.D. Combining sdm-based circuit switching with packet switching in a NoC for real-time applications. In Proceedings of the IEEE International Symposium of Circuits and Systems, Rio de Janeiro, Brazil, 15–18 May 2011. [Google Scholar]

- Jerger, N.; Peh, L.S.; Lipasti, M.H. Circuit-Switched Coherence. In Proceedings of the Second ACM/IEEE International Symposium on Networks-on-Chip (nocs 2008), Newcastle upon Tyne, UK, 7–10 April 2008. [Google Scholar]

- Mazloumi, A.; Modarressi, M. A hybrid packet/circuit-switched router to accelerate memory access in NoC-based chip multiprocessors. In Proceedings of the 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2015; pp. 908–911. [Google Scholar]

- Yong, C.; Matus, E.; Fettweis, G.P. Combined packet and TDM circuit switching NoCs with novel connection configuration mechanism. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 18–31 May 2017. [Google Scholar]

- Fallahrad, M.; Patooghy, A.; Ziaeeziabari, H.; Taheri, E. CirKet: A Performance Efficient Hybrid Switching Mechanism for NoC Architectures. In Proceedings of the Digital System Design, Limassol, Cyprus, 31 August–2 September 2016. [Google Scholar]

- Modarressi, M.; Sarbaziazad, H.; Arjoma, M. A hybrid packet-circuit switched on-chip network based on SDM. In Proceedings of the 2009 Design, Automation & Test in Europe Conference & Exhibition, Nice, France, 20–24 April 2009. [Google Scholar]

- Zeng, S.M.; Ni, W.; Zhang, Y.X.; Song, Y.K.; Zhang, D.L. Design of adaptive transmission NoC based on packet and circuit switching mechanism. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nanjing, China, 25–28 October 2022; pp. 1–3. [Google Scholar]

- Biswas, A.K. Efficient Timing Channel Protection for Hybrid (Packet/Circuit-Switched) Network-on-Chip. IEEE Trans. Parallel Distrib. Syst. 2018, 29, 1044–1057. [Google Scholar] [CrossRef]

- Manzoor, M.; Mir, R.N.; Hakim, N.-u.-d. PAAD (Partially adaptive and deterministic routing): A Deadlock Free Congestion Aware Hybrid Routing for 2D Mesh Network-on-chips. Microprocess. Microsyst. 2022, 92, 104551. [Google Scholar] [CrossRef]

- Catania, V.; Mineo, A.; Monteleone, S.; Palesi, M.; Patti, D. Noxim: An open, extensible and cycle-accurate network on chip simulator. In Proceedings of the 2015 IEEE 26th International Conference on Application-Specific Systems, Architectures and Processors (ASAP), Toronto, ON, Canada, 27–29 July 2015. [Google Scholar]

- Soteriou, V.; Wang, H.; Peh, L. A statistical traffic model for on-chip interconnection networks. In Proceedings of the 14th IEEE International Symposium on Modeling, Analysis, and Simulation, Monterey, CA, USA, 11–14 September 2006; pp. 104–116. [Google Scholar]

- Tosun, S.; Ajabshir, V.B.; Mercanoglu, O.; Ozturk, O. Fault-tolerant topology generation method for application-specific network-on-chips. IEEE Trans.-Comput.-Aided Des. Integr. Syst. 2015, 34, 1495–1508. [Google Scholar] [CrossRef]

- Christie, P.; Stroobandt, D. The interpretation and application of Rent’s rule. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2000, 8, 639–648. [Google Scholar] [CrossRef]

- Carlson, T.E.; Heirman, W.; Eyerman, S.; Hur, I.; Eeckhout, L. An evaluation of high-level mechanistic core models. ACM Trans. Archit. Code Optim. (TACO) 2014, 11, 1–25. [Google Scholar] [CrossRef]

- Bienia, C.; Kumar, S.; Singh, J.P.; Li, K. The PARSEC benchmark suite: Characterization and architectural implications. In Proceedings of the 17th International Conference on Parallel Architectures and Compilation Techniques, Toronto, ON, Canada, 25–29 October 2008; pp. 72–81. [Google Scholar]

- Liu, S.; Liu, D. A high-flexible low-latency memory-based FFT processor for 4G, WLAN, and future 5G. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 27, 511–523. [Google Scholar] [CrossRef]

| Port Name | Bit Width | Direction | Function |

|---|---|---|---|

| Data | N bits | DS to DR | Payload or packet. |

| Enable (EN) | 1 bit | DS to DR | To indicates whether the transmission is valid |

| Unlink (UL) | 1 bit | DS to DR | To unlock the constructed path |

| Overtime (OT) | 1 bit | DR to DS | To notice the transaction has time violation |

| CRCe (CRC) | 1 bit | DR to DS | To states the data transmission fails |

| Trans_grt (TG) | 1 bit | DR to DS | To authorize data transaction of data sender |

| Trans_ref (TF) | 1 bit | DR to DS | to refuse data transmission |

| NoC Model | Mesh: 4 × 4, 6 × 6, 8 × 8 |

| Flit width | 34 bits (2-bit flit type + 32-bit(4Byte) message data) |

| Packet length | 12 flits (1 head flit + 14 body flits + 1 tail flit), total 48 byte message data. |

| Operation time | 10,000 cycles |

| Traffic model | Uniform random |

| Route algorithm | adaptive-XY |

| Synthesis time | 100,000 clock cycles |

| AEthereal [26] | dAElite [25] | CTN [34] | PCCNoC | |||||

|---|---|---|---|---|---|---|---|---|

| ideal | measured | ideal | measured | ideal | measured | ideal | measured | |

| Cycles | 246 | 1000 | 60 | 81 | 16 | 30 | 8 | 8 |

| Cost factor | 30.8× | 125× | 7.5× | 10× | 2× | 3.8× | 1× | 1× |

| Bandwidth (bits) | Area (m) | Combinational Area (m) | Noncombinati-Onal Area (m) | Power (mW) | |

|---|---|---|---|---|---|

| PCCNoC | 263 | 3180.81 | 1406.78 | 1774.03 | 3.2 |

| Research | Bandwidth (bits) | Technology (nm) | Frequency (GHz) | Area (m) | Normalized Area (m) 1 | Power (mW) |

|---|---|---|---|---|---|---|

| CTN [31] | 48 | TSMC 65 | 2.8 | 44,157 | 44,157 | 29 |

| VCS [7] | - | TSMC 45 | 2 | 46,000 | 95,975 | 17.1 |

| MRBS [9] | 34 | SAED 32 | 0.5 | 87,753 | 362,066 | 11.8 |

| MRCN [8] | 34 | SAED 32 | - | 85,616 | 353,249 | 8.5 |

| SmartFork [14] | - | 45 | 1 | 62,370 | 130,130 | 5.58 |

| Our work | 49 | TSMC 12 | 3 | 1421 | 41,692 | 1.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, X.; Hao, P.; Liu, D. PCCNoC: Packet Connected Circuit as Network on Chip for High Throughput and Low Latency SoCs. Micromachines 2023, 14, 501. https://doi.org/10.3390/mi14030501

Zhou X, Hao P, Liu D. PCCNoC: Packet Connected Circuit as Network on Chip for High Throughput and Low Latency SoCs. Micromachines. 2023; 14(3):501. https://doi.org/10.3390/mi14030501

Chicago/Turabian StyleZhou, Xinbing, Peng Hao, and Dake Liu. 2023. "PCCNoC: Packet Connected Circuit as Network on Chip for High Throughput and Low Latency SoCs" Micromachines 14, no. 3: 501. https://doi.org/10.3390/mi14030501

APA StyleZhou, X., Hao, P., & Liu, D. (2023). PCCNoC: Packet Connected Circuit as Network on Chip for High Throughput and Low Latency SoCs. Micromachines, 14(3), 501. https://doi.org/10.3390/mi14030501