Signal-Independent Background Calibration with Fast Convergence Speed in Pipeline-SAR ADC

Abstract

:1. Introduction

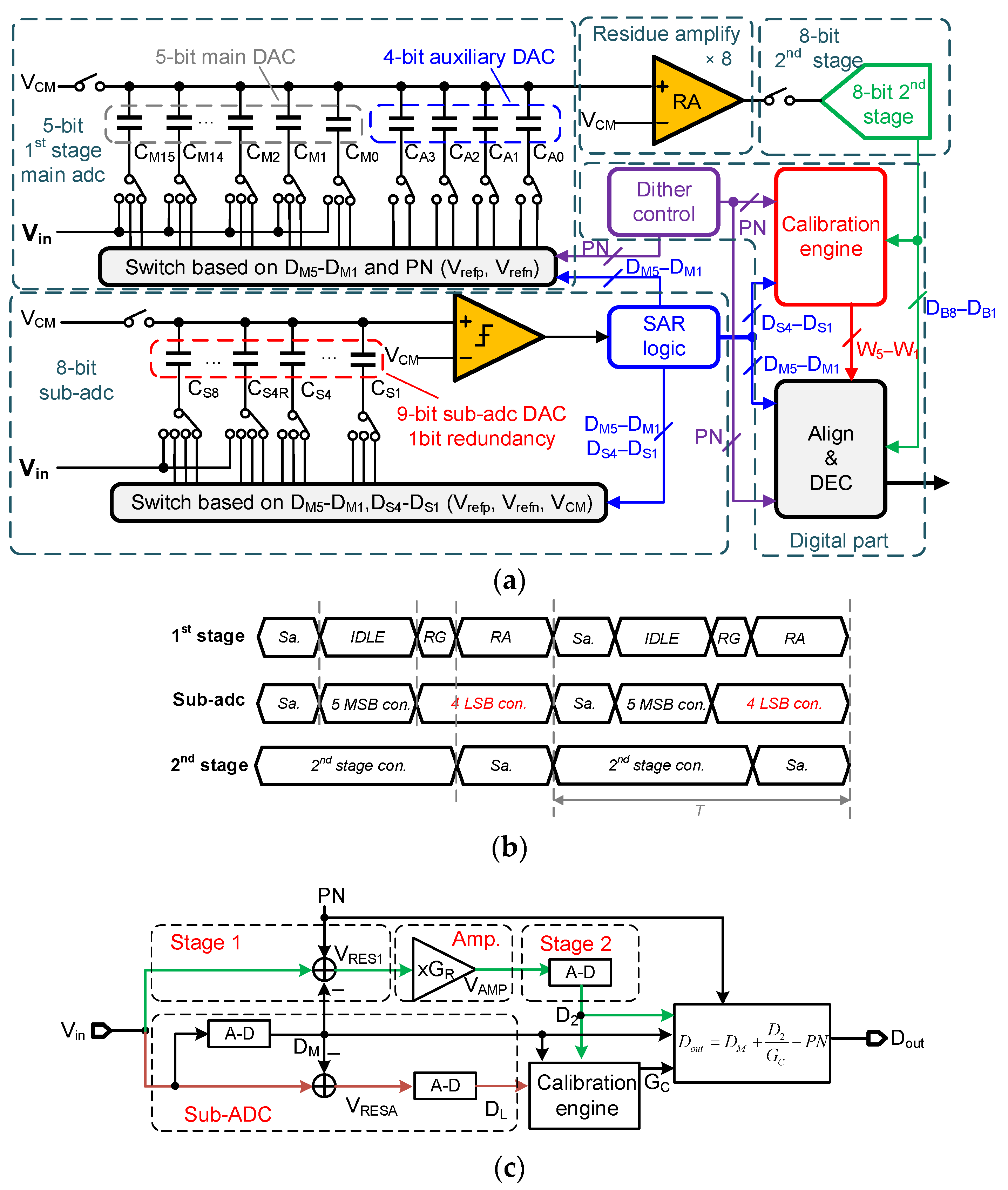

2. Proposed Background Calibration

2.1. Signal-Independent PN Injection

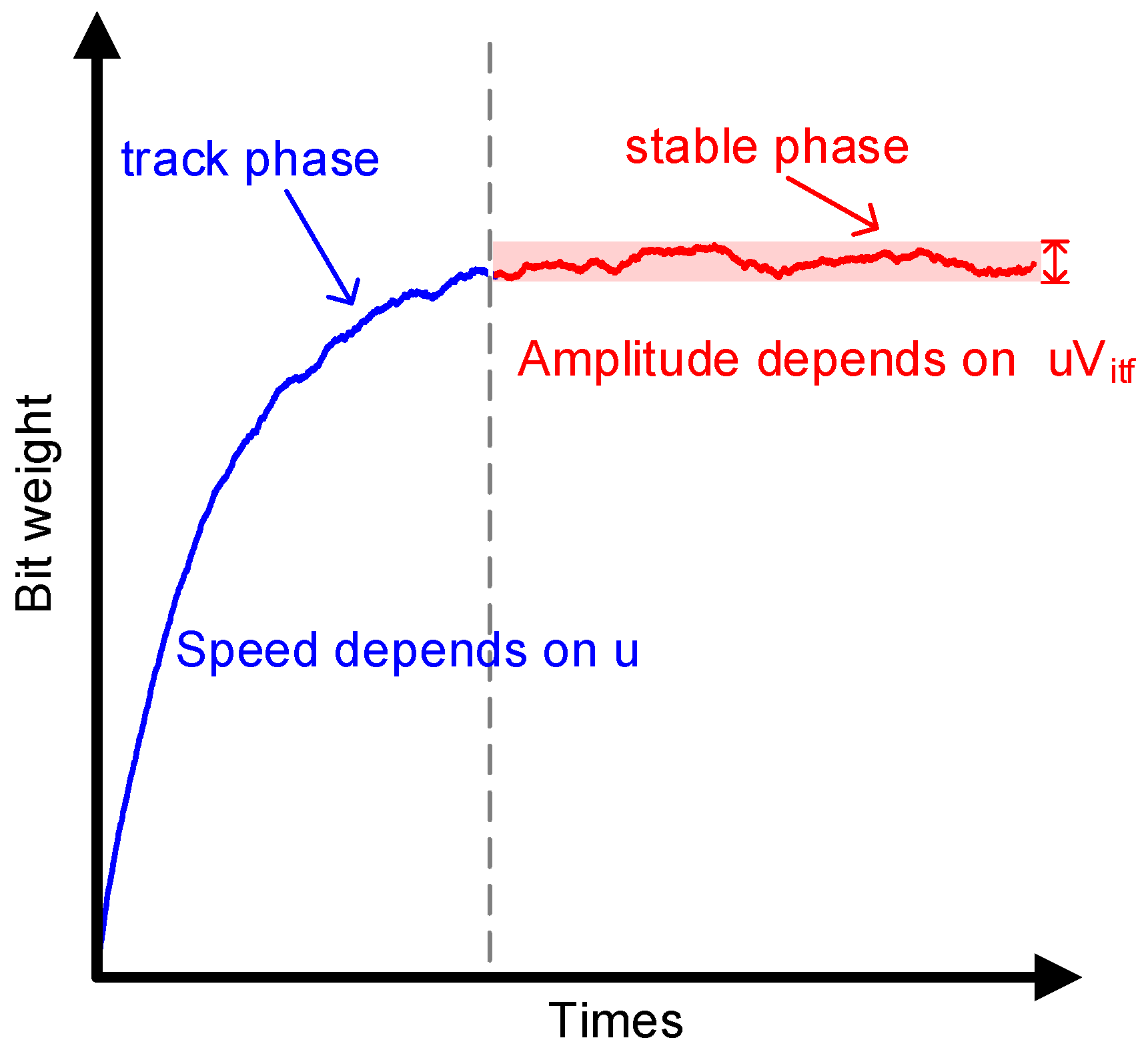

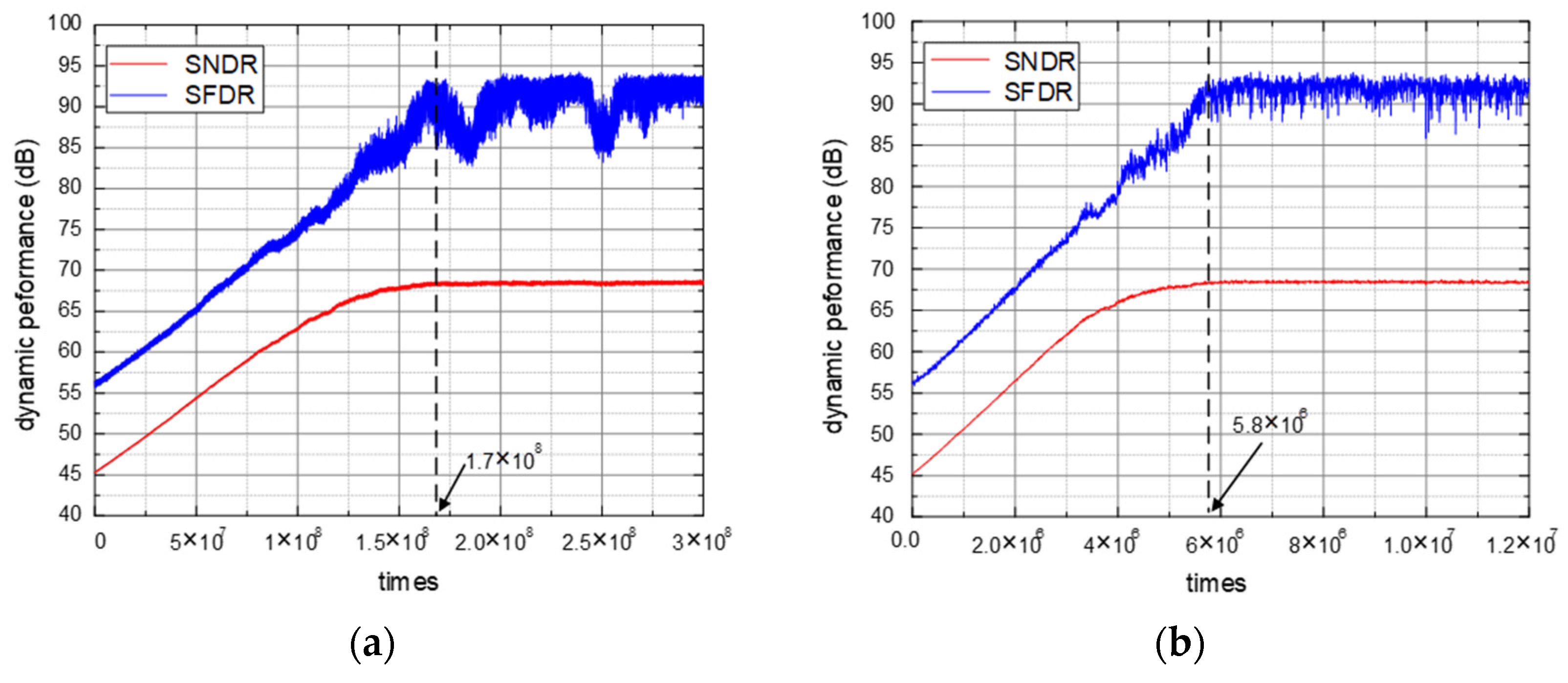

2.2. Signal Elimination and Convergence Acceleration

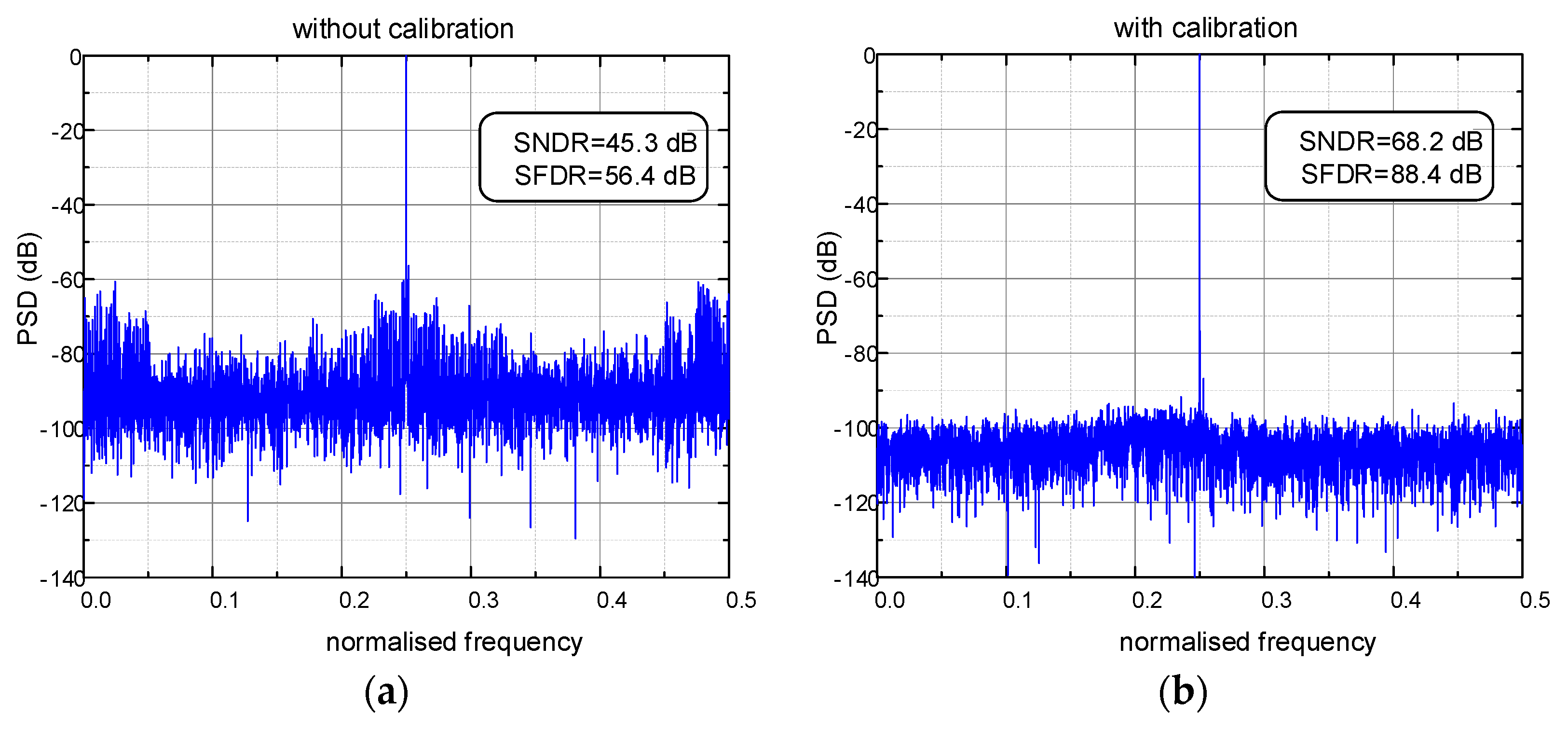

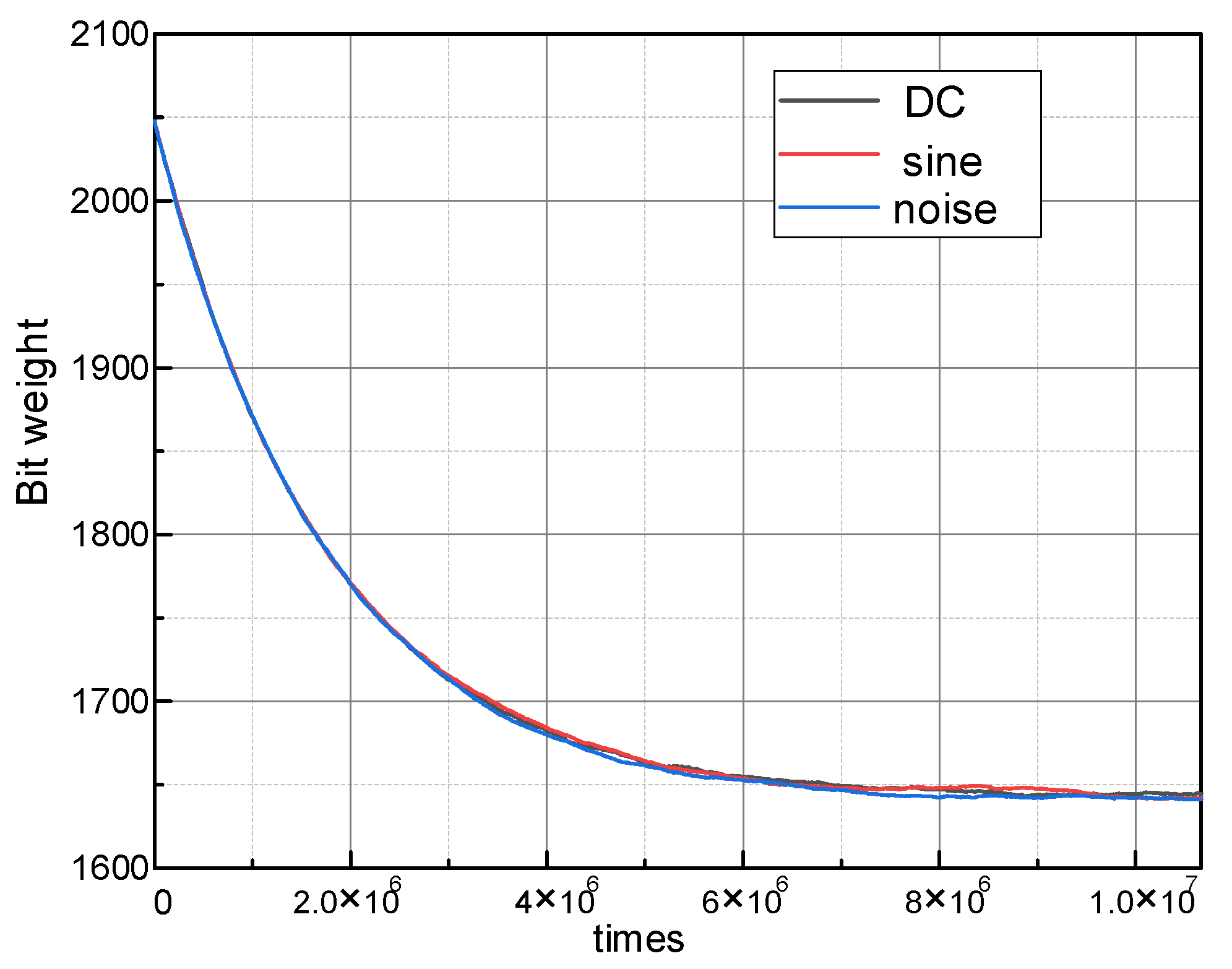

3. Simulation Results and Comparison

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Li, D.; Zhu, Z.; Ding, R.; Yang, Y. A 1.4-mW 10-Bit 150-MS/s SAR ADC With Nonbinary Split Capacitive DAC in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1524–1528. [Google Scholar] [CrossRef]

- Park, J.-S.; Jeon, J.-M.; Boo, J.-H.; Lee, J.-H.; Cho, K.-I.; Kim, H.-J.; Ahn, G.-C.; Lee, S.-H. A 2.2mW 12-bit 200MS/s 28nm CMOS Pipelined SAR ADC with Dynamic Register-Based High-Speed SAR Logic. In Proceedings of the 2020 IEEE Asian Solid-State Circuits Conference (A-SSCC), Hiroshima, Japan, 9–11 November 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Liu, Q.; Shu, W.; Chang, J.S. A 1-GS/s 11-Bit SAR-Assisted Pipeline ADC With 59-dB SNDR in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1164–1168. [Google Scholar] [CrossRef]

- Lin, C.; Lee, T. A 12-bit 210-MS/s 2-Times Interleaved Pipelined-SAR ADC With a Passive Residue Transfer Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 929–938. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. 26.1 A 1mW 71.5dB SNDR 50MS/S 13b fully differential ring-amplifier-based SAR-assisted pipeline ADC. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Huang, H.; Sarkar, S.; Elies, B.; Chiu, Y. 28.4 A 12b 330MS/s pipelined-SAR ADC with PVT-stabilized dynamic amplifier achieving <1dB SNDR variation. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 472–473. [Google Scholar] [CrossRef]

- Verbruggen, B.; Deguchi, K.; Malki, B.; Craninckx, J. A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28nm digital CMOS. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Zhang, M.; Chan, C.; Martins, R.P. 3.2 A 7.6mW 1GS/s 60dB SNDR Single-Channel SAR-Assisted Pipelined ADC with Temperature-Compensated Dynamic Gm-R-Based Amplifier. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 60–62. [Google Scholar] [CrossRef]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12 bit 160 MS/s Two-Step SAR ADC With Background Bit-Weight Calibration Using a Time-Domain Proximity Detector. IEEE J. Solid-State Circuits 2015, 50, 920–931. [Google Scholar] [CrossRef]

- Verbruggen, B.; Iriguchi, M.; de la Guia Solaz, M.; Glorieux, G.; Deguchi, K.; Malki, B.; Craninckx, J. A 2.1 mW 11b 410 MS/s dynamic pipelined SAR ADC with background calibration in 28nm digital CMOS. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013; pp. C268–C269. [Google Scholar]

- Cao, Y.; Zhang, S.; Zhang, T.; Chen, Y.; Zhao, Y.; Chen, C.; Ye, F.; Ren, J. A 91.0-dB SFDR Single-Coarse Dual-Fine Pipelined-SAR ADC With Split-Based Background Calibration in 28-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 641–654. [Google Scholar] [CrossRef]

- Li, H.; Maddox, M.; Coin, M.C.W.; Buckley, W.; Hummerston, D.; Naeem, N. A signal-independent background-calibrating 20b 1MS/S SAR ADC with 0.3ppm INL. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 242–244. [Google Scholar] [CrossRef]

- Lin, Y.; Liu, C.; Huang, G.; Shyu, Y.; Liu, Y.; Chang, S. A 9-Bit 150-MS/s Subrange ADC Based on SAR Architecture in 90-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 570–581. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. A calibration-free 2.3 mW 73.2 dB SNDR 15b 100 MS/s four-stage fully differential ring amplifier based SAR-assisted pipeline ADC. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C98–C99. [Google Scholar] [CrossRef]

| Inj. Cap | Connection of (CM1, CM0, CA3, CA2, CA1, CA0) | |

|---|---|---|

| Sampling Phase | Residue-Generation Phase | |

| CA0 | (Vin, Vin, 0, 0, 0, −PN) | (DM2, DM1, 0, 0, 0, 0) |

| CA1 | (Vin, Vin, 0, 0, −PN, PN) | (DM2, DM1, 0, 0, 0, 0) |

| CA2 | (Vin, Vin, 0, −PN, PN, PN) | (DM2, DM1, 0, 0, 0, 0) |

| CA3 | (Vin, Vin, PN, −PN, PN, PN) | (DM2, DM1, 0, 0, 0, 0) |

| CM0 | (Vin, Vin, PN, PN, PN, PN) | (DM2, PN, DM1, 0, 0, 0) |

| CM1 | (Vin, Vin, PN, PN, PN, PN) | (PN, DM1, DM2, DM2, DM2, DM2) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.-J.; Wang, P.; Wan, L.-X.; Jin, Z. Signal-Independent Background Calibration with Fast Convergence Speed in Pipeline-SAR ADC. Micromachines 2023, 14, 300. https://doi.org/10.3390/mi14020300

Wang Y-J, Wang P, Wan L-X, Jin Z. Signal-Independent Background Calibration with Fast Convergence Speed in Pipeline-SAR ADC. Micromachines. 2023; 14(2):300. https://doi.org/10.3390/mi14020300

Chicago/Turabian StyleWang, Yu-Jun, Peng Wang, Li-Xi Wan, and Zhi Jin. 2023. "Signal-Independent Background Calibration with Fast Convergence Speed in Pipeline-SAR ADC" Micromachines 14, no. 2: 300. https://doi.org/10.3390/mi14020300

APA StyleWang, Y.-J., Wang, P., Wan, L.-X., & Jin, Z. (2023). Signal-Independent Background Calibration with Fast Convergence Speed in Pipeline-SAR ADC. Micromachines, 14(2), 300. https://doi.org/10.3390/mi14020300