Temperature Cycle Reliability Analysis of an FBAR Filter-Bonded Ceramic Package

Abstract

:1. Introduction

2. Temperature Cycle Reliability Analysis and Life Prediction of Devices

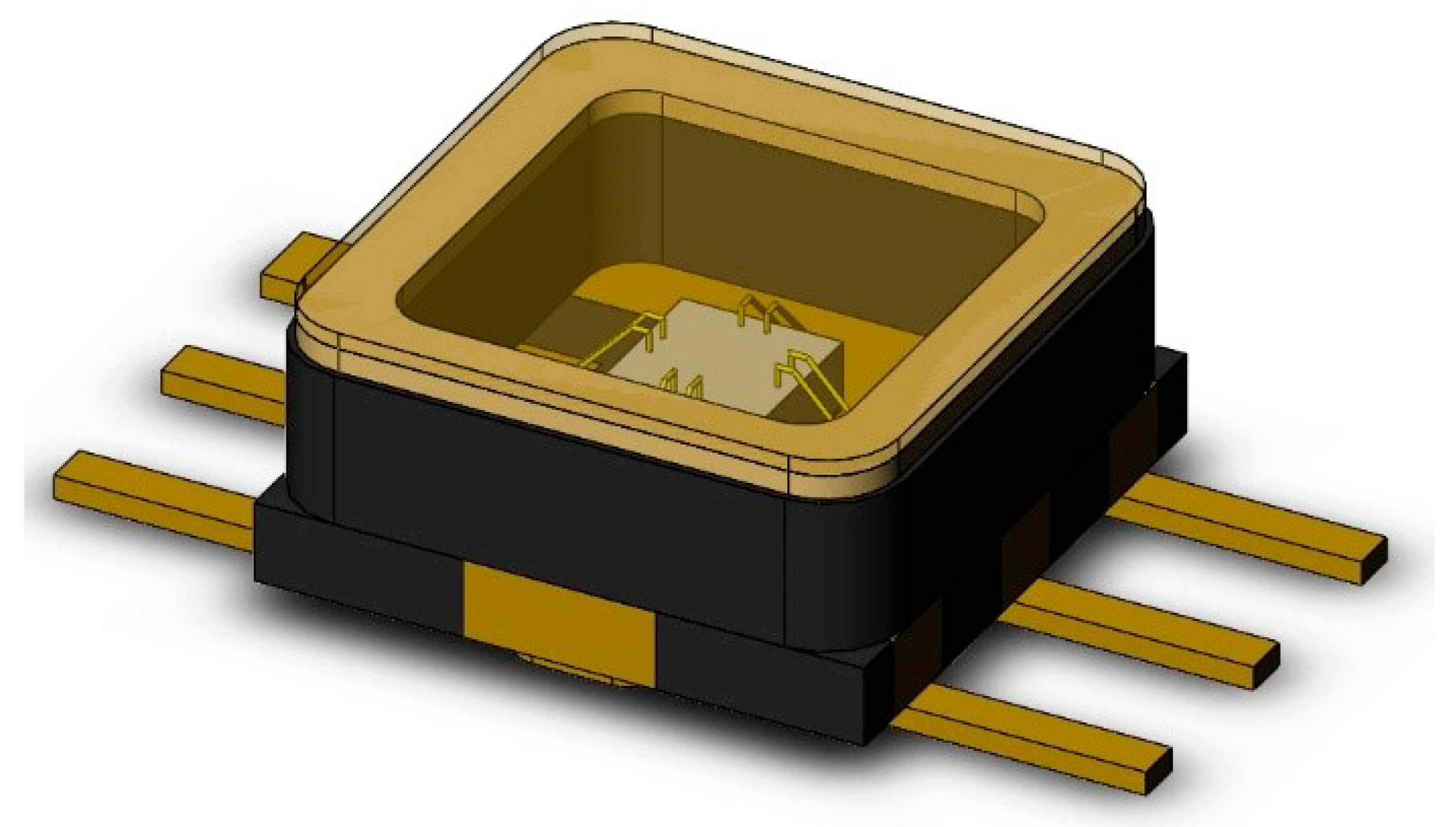

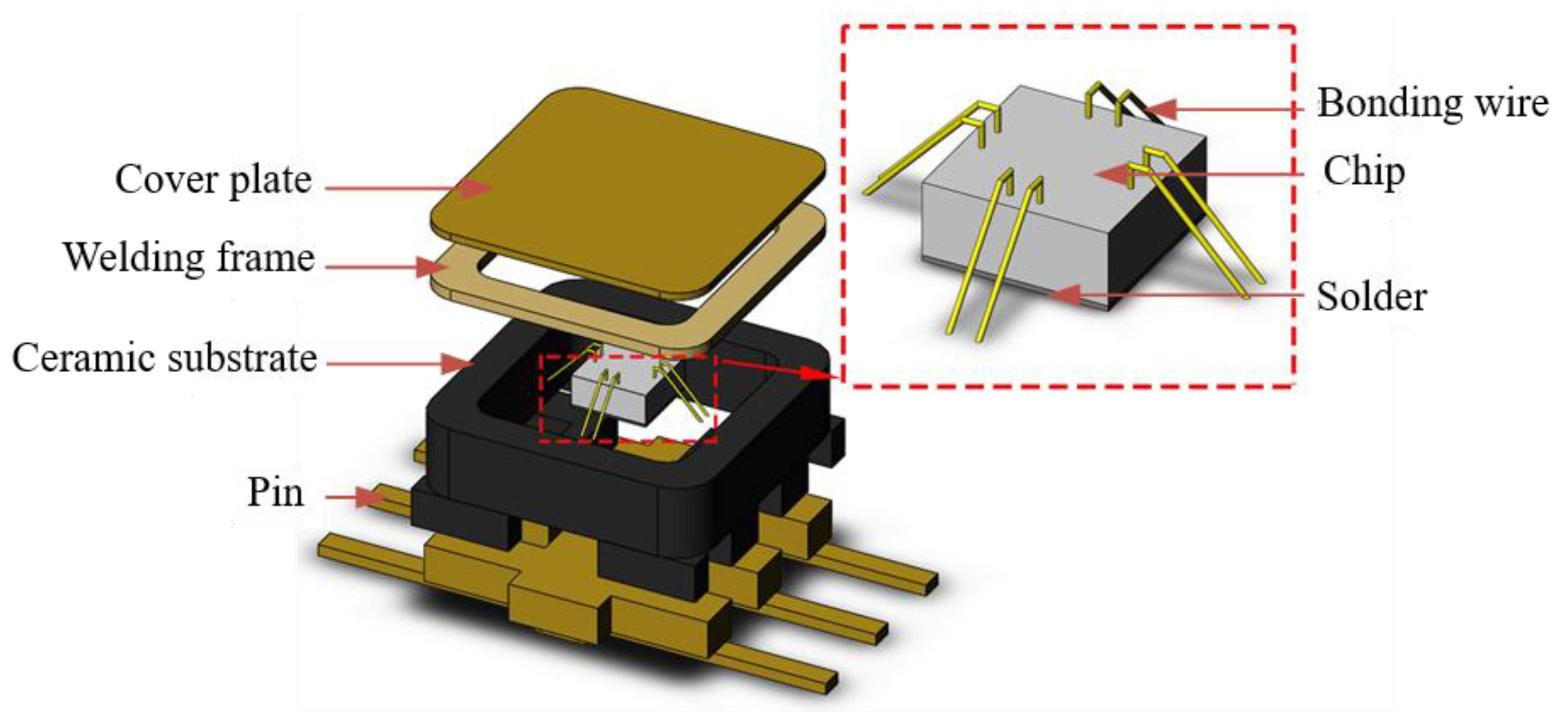

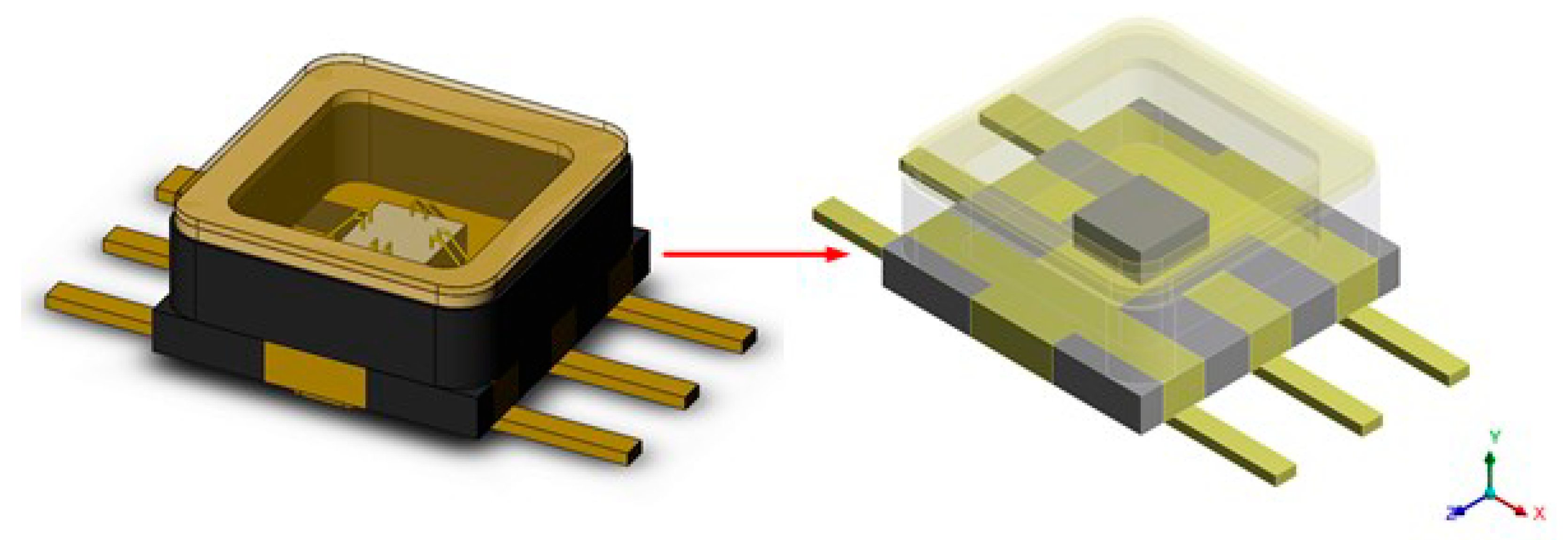

2.1. The Establishment of the Bonded Ceramic Package Filter Finite Element Model

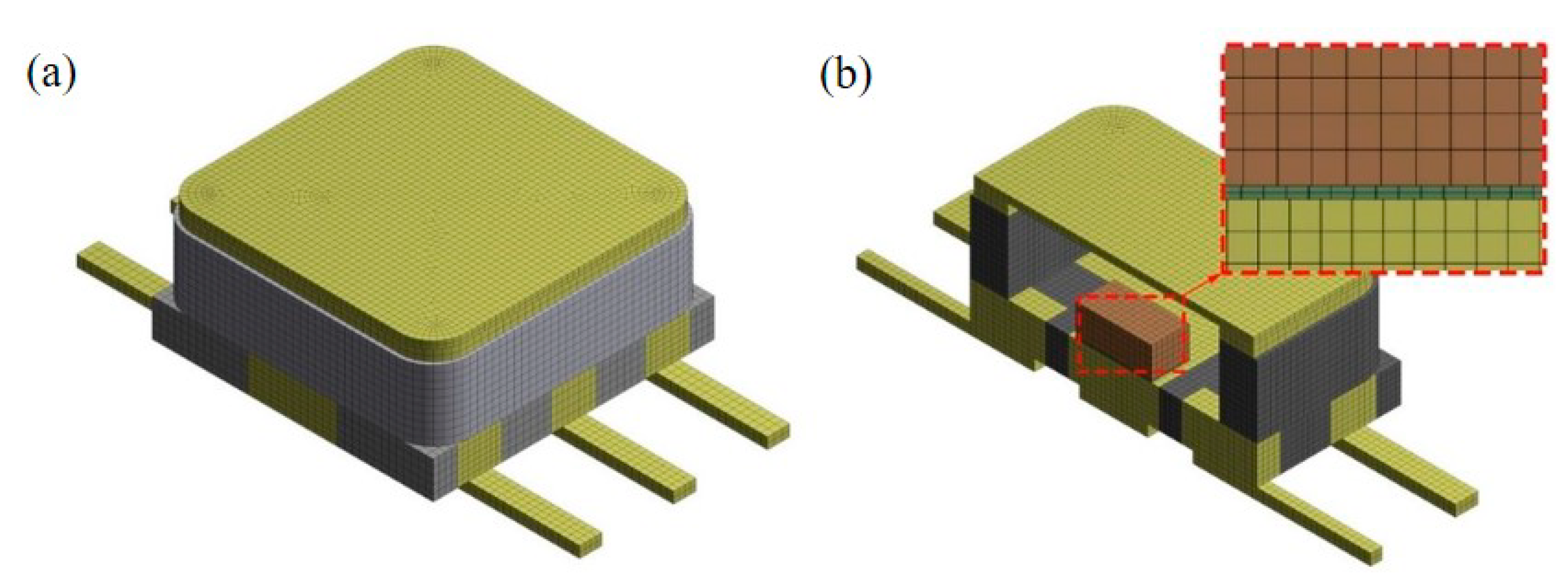

2.2. Material Parameters and Meshing

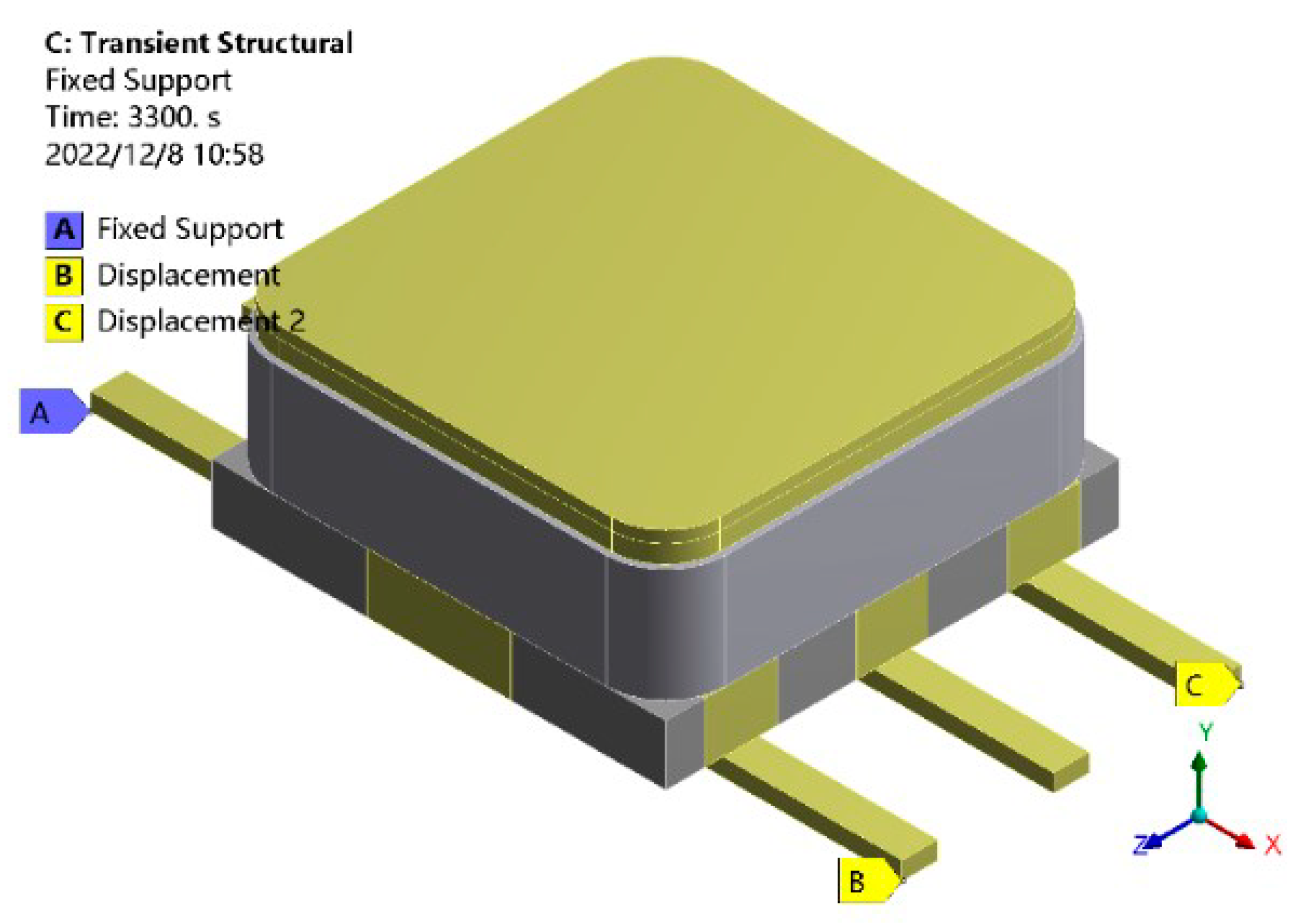

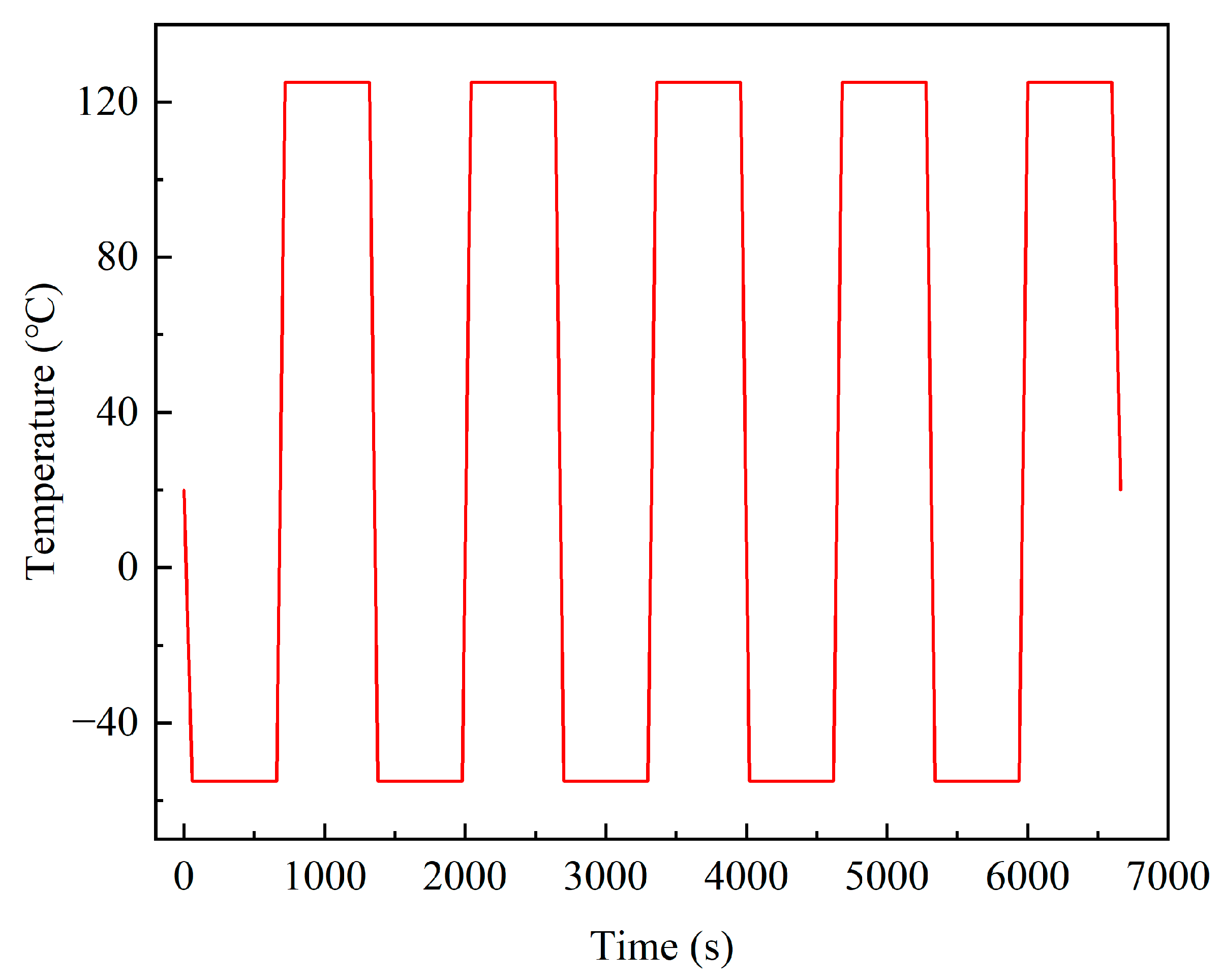

2.3. Temperature Load and Boundary Conditions

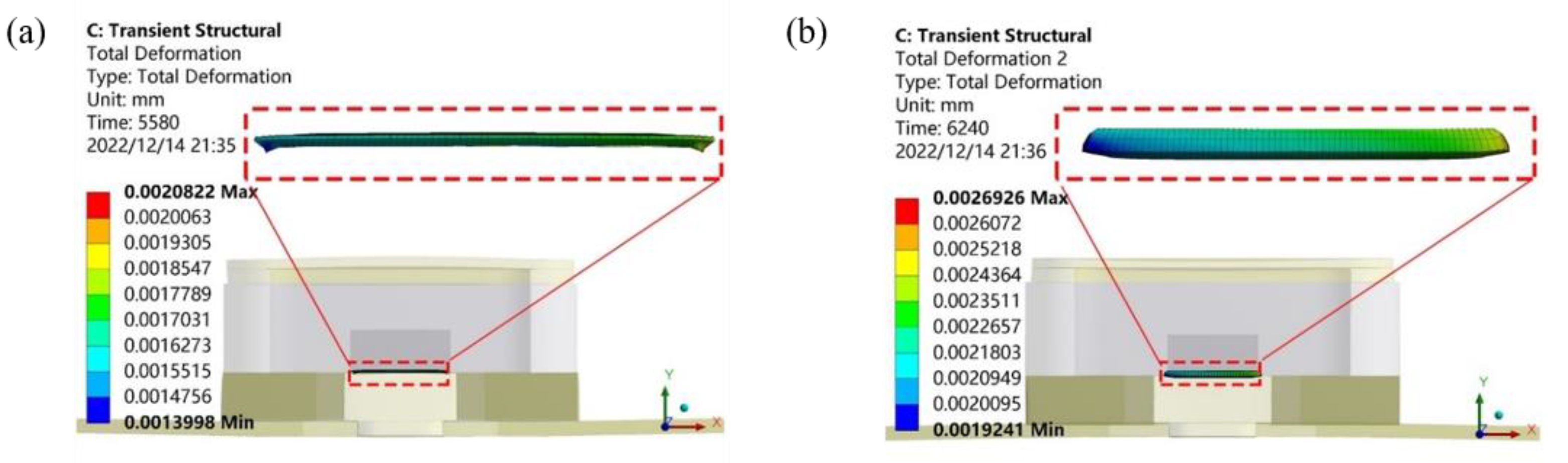

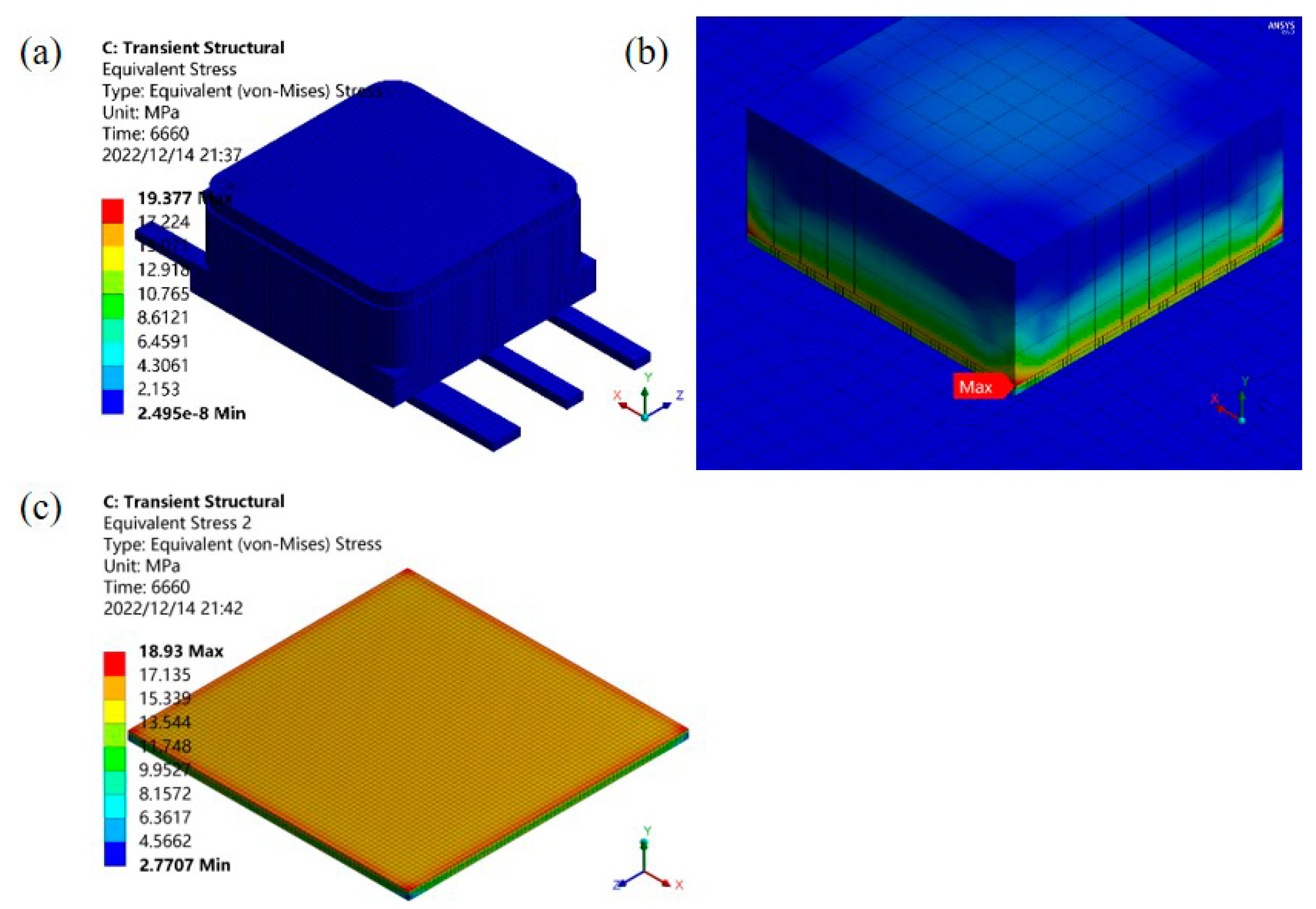

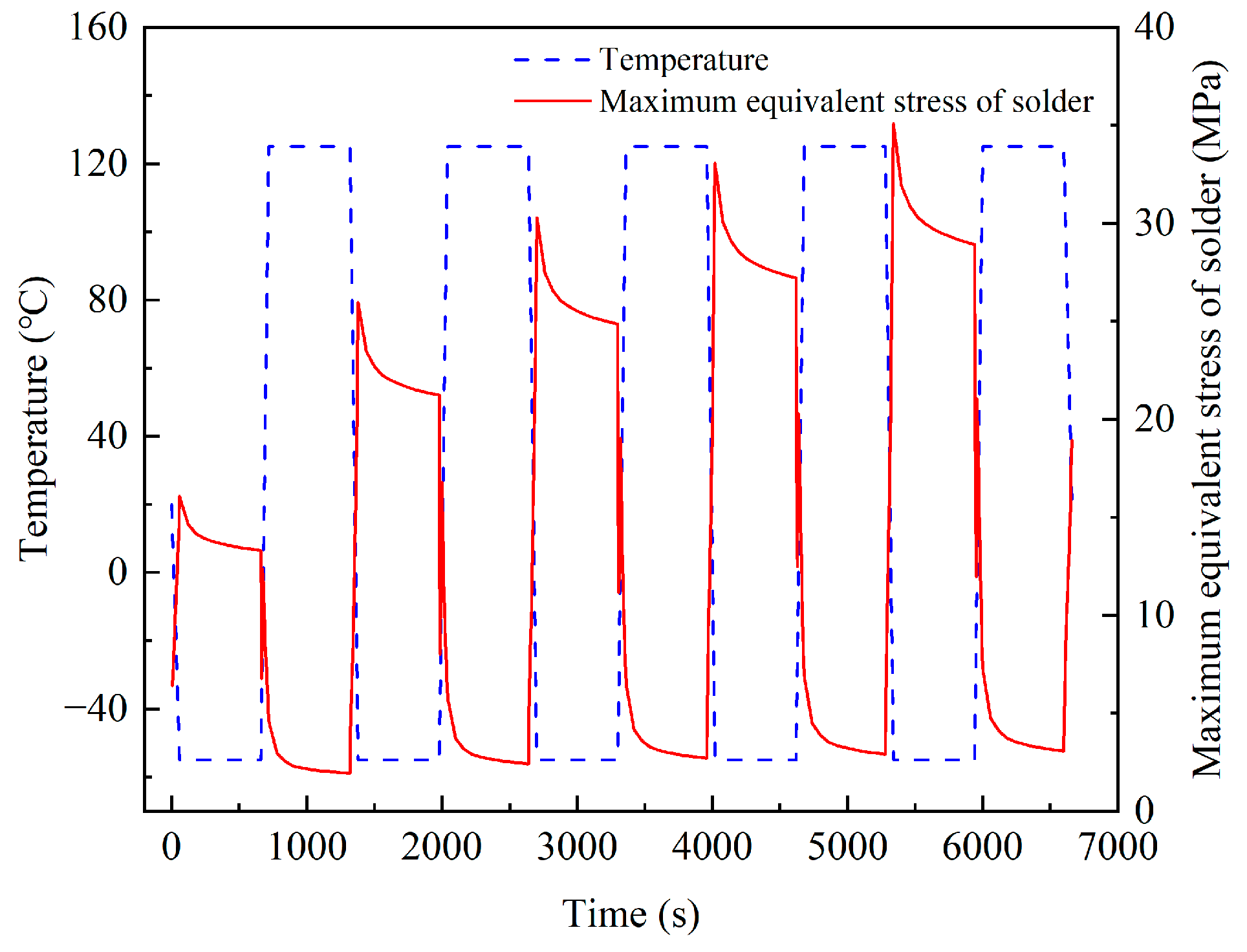

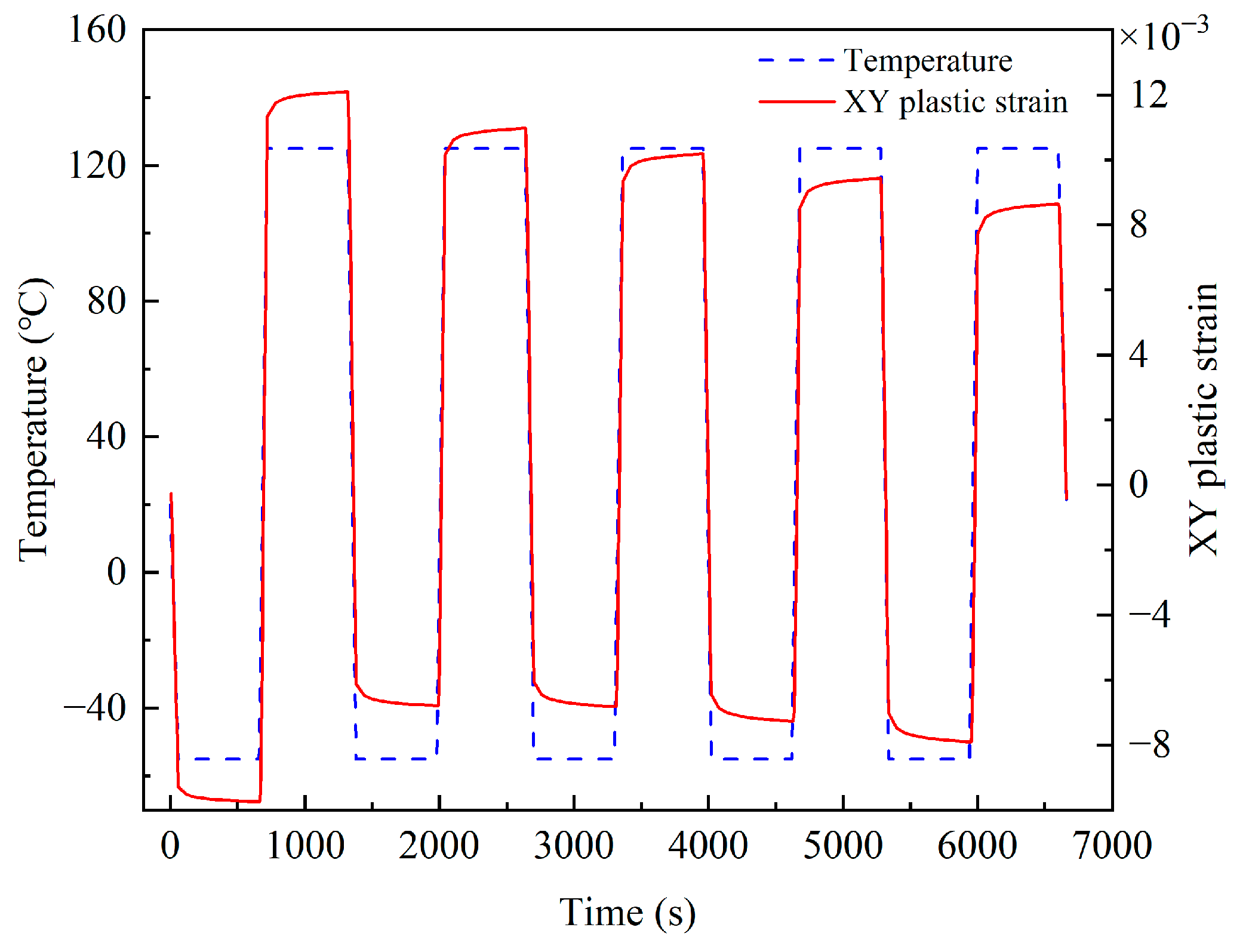

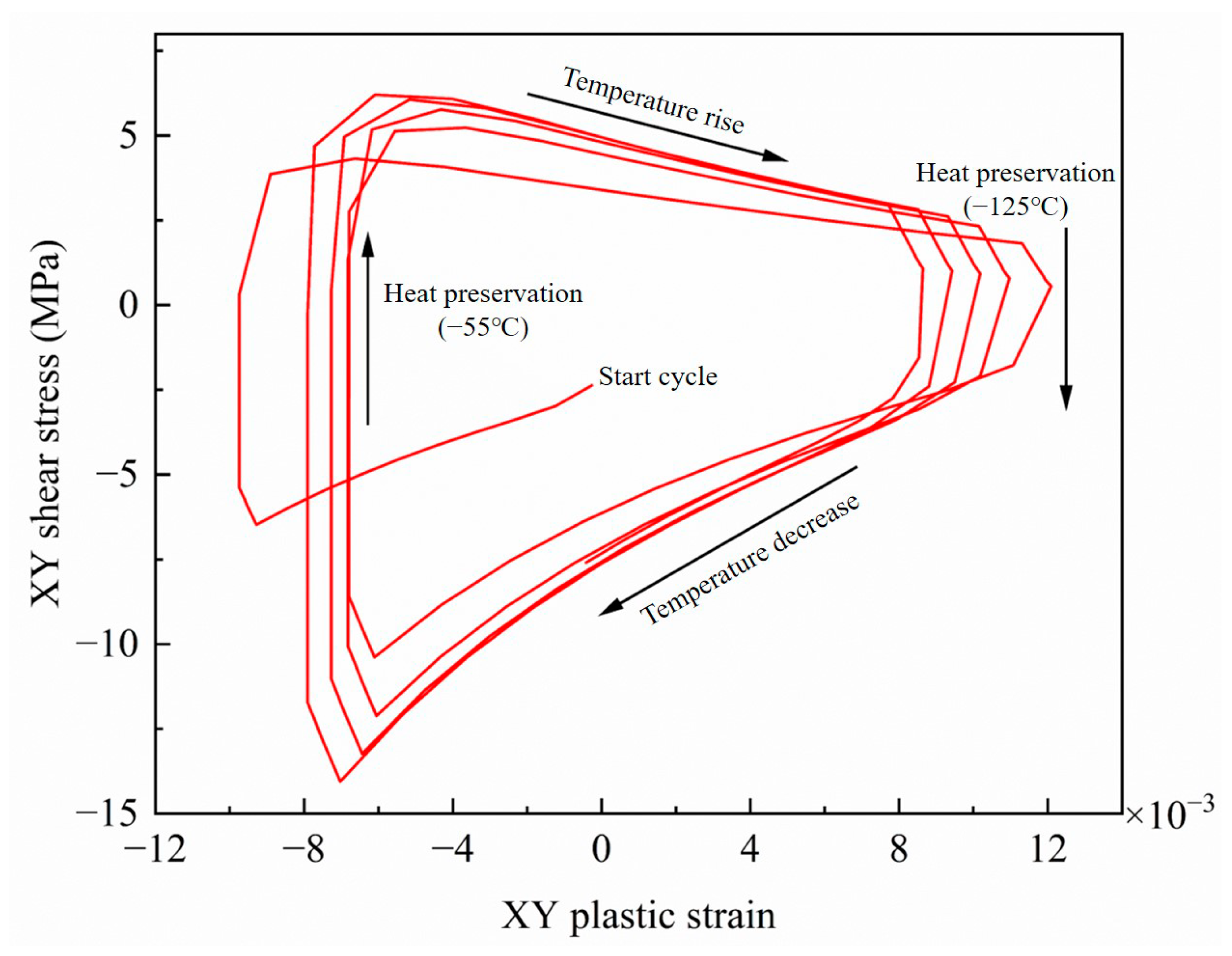

2.4. Temperature Cycle Result Analysis and Life Prediction

3. Influence of Solder Overflow on Temperature Fatigue Life

3.1. Establishment of the Overflow Solder Model

- (1)

- The direction of the solder overflow is entirely random;

- (2)

- If we use the same quality of solder to bond the chip, the volume of spilled solder is the same;

- (3)

- The solder density is uniform after bonding, without holes, residual stress, and strain.

- (1)

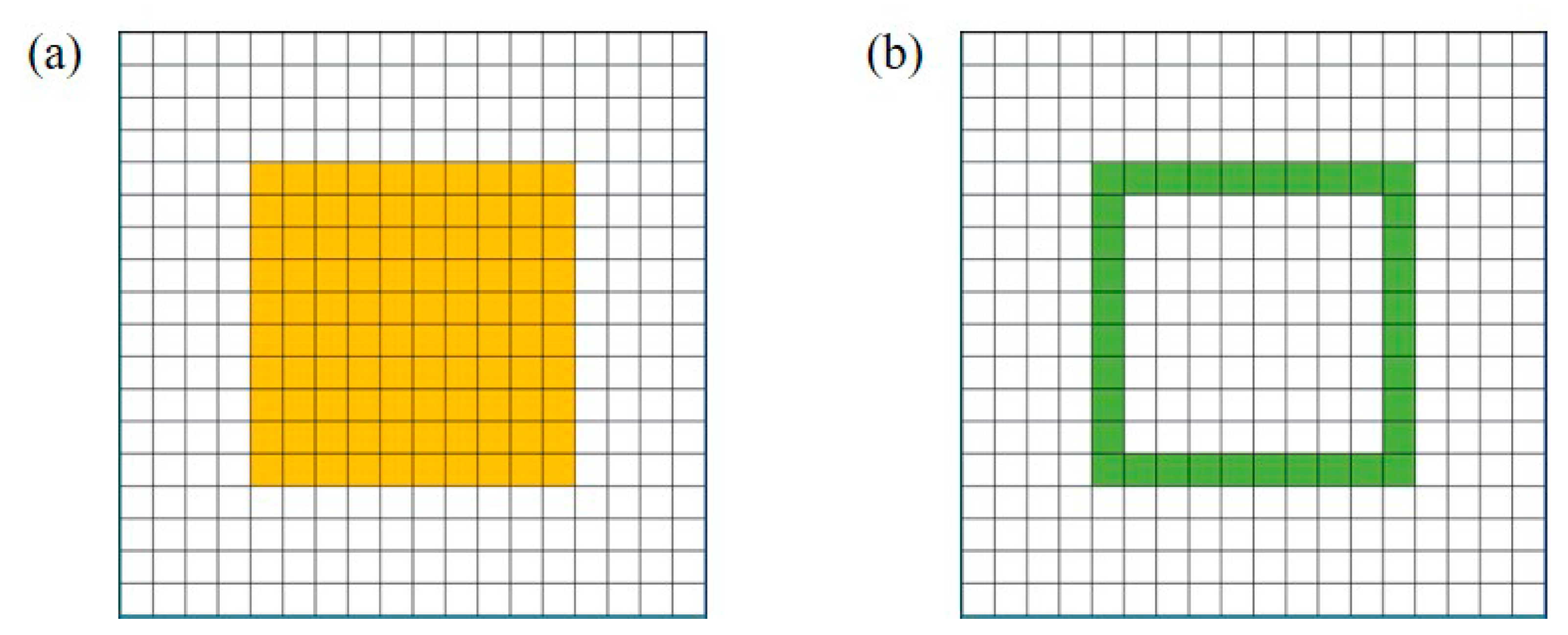

- As shown in Figure 12, the solder spillable area is first decomposed into 18 × 18 squares.

- (2)

- Select the location of the chip as the initial solder area. Figure 13a shows that the yellow area is the initial solder area. The boundary pool is set up by taking the grid with a blank area in the connected position as the boundary. Figure 13b shows that the green square is the boundary pool, starting from the boundary pool and expanding outwards.

- (3)

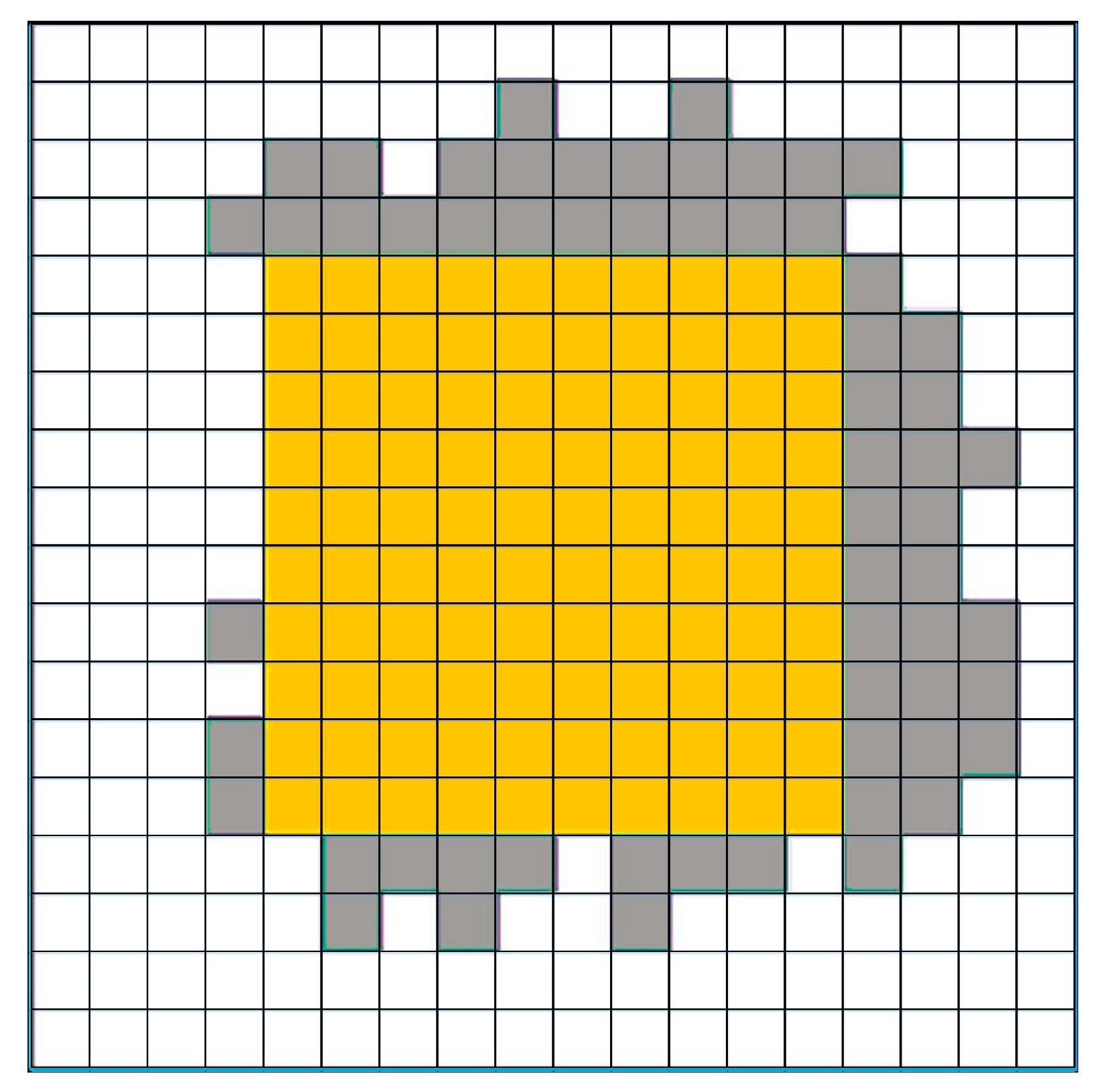

- Take a random square from the boundary pool. Suppose its coordinates are (x, y). Find the coordinates of the four points connected to it, namely (x + 1, y), (x − 1, y), (x, y + 1), and (x, y − 1), and determine whether the four points have been filled. Take the points that have not been filled to form an array. In the above array, randomly select a point to fill it. After filling, judge whether all four squares connected to the filling square are filled. If not, the coordinate is added to the boundary pool. Iterate over the squares in the boundary pool, determine whether the four positions connected to the squares have been filled, and remove them from the boundary pool if they have been filled. The specific process is shown in Figure 14. Repeat the above steps N times (N = overflow area/chip area × 100).

- (4)

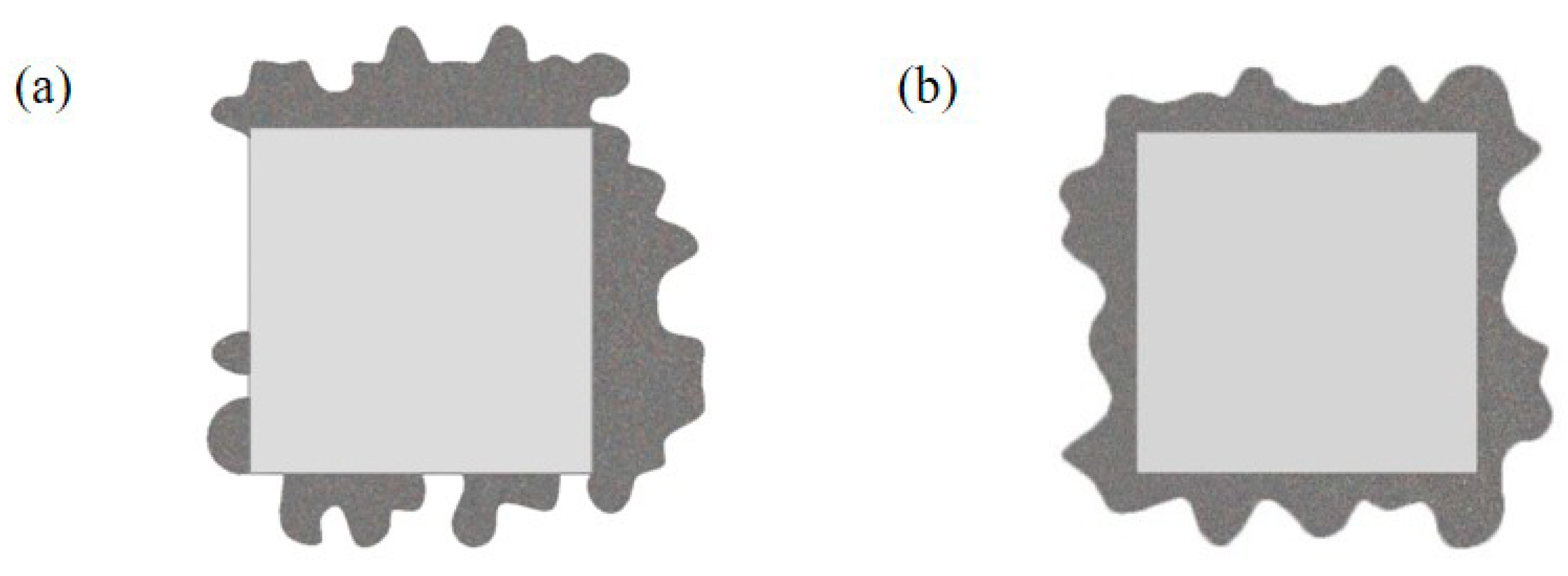

- Return to step (2) to continue the loop and return the filled result at the end. Figure 15 is a random graph with an area equal to 1.6 mm2.

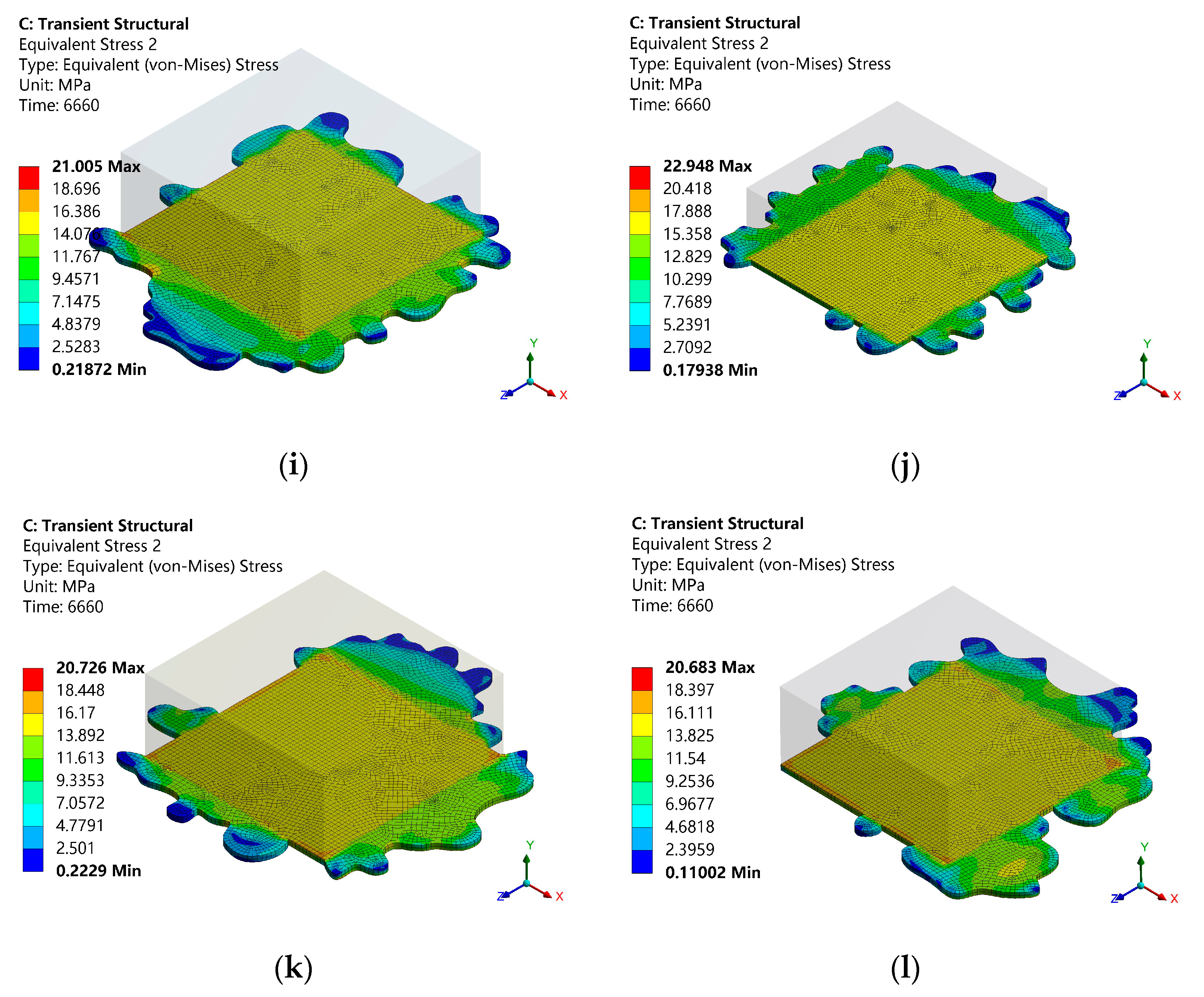

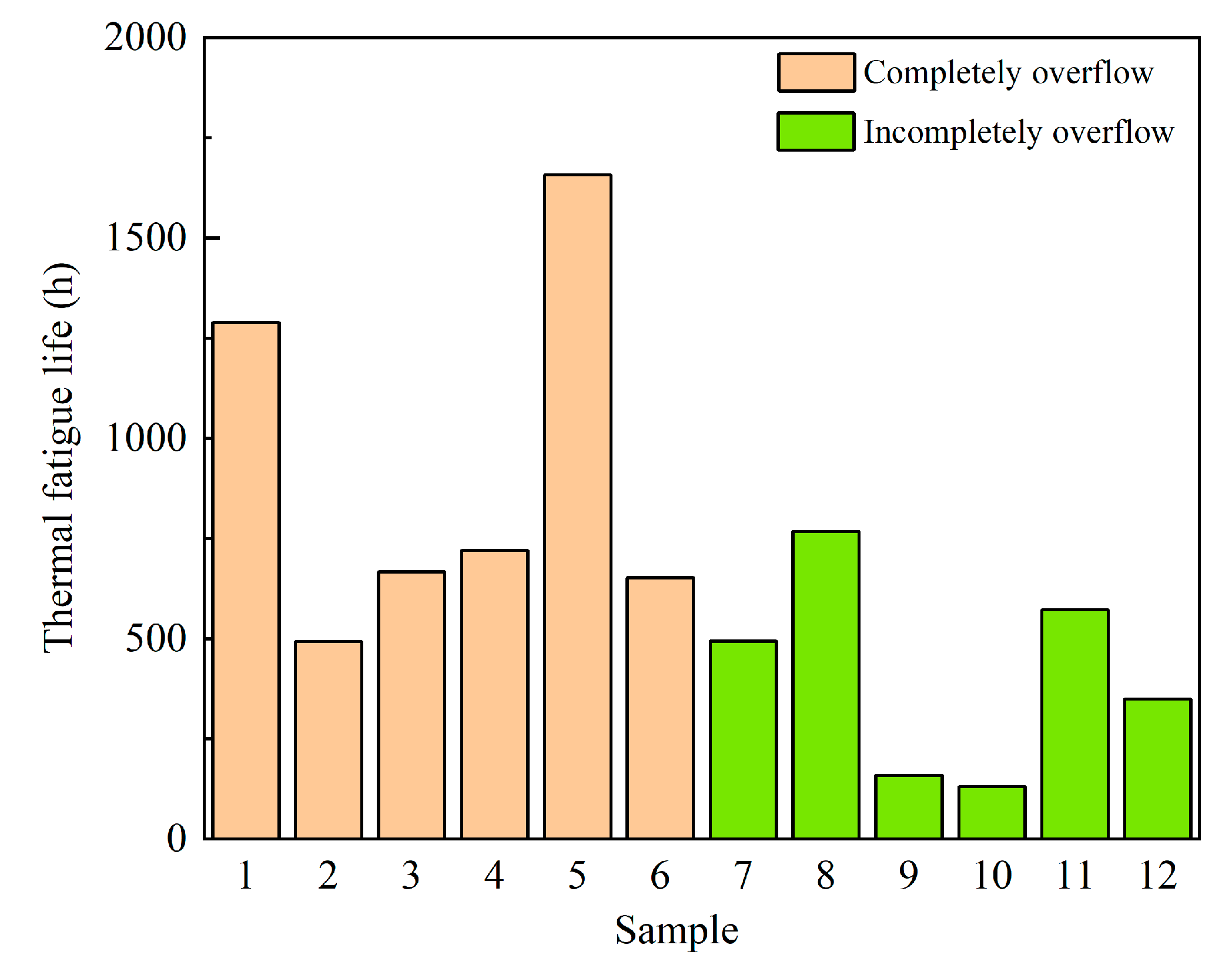

3.2. Thermal Fatigue Life of the Overflow Solder Model

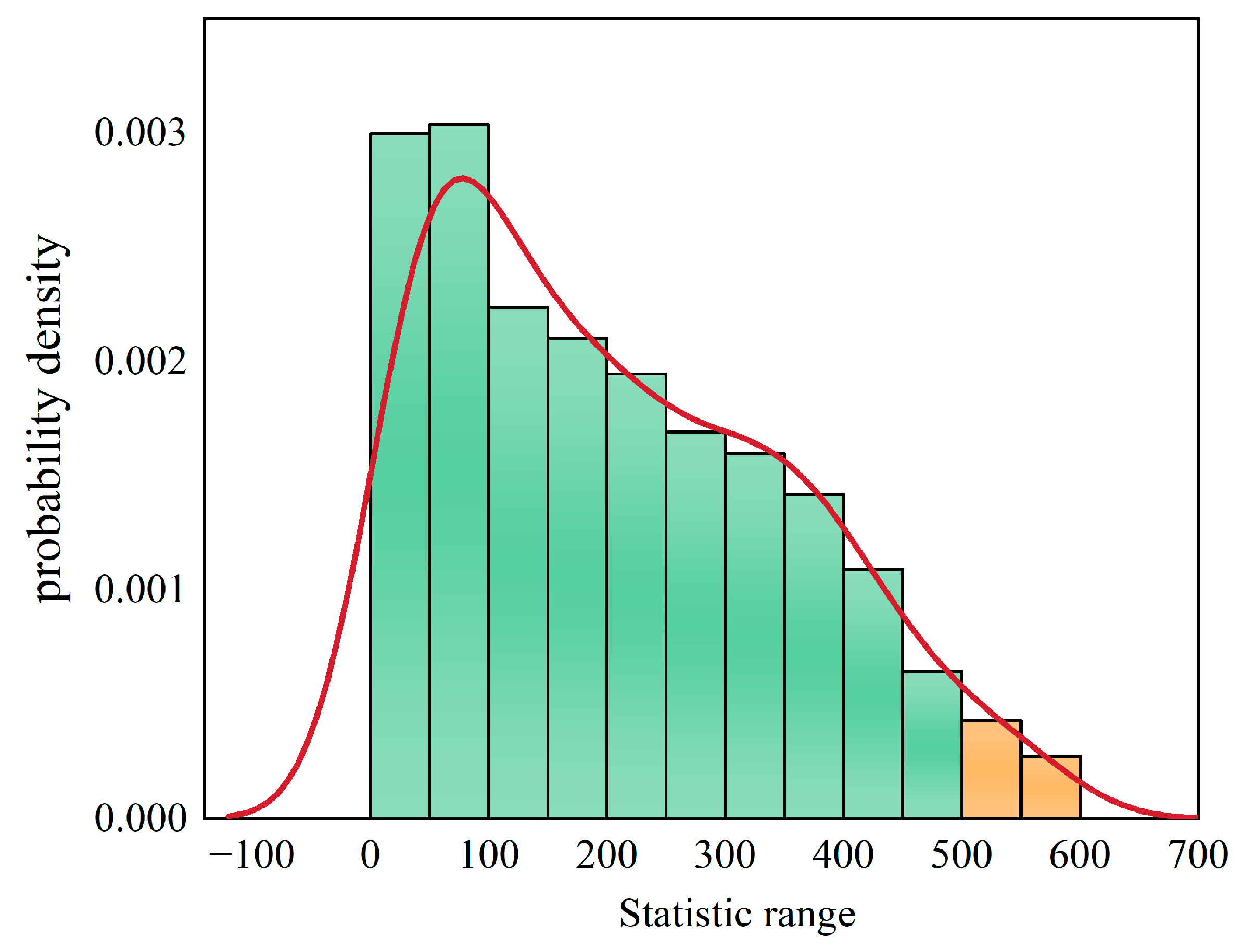

3.3. The Permutation Test

- (1)

- Proposing an original hypothesis H0: both groups of samples are taken from the same distribution;

- (2)

- Calculate the test statistic: calculate the difference between the means of the two groups of samples, denoted as t0;

- (3)

- Put all the samples in the same array, then sort them randomly and divide them into two groups (for example, if group A has a samples and group B has b samples, the number of data in the two groups is a and b respectively), and calculate its statistic (the difference between the means of the two groups);

- (4)

- Repeat step (3) n times (small sample n is usually 1000) to obtain a series of statistics (t1…tn);

- (5)

- Finally, sort (t1…tn) from smallest to largest to form (t1…tn) sampling distribution, and calculate the P (the number of (t1…tn) greater than t0/n). The null hypothesis is rejected if the P is less than the significance level α (α is always 0.05 in statistics).

4. Conclusions

- (1)

- The deformation of the device changes periodically with the loading of temperature load. In the low-temperature holding stage, the whole package presents a downward arch posture, and the whole solder presents an inward shrinking state. In the high-temperature holding stage, the package as a whole is arching, and the solder as a whole is expanding outward. In the whole process, the deformation of the device in the high-temperature holding stage is the largest, and the largest deformation position is near the sharp corner of the chip edge.

- (2)

- After five temperature cycles, the stress distribution between the solder layer and the inner side of the contact surface of the chip is uniform, and the stress at the edge is the largest, so it is concluded that the solder at the corner of the chip cracks first. In the heating stage, the solder stress decreases and fluctuates slightly. In the cooling stage, the solder stress increases greatly. The solder stress in the low-temperature holding stage is greater than that in the high-temperature holding stage.

- (3)

- The thermal fatigue life of solder is 1928.67 h using the Engelmaier model. When the solder spillage occurs, the solder layer will produce local stress concentration, resulting in layered solder expansion, which seriously affects the thermal fatigue life of the device. The mean thermal fatigue life of the device is 913.36 h and 411.86 h, respectively, when the solder completely overflows and incompletely overflows. The permutation test shows that the device has higher reliability under the temperature cycle when the solder is completely spilled.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zou, Y.; Cai, Y.; Gao, C.; Luo, T.; Liu, Y.; Xu, Q.; Wang, Y.; Nian, L.; Liu, W.; Soon, J.B.W.; et al. Design, Fabrication, and Characterization of Aluminum Scandium Nitride-Based Thin Film Bulk Acoustic Wave Filter. J. Microelectromechanical Syst. 2023, 32, 263–270. [Google Scholar] [CrossRef]

- Yang, K.; He, C.; Fang, J.; Cui, X.; Sun, H.; Yang, Y.; Zuo, C. Advanced RF filters for wireless communications. Chip 2023, 100058. [Google Scholar] [CrossRef]

- Yu, H.; Deng, L.; Zhang, L.; Jiang, M.; Ma, J.; Jiang, P.; Tao, B.; Hu, S. Simulation Modeling and Analysis of FBAR RF Filters Considering Different Configurations of Grounding Bond-Wires. In Proceedings of the 2021 IEEE Asia-Pacific Microwave Conference (APMC), Brisbane, Australia, 28 November–1 December 2021; pp. 374–376. [Google Scholar]

- Memon, M.H.; Khan, Z.; Zhang, P.; Sun, H.; Lin, F. Design of High-Q Film Bulk Acoustic Resonator for 5G Applications. In Proceedings of the 2020 IEEE MTT-S International Wireless Symposium (IWS), Shanghai, China, 20–23 September 2020; pp. 1–3. [Google Scholar]

- Tan, L.; Tang, W. Simulation Study on Thermal-Mechanical Coupling of Antenna Array BGA Package. In Proceedings of the Seventh Asia International Symposium on Mechatronics: Volume I; Springer: Singapore, 2020; pp. 31–37. [Google Scholar]

- Depiver, J.A.; Mallik, S.; Harmanto, D. Solder joint failures under thermo-mechanical loading conditions—A review. Adv. Mater. Process. Technol. 2021, 7, 1–26. [Google Scholar] [CrossRef]

- Zhu, Y.; Li, X.; Gao, R.; Wang, C. Low-cycle fatigue failure behavior and life evaluation of lead-free solder joint under high temperature. Microelectron. Reliab. 2014, 54, 2922–2928. [Google Scholar] [CrossRef]

- Arakere, G.; Vujosevic, M.; Cook, J. Temperature cycling performance of ball grid array packages under thermal enabling load. In Proceedings of the Fourteenth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 27–30 May 2014; pp. 621–631. [Google Scholar]

- Li, S.; Iruvanti, S.; Sikka, K.; Wang, R. A Study of Organic Chip Carrier Fatigue Cracking. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 1044–1049. [Google Scholar]

- Depiver, J.A.; Mallik, S.; Amalu, E.H. Thermal fatigue life of ball grid array (BGA) solder joints made from different alloy compositions. Eng. Fail. Anal. 2021, 125, 105447. [Google Scholar] [CrossRef]

- Watanabe, Y.; Yamaguchi, H.; Enomoto, T.; Ogawa, K.; Kobayashi, T.; Omiya, M. Evaluation of thermal fatigue crack propagation in underfill resin materials for electronic packages. Fatigue Fract. Eng. Mater. Struct. 2022, 45, 1349–1360. [Google Scholar] [CrossRef]

- Suhaimi, M.F.; Abu Bakar, M.; Jalar, A.; Che Ani, F.; Ramli, M.R. Thermal cycling effect on the crack formation of solder joint in ball grid array package. J. Phys. Conf. Ser. 2022, 2169, 012006. [Google Scholar] [CrossRef]

- Expansion Alloy Wire Hard Glass Sealed Alloy 4j29 Kovar. Available online: https://www.ecplaza.net/products/expansion-alloy-wire-hard-glass-sealed-4721147 (accessed on 15 December 2021).

- Harper, C.A. Electronic Materials and Processes Handbook; McGraw-Hill Education: New York, NY, USA, 2004. [Google Scholar]

- Chang, R.W.; McCluskey, F.P. Reliability assessment of indium solder for low temperature electronic packaging. Cryogenics 2009, 49, 630–634. [Google Scholar] [CrossRef]

- Gere, J.M.; Goodno, B.J. Mechanics of Materials; Cengage Learning: Boston, MA, USA, 2012. [Google Scholar]

- Ramberg, W.; Osgood, W.R. Description of Stress-Strain Curves by Three Parameters; National Advisory Committee for Aeronautics: Kitty Hawk, NC, USA, 1943.

- Kilinski, T.J.; Lesniak, J.R.; Sandor, B.I. Modern approaches to fatigue life prediction of SMT solder joints. In Solder Joint Reliability; Springer: New York, NY, USA, 1991; pp. 384–405. [Google Scholar]

- Engelmaier, W. Fatigue life of leadless chip carrier solder joints during power cycling. IEEE Trans. Compon. Hybrids Manuf. Technol. 1983, 6, 232–237. [Google Scholar] [CrossRef]

- Tian, W.; Wang, C.; Zhao, Z.; Feng, X.; Wen, Z. Temperature cycle reliability analysis and life prediction of plastic encapsulated power semiconductor devices. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020; pp. 1–4. [Google Scholar]

- I, J. The Design of Experiments. Nature 1936, 137, 252–254. [Google Scholar] [CrossRef]

- Welch, W.J. Construction of permutation tests. J. Am. Stat. Assoc. 1990, 85, 693–698. [Google Scholar] [CrossRef]

| Materials | Density ρ (g/cm3) | Young’s Modulus E (MPa) | Poisson’s Ratio ν | CTE α (1 × 10−6/K) | Thermal Conductivity λ (W/m·K) | Specific Heat Capacity c (J/(kg·°C)) |

|---|---|---|---|---|---|---|

| Kovar | 8359 | 208,000 | 0.317 | 5.1 | 17.3 | 220 |

| Si | 2350 | 159,000 | 0.25 | 2.6 | 149 | 702 |

| Ceramic | 3100 | 28,400 | 0.24 | 7.1 | 31 | 766 |

| 92.5Pb5Sn2.5Ag | 1075 | Table 2 | Table 2 | 29 | 25 | 130 |

| Temperature (°C) | −55 | −35 | −15 | 5 | 50 | 100 | 125 |

|---|---|---|---|---|---|---|---|

| Young’s modulus E (MPa) | 25,470 | 24,930 | 24,400 | 23,870 | 22,670 | 21,330 | 20,660 |

| Poisson’s Ratio ν | 0.392 | 0.394 | 0.397 | 0.4 | 0.415 | 0.427 | 0.431 |

| Parameters | Value | Definition |

|---|---|---|

| s0 (MPa) | 15.09 | Initial value of deformation resistance |

| Q/R (1/K) | 15,583 | Activation energy |

| A (1/s) | 3.25 × 1012 | Pre-exponential factor |

| ξ | 7 | Stress multiplier |

| m | 0.143 | Strain rate sensitivity of stress |

| h0 (MPa) | 1787 | Hardening coefficient |

| Ŝ (MPa) | 72.73 | Coefficient for deformation resistance Saturation value |

| n | 0.00428 | Strain rate sensitivity of saturation value |

| α | 3.73 | Strain rate sensitivity of hardening coefficient |

| Completely Overflow | Lifetime (h) | Incompletely Overflow | Lifetime (h) |

|---|---|---|---|

| Sample 1 | 1289.93 | Sample 7 | 493.41 |

| Sample 2 | 492.54 | Sample 8 | 767.83 |

| Sample 3 | 667.47 | Sample 9 | 158.32 |

| Sample 4 | 719.96 | Sample 10 | 130.48 |

| Sample 5 | 1657.84 | Sample 11 | 572.31 |

| Sample 6 | 652.40 | Sample 12 | 348.82 |

| Mean value | 913.36 | Mean value | 411.86 |

| Statistic Range | Frequency | Statistic Range | Frequency |

|---|---|---|---|

| 0–50 | 154 | 300–350 | 82 |

| 50–100 | 156 | 350–400 | 73 |

| 100–150 | 115 | 400–450 | 56 |

| 150–200 | 108 | 450–500 | 33 |

| 200–250 | 100 | 500–550 | 22 |

| 250–300 | 87 | 550–600 | 14 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, W.; Li, W.; Zhang, S.; Zhou, L.; Wang, H. Temperature Cycle Reliability Analysis of an FBAR Filter-Bonded Ceramic Package. Micromachines 2023, 14, 2132. https://doi.org/10.3390/mi14112132

Tian W, Li W, Zhang S, Zhou L, Wang H. Temperature Cycle Reliability Analysis of an FBAR Filter-Bonded Ceramic Package. Micromachines. 2023; 14(11):2132. https://doi.org/10.3390/mi14112132

Chicago/Turabian StyleTian, Wenchao, Wenbin Li, Shuaiqi Zhang, Liming Zhou, and Heng Wang. 2023. "Temperature Cycle Reliability Analysis of an FBAR Filter-Bonded Ceramic Package" Micromachines 14, no. 11: 2132. https://doi.org/10.3390/mi14112132

APA StyleTian, W., Li, W., Zhang, S., Zhou, L., & Wang, H. (2023). Temperature Cycle Reliability Analysis of an FBAR Filter-Bonded Ceramic Package. Micromachines, 14(11), 2132. https://doi.org/10.3390/mi14112132